关于ARM中的名词常用解释

arm中一些常见英文缩写解释

arm中一些常见英文缩写解释1.arm中一些常见英文缩写解释msb:最高有效位;lsb:最低有效位;ahb:先进的高性能总线;vpb:连接片内外设功能的vlsi外设总线;emc:外部存储器控制器;mam:存储器加速模块;vic:向量中断控制器;spi:全双工串行接口;can:控制器局域网,一种串行通讯协议;pwm:脉宽调制器;etm:嵌入式跟踪宏;cpsr:当前程序状态寄存器;spsr:程序保护状态寄存器;2.mam使用注意事项:答:当改变mam定时值时,必须先通过向mamcr写入0来关闭mam,然后将新值写入mamtim。

最后,将需要的操作模式的对应值写入mamcr,再次打开mam。

对于低于20mhz的系统时钟,mamtim设定为001。

对于20mhz到40mhz之间的系统时钟,建议将flash访问时间设定为2cclk,而在高于40mhz的系统时钟下,建议使用3cclk。

3.vic使用注意事项答:如果在片内ram当中运行代码并且应用程序需要调用中断,那么必须将中断向量重新映射到flash地址0x0。

这样做是因为所有的异常向量都位于地址0x0及以上。

通过将寄存器memmap(位于系统控制模块当中)配置为用户ram模式来实现这一点。

用户代码被连接以便使中断向量表装载到0x4000 0000。

4.arm启动代码设计答:arm启动代码直接面对处理器内核和硬件控制器进行编程,一般使用汇编语言。

启动代码一般包括:中断向量表初始化存储器系统初始化堆栈初始化有特殊要求的端口、设备初始化用户程序执行环境改变处理器模式呼叫主应用程序5.irq和fiq之间的区别答:irq和fiq是arm处理器的两种编程模式。

irq是指中断模式,fir是指快速中断模式。

对于fiq你必须尽快处理你的事情并离开这个模式。

irq可以被fiq所中断,但irq不能中断fiq。

为了使fiq更快,所以这种模式有更多的影子寄存器。

fiq不能调用swi(软件中断)。

ARM技术中英文缩写解说

A R M技术中英文缩写解说-标准化文件发布号:(9456-EUATWK-MWUB-WUNN-INNUL-DDQTY-KIIARM技术中英文缩写解说1.ARM中一些常见英文缩写解释MSB:最高有效位;LSB:最低有效位;AHB:先进的高性能总线;VPB:连接片内外设功能的VLSI外设总线;EMC:外部存储器控制器;MAM:存储器加速模块;VIC:向量中断控制器;SPI:全双工串行接口;CAN:控制器局域网,一种串行通讯协议;PWM:脉宽调制器;ETM:嵌入式跟踪宏;CPSR:当前程序状态寄存器;SPSR:程序保护状态寄存器;2.MAM 使用注意事项:答:当改变 MAM 定时值时,必须先通过向 MAMCR 写入 0 来关闭 MAM,然后将新值写入 MAMTIM。

最后,将需要的操作模式的对应值写入MAMCR,再次打开MAM。

对于低于 20MHz 的系统时钟,MAMTIM 设定为 001。

对于 20MHz 到 40MHz 之间的系统时钟,建议将Flash访问时间设定为2cclk,而在高于40MHz的系统时钟下,建议使用3cclk。

3.VIC 使用注意事项答:如果在片内RAM当中运行代码并且应用程序需要调用中断,那么必须将中断向量重新映射到Flash地址0x0。

这样做是因为所有的异常向量都位于地址0x0及以上。

通过将寄存器MEMMAP(位于系统控制模块当中)配置为用户RAM模式来实现这一点。

用户代码被连接以便使中断向量表装载到0x4000 0000。

4. ARM启动代码设计答:ARM启动代码直接面对处理器内核和硬件控制器进行编程,一般使用汇编语言。

启动代码一般包括:中断向量表初始化存储器系统初始化堆栈初始化有特殊要求的端口、设备初始化用户程序执行环境改变处理器模式呼叫主应用程序5.IRQ 和 FIQ 之间的区别答:IRQ和FIQ是ARM处理器的两种编程模式。

IRQ是指中断模式,FIR是指快速中断模式。

对于 FIQ 你必须尽快处理你的事情并离开这个模式。

ARM体系结构相关术语解释

在线学习好工作/ARM体系结构相关术语解释那么A系列的处理器,会有一个相关的术语,这些术语在这里会给大家做一个介绍,大概这些术语要给大家说一下,首先是流水线,流水线就是底层架构的术语。

流水线:流水线其实是底层架构涉及到的术语,就比如说中间是个CPU,然后外面一个转盘围绕着它在转,它们在多任务分时的处理,那么在处理的过程中,CPU会得到指令,并且处理一些指令,那么它的过程,应该先从某个地方去取指令(F),取完指令之后要译码然后在执行,也就是基于FDE,那么这个就是我们在某一个时刻它应该做的三步操作,就这三步操作我们才能完成CPU正在进行运算,因为它必须要取指令,然后这些指令是ARM指令,CPU默认的情况下不一定认可,所以就要进行一个翻译,翻译成最简单的然后再去执行,那么这个就是第一个时刻“F-D-E”,然后马上它又转到另外一个任务里面,那么就会有一段时间的延后,那么又是一个“F-D-E”的过程,后面同样的延后又会是同样的过程,这样看来就会像一个流水线,所以我们就称为流水线,这就是CPU运转的一个机制,而这样三步就称为三级流水。

后来我们在这个过程中又增加一些步骤,我们可以有多级流水,所以这个就知道这是CPU在去读取指令和运行的一个机制。

DSP-数字信号处理:还有就是DSP-数字信号处理,这个可以把它理解为一个单独的芯片,它能够专门针对数字信号,特别是多媒体是典型的语音数字信号,它可以来单独处理,因为这块数字信号处理对芯片独占性要求挺高,如果我们用主CPU去处理,别的任务就有可能不能兼顾。

Jazelle:Jazelle是ARM里面针对JAVA这块的编程模型。

ThumbEE:这个就是Thumb指令,它的全称是Thumb的环境变量,Thumb 是辅助ARM指令的另外一个指令,它是十六位的,后面的Thumb-2是Thumb的延伸,认为它有一些缺陷,就又升级了,成为十六位和三十二位并存的。

TrustZone:是ARM体系里面的安全架构。

arm术语集锦.

arm术语集锦1. ARM中一些常见英文缩写解释MSB:最高有效位;LSB:最低有效位;AHB:先进的高性能总线;VPB:连接片内外设功能的VLSI外设总线;EMC:外部存储器控制器;MAM:存储器加速模块;VIC:向量中断控制器;SPI:全双工串行接口;CAN:控制器局域网,一种串行通讯协议;PWM:脉宽调制器;ETM:嵌入式跟踪宏;CPSR:当前程式状态寄存器;SPSR:程式保护状态寄存器;2. MAM 使用注意事项:答:当改动MAM定时值时,必须先通过向MAMCR写入0来关闭MAM,然后将新值写入MAMTIM。

最后,将需要的操作模式的对应值写入MAMCR,再次打开MAM。

对于低于20MHz的系统时钟,MAMTIM 设定为001。

对于20MHz到40MHz之间的系统时钟,建议将Flash访问时间设定为2cclk,而在高于40MHz的系统时钟下,建议使用3cclk。

3. VIC 使用注意事项答:如果在片内RAM当中运行代码并且应用程式需要调用中断,那么必须将中断向量重新映射到Flash地址0x0。

这样做是因为所有的异常向量都位于地址0x0及以上。

通过将寄存器MEMMAP(位于系统控制模块当中)设置为用户RAM模式来实现这一点。

用户代码被连接以便使中断向量表装载到0x4000 0000。

4. ARM启动代码设计答:ARM启动代码直接面对处理器内核和硬件控制器进行编程,一般使用汇编语言。

启动代码一般包括:01、中断向量表02、初始化存储器系统03、初始化堆栈初始化有特别需求的端口、设备04、初始化用户程式执行环境05、改动处理器模式06、呼叫主应用程式5. IRQ 和FIQ 之间的差别答:IRQ和FIQ是ARM处理器的两种编程模式。

IRQ是指中断模式,FIR是指快速中断模式。

对于FIQ必须尽快处理你的事情并离开这个模式。

IRQ 能被FIQ 所中断,但IRQ 不能中断FIQ。

为了使FIQ更快,所以这种模式有更多的影子寄存器。

ARM内核的一些名词

LR:链接寄存器

MMAR:存储器管理地址寄存器

MPU:存储器保护单元

MSP:主堆栈

NMI:不可屏蔽中断

NVIC:嵌套向量中断控制器

opcodeΒιβλιοθήκη 指令助记符 PC:程序计算器

PendSV:系统服务请求

PRIGROUP:中断优先级分组域

PRIMASK:中断屏蔽寄存器

PSP:线程堆栈

ETM:嵌入式跟踪宏单元

FAULTMASK:错误屏蔽寄存器

FPB:断点单元

ICI:可中断-可继续指令区

IPSR:中断状态寄存器

IRQ:中断请求

ISR:中断服务程序

IT:If-Then状态区

ITM:仪表跟踪宏单元

LDM和STM:加载存储指令

LDR:加载存储指令

LDREX/STREX:互斥访问指令

APSR:应用状态寄存器

AL:无条件执行

BASEPRI:可屏蔽等于和低于某个优先级的中断

BASEPRI-MAX:BASEPRI允许设置的最大值

BFAR:总线故障地址寄存器

cond:指令执行条件

CONTROL:控制寄存器

CPU ID:基址寄存器

DWT:触发单元

EPSR:执行状态寄存器

Rd:目的寄存器

Rn:第一个操作数的寄存器

SDIV和UDIV:硬件除法指令

SP:堆栈

STR:加载存储指令

SVcall:软件中断

SW—DP:串行线(JTAG也是一种调试)

SysTick:系统节拍定时器

TEX:访问权限位

TPIU:跟踪端口的接口单元

WFI:睡眠控制指令

XPSR:程序状态寄存器

arm常用的名词解释

arm常用的名词解释ARM(Advanced RISC Machine)是一种常用的计算机架构,被广泛应用于移动设备、嵌入式系统和单片机等领域。

本文将对ARM常用的一些名词进行解释,以帮助读者更好地了解ARM架构。

1. RISC(Reduced Instruction Set Computer):精简指令集计算机。

相对于复杂指令集计算机(CISC),RISC采用简化指令集,每条指令都非常简单,执行速度快,并且易于设计和优化硬件。

2. 架构:计算机系统的基本设计和组织原则。

ARM架构设计了一套标准的指令集和寄存器组织,以及与之兼容的处理器核心,为ARM生态系统提供了一致的编程接口。

3. 处理器核心(Processor Core):ARM的核心部分,负责执行指令和进行算术逻辑运算。

常见的ARM处理器核心包括Cortex-A系列(用于应用处理器)、Cortex-M系列(用于嵌入式系统和微控制器)和Cortex-R系列(用于实时应用和嵌入式处理器)。

4. 指令集架构(Instruction Set Architecture):定义了一套计算机指令的规范和编码方式。

ARM指令集架构包括ARMv8-A、ARMv7-A、ARMv6-M等不同的版本,不同版本支持不同的指令集和功能。

5. 寄存器:位于处理器核心内部的高速存储器,用于存储指令执行过程中需要操作的数据。

ARM体系结构中,常见的寄存器包括通用寄存器、程序计数器、状态寄存器等。

6. 多核处理器(Multi-core Processor):使用多个处理器核心的处理器。

ARM 架构支持多核处理器的设计,使得多个核心可以同时进行计算任务,提高处理能力和并行性能。

7. SoC(System on a Chip):一种集成了多个功能组件的芯片,包括处理器核心、内存控制器、I/O接口等。

ARM架构广泛应用于SoC的设计,提供了高度集成的解决方案,节省了系统板块的空间和功耗。

ARM中的一些名词

IIS(Inter-IC Sound bus)又称I2S,是菲利浦公司提出的串行数字音频总线协议。

目前很多音频芯片和MCU都提供了对IIS的支持。

IIS总线只处理声音数据。

Internet Information Services(IIS,互联网信息服务),是由微软公司提供的基于运行Microsoft Windows的互联网基本服务。

IIC是作为英特尔IC的互补,这种总线类型是由菲利浦半导体公司在八十年代初设计出来的,主要是用来连接整体电路(ICS) ,IIC是一种多向控制总线,也就是说多个芯片可以连接到同一总线结构下,同时每个芯片都可以作为实施数据传输的控制源。

这种方式简化了信号传输总线。

MCU(Micro Control Unit)中文名称为微控制单元,又称单片微型计算机(Single Chip Microcomputer)或者单片机,是指随着大规模集成电路的出现及其发展,将计算机的CPU、RAM、ROM、定时计数器和多种I/O接口集成在一片芯片上,形成芯片级的计算机,为不同的应用场合做不同组合控制。

SDRAM是Synchronous Dynamic Random Access Memory(同步动态随机存储器)的简称,SDRAM采用3.3v工作电压,带宽64位,SDRAM 将CPU与RAM通过一个相同的时钟锁在一起,使RAM和CPU能够共享一个时钟周期,以相同的速度同步工作,与EDO内存相比速度能提高50%。

SDRAM基于双存储体结构,内含两个交错的存储阵列,当CPU从一个存储体或阵列访问数据时,另一个就已为读写数据做好了准备,通过这两个存储阵列的紧密切换,读取效率就能得到成倍的提高。

SDRAM不仅可用作主存,在显示卡上的显存方面也有广泛应用。

SDRAM曾经是长时间使用的主流内存,从430TX芯片组到845芯片组都支持SDRAM。

但随着DDR SDRAM的普及,SDRAM也正在慢慢退出主流市场。

关于ARM的22个常用概念介绍_百度文库.

关于ARM的22个常用概念介绍 1.ARM中一些常见英文缩写解释MSB:最高有效位;LSB:最低有效位;AHB:先进的高性能总线;VPB:连接片内外设功能的VLSI外设总线;EMC:外部存储器控制器;MAM:存储器加速模块;VIC:向量中断控制器;SPI:全双工串行接口;CAN:控制器局域网,一种串行通讯协议;PWM:脉宽调制器;ETM:嵌入式跟踪宏;CPSR:当前程序状态寄存器;SPSR:程序保护状态寄存器; 2.MAM 使用注意事项:答:当改变 MAM 定时值时,必须先通过向 MAMCR 写入 0 来关闭 MAM,然后将新值写入 MAMTIM。

最后,将需要的操作模式的对应值写入MAMCR,再次打开MAM。

对于低于 20MHz 的系统时钟,MAMTIM 设定为 001。

对于 20MHz 到 40MHz 之间的系统时钟,建议将Flash访问时间设定为2cclk,而在高于40MHz的系统时钟下,建议使用3cclk。

3.VIC 使用注意事项答:如果在片内RAM当中运行代码并且应用程序需要调用中断,那么必须将中断向量重新映射到Flash地址0x0。

这样做是因为所有的异常向量都位于地址0x0及以上。

通过将寄存器MEMMAP(位于系统控制模块当中)配置为用户RAM模式来实现这一点。

用户代码被连接以便使中断向量表装载到0x4000 0000。

4. ARM启动代码设计答:ARM启动代码直接面对处理器内核和硬件控制器进行编程,一般使用汇编语言。

启动代码一般包括:中断向量表初始化存储器系统初始化堆栈初始化有特殊要求的端口、设备初始化用户程序执行环境改变处理器模式呼叫主应用程序 5.IRQ 和 FIQ 之间的区别答:IRQ和FIQ是ARM处理器的两种编程模式。

IRQ是指中断模式,FIR是指快速中断模式。

对于 FIQ 你必须尽快处理你的事情并离开这个模式。

IRQ 可以被 FIQ 所中断,但 IRQ 不能中断 FIQ。

嵌入式中arm名词解释

嵌入式中arm名词解释

嘿,朋友!你知道什么是嵌入式中的 arm 吗?这可真是个超级重要

的东西啊!就好比汽车里的发动机,没有它车子可跑不起来呀!arm 呢,其实就是一种处理器架构啦。

想象一下,你有一台超级厉害的小机器,它要做各种各样复杂又精

细的任务,这时候就需要一个强大的“大脑”来指挥,arm 就是这个厉害

的“大脑”哟!比如你的手机、智能手表,甚至一些智能家居设备里,

都有 arm 的身影呢。

我记得有一次,我和几个朋友在讨论智能设备,就说到了 arm。

一

个朋友好奇地问:“这 arm 到底有啥了不起的呀?”另一个朋友马上接话:“嘿,你可别小瞧它,没有它,你的手机能那么流畅地运行各种软

件吗?”可不是嘛!arm 就像是一个默默工作的小英雄,在背后支撑着

这些设备的运行呢。

arm 具有很多优点呀,它功耗低,这就像一个很会节约能量的小能手,能让设备长时间工作而不用频繁充电。

而且它性能也很不错,能

快速处理各种数据和任务,就像一个跑步很快的运动员,能迅速到达

终点完成任务。

它还具有高度的可扩展性,就如同乐高积木一样,可以根据不同的

需求组合出不同的功能。

你看现在科技发展得多快呀,各种新的应用

和功能不断涌现,arm 就能很好地适应这种变化。

总之,arm 在嵌入式领域中那可是至关重要的呀!没有它,我们的智能生活可就没那么精彩啦!所以呀,可千万不能小看了 arm 哦!。

ARM知识点讲解.

ARM知识点讲解.1、ARM处理器工作模式有几种?各种工作模式下分别有什么特点?答:ARM 处理器有7种工作模式,这7种模式及其特点是:快速中断模式(fiq)支持高速数据传输或通道处理,外部中断fiq信号有效且CPSR的F=0进入。

中断模式(irq)用于通用中断处理,外部中断irq信号有效CPSR的I=0进入。

管理员模式(svc)- 操作系统的保护模式,复位、软件中断进入。

主要用于SWI(软件中断)和OS(操作系统)。

这个模式有额外的特权,允许你进一步控制计算机。

中止模式(abt)- 支持虚拟内存和/或内存保护预取指令中止/数据中止进入未定义模式(und)- 支持硬件协处理器的软件仿真(浮点、向量运算)未定义指令进入系统模式(sys)- 支持操作系统的特殊用户模式(运行操作系统任务)用户模式(usr)正常的程序执行模式,此模式应用程序不能访问受操作系统保护的资源,不能改变模式,除非异常发生。

2、ARM处理器总共有多少个寄存器,这些寄存器按其在用户编程中的功能是如何划分的?这些寄存器在使用中各有何特殊之处?答:ARM微处理器共有37个32位寄存器,其中31个为通用寄存器,6个为状态寄存器。

31个通用寄存器根据其编程特点可分为如下几种类型:1、不分组寄存器R0-R7 为所有模式共享2、分组寄存器R8-R12R8_fiq-R12_fiq:FIQ模式下的寄存器R8-R12:其它模式共享3、分组寄存器R13-R14分为6组,用户、系统一组,其他每种模式一组。

R13_通常用作堆栈指针SP,R14_通常用作子程序链接寄存器,当进入子程序时,常用来保存PC的返回值其中,mode为以下几种模式之一:usr、fiq、irq、svc、abt、und。

4、程序寄存器R15(PC)所有模式共享6个状态寄存器:一个CPSR当前程序状态寄存器,保存当前程序状态。

五个程序状态备份寄存器SPSR(svc,abt,und,irq,frq),只有在异常模式下,才能被访问;各异常模式都拥有属于自己的SPSR,当发生异常时,SPSR用来保存CPSR的值,从异常退出时则可由SPSR 来恢复CPSR。

ARM程序设计的基本概念

ARM程序设计的基本概念ARM(Advanced RISC Machines)是一种流行的处理器架构,广泛应用于多种设备,包括智能手机、平板电脑、物联网设备等各种嵌入式系统。

ARM程序设计的基本概念包括指令集架构、寄存器、存储器访问和程序流程控制等方面。

1.指令集架构(Instruction Set Architecture,ISA):ISA是ARM处理器的核心组成部分,包括了处理器能够识别和执行的指令集合。

ARM指令集被设计成简洁且高效,以满足节能和性能的要求。

ARM处理器通常支持两种ISA:ARM模式和Thumb模式。

ARM模式下指令长度为32位,能提供更多的功能和更高的性能,而Thumb模式下指令长度为16位,适用于内存空间有限的设备。

2.寄存器:ARM处理器包含多个寄存器,用于存储数据和地址。

常见的寄存器包括通用寄存器、程序计数器、堆栈指针和链接寄存器等。

通用寄存器用于存储计算过程中的临时数据,ARMv8-A体系结构有31个32位的通用寄存器。

程序计数器(PC)指向当前执行的指令地址,堆栈指针(SP)用于管理函数调用时的局部变量和返回地址,链接寄存器(LR)用于存储函数调用的返回地址。

3.存储器访问:ARM处理器通过内存访问指令进行与存储器的交互。

存储器分为两种类型:寄存器文件和主存。

寄存器文件是位于处理器内部的高速存储器,用于暂时存放指令和数据。

主存则是位于处理器外部的大容量存储器,用于存放程序和数据。

ARM处理器通过加载指令将数据从主存中读取到寄存器中,通过存储指令将数据从寄存器写回主存。

存储器访问需要注意对齐和字节顺序等问题,以确保高效的数据交换和正确的数据操作。

4.程序流程控制:程序流程控制是ARM程序设计中的核心概念之一,用于控制指令的执行顺序。

最常见的程序流程控制语句包括分支、跳转和循环等。

分支(Branch)指令用于根据条件改变程序的执行顺序,比如根据一些条件是否成立进行不同的处理。

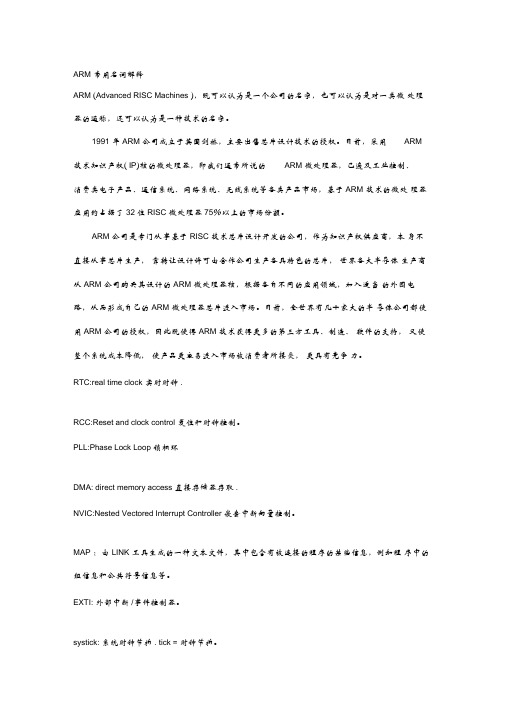

ARM常用名词解释20131105

ARM常用名词解释RTC:real time clock 实时时钟.RCC:Reset and clock control 复位和时钟控制。

PLL:Phase Lock Loop 锁相环DMA: direct memory access 直接存储器存取.NVIC:Nested Vectored Interrupt Controller 嵌套中断向量控制。

MAP:由LINK工具生成的一种文本文件,其中包含有被连接的程序的某些信息,例如程序中的组信息和公共符号信息等。

EXTI:外部中断/事件控制器。

systick: 系统时钟节拍. tick = 时钟节拍。

ADC:Analog-to-Digital Converter模拟/数字转换器BKP: BACKUP备份寄存器CAN: 控制器区域网络FLASH: Flash 存储器GPIO: General-Purpose IN OUT通用I/OI2C:Inter-integrated 电路,是一种通讯总线IWDG:indie watch dog独立看门狗PWR: power电源控制SPI:Serial Peripheral Interface串行外设接口TIM:time定时器USART:Universal Serial Asynchronous Receiver Transmitter通用串行同步异步接收传送器WWDG:window watch dog窗口看门狗寄存器描述CR1 控制寄存器1CR2 控制寄存器2SMCR 从模式控制寄存器DIER DMA和中断使能寄存器SR 状态寄存器EGR 事件生成寄存器CCMR1 捕获/比较模式寄存器1CCMR2 捕获/比较模式寄存器2CCER 捕获/比较使能寄存器CNT 计数寄存器PSC 预分频数寄存器ARR 自动重载寄存器CCR1 捕获/比较寄存器1CCR2 捕获/比较寄存器2CCR3 捕获/比较寄存器3CCR4 捕获/比较寄存器4DCR DMA控制寄存器DMAR DMA猝发模式下的地址寄存器RTC:real time clock实时时钟RCC:Reset and clock control 复位和时钟控制。

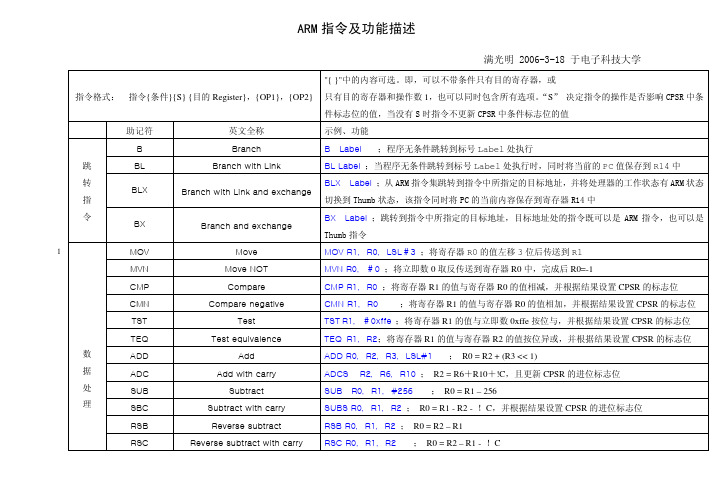

ARM指令全称及含义

Great than or equal, or unordered Less than Less than Greater than or equal , or unordered Unordered

域

VC

HI

LS

GE

LT

GT

LE

AL

V=0 C=1 且 Z=0 C=0 或 Z=1 N=1 且 V=1 或 N=0 且 V=0 N=1 且 V=0 或 N=0 且 V=1 Z=0 或 N=V Z=1 或 N!=V

M[4:0]

0b10000 0b10001 0b10010 0b10011 0b10111 0b11011 0b11111

User FIQ IRQ Supervisor Abort Undefined System

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

Signed saturating arithmetic

Signed arithmetic, halving results

Swap byte

AND R0,R0,#3 ; 该指令保持 R0 的 0、1 位,其余位清零。 ORR R0,R0,#3 ; 该指令设置 R0 的 0、1 位,其余位保持不变。 EOR R0,R0,#3 ; 该指令反转 R0 的 0、1 位,其余位保持不变。 BIC R0,R0,#0b1011 ; 该指令清除 R0 中的位 0、1、和 3,其余的位保持不变。 计算操作数最高端 0 的个数 MUL R0,R1,R2 ;R0 = R1 × R2 MLAS R0,R1,R2,R3 ;R0 = R1 × R2 + R3,同时设置 CPSR 中的相关条件标志位 SMULL R0,R1,R2,R3 ;R0 = (R2 × R3)的低 32 位 R1 = (R2 × R3)的高 32 位 SMLAL R0,R1,R2,R3;R0 =(R2 × R3)的低 32 位+R0; R1 =(R2 × R3)的高 32 位+ R1 UMULL R0,R1,R2,R3;R0 = (R2 × R3)的低 32 位;R1 =(R2 × R3)的高 32 位 UMLAL R0,R1,R2,R3;R0 =(R2 × R3)的低位+R0;R1 =(R2 × R3)的高 32 位+R1 MRS R0,CPSR ;传送 CPSR 的内容到 R0 MSR CPSR_c ,R0 ;传送 R0 的内容到 SPSR,但仅仅修改 CPSR 中的控制位域 LDR R0,[R1,R2]! ;将存储器地址为 R1+R2 的字数据读入 R0,并将新地址 R1+R2 写入 R1。 LDRB R0,[R1,#8] ;将存储器地址为 R1+8 的字节数据读入 R0,并将 R0 的高 24 位清零 LDRH R0,[R1] ;将存储器地址为 R1 的半字数据读入寄存器 R0,并将 R0 的高 16 位清零 LDMFD R13!,{R0,R4-R12,PC} ;将堆栈内容恢复到寄存器(R0,R4 到 R12,LR) STR R0,[R1],#8 ;将 R0 中的字数据写入 R1 为地址的存储器中,并将新地址 R1+8 写入 R1 STRB R0,[R1,#8] ;将寄存器 R0 中的字节数据写入以 R1+8 为地址的存储器中 STRH R0,[R1,#8] ;将寄存器 R0 中的半字数据写入以 R1+8 为地址的存储器中 STMFD R13!,{R0,R4-R12,LR};将寄存器列表中的寄存器(R0,R4 到 R12,LR)存入堆栈 SWP R0,R1,[R2] ;R2 所指的字数据传送到 R0,同时 R1 的数据传送到 R2 所指的单元 SWPB R0,R1,[R2] ;R2 所指的字节数据传送到 R0,R0 高 24 位清零,同时 R1 低 8 位送 R2 所指单元。

常用arm指令集

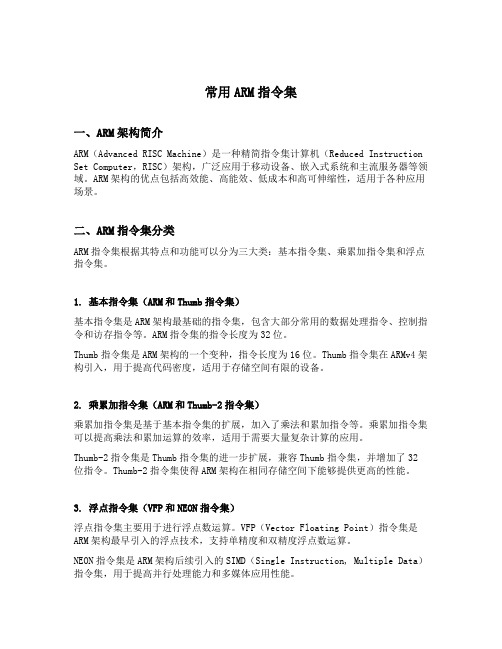

常用ARM指令集一、ARM架构简介ARM(Advanced RISC Machine)是一种精简指令集计算机(Reduced Instruction Set Computer,RISC)架构,广泛应用于移动设备、嵌入式系统和主流服务器等领域。

ARM架构的优点包括高效能、高能效、低成本和高可伸缩性,适用于各种应用场景。

二、ARM指令集分类ARM指令集根据其特点和功能可以分为三大类:基本指令集、乘累加指令集和浮点指令集。

1. 基本指令集(ARM和Thumb指令集)基本指令集是ARM架构最基础的指令集,包含大部分常用的数据处理指令、控制指令和访存指令等。

ARM指令集的指令长度为32位。

Thumb指令集是ARM架构的一个变种,指令长度为16位。

Thumb指令集在ARMv4架构引入,用于提高代码密度,适用于存储空间有限的设备。

2. 乘累加指令集(ARM和Thumb-2指令集)乘累加指令集是基于基本指令集的扩展,加入了乘法和累加指令等。

乘累加指令集可以提高乘法和累加运算的效率,适用于需要大量复杂计算的应用。

Thumb-2指令集是Thumb指令集的进一步扩展,兼容Thumb指令集,并增加了32位指令。

Thumb-2指令集使得ARM架构在相同存储空间下能够提供更高的性能。

3. 浮点指令集(VFP和NEON指令集)浮点指令集主要用于进行浮点数运算。

VFP(Vector Floating Point)指令集是ARM架构最早引入的浮点技术,支持单精度和双精度浮点数运算。

NEON指令集是ARM架构后续引入的SIMD(Single Instruction, Multiple Data)指令集,用于提高并行处理能力和多媒体应用性能。

三、常用ARM指令以下是常用的ARM指令及其功能:1.数据处理指令–加法指令:ADD、ADC(带进位的加法指令)–减法指令:SUB、SBC(带借位的减法指令)–乘法指令:MUL、SMULL(有符号乘法指令)、UMULL(无符号乘法指令)–除法指令:SDIV(有符号除法指令)、UDIV(无符号除法指令)–移位指令:LSL(逻辑左移)、LSR(逻辑右移)、ASR(算术右移)、ROR(循环右移)2.控制指令–条件分支指令:B(无条件分支指令)、BEQ(等于零条件分支指令)、BNE(不等于零条件分支指令)等–无条件分支指令:BX(无条件跳转指令,用于实现函数调用)–跳转指令:BL(带链接跳转指令,用于实现函数调用,并将返回地址保存在链接寄存器中)3.访存指令–数据传送指令:LDR(加载指令,用于将数据从内存中加载到寄存器中)、STR(存储指令,用于将数据从寄存器中存储到内存中)–堆栈指令:PUSH(将数据压入堆栈)、POP(将数据从堆栈中弹出)–字节和半字操作指令:LDRB(加载字节指令)、LDRH(加载半字指令)、STRB(存储字节指令)、STRH(存储半字指令)4.特殊指令–中断指令:SWI(软中断指令,用于触发软件中断)–协处理器指令:CDP(协处理器数据处理指令)、MCR、MRC(协处理器寄存器传递指令)四、ARM指令优化技巧为了提高ARM指令执行效率和代码性能,可以采取以下优化技巧:1.使用适当的数据处理指令,避免不必要的指令执行和数据拷贝。

arm编程名词解释

param:参数

expr:表达式

config:配置

usart:串口,232或485总线,通用同步异步收发器

uart:通用异步收发器,串口

serial:串行接口数据是同步的,连接时要dce同步时钟频率

fsmc:外部总线;可变静态存储控制器

halted:中断

pos:position

msk:假面具,掩码

volatile:易变的,确保本条指令不会因为优化而省略

core:核心

calib:calibration校准

prio:优先级priority

irq:interrupt request中断请求

offset:地址偏移量

periph:外围的,arm核心之外的设备,比如AD,DA,Timer,SPI等

ETM:指令跟踪,ITM:测量跟踪,DWT:数据跟踪

decrement:衰减

declaration:宣告,布告,陈述

imcompatible:不相容的,矛盾的

verify:校验

nvic:嵌套向量中断控制器

exti:中断线

statement:声明,申请,

ecutable:可执行

declaration:宣言,声明,

block:街区,阻止,阻塞,限制

lvalue:左值

modifiable:可更改的

cursor:光标

systick:定时器,当记到零的时候,自动从reload寄存器中重新装载

AHB:主要用于高性能模块(如CPU、DMA和DSP等)之间的连接,作为SoC的片上系统总线,

DMA(Direct Memory Access),即直接存储器存取,是一种快速传送数据的机制。数据传递可以从适配卡到内存,从内存到适配卡或从一段内存到另一段内存。 利用它进行数据传送时不需要CPU的参与。

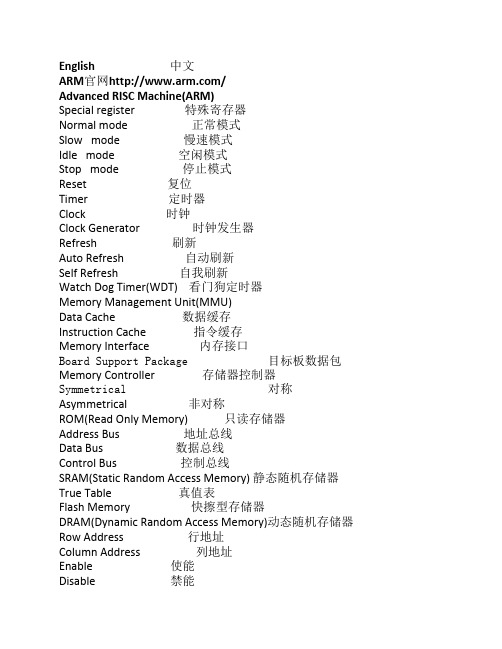

单片机常用词汇及ARM词汇

English 中文ARM官网/Advanced RISC Machine(ARM)Special register 特殊寄存器Normal mode 正常模式Slow mode 慢速模式Idle mode 空闲模式Stop mode 停止模式Reset 复位Timer 定时器Clock 时钟Clock Generator 时钟发生器Refresh 刷新Auto Refresh 自动刷新Self Refresh 自我刷新Watch Dog Timer(WDT) 看门狗定时器Memory Management Unit(MMU)Data Cache 数据缓存Instruction Cache 指令缓存Memory Interface 内存接口Board Support Package 目标板数据包Memory Controller 存储器控制器Symmetrical 对称Asymmetrical 非对称ROM(Read Only Memory) 只读存储器Address Bus 地址总线Data Bus 数据总线Control Bus 控制总线SRAM(Static Random Access Memory) 静态随机存储器True Table 真值表Flash Memory 快擦型存储器DRAM(Dynamic Random Access Memory)动态随机存储器Row Address 行地址Column Address 列地址Enable 使能Disable 禁能SDRRAM(Synchronous DRAM) 同步动态随机存储器Command 命令ARM Core ARM核SoC(System On Chip) 系统芯片Write Buffer 写入缓冲区Cache 高速缓存DSP(Digital Signal Processor) 数字信号处理器Interrupt Controller 中断控制器LAN Controller 网络控制器UART 异步串行收发数据RTC(Real Time Clock) 实时时钟RAM(Random Access Memory) 随机存储器JTAG(Join Test Action Group)RISC(Reduced Instruction Set Computer)IP(Intellectual Property)Debugger 调试器Object File 目标文件Command Line 命令模式Plain Binary 无格式的二进制文件Breakpoints 可设置断点RDI(Remote Debug Interface) 远程调试接口Pseudo instructions 伪指令Hardware Reset 硬件复位Reset Exception 复位异常Memory Bus Mode 存储器的总线模式Crystal 石英晶体振荡器Oscillator 振荡器Datasheet 数据手册Timing Chart 时序图Memory Bus Width 存储器总线宽度Boot 引导Memory Type 存储类型Memory Access Type 存储器存取类型Memory Bank 内存区块Memory Interface 存储器接口Instruction Cycle 指令周期Burst mode 快速模式ROW 行Column 列BA(Bank Address) 区块位置选择Special Register 特殊寄存器Chip Enable 芯片使能MSB(Most Significant Byte) 最有意义的字节Bus Mode 总线模式User Mode 用户模式FIQ mode 快速中断模式IRQ mode 中断模式Supervisor mode 管理模式Abort mode 中止模式System Mode 系统模式Undefined mode 未定义模式Exception 异常Microprocessor 微处理器Machine Code 机器码Reset Exception 复位异常General Purpose Register 通用目的寄存器Status Register 状态寄存器Bank Register 模式寄存器SP(Stack Pointer) 堆栈指针Current Mode 当前模式Local Variable 局部变量FILO(Fist In Last Out) 先进后出SP(Stack Pointer) 堆栈指针Link Register 连接寄存器Label 标号Instruction 指令PC(Program Counter) 程序计数器CPSR(Current Program Status Register) 当前程序状态寄存器Condition Code Flag 条件标记Control Bit 控制位Mode Bit 模式位FIQ 快速中断IRQ 中断Disable 停止位Interrupt disable bit 中断停止位TBIT(Thumb Bit) 又称State Bit状态位Software Interrupt 软件中断Offset 偏移量Overflow 发生溢出Shifted Register 移位寄存器Logical Right 逻辑右移Logical Left 逻辑左移Arithmetic Right 算术右移Rotate Right 右移循环Immediate Operand Rotates 立即操作数的旋转操作SPSR(Saved Program Status Register) 保存程序状态寄存器Register offset 偏移寄存器Source register 源寄存器Addressing Modes 寻址模式Block Data Transfer Instructions 区块数据转换指令Addressing Mode Names 寻址模式名称Exception 异常Interrupt Controller 中断控制器Disable IRQ 停止中断请求SWI(Software Interrupt Exception) 软件中断异常Abort Exception 中止异常Undefined Exception 未定义异常Abort of data Exception 数据中止异常Boot Loader 引导程序Rest Exception 复位异常Static Exception Handle Routine 执行静态异常处理程序Jump Table 条转表Assembler 编译Object File 目标文件Binary File 二进制文件ADS(ARM Developer Suite)编译器Boot Loader 软件引导程序Embedded System 嵌入式系统Listing 列表文件Local Variable 局部变量Pin Group 管脚组Feature 特性Vector 向量Non-vector 非向量2-channel Purpose DMA 双通道通用目的直接内存存取2-channel Bridge DMA-peripheral 双通道桥式直接内存存取Single Scan 单条扫描Dual Scan 双条扫描Watch Dog Timer 看门狗定时器IIC bus interface IIC接口IIS bus interface IIS接口SIO Interface 串行传输接口Bus Controller 总线控制器Write Buffer 写入缓冲区寄存器Clock Generator 时钟发生器Lock Time 锁定时间Master Unit 主要单元Slave Unit 次要单元Offset 偏移量Stack Pointer 堆栈指针GPIO Port 输入输出端口Wakeup 唤醒Power consumption 电源管理模式Low Lever trigger 低电平触发High Level trigger 高电平触发Falling edge trigger 下降沿触发Rising edge trigger 上升沿触发Edge trigger 边沿触发Digital filter 数字过滤器Level trigger 电平触发Edge trigger 边沿触发Ext Bus 扩展总线Baud-rate 波特率Infra-red IR 红外线发送/接收Stop bit 停止位Parity-bit 奇偶校验检查Handshake 发送/接收具有硬件握手Loop-back 回路检查模式Overrun error 溢出错误Parity error 奇偶校验错误Frame error 帧错误Break condition 中止条件Time-out condition 超时条件Look back 回路检查BPS(Bits Per Second) 每秒发送几个Bits Serial communication 串行传输Serial communication Operation 串行传输操作Parity bit 奇偶校验位Parallel 并列传输Odd 奇数位Even 偶数位Ring Buffer 环状缓冲区Fptr 前指针Rptr 后指针中英文术语对照表Abort Exception 中止异常Abort Mode 中止模式Access 存取(包含读取及写入)Address 地址Address Bus 地址总线AC(Alternating Current) 交流Access Cycle 存取周期ADC(Analog Digital Converter) 模拟数字转换器AFC(Auto Flow Control) 自动流量控制Assembler 汇编器Assembly 汇编Asynchronous 异步Auto Index 自动索引Auto-reload 自动重载Auto Refresh 自动刷新Bank 区块Bank Address(BA) 区块位置选择Bank Control Register 区块控制寄存器Bank Select 区块选择Bank Size Register 区块大小寄存器Bank Register 模式寄存器Base Register 基地址寄存器Baud-rate 波特率BDMA(Bridge Direct Memory Access) 桥接式直接内存存取Binary File 二进制文件BIOS(Basic Input output System) 基本输入输出系统Buffer 缓冲区Bus Controller 总线控制器Bus 总线Bus Hold Acknowledge 总线保持应答Bus Hold Request 总线保持请求Bus Mode 总线模式Boot 引导Boot Loader 引导程序Break Condition 中止条件Breakpoint 断点Byte Enable 位使能Cache(memory) 高速缓存CAS(Column Address Signal) 列地址信号CAS Latency 列地址信号等待时间Chip Enable 芯片使能Chip Select 芯片选择Clock 时钟Clock Control Register 时钟控制寄存器Clock Generator 时钟发生器Column Address 列地址Command 命令Command-line 命令模式Condition(Code)Flag 条件标志Controller 控制器Coprocessor 协处理器CPU(Central Processing Unit) 中央处理器CPSR(Current Program Status Register) 当前程序状态寄存器Current Mode 当前模式Crystal 石英振荡器Cycle 周期Current TRQ Priority of Master Register当前中断请求优先级的主寄存器Current TRQ Priority of Slave Register 当前中断请求优先级的从寄存器Device 设备Data 数据Data Bus 数据总线Data Abort 数据中止Data Cache 数据高速缓冲寄存器Destination Register 目标寄存器Digital Filter 数字滤波器Disable 禁止/停止/禁能DMA (Direct Memory Access) 直接内存存取DSP(Digital Signal Processor) 数字信号处理器Edge trigger 边沿触发Enable 使能Exception Handler 异常处理Exception 异常Exception Handle Routine 异常处理程序Exception Vector 异常向量Exception Vector Table 异常向量表External Interrupt 外部中断External Interrupt Pending Register 外部中断未处理器Falling edge trigger 下降沿触发FIFO 先进先出FILO 先进后出FIQ(Fast Interrupt Request) 快速中断(请求)FIQ Exception 快速中断异常FIQ(Fast Interrupt Request) Mode 快速中断(请求)模式Frame error 帧错误Front Pointer 前指针General Purpose Register 通用寄存器GPIO(General Purpose Input/Output) 通用(目的)输入输出Handshake 握手Hardware Reset 硬件复位High Level Trigger 高电平触发Hold Time 持续时间IDLE Mode 空闲模式Instruction 指令Instruction Cache 指令高速缓存Instruction Cycle 指令周期Internal SDRAM 内部存储器Interrupt 中断Interrupt Controller 中断控制器Interrupt Control Register 中断控制寄存器Interrupt Exception 异常中断Interrupt Mask Register 中断屏蔽寄存器Interrupt Mode Register 中断模式寄存器Interrupt Pending Register 中断未处理寄存器Interrupt Priority 中断优先级Interrupt Priority Generating Block 中断优先级产生模块Interrupt Request 中断请求Interrupt Service Pending Clear Register中断服务未处理清楚寄存器Interrupt Source 中断源Interrupt Vector 中断向量表I/O Pad 输入输出接点I/O Port 输入输出端口IR(Infra-red) 红外线IRQ(Interrupt Request) 中断请求IRQ(Interrupt Request) Mode 中断请求模式IRQ Interrupt Service Pending Register 中断请求服务处理寄存器ISR(Interrupt Service Routine) 中断服务程序IP(Intellectual Property) 网际协议IRQ Priority Of Master Register 中断请求优先级的主寄存器IRQ Priority Of Slave Register 中断请求优先级的从寄存器Label 标签Level Trigger 电平触发Link Register 连接寄存器Loop-back 回环Local Variable 局部变量Lock Time 锁定时间Lock Time Count Register 锁定时间计数寄存器Lower Byte 低位Low Level trigger 低电平触发LRU(Least Recently Used) 最近使用过的内存Machine Code 机器码Macro 宏Main Clock 主时钟Mask 屏蔽Master Priority Generating Unit 主优先级产生模块单元Master Unit 主单元Memory Access Type 内存存取类型Memory Bank 内存区块Memory Bus Mode 内存总线模式Memory Bus Width 内存总线宽度Memory Controller 内存控制器Memory Map 内存映射Memory Type 内存类型Microprocessor 微处理器Millisecond 毫秒MODEM(Modulator-Demodulator) 调制解调器MRSR(SDRAM Mode Register Set Register) SDRAM模式寄存器设定寄存器Non-auto flow control 非自动流量控制Non-Cacheable Area Control Register 非高速缓存区域控制寄存器Non-PLL Mode 非PLL模式Non-Page-Mode 非分页模式Non-vector Interrupt 非向量式中断Normal Mode 正常模式NS (Nero Second) 豪微妙Object Code 目标码Object File 目标文件Offset 偏移量Oscillator 振荡器Open Drain 开漏集Operand Register 操作寄存器Operation Code 操作码Output Port 输出端口Overrun error 溢出错误Page Mode 分页模式Parity bit 奇偶Parity error 奇偶错误PC(Program Counter) 个人计算机Pending Condition 未处理条件PFD(Phase Frequency Detector) 相位频率检测器Plain Binary 无格式二进制PLL(Phase-Locked-Loop) 锁相环PLL Control Register 锁相环控制寄存器Port 端口Port Control Register 端口控制寄存器Post-Index 后索引Post-Decrement Addressing 后减寻址模式Post-Increment Addressing 后增寻址模式Power Down Mode 省电模式Power Consumption 电源管理Pre-assembly 预编译Pre-charge 预先充电Pre-fetch Abort 指令获取中止Pre-Index 前索引Priority Generating Block 优先级产生模块Power-On Reset 电源复位Pseudo Instruction 伪指令PSR(Program Status Register) 程序状态寄存器Pre-Decrement Addressing 前减寻址模式Pre-Increment Addressing 前增寻址模式Privileged Mode 特权模式Project 工程Pull-Up register 上拉寄存器Pull-Up resister 上拉电阻PWM (Pulse Width Modulation) Timer 脉宽调制寄存器RAM(Random Access Memory) 随机存储器RAS(Row Address Signal) 行地址信号Rear Pointer 后指针Receive buffer register 接收缓冲寄存器RESET 复位Reset Exception 复位异常Refresh 刷新Refresh Control Register 刷新控制寄存器Remapping 二次映射Reset Exception 异常复位Return address 返回地址RDI (Remote Debug Interface) 远程调试接口Ring Buffer 环状缓冲区Rising edge trigger 上升沿触发Round-robin 循环Row Address 行地址RTC (Real Time Clock) 实时时钟Rx FIFO 接收先进先出缓冲区Output Enable 输出使能Self-refresh 自我刷新Section Name 节区名称Serial 串行Serial Communication 串行通讯Serial Communication Operation 串行通讯操作SIO(Serial Input and Output) 串行输入输出SIO(Synchronous Input output) 同步输入输出SL Idle Mode 慢速空闲模式Slave Priority Generating unit 从优先级产生模块单元Slave Unit 从单元Slow Mode 慢速模式Slow Clock Control Register 慢速时钟控制寄存器SOC (System On Chip) 片上系统Special Function Register 特殊功能寄存器Special Pull Up Resister Control Register特殊上拉电阻寄存器控制寄存器SPSR(Saved Program Status Register) 保存程序状态寄存器Start Bit 开始bitStatus Register 状态寄存器Stack 堆栈Stack Pointer (SP) 堆栈指针Static Exception Handle Routine 静态异常处理程序Stop bit 结束bitStop Mode 停止模式SWI (Software Interrupt) 软件中断SWI Exception 软件中断异常Supervision Mode 监督管理模式Synchronous 同步System Bus Priority Control Register 系统总线优先级控制寄存器System Configuration Register 系统配置寄存器System Mode 系统模式System Reset 系统复位THAW mode 解冻模式Timer 时间,定时器Time-out condition 超时条件Transmit buffer register 发送缓冲寄存器Transmit shifter 发送位移器Transmit shift register 发送位移寄存器UART(Universal Asynchronous Receiver and Transmitter)通用异步串行收发UART Control Register 通用异步串行收发器控制寄存器UART Baud-rate Division Register通用异步串行收发器的波特率分频寄存器UART FIFO Control Register通用异步串行收发器的先进先出缓冲区控制寄存UART FIFO Status Register通用异步串行收发器的先进先出缓冲区状态寄存器UART Line Control Register通用异步串行收发器在线控制寄存器UART MODEM Control Register通用异步串行收发器的调制解调器控制寄存器UART MODEM Status Register通用异步串行收发器的调制解调器状态寄存器UART Receive Holding Buffer Register通用异步串行收发器的接收保持缓冲~UART Transmit Holding Buffer Register通用异步串行收发器的发送保持缓冲UART TX/RX Status Register 通用异步串行收发器的状态寄存器UART RX Error Status Register通用异步串行收发器的接收错误状态寄存器Undefined Exception 未定义异常Undefined Mode 未定义模式Upper Byte 高位User Mode 用户模式Vectored Interrupt 向量式中断Vector Table 向量表Watchdog Timer Count Register 看门狗定时器计数寄存器Watchdog Timer Data Register 看门狗定时器数据寄存器WDT (Watch Dog Timer) 看门狗定时器Wake Up 叫(唤)醒Write 写入Write Back 写回Write Buffer 写入缓冲区Write Enable 写入使能ZDMA (General Direct Memory Access) 一般直接内存存取。

arm 词根词缀

arm 词根词缀《【arm 词根词缀】》1. 单词概述单词:arm含义:这个单词有多种含义呢。

作名词时,它可以表示“手臂”,这是我们身体的一部分,就像我们经常说“raise your arms(举起你的手臂)”;还可以表示“武器”,比如在战争或者军事场景中,“arms and ammunition(武器和弹药)”。

作动词时,有“武装”的意思,例如“arm oneself(武装自己)”。

2. 词根词缀解析词根:arm - 来源于拉丁语,表示“武器”或者“手臂”。

词缀:其实arm本身也可以作为词干,没有太多额外典型的词缀与之组合出新意的情况,但如果从广义来说, - ed(作为过去式词缀),当arm加上 - ed变成armed,表示“武装了的,有武器的”,就像“an armed force(一支武装力量)”。

这里的合成逻辑就是:arm(本身有武器、武装的意思)+ - ed(表示动作的完成或状态) = armed(武装了的,有武器的)。

3. 应用短文与场景应用短文1:I was walking down the street one day, and I saw this really strange guy. He had his arms full of all kinds of stuff. I mean, it was like he was carrying half of his house in his arms! My friend Tom was with me, and he said, "Look at that guy. What do you think he's doing?" I replied, "I have no idea. Maybe he's moving or something." As we got closer, we noticed that some of the things he was carrying looked like old - fashioned arms. I was a bit worried and whispered to Tom, "Do you think he's up to no good?I mean, why would someone be carrying arms like that in the middle of the street?" Tom shrugged and said, "Maybe he's a collector or something. But it's still a bit odd." We decided to keep our distance just in case. After all, arms can be dangerous things if they're in the wrong hands.中文翻译:有一天我正走在街上,然后看到一个特别奇怪的家伙。

ARM常用名词解释

ARM 常用名词解释ARM (Advanced RISC Machines ),既可以认为是一个公司的名字,也可以认为是对一类微处理器的通称,还可以认为是一种技术的名字。

1991 年ARM 公司成立于英国剑桥,主要出售芯片设计技术的授权。

目前,采用ARM 技术知识产权( IP)核的微处理器,即我们通常所说的ARM 微处理器,已遍及工业控制、消费类电子产品、通信系统、网络系统、无线系统等各类产品市场,基于ARM 技术的微处理器应用约占据了32位RISC 微处理器75%以上的市场份额。

ARM 公司是专门从事基于RISC 技术芯片设计开发的公司,作为知识产权供应商,本身不直接从事芯片生产,靠转让设计许可由合作公司生产各具特色的芯片,世界各大半导体生产商从ARM 公司购买其设计的ARM 微处理器核,根据各自不同的应用领域,加入适当的外围电路,从而形成自己的ARM 微处理器芯片进入市场。

目前,全世界有几十家大的半导体公司都使用ARM 公司的授权,因此既使得ARM 技术获得更多的第三方工具、制造、软件的支持,又使整个系统成本降低,使产品更容易进入市场被消费者所接受,更具有竞争力。

RTC:real time clock 实时时钟.RCC:Reset and clock control 复位和时钟控制。

PLL:Phase Lock Loop 锁相环DMA: direct memory access 直接存储器存取.NVIC:Nested Vectored Interrupt Controller 嵌套中断向量控制。

MAP :由LINK 工具生成的一种文本文件,其中包含有被连接的程序的某些信息,例如程序中的组信息和公共符号信息等。

EXTI: 外部中断/事件控制器。

systick: 系统时钟节拍. tick = 时钟节拍。

ADC:Analog-to-Digital Converter 模拟/数字转换器BKP: BACKUP 备份寄存器CAN: 控制器区域网络FLASH: Flash 存储器GPIO: General-Purpose IN OUT 通用I/OI2C:Inter-integrated 电路,是一种通讯总线IWDG:indie watch dog 独立看门狗PWR: power 电源控制SPI:Serial Peripheral Interface 串行外设接口TIM:time 定时器USART:Universal Serial Asynchronous Receiver Transmitter 通用串行同步异步接收传送器WWDG:window watch dog 窗口看门狗寄存器描述CR1 控制寄存器1CR2 控制寄存器2SMCR 从模式控制寄存器DIER DMA 和中断使能寄存器SR 状态寄存器EGR 事件生成寄存器CCMR1 捕获/比较模式寄存器1CCMR2 捕获/比较模式寄存器2CCER 捕获/比较使能寄存器CNT 计数寄存器PSC 预分频数寄存器ARR 自动重载寄存器CCR1 捕获/比较寄存器1CCR2 捕获/比较寄存器2CCR3 捕获/比较寄存器3CCR4 捕获/比较寄存器4DCR DMA 控制寄存器DMAR DMA 猝发模式下的地址寄存器RTC:real time clock 实时时钟RCC:Reset and clock control 复位和时钟控制。

arm动词用法集锦

arm动词用法集锦arm的意思是手臂,它还可以作为动词用,意思是武装。

下面小编把它的用法分享给大家!释义armn. 手臂;武器;袖子;装备;部门vi. 武装起来vt. 武装;备战Orion arm 猎户臂 ; 猎户座旋臂 ; 叫猎户涡臂valve arm 气阀摇臂 ; 汽门摇臂 ; 阀杆 ; 阀摇臂Trailing Arm 曳力杆 ; [车辆] 纵臂 ; 拖曳臂 ; 拖拽臂left arm 左臂 ; 左扶手 ; 左手臂Actuating arm 驱动臂 ; [机] 驱动杆 ; 力臂 ; 起动臂Lower Arm 下臂 ; 下拉臂 ; 下摇臂 ; 下摆臂arm extension 面前直臂上举dynein arm 缺少位动蛋白臂 ; 纤毛蛋白臂 ; 动力蛋白臂righting arm 扶正力臂 ; 稳性力臂 ; 回复力臂 ; 复原臂arm用法arm可以用作名词arm用作名词的基本意思是“臂”,多指人的手臂、胳膊,也可指动物的前肢,亦喻指各种状似手臂的东西。

arm的复数形式arms,指“武器(尤指枪支)”。

用于比喻时可指“权力”,也可指“兵种”,此时既不能带不定冠词,也不能为数词所修饰。

用作定语时亦然。

arms可用在另一名词前作修饰语。

arm用作名词的用法例句You should wind a cloth round the wounded arm.你应该把一块布缠在受伤的和臂上。

The archer holds the bow in his bow arm.运动员用执弓臂握住弓。

His left arm was hurt in an accident.他的左胳膊在一次事故中受伤了。

arm用作名词的用法例句They were not allowed to use arms.不许他们使用武器。

We must arm ourselves against the enemy.我们必须武装自己,防范敌人。

The new battleship shall be armed with 16-inch guns.新战舰将以16英寸口径的大炮武装起来。

ARM知识

一.嵌入式系统嵌入式系统是“控制、监视或者辅助装置、机器和设备运行的装置”(devices used to control, monitor, or assist the operation of equipment, machinery or plants)。

从中可看出嵌入式系统是软件和硬件的综合体,还可以涵盖机械等附属装置。

嵌入式系统是与应用紧密结合的,具有很强专用性,必须结合实际系统需求进行合理的裁减利用。

国内一个普遍被认同的定义是:以应用为中心、以计算机技术为基础、软件硬件可裁剪、适应应用系统对功能、可靠性、成本、体积、功耗严格要求的专用计算机系统。

分类基于硬件嵌入式微处理器(Micro Processor Unit,MPU)嵌入式微控制器(Microcontroller Unit, MCU)嵌入式DSP处理器(Embedded Digital Signal Processor, EDSP)嵌入式片上系统(System On Chip)soc基于软件从软件方面划分,主要可以依据操作系统的类型。

目前嵌入式系统的软件主要有两大类:实时系统和分时系统。

其中实时系统又分为两类:硬实时系统和软实时系统。

组成硬件层硬件层中包含嵌入式微处理器、存储器(SDRAM、ROM、Flash等)、通用设备接口和I/O接口(A/D、D/A、I/O等)。

在一片嵌入式处理器基础上添加电源电路、时钟电路和存储器电路,就构成了一个嵌入式核心控制模块。

其中操作系统和应用程序都可以固化在ROM中。

中间层也称为硬件抽象层(Hardware Abstract Layer,HAL)或板级支持包(Board Support Package,BSP设计一个完整的BSP需要完成两部分工作:嵌入式系统的硬件初始化以及BSP功能,设计硬件相关的设备驱动。

系统软件层系统软件层由实时多任务操作系统(Real-time Operation System,RTOS)(多为嵌入式操作系统)、文件系统、图形用户接口(Graphic User Interface,GUI)、网络系统及通用组件模块组成。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

关于ARM中的名词常用解释1.ARM中一些常见英文缩写解释MSB:最高有效位;LSB:最低有效位;AHB:先进的高性能总线;VPB:连接片内外设功能的VLSI外设总线;EMC:外部存储器控制器;MAM:存储器加速模块;VIC:向量中断控制器;SPI:全双工串行接口;CAN:控制器局域网,一种串行通讯协议;PWM:脉宽调制器;ETM:嵌入式跟踪宏;CPSR:当前程序状态寄存器;SPSR:程序保护状态寄存器;2.MAM 使用注意事项:当改变MAM 定时值时,必须先通过向MAMCR 写入0 来关闭MAM,然后将新值写入MAM ti M。

最后,将需要的操作模式的对应值写入MAMCR,再次打开MAM。

对于低于20MHz 的系统时钟,MAMTIM 设定为001。

对于20MHz 到40MHz 之间的系统时钟,建议将Flash访问时间设定为2cclk,而在高于40MHz 的系统时钟下,建议使用3cclk。

3.VIC 使用注意事项如果在片内RAM当中运行代码并且应用程序需要调用中断,那么必须将中断向量重新映射到Flash地址0x0。

这样做是因为所有的异常向量都位于地址0x0及以上。

通过将寄存器MEMMAP(位于系统控制模块当中)配置为用户RAM模式来实现这一点。

用户代码被连接以便使中断向量表装载到0x4000 0000。

4. ARM启动代码设计ARM启动代码直接面对处理器内核和硬件控制器进行编程,一般使用汇编语言。

启动代码一般包括:中断向量表初始化存储器系统初始化堆栈初始化有特殊要求的端口、设备初始化用户程序执行环境改变处理器模式呼叫主应用程序5.IRQ 和FIQ 之间的区别IRQ和FIQ是ARM处理器的两种编程模式。

IRQ是指中断模式,FIR是指快速中断模式。

对于FIQ 你必须尽快处理你的事情并离开这个模式。

IRQ 可以被FIQ 所中断,但IRQ 不能中断FIQ。

为了使FIQ 更快,所以这种模式有更多的影子寄存器。

FIQ 不能调用SWI(软件中断)。

FIQ 还必须禁用中断。

如果一个FIQ 例程必须重新启用中断,则它太慢了,并应该是IRQ 而不是FIQ。

6.ARM处理器对异常中断的响应过程ARM处理器对异常中断的响应过程如下所述:保存处理器当前状态、中断屏蔽位以及各条件标志位;设置当前程序状态寄存器CPSR中的相应位;将寄存器lr_mode设置成返回地址;将程序计数器值PC,设置成该异常中断的中断向量地址,跳转到相应异常中断处执行。

7.ARM指令与Thumb指令的区别在ARM体系结构中,ARM指令集中的指令是32位的指令,其执行效率很高。

对于存储系统数据总线为16位的应用系统,ARM体系提供了Thumb指令集。

Thumb指令集是对ARM指令集的一个子集重新编码得到的,指令长度为16位。

通常在处理器执行ARM程序时,称处理器处于ARM状态;当处理器执行Thumb程序时,称处理器处于Thumb状态。

Thumb指令集并没有改变ARM体系地层的程序设计模型,只是在该模型上加上了一些限制条件。

Thumb指令集中的数据处理指令的操作数仍然为32位,指令寻址地址也是32位的。

8.什么是ATPCS为了使单独编译的C语言程序和汇编程序之间能够相互调用,必须为子程序之间的调用规定一定的规则。

ATPCS就是ARM程序和Thumb程序中子程序调用的基本规则。

这些规则包括寄存器使用规则,数据栈的使用规则,参数的传递规则等。

9.ARM程序和Thumb程序混合使用的场合通常,Thumb程序比ARM程序更加紧凑,而且对于内存为8位或16位的系统,使用Thumb程序效率更高。

但是,在下面一些场合下,程序必须运行在ARM状态,这时就需要混合使用ARM和Thumb程序。

强调速度的场合,应该使用ARM程序;有些功能只能由ARM程序完成。

如:使用或者禁止异常中断;当处理器进入异常中断处理程序时,程序状态切换到ARM状态,即在异常中断处理程序入口的一些指令是ARM指令,然后根据需要程序可以切换到Thumb状态,在异常中断程序返回前,程序再切换到ARM状态。

ARM处理器总是从ARM状态开始执行。

因而,如果要在调试器中运行Thumb程序,必须为该Thumb程序添加一个ARM程序头,然后再切换到Thumb状态,执行Thumb程序。

10.ARM处理器运行模式ARM微处理器支持7种运行模式,分别为:用户模式(usr):ARM处理器正常的程序执行状态;快速中断模式(fiq):用于高速数据传输或通道管理;外部中断模式(irq):用于通用的中断处理;管理模式(svc):操作系统使用的保护模式;数据访问终止模式(abt):当数据或指令预取终止时进入该模式,用于虚拟存储及存储保护;系统模式(sys):运行具有特权的操作系统任务;未定义指令中止模式(und):当未定义指令执行时进入该模式,可用于支持硬件协处理器的软件仿真11.ARM体系结构所支持的异常类型ARM体系结构所支持的异常和具体含义如下(圈里面的数字表示优先级):复位①:当处理器的复位电平有效时,产生复位异常,程序跳转到复位异常处执行(异常向量:0x0000,0000);未定义指令⑥:当ARM处理器或协处理器遇到不能处理的指令时,产生为定义异常。

可使用该异常机制进行软件仿真(异常向量:0x0000,0004);软件中断⑥:有执行SWI指令产生,可用于用户模式下程序调用特权操作指令。

可使用该异常机制实现系统功能调用(异常向量:0x0000,0008);指令预取中止⑤:若处理器的预取指令的地址不存在,或该地址不允许当前指令访问,存储器会向处理器发出中止信号,当预取指令被执行时,才会产生指令预取中止异常(异常向量:0x0000,000C);数据中止②:若处理器数据访问的指令的地址不存在,或该地址不允许当前指令访问,产生数据中止异常(异常向量:0x0000,0010);IRQ④(外部中断请求):当处理器的外部中断请求引脚有效,且CPSR中的I位为0时,产生IRQ异常。

系统的外设可以该异常请求中断服务(异常向量:0x0000,0018);FIQ③(快速中断请求):当处理器的快速中断请求引脚有效,且CPSR中的F位为0时,产生FIQ异常(异常向量:0x0000,001C)。

说明:其中异常向量0x0000,0014为保留的异常向量。

12.ARM体系结构的存储器格式ARM体系结构的存储器格式有如下两种:大端格式:字数据的高字节存储在低地址中,字数据的低字节存放在高地址中;小端格式:与大端存储格式相反,高地址存放数据的高字节,低地址存放数据的低字节。

13.ARM寄存器总结:ARM有16个32位的寄存器(r0到r15)。

r15充当程序寄存器PC,r14(link register)存储子程序的返回地址,r13存储的是堆栈地址。

ARM有一个当前程序状态寄存器:CPSR。

一些寄存器(r13,r14)在异常发生时会产生新的instances,比如IRQ处理器模式,这时处理器使用r13_irq和r14_irqARM的子程序调用是很快的,因为子程序的返回地址不需要存放在堆栈中。

14.存储器重新映射(Remap)的原因:使Flash存储器中的FIQ处理程序不必考虑因为重新映射所导致的存储器边界问题;用来处理代码空间中段边界仲裁的SRAM和Boot Block向量的使用大大减少;为超过单字转移指令范围的跳转提供空间来保存常量。

ARM中的重映射是指在程序执行过程中通过写某个功能寄存器位操作达到重新分配其存储器地址空间的映射。

一个典型的应用就是应用程序存储在Flash/ROM中,初始这些存储器地址是从0开始的,但这些存储器的读时间比SRAM/DRAM长,造成其内部执行频率不高,故一般在前面一段程序将代码搬移到SRAM/DRAM中去,然后重新映射存储器空间,将相应SRAM/DRAM映射到地址0,重新执行程序可达到高速运行的目的。

15.存储异常向量表中程序跳转使用LDR指令,而不使用B指令的原因:LDR指令可以全地址范围跳转,而B指令只能在前后32MB范围内跳转;芯片具有Remap功能。

当向量表位于内部RAM或外部存储器中,用B指令不能跳转到正确的位置。

16.锁相环(PLL)注意要点:PLL在芯片复位或进入掉电模式时被关闭并旁路,在掉电唤醒后不会自动恢复PLL的设定;PLL只能通过软件使能;PLL在激活后必须等待其锁定,然后才能连接;PLL如果设置不当将会导致芯片的错误操作。

17.ARM7与ARM9的区别:ARM7内核是0.9MIPS/MHz的三级流水线和冯&S226;诺伊曼结构;ARM9内核是五级流水线,提供1.1MIPS/MHz的哈佛结构。

ARM7没有MMU,ARM720T是MMU的;ARM9是有MMU的,ARM940T只有Memory protection unit.不是一个完整的MMU。

ARM7TDMI提供了非常好的性能——功耗比。

它包含了Thumb指令集快速乘法指令和ICE调试技术的内核。

ARM9的时钟频率比ARM7更高,采用哈佛结构区分了数据总线和指令总线。

18.VIC的基本操作如下:设置IRQ/FIQ中断,若是IRQ中断则可以设置为向量中断并分配中断优先级,否则为非向量IRQ。

然后可以设置中断允许,以及向量中断对应地址或非向量中断默认地址。

当有中断后,若是IRQ中断,则可以读取向量地址寄存器,然后跳转到相应的代码。

当要退出中断时,对向量地址寄存器写0,通知VIC 中断结束。

当发生中断时,处理器将会切换处理器模式,同时相关的寄存器也将会映射。

19.使用外部中断注意把某个引脚设置为外部中断功能后,该引脚为输入模式,由于没有内部上拉电阻,所以必须外接一个上拉电阻,确保引脚不被悬空;除了引脚连接模块的设置,还需要设置VIC模块,才能产生外部中断,否则外部中断只能反映在EXTINT寄存器中;要使器件进入掉电模式并通过外部中断唤醒,软件应该正确设置引脚的外部中断功能,再进入掉电模式。

20.UART0的基本操作方法设置I/O连接到UART0;设置串口波特率(U0DLM、U0DLL);设置串口工作模式(U0LCR、U0FCR);发送或接收数据(U0THR、U0RBR);检查串口状态字或等待串口中断(U0LSR)。

21.I2C的基本操作方法I2C主机基本操作方法:设置I2C管脚连接;设置I2C时钟速率(I2SCLH、I2SCLL);设置为主机,并发送起始信号(I2CONSET的I2EN、STA位为1,AA位为0);发送从机地址(I2DAT),控制I2CONSET发送;判断总线状态(I2STAT),进行数据传输控制;发送结束信号(I2CONSET)。

I2C从机基本操作方法:设置I2C管脚连接;设置自身的从机地址(I2ADR);使能I2C(I2CONSET的I2EN、AA位为1);判断SI位或等待I2C中断,等待主机操作;判断总线状态I2STAT,进行数据传输控制。