采样保持电路

信号转换I-模拟开关采样保持电路概要

36

➢模拟开关中存储电容的性能要求

选用介质吸附效应小和泄漏电阻大的电容器,如聚 苯乙烯,钽电容和聚碳酸脂电容器等。

➢当电路从采样转到保持(充电结束时),介质的吸附 效应会使电容器上的电压下降,被保持的电压低于采样 转保持瞬间的输入电压; ➢开关接通时,电容放电,介质吸附效应会使放电后的 电容电压回升,引起小信号峰值的误差。 ➢电容器的泄漏电阻引起电容上的保持电压随时间逐渐 减小,降低保持精度

➢实际的场效应模拟开关模型

1 当闭合时,相当一个小电阻 (如DG403, RON<30欧姆)

2 当断开时,相当一个小的电容 (如DG403;约0.5PF)

3 当断开时,还存在一定量的泄漏电流 (DG403;<0.5NA)

35

MOS开关

MOS采样电路

采样模式时的等效电路

MOS开关在“开”状态,存在一定的电阻;

a)吸电流;b)拉电流

N沟道MOSFET的 Ron-ui特性

N沟道增强型MOSFET开关原理 当ui吸入电流时,ui端为S,uo为D; 当uo吸入电流时,uo端为S,ui为D;

Ron随ui不同而变化

31

➢P沟道增强型MOSFET开关(绝缘栅型)

VGS小于VT的绝对值, 场效应管不能导通。 P沟道增强型MOSFET衬底B接高电位才能正常工作 32

5

一、基本理论

6

如何实现采样和保持?

采样: 采集器必须与输入信号相连接,且不影响输入 信号;采样的信号是被采信号的“拷贝”。 保持:能储存信号(信号的存在是以能量来刻画) 能够存储能量的元件:电感和电容

通常电感体积大,价格高,在集成电路中制造较 困难,同时,电流的信号也很难处理,故较少使用。 通过分析,我们用一个开关和电容就可实现信号 的采样和保持。

采样保持电路名词解释,采样保持器作用是什么?一文给你讲清楚

采样保持电路名词解释,采样保持器作用是什么?一文给你讲清楚主要是关于:采样保持名词解释、采样保持电路工作原理、采样保持电路功能、采样保持电路作用以及采样保持电路设计。

一、采样保持名词解释采样保持电路从模拟输入信号中提取样本并将它们保持特定时间段,然后输出输入信号的采样部分。

采样保持电路仅适用于对几微秒的输入信号进行采样。

采样保持电路由开关器件、电容和运算放大器组成。

电容是采样和保持电路的核心,因为它是保持采样输入信号并根据命令输入将其提供到输出端的电路。

采样电路主要用于模数转换器,以消除输入信号中的某些变化,这些变化可能会破坏转换过程。

最简单的采样保持电路原理图如下图所示。

最简单的采样保持电路•Vs:输出信号•C:电•S:作为开关工作的 MOS 晶体管•Va:输入信号二、采样保持电路典型的采样保持电路框图如下:采样保持电路框图一般施加的输入电压信号是连续变化的模拟信号。

提供命令输入来触发输入信号的采样和保持。

命令输入只不过是一个开/关信号,用于开始/停止输入信号的采样,一般是PWM。

采样和保持过程取决于命令输入。

当开关闭合时,信号被采样,当它打开时,电路保持输出信号。

开关的开/关状态由指令输入控制。

时钟脉冲激活开关(S)。

根据时钟脉冲,输入信号被采样或保持为最近采样的值。

当时钟脉冲为高电平时对输入信号进行采样,并在时钟脉冲为低电平时保留这些值。

该电路可以在两种模式下工作,这取决于采样和保持时钟信号的逻辑电平。

时钟切换的输入脉冲和电路的输出如下图所示。

开关时钟脉冲和电路输出三、采样保持电路功能及工作原理采样保持电路的工作原理可以通过其组件的工作原理来简单理解。

构建采样保持电路的主要部件包括一个 N 沟道增强型 MOSFET、一个电容和一个高精度运算放大器。

作为开关元件,使用了 N 沟道增强型 MOSFET。

输入电压通过其漏极端子给出,控制电压也通过其栅极端子给出。

当施加控制电压的+ve 脉冲时,MOSFET将处于激活状态。

3.1、采样保持电路

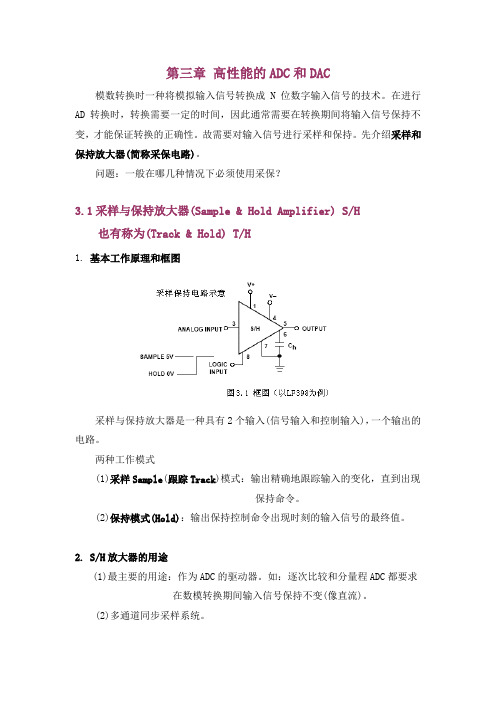

第三章高性能的ADC和DAC模数转换时一种将模拟输入信号转换成N位数字输入信号的技术。

在进行AD转换时,转换需要一定的时间,因此通常需要在转换期间将输入信号保持不变,才能保证转换的正确性。

故需要对输入信号进行采样和保持。

先介绍采样和保持放大器(简称采保电路)。

问题:一般在哪几种情况下必须使用采保?3.1采样与保持放大器(Sample & Hold Amplifier) S/H也有称为(Track & Hold) T/H1.基本工作原理和框图采样与保持放大器是一种具有2个输入(信号输入和控制输入),一个输出的电路。

两种工作模式(1)采样Sample(跟踪Track)模式:输出精确地跟踪输入的变化,直到出现保持命令。

(2)保持模式(Hold):输出保持控制命令出现时刻的输入信号的最终值。

2.S/H放大器的用途(1)最主要的用途:作为ADC的驱动器。

如:逐次比较和分量程ADC都要求在数模转换期间输入信号保持不变(像直流)。

(2)多通道同步采样系统。

(3)峰值检波器,延迟线。

3.S/H放大器的基本电路电路构成:四部分。

输入放大器A1,储能元件(保持电容,外接)C,输出缓冲器A2和开关驱动器(1)储能元件:是S/H放大器的心脏,其上的电压在保持期间要求基本不变,在采样期间要能精确跟踪输入信号的变化。

(2)输入放大器:要求具有高输入阻抗,以减少对前级影响。

其输出可作为一个低输出阻抗的信号源,用来对保持电容充电。

(3)输出放大器:要求其输入阻抗极高,以减少保持期间对保持电容的放电。

(4)开关驱动器:用来切换两种工作模式。

要求导通时开关内阻小,关断时阻抗大。

保持电容的容值:大,利于保持不利于跟踪;小,利于跟踪不利于保持;4.S/H放大器的技术指标分两种模式来讨论技术指标,分为静态和动态两类。

(1)跟踪模式(和普通的放大器一样)1)失调:对零输入,输出随时间和温度对零点的偏移。

2)非线性:输出作为输入的函数,该曲线对理想直线的偏差,一般用满标度的百分数表示。

简述mos采样保持电路

简述mos采样保持电路英文回答:MOS Sampling and Hold Circuit.A MOS sampling and hold circuit (S/H) is an analog circuit that captures and holds a voltage signal at a specific point in time. It is commonly used in signal processing applications where a signal needs to be held constant for дальнейшая обработка.The basic operation of a MOS S/H circuit involves two main stages:1. Sampling: During the sampling phase, a switch (typically a MOSFET) is closed, connecting the input signal to a capacitor. The capacitor rapidly charges to the voltage level of the input signal.2. Holding: Once the sampling phase is complete, theswitch is opened, disconnecting the capacitor from the input signal. The capacitor retains the stored voltage, effectively "holding" the signal at that instant.中文回答:MOS采样保持电路。

MOS采样保持电路(S/H)是一种模拟电路,它可以在特定的时间点捕捉并保持电压信号。

采样保持电路(一)

采样保持电路(一)

采样保持电路(采样/保持器)又称为采样保持放大器。

当对模拟信号进行A/D转换时,需要一定的转换时间,在这个转换时间内,模拟信号要保持基本不变,这样才能保证转换精度。

采样保持电路即为实现这种功能的电路。

一、基本原理

在输入逻辑电平控制下出于“采样”或“保持”两种工作状态。

“采样”状态下电路的输出跟踪输入模拟信号,在“保持”状态下电路的输出保持前次采样结束时刻的瞬时输入模拟信号,直至进入下一次采样状态为止。

下图为采样/保持示意图:

最基本的采样/保持器由模拟开关、存储元件(保持电容)和缓冲放大器组成。

如下图:

当Vc为采样电平时,开关s导通,模拟信号Vi通过S向CH充电,输出电压Vo跟踪模拟信号的变化;当Vc为保持电平时,开关S 断开,输出电压Vo保持在模拟开关断开瞬间的输入信号值。

高输入阻抗的缓冲放大器的作用是把CH和负载隔离,否则保持阶段在CH上的

电荷会通过负载放掉,无法实现保持功能。

二、采样/保持器的基本结构

1、串联型

2、反馈型

3、电容校正型。

采样保持电路

➢ 在这种条件下,V1的漏电流大约减小两个数量级。

-E

V ui

R V1

∞

-

+

+N

uo

C

Uc

➢ 可见采用V1后能将V与存储电容C隔离, ➢ 一方面使V的漏电流不流经存储电容, ➢ 另一方面又有效地降低了V1的漏流,从而提高了存储电容的

保持精度。

二、采样保持实用电路

(2)电容校正方法 ➢ 应用补偿电容C1来减小开关漏电流及运算放大器偏

对采样保持电路的主要 要求:

基本原理

精度和速度,充电快、 放电慢

导通电阻、截止电 阻、延迟时间

∞

-

+Biblioteka ui+ N1

∞

-

S

+

+

C UC

为提高实际电路的精度 和速度,需同时从元件 和电路两方面着手解决。

uo

带宽,上升速 率、最大输出 电流和漂移

漏电流

输入阻抗、上升速 率、漂移

采样保持电路

基本原理

采样保持电路的主要性能指标: 捕捉时间:从发出采样指令的时刻起,到输出值达到

处于采样状态,等效电路如图。

Uc

R1

VD1

VD2 V2

C1

V1

∞

∞ -

R2

+

R3 V

-

+

+ N2

uo

ui

+ N1

C

二、采样保持实用电路

当Uc为高电平时:

Ron2

C1

等效电路如图。

∞

∞

-

-

Ron

+

uo

+

(完整)采样保持电路

采样-保持电路采样一保持(S/H )电路具有采集某一瞬间的模拟输入信号,并根据需要保持并输出 所采集的电压数值的功能。

S / H 电路广泛应用于多路快速数据检测系统。

采样一保持电路基本工作原理及性能1、S/H 电路基本工作原理S/H 电路的原理电路、电路符号及波形如图所示。

S/H 电路的原理电路、电路符号及波形 电路中,SW 为模拟电子开关,其状态由逻辑控制信号vc 控制.CH 为保持电容,其两端电压即为S/H 电路输出电压vo.当控制信号vc 为高电平“1”时,模拟电子开关SW 闭合S/H 电路进入采样状态,输入信号vs (t ) 迅速对CH 充电,vo (t )精确地跟踪输入信号;当vc 为低电平“0”时,SW 断开CH 立即停止充电S/H 电路进入保持状态,vo (t )保持SW 断开瞬间的输入信号电压值不变。

理想采样一保持特性如图(c ) 所示,其数学表达式为5(力Qc = T”,采样期)v s (t D )(玫=“0”,保持期)式中,to 为逻辑控制信号vc 从“1”变为“0”的时间。

实际的采样一保持电路,常需设置缓冲级把模拟开关SW/保持电容CH 与信号源及负载隔离开,以 提高采样一保持电路的性能.2、S/H 电路性能指标6)电路符号(。

)波弗S/H电路的主要性能指标有采样时间、断开时间;采样精度、保持精度等.(1)采样时间和断开时间S/H电路由保持状态变为采样状态,或由采样状态变为保持状态并不是瞬间完成,需要一定的时间。

从发出采样指令开始到输出信号达到所规定的误差范围内的数值为止,所需的时间称为采样时间(又称捕捉时间),一般为0。

1~10^$数量级。

从发出保持指令开始到模拟开关断开,输出稳定下来为止,所需的时间称为断开时间(又称孔径时间),一般为10〜150门$数量级.采样时间长,电路的跟踪特性差;断开时间长,电路的保持特性不好。

两者都限制了5 /H电路工作频率的提高,即限制了电路工作速度。

采样保持电路课程设计

采样保持电路课程设计一、课程目标知识目标:1. 学生能够理解采样保持电路的基本原理和电路构成,掌握其工作过程。

2. 学生能够运用采样保持电路的相关理论知识,分析并计算电路参数。

3. 学生了解采样保持电路在模拟信号处理中的应用及其重要性。

技能目标:1. 学生能够运用所学知识,设计简单的采样保持电路,并进行仿真实验。

2. 学生能够通过实验分析采样保持电路的性能,并提出优化方案。

3. 学生能够熟练使用相关仪器和软件进行电路测试和数据分析。

情感态度价值观目标:1. 学生培养对电子技术的兴趣,激发学习热情,增强实践操作的自信心。

2. 学生养成团队协作、沟通交流的良好习惯,提高解决问题的能力。

3. 学生认识到采样保持电路在科技发展中的重要作用,增强社会责任感和使命感。

课程性质分析:本课程为电子技术基础课程,通过理论教学和实验操作,使学生掌握采样保持电路的基本原理和应用。

学生特点分析:学生处于高中年级,具备一定的电子技术基础知识和实验操作能力,但需要进一步培养实践能力和创新思维。

教学要求:结合学生特点,注重理论与实践相结合,提高学生的动手能力,培养解决实际问题的能力。

在教学过程中,关注学生的个体差异,充分调动学生的积极性,引导他们主动参与课堂讨论和实验操作。

通过本课程的学习,使学生能够达到上述课程目标,为后续相关课程打下坚实基础。

二、教学内容1. 理论知识:- 采样保持电路的基本原理及其数学描述。

- 采样保持电路的电路构成和关键元件功能。

- 采样保持电路的工作过程和性能参数分析。

- 采样保持电路在模拟信号处理中的应用案例分析。

2. 实践操作:- 设计简单的采样保持电路,并进行仿真实验。

- 使用示波器、信号发生器等仪器进行电路测试。

- 分析实验数据,探讨采样保持电路性能的优化方法。

3. 教学大纲:- 第一课时:采样保持电路的基本原理及数学描述。

- 第二课时:采样保持电路的电路构成及关键元件功能。

- 第三课时:采样保持电路的工作过程及性能参数分析。

采样保持电路

3.3.2 放大电路实例

3、热电耦测量放大电路

由于热电偶Tc 的电压输出决定于热端与

冷端的温度差,理论上应使冷端温度为基 点即0℃,而实际上冷端温度通常为室温, 所以图中利用PN结的结电压随温度上升而 线性下降的特性来进行补偿。

3.3.2 放大电路实例

3、热电耦测量放大电路 热端每变化1℃,K型热电偶有40mV的电

3.4.1 DAC与微机接口的一般方法

1、8位DAC接口 典型的CPU系统与DAC的接口如下图所示:

图 3-21 8位DAC接口

3.4.1 DAC与微机接口的一般方法

1、8位DAC接口 通过74100锁存器把8位DAC连接到CPU系

统。 CPU把数字存入锁存器。 DAC把二进制数变换为输出电流。 741型集成运放把电流变换为0~1V的输出

的测温电路,如下图。输出电压Vo=10mV×t(t为测量温

度值),温度测量范围为-20℃~+100℃。

图3-7 温度传感器测温电路

3.2.2 传感器应用实例

2、 LM35系列电压输出式集成温度传感器 2)温度/频率变换电路

用V/F变换器LM131、集成温度传感器LM35或 LM45及光偶4N128,组成输入输出隔离的温度/ 频率变换电路,如图3-8。光偶还进行电平转换。

电压,该输出模拟电压与数字量成比例。

3.4.1 DAC与微机接口的一般方法

1、8位DAC接口 下列程序可产生一个线性增加的斜波电压。

MOV SP,#53H

CLR A

MOV R1,#17H LOOP: MOVX @R1,A

ACALL DELAY

INC A

AJMP LOOP

DELAY: …

采样保持电路

采样保持电路

采样保持电路常用于输入信号变化较快或具有多路输入信号的数据采集系统中,也可用于其它一切要求对信号进行瞬时采样和存储的场合。

在A/D转换过程中,因为每次转换过程需要一定的时间,所以需要采样保持电路的配合,以便有一个稳定的采集量。

采样保持器的工作过程由外部控制信号来决定,工作过程分“采样”和“保持”两个周期。

“采样”就是要求输出信号能快速而准确地跟随信号的变化;而“保持” 则是在两次采样间隔时间内保持上一次采样结束时的状态。

采样保持电路工作原理图如上图所示,其主要由场效应管T,电容C、电阻R和运放组成。

工作原理:在采样过程中,控制信号L为高电平,场效应管相当于一个开关导通,输入电压迅速对电容C充电,此时充电电阻很小〔近似为0〕,电容电压与输入电压ui相等,经过运放电压跟随器输出到输出端uo。

在保持过程中,L为低电平,场效应管关断,电容电荷没有放电回路〔运放输入电阻为无穷大〕。

因此输出电压uo就保持在场效应管关断时的输入电压值不变。

采样保持电路

采样保持电路基本知识1、采样保持电路原理采样保持电路能够跟踪或者保持输入模拟信号的电平值。

在理想状况下,当处于采样状态时,采样保持电路的输出信号跟随输入信号变化而变化;当处于保持状态时,采样保持电路的输出信号保持为接到保持命令的瞬间的输入信号电平值。

一个典型的米样保持电路模型如图1所示图1采样保持电路基本模型当电路处于采样状态时开关导通,这时电容充电,如果电容值很小,电容可以在很短的时间内完成充放电,这时,输出端输出信号跟随输入信号的变化而变化;当电路处于保持状态时开关断开,这是由于开关断开,以及集成运放的输入端呈高阻状态,电容放电缓慢,由于电容一端接由集成运放构成的信号跟随电路,所以输出信号基本保持为断开瞬间的信号电平值。

2、采样保持电路的主要技术指标采样保持电路有采样和保持两种工作状态,这两种工作状态对于电路的性能,整个A/D转换部分性能都有很大的影响。

在这两种不同的模式下,电路的特点也有一定的差别,下面根据采样保持电路两种不同的工作状态来分析其主要技术指标。

2.1采样状态下的主要技术指标偏移电压,是指在采样模式下,当输入端电压为零时,输出端的输出电压值。

为了保证A/D转化芯片能够准确地采样,偏移电压的值应当满足Vof<Vfs/2^(n+1)其中,Vof为偏移电压,Vfs为A/D芯片的满量程电压,n为A/D芯片的位数。

最大变化频率,是指在采样模式下,输出电压最高的变化频率。

这个频率值受到保持电容容值大小的影响,对系统的工作频率有一定的限制作用。

2.2保持状态下的主要技术指标降压速率,是指在保持模式下,输出端的输出电压值随输入时间变化的速率。

降压速率满足:dVc/dt = Ic/Ch其中,Vc为电容两端的电压值,Ic为流经电容的电流值,Ch为保持电容的容值。

馈通衰减量,是指在保持模式下,输入信号的电压值到经过采样保持电路后,在输出端输出时的减少量。

为了使A/D芯片能够准确地采样出信号,馈通衰减量小于A/D芯片的最低有效位LSB的1/2。

采样保持电路原理(S-H)

采样保持电路原理(S-H)

采样保持电路原理(S/H)

采样保持电路(S/H)原理

A/D转换需要一定时间,在转换过程中,如果送给ADC的模拟量发生变化,则不能保证精度。

为此,在ADC前加入采样保持电路,如图8-30所示。

采样保持电路有两种工作状态:采样状态和保持状态。

采样状态:控制开关K闭合,输出跟随输入变化。

保持状态:

ADC1210是无三态输出锁存功能的A/D转换器,如图8-28所示,是12位逐次逼近式ADC,转换时间100微秒。

它的数据线不能与系统数据总线直接连接,必须通过两个具有三态锁存能力的74LS244接到数据总线上,如图8-29所示。

其中:

D11~D0:数据输出线。

数据结果为二进制反码。

输出有锁存, 但无三态功能à 接口电路中应加三态缓冲器(用74LS244)。

SC: 启动信号。

脉冲启动,要求SC的宽度等于时钟周期,用“与非门RS触发器”保证与时钟信号同步。

CC: 转换结束信号。

低电平有效,它一直持续到下次启动转换为止。

.ADC570概述。

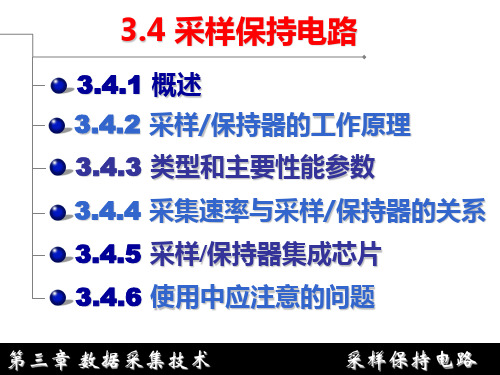

3.4 采样保持电路解析

第三章 数据采集技术

采样保持电路

3.4.3 采样/保持器的类型和主要性能参数

1. 采样/保持器的类型

按结构分为两种类型:

串联型采样/保持器

UK A1 K + A2 UO

Ui

+

CH

模拟地

串联型采样/保持器的结构

A1和A2分别是输入和输出缓冲放大器,用以提高采样/保 持器的输入阻抗,减小输出阻抗,以便与信号源和负载连 接。

第三章 数据采集技术

采样保持电路

3.4.3 采样/保持器的类型和主要性能参 数

1. 采样/保持器的类型

按结构分为两种类型:

串联型采样/保持器 优点:结构简单。

缺点: 其失调电压为两个运放失调电 压之和,比较大,影响到采样 /保持器的精度。 跟踪速度也较低。

第三章 数据采集技术

采样保持电路

电容CH对精度的影响:

如果电容值过大,则其时间常数大,当模拟信号频 率高时,由于电容充放电时间长,将会影响电容对 在选择电容时,容量大小要适宜,以保证其时间常 输入信号的跟踪特性,而且在跟踪的瞬间,电容两 数适中,并选用泄露小的电容。 端的电压会与输入信号电压有一定的误差。 另外,一般在输入端和输出端均采用缓冲器,以减 如果电容值过小,在保持状态时,由于电容漏电流 少信号源的输出阻抗,增加负载的输入阻抗。 的存在或者负载内阻太小的影响,会引起保持信号 电平的变化。

第三章 数据采集技术

采样保持电路

3.4.3 采样/保持器的类型和主要性能参数

1. 采样/保持器的类型

按结构分为两种类型:

串联型采样/保持器

UK A1 K + A2 UO

Ui

+

采样保持电路

一、米样保持电路的引入在A/D转换期间,为了使输入信号不变,保持在开始转换时的值,通常要采用一个采样保持电路。

对于MCS-96单片机的A/D转换器,启动转换实际上是把采样开关接通,进行采样,过一段时间后,开关断开,采样电路进入保持模式,才是A/D真正开始转换二、采样保持电路的原理A/D转换需要一定时间,在转换过程中,如果送给ADC的模拟量发生变化,则不能保证精度。

为此,在ADC前加入采样保持电路,如图下所示。

采样保持电路有两种工作状态:采样状态和保持状态。

1、采样状态:控制开关K闭合,输出跟随输入变化2、保持状态:控制开关K断开,由保持电容C维持该电路的输出不变运算放大器A2:典型的跟随器接法。

输入阻抗:高阻。

保持状态(K分)下Ch放电小,保持电压不变。

输出阻抗:小。

采样保持电路的负载能力大。

运算放大器A1:K闭合时为跟随器。

(不关心K断开的情况)。

输入阻抗:高阻。

对输入信号的负载能力要求小。

输出阻抗:小。

采样状态时,Ch上的电压快速跟随输入变化。

控制开关K:由接口电路控制。

、采样采样脉冲的频率由下图可知,采样脉冲的频率fs (fs =1/T s )越高,采样越密,采样值越多,采样信号的包络线越接近输入信号的波形•假设输入信号的最高频率为fm ,则根据采样定理知:当采样频率fs> 2 fm时,采样信号可正确反映输入信号。

JU圈2. 30 采样/保持电路的输岀蹟输入变化的波形as 通常对直流或缓变低频信号进行采样时可不用采样保持电路、加入S/H后模/数转换控制过程加入S/H后,整个模/数转换过程如下图所示1、C PU S接口电路使K闭合(启动采样)。

2、C PU S接口电路使K断开(保持)。

(*)3、C PU向ADC发出启动转换信号(转换或称量化)。

(*)4、查询A/D转换完成否,或使用中断方式。

5、读取转换后的数字。

6在实际硬件设计中,一般第②、③步设计为用一条指令完成。

四、多路转换模拟开关1、原理由于计算机在任一时刻只能接收一路模拟量信号的采集输入,当有多路模拟量信号时需通过模拟转换开关,按一定顺序选取其中一路进行采集。

采样保持电路的作用及原理

采样保持电路的作用及原理采样保持电路是一种电子电路,用于将输入信号的瞬时值保持在输出上,同时与输入信号进行隔离。

它在模拟信号处理中起到重要的作用。

采样保持电路可以用于多种应用,如模数转换、信号处理、时间测量、测试仪器等。

采样保持电路的原理是通过一个开关控制输入信号的采样和保持。

当开关打开时,输入信号从采样电容器通过输入放大器传输到输出电路。

当开关关闭时,输入信号被“冻结”在采样电容器中,以便输出电路可以准确地采样和测量信号的瞬时值。

开关控制脉冲的频率通常是一个固定频率的电平,由时钟信号提供。

采样保持电路通常由以下几个主要组成部分构成:1. 采样开关:负责在特定时间对输入信号进行采样,并将其存储在采样电容器中。

2. 采样电容器:用于存储输入信号的电容器。

它的大小必须足够大,以便在保持期间能够存储足够的电荷。

3. 输入放大器:放大采样信号并将其输出到输出电路。

4. 保持开关:在输入信号被采样并存储在采样电容器之后,保持开关控制输入信号的输出,以便输出电路进行测量和处理。

5. 控制电路:负责控制开关的开关时间以及输入和输出信号之间的切换。

当采样保持电路开始工作时,采样开关打开,允许输入信号通过输入放大器进入采样电容器。

在一定的时间内,采样电容器会收集并储存输入信号。

然后,保持开关关闭,阻止输入信号进入采样电容器。

保持期间,输出电路可以测量和处理采样电容器中存储的信号。

采样保持电路的作用主要有以下几个方面:1. 信号测量:采样保持电路可以用于模拟信号的精确测量,测量过程中可以保持信号的瞬时值,避免信号在测量过程中发生变化。

2. 信号处理:采样保持电路可以将输入信号的瞬时值保持在输出上,使得后续的信号处理电路可以准确处理采样到的信号。

3. 信号传输:采样保持电路可以实现输入信号和输出信号之间的隔离,防止输入信号对输出信号产生干扰。

4. 下变频率转换:采样保持电路可以将高频模拟信号转换为低频模拟信号,以便于后续数字处理或其他应用。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

一、采样保持电路结构的选择

常见的采样保持结构有以下两种:

图1、电荷传输型采样保持电路

图2、电容翻转型采样保持电路

图3、图1,图2所用的时钟信号工作原理:一、电荷传输型采样保持电路

首先Φ1、Φ1’为高电平,采样电容CS 对输入信号进行采样,然后Φ1’比Φ1提前0.4ns 进入下降沿,此时x 点为高阻状态,故当Φ1变为低电平,即ks1开关关断时,x 点不再导通,即抑制了开关ks1的电荷注入效应。

当Φ2为高电平的时候,Φ1、Φ1’此时为低电平,电路进入保持状体。

CS 上的差分电荷就传到了Cf 上,此时差分输出电压即为差分输入电压(CS=Cf )。

二、电容翻转型采样保持电路

首先Φ1、Φ1’为高电平,采样电容CS 对输入信号进行采样,然后Φ1’比Φ1提前0.4ns 进入下降沿,此时x 点为高阻状态,故当Φ1变为低电平,即ks1开关关断时,x 点不再导通,即抑制了开关ks1的电荷注入效应。

当Φ2为高定平时,采样电容C 的左端接放大器的输出端,因为输出共模电平等于输入共模电平,所以采样保持电路的输出等于采样保持电路的输入。

对两种结构进行对比。

1、 所需放大器的带宽。

为简化分析我们将其简化为单极点系统,则放大器的传输函数为:

()1A A S s

ω=

+ (1)

式中:A 表示低频增益,0ω为3dB 带宽。

将放大器接成闭环后,其闭环传输函数为:

00

/(1/)/(1)

()1/(1)11/A s A fA Ac S Af s fA s ωωω++=

=+++

+ (2) 其中f 为反馈系数。

则该闭环系统的时间常数为: τ=01/fA ω= 1/n f ω (3) 其中n ω为运放的单位增益带宽

对于单位阶跃输入信号,闭环系统输出阶跃响应为: Vout (t )= /1(1)()t e u t f

-τ- (4)

同样我们要求输出的误差必须小于1/2LSB ,得

/t e -τ<

1

12N + (5)

从(3)、(5)我们可得

11

ln 2N n p

ft ω+>

(6) 其中p t 为信号建立时间,大约为3/8T 。

在电荷传输型的采样结构中,理想情况下f=Cf/(CS+Cf)=1/2;而在电容翻转型结构中f=1:;故从(6)式可以看出电荷传输型的采样结构中所需运放的带宽是电容翻转型结构所需运放带宽的2倍。

2、 噪声

电荷传输型采样保持电路的噪声为2KT/C,电容翻转型采样保持电路的噪声为KT/C (A 3-V 340-mW 14-b 75-Msample/s CMOS ADC With 85-dB SFDR at Nyquist Input ),而噪声的大小决定了我们采样电容的大小,采样电容的增大会增加放大器的负载电容,同样会增大功耗。

3、输入范围

电容翻转型采样保持电路要求输入共模电压和输出共模电压必须相同,故电容翻转型所需放大器应有较大的输入范围,在此应该是1.15V—2.15V的输入范围。

而电荷传输型在保持时传输仅仅是差分信号电荷,故输入共模电压可以与输出共模电压不同。

根据以上三点比较我们选择电容翻转型采样保持电路。

二、采样保持电路参数的计算

1、精度(resolution)

规定此采样保持用在精度为12位的ADC上。

2、采样速率(conversion rate)

规定此采样保持电路用在采样速率为50MHZ的ADC上

3、输入范围(Input range)

采样保持电路的单端输入范围:

VINp(max)—VINn(min)=2.15-1.15=1V

所以全差分输入范围为-1V到1V,即2Vpp(其中Vpp为单端输入峰峰值)。

4、输出摆幅(output range)

因为输出跟随输入,故此采样保持电路输出范围亦为-1V—1V,即2Vpp

5、SNDR(信噪失真比)

模数转换器的实际有效位数是根据信噪失真比得到的,其关系式为:

有效位数ENOB=(SNDR—1.76dB)/6.02dB (1)nnn

SNDR=6.02ENOB+1.76 (2)

若要取得12位的有效位,将ENOB=12带入式(2)得

SNDR=74dB

但是实际中并不可能达到12位的有效位,我们如果按照11位的有效位进行计算,则SNDR=67.98dB。

6、INL/DNL(积分非线性/微分非线性)

当DNL>1LSB时,就会出现丟码,所以DNL必须小于±1LSB。

如果INL的最大值大于1LSB则在此处就会出现一个误码,所以INL 同样小于<±1LSB。

7、无杂散动态范围

SFDR=20log(2/)

N INL

(其中INL用LSB表示),在此我们假设

INL=1LSB,则SFDR=72dB

故我们的具体设计指标如下表所示

表一、采样保持电路的参数

三、采样保持电路中放大器相关参数的计算及结构的选取。

1、相关参数的计算 (1)负载电容

(1)_Cleff f Cs Cs next Cout Ccom Ccmfb =-++++(1)lian

在采样保持电路中开关的噪声必须小于量化噪声,故

KT/C<2

(

)/1221N

FS -整理得:

22122N KT C FS •>

其中FS=1V

解得C>0.87pF ,在此我们取Cs=1.2pF

所以(1)式中采样电容Cs=1.2pF ,Cout 为运放输出的寄生电容,在此取Cout=0.2pF ,Ccom 为比较器电容,在此我们也取0.2pF ,Ccmfb 为共模反馈电路的寄生电容,我们在此取0.2pF ,Ccom 为比较器的寄生电容,我们在此取0.2pF,Cs_next 为下一级MDAC 的采样电容,我们也取1.2pF ,f 为反馈系数,f=Cs/(Cs+Cp),其中Cp 为运放的输入寄生电容在此我们取Cp=0.5pF ,整个代入式(1),得 Cleff=2.4pF (2)直流增益

放大器的增益误差必须小于1/2LSB ,即

1

011

12

N fA +≤+

将f=0.7,N=12代入解得: A 0>81.4dB

在此我们取A 0=82dB (3)压摆率 SR=Vpp/2Tslew

其中Vpp 为单端输出峰峰值,即Vpp=1V ,Tslew=1/6T ,为留有一定裕度,在此我们按采样速率为60MHZ 进行计算,即Tslew=1/8(1/60M)=2ns ,代入得 SR=500V/us

所以放大器的尾电流为 Iss=SR*Cleff=1.2mA (4)单位增益带宽 由第三页的公式(6)11

ln 2N n p

ft ω+>

其中t p=2/6T=5ns,代入可得: 单位增益带宽

n

ω>260MHZ (?)

所以运放的参数如下表所示:

差分输入范围2V(2Vpp)

共模输入范围 1.15V—2.15V

负载电容 2.4pF

直流增益>82dB

压摆率>500V/us

单位增益带宽>260MHZ

问题1、对于采样保持电路中的参数SNDR

在A 3-V 340-mW 14-b 75-Msample/s CMOS ADC With 85-dB SFDR at Nyquist Input(solid—state)

在这篇文章中其同样运用了电容翻转式的采样保持电路,如下图所示下图为其所用的放大器

其SNR=73dB,由第四页的式(1)ENOB=(SNDR—1.76dB)/6.02dB 得其有效位为11.8,所以我不知道我在参数设置时,规定SNDR的目

标参数为67dB.。