单片采样保持电路

ad9653工作原理

ad9653工作原理AD9653是一个高速,高精度,低功耗的12位模数转换器(ADC),采用混合信号设计技术,通过使用单片形式整合了12位模数转换器和采样保持电路。

它适用于广泛的应用,包括通信、测量仪器、医疗设备和工业控制等领域。

AD9653采用了先进的Nyquist架构,它基于折叠和增益校准技术,可以提供卓越的动态性能和高抗混叠性能。

该芯片具备高达3.6 GSPS的采样速率和70 dB的SNR(信噪比),并支持宽带接收。

此外,AD9653采用并行数据接口,可以同时输出12位的模数转换结果。

这使得它可以直接与高速数据采集、处理和存储系统配合使用。

AD9653的工作原理可以分为以下几个关键步骤:1.采样:AD9653通过内部的采样保持电路和模数转换器单元进行采样。

采样保持电路能够将输入信号的电压进行保持,并保持一段时间供模数转换器进行转换。

这样可以避免由于采样过程中的信号变化引起的数据失真。

采样保持电路的性能对AD9653的动态性能有着重要的影响。

2.模数转换:AD9653采用了12位的模数转换器单元对采样结果进行模数转换。

模数转换器使用了电流模式的架构,采用了积分非特权的操作方式来实现高速和高精度的转换。

它以一定的速率对保持电路中的电压进行积分,然后将积分结果进行量化并输出对应的二进制码。

3.数据输出:AD9653的模数转换结果通过并行数据接口输出。

接口采用了高速差分信号传输,以确保在高速数据传输中的信号完整性和抗干扰性能。

通过并行接口,AD9653可以同时输出12位的模数转换结果,以满足应用系统对高数据速率的需求。

4.精度和校准:为了提供高精度的模数转换性能,AD9653采用了多种校准技术。

其中包括增益和功率校准技术,可以校准误差引起的增益和偏压。

这些校准技术能够提供高精度和稳定的模数转换结果,从而提高整个系统的性能。

总之,AD9653是一款高性能的12位模数转换器,采用了混合信号设计技术,通过采样、模数转换和数据输出等步骤实现对输入信号的转换。

采样保持电路

一、采样保持电路结构的选择常见的采样保持结构有以下两种:图1、电荷传输型采样保持电路图2、电容翻转型采样保持电路图3、图1,图2所用的时钟信号工作原理:一、电荷传输型采样保持电路首先Φ1、Φ1’为高电平,采样电容CS 对输入信号进行采样,然后Φ1’比Φ1提前0.4ns 进入下降沿,此时x 点为高阻状态,故当Φ1变为低电平,即ks1开关关断时,x 点不再导通,即抑制了开关ks1的电荷注入效应。

当Φ2为高电平的时候,Φ1、Φ1’此时为低电平,电路进入保持状体。

CS 上的差分电荷就传到了Cf 上,此时差分输出电压即为差分输入电压(CS=Cf )。

二、电容翻转型采样保持电路首先Φ1、Φ1’为高电平,采样电容CS 对输入信号进行采样,然后Φ1’比Φ1提前0.4ns 进入下降沿,此时x 点为高阻状态,故当Φ1变为低电平,即ks1开关关断时,x 点不再导通,即抑制了开关ks1的电荷注入效应。

当Φ2为高定平时,采样电容C 的左端接放大器的输出端,因为输出共模电平等于输入共模电平,所以采样保持电路的输出等于采样保持电路的输入。

对两种结构进行对比。

1、 所需放大器的带宽。

为简化分析我们将其简化为单极点系统,则放大器的传输函数为:()1A A S sω=+ (1)式中:A 表示低频增益,0ω为3dB 带宽。

将放大器接成闭环后,其闭环传输函数为:00/(1/)/(1)()1/(1)11/A s A fA Ac S Af s fA s ωωω++==++++ (2) 其中f 为反馈系数。

则该闭环系统的时间常数为: τ=01/fA ω= 1/n f ω (3) 其中n ω为运放的单位增益带宽对于单位阶跃输入信号,闭环系统输出阶跃响应为: Vout (t )= /1(1)()t e u t f-τ- (4)同样我们要求输出的误差必须小于1/2LSB ,得/t e -τ<112N + (5)从(3)、(5)我们可得11ln 2N n pft ω+>(6) 其中p t 为信号建立时间,大约为3/8T 。

采样保持电路原理(S-H)

采样保持电路原理(S/H)

采样保持电路(S/H)原理

A/D转换需要一定时间,在转换过程中,如果送给ADC的模拟量发生变化,则不能保证精度。

为此,在ADC前加入采样保持电路,如图8-30所示。

采样保持电路有两种工作状态:采样状态和保持状态。

采样状态:控制开关K闭合,输出跟随输入变化。

保持状态:

ADC1210是无三态输出锁存功能的A/D转换器,如图8-28所示,是12位逐次逼近式ADC,转换时间100微秒。

它的数据线不能与系统数据总线直接连接,必须通过两个具有三态锁存能力的74LS244接到数据总线上,如图8-29所示。

其中:

D11~D0:数据输出线。

数据结果为二进制反码。

输出有锁存, 但无三态功能à 接口电路中应加三态缓冲器(用74LS244)。

SC: 启动信号。

脉冲启动,要求SC的宽度等于时钟周期,用“与非门RS触发器”保证与时钟信号同步。

CC: 转换结束信号。

低电平有效,它一直持续到下次启动转换为止。

.ADC570概述。

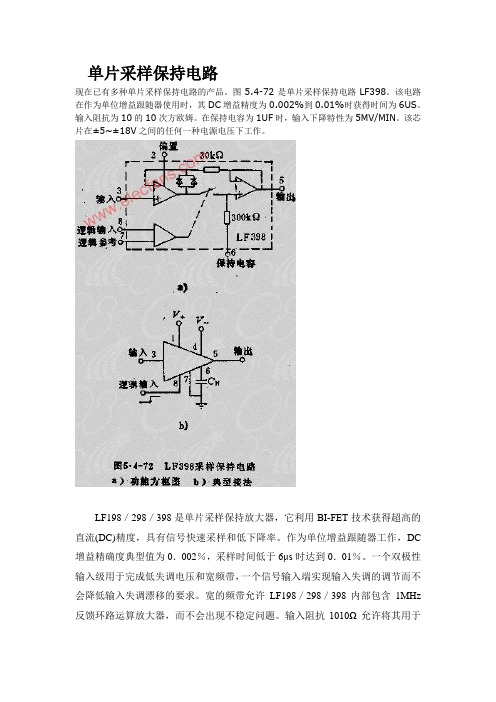

单片采样保持电路

单片采样保持电路现在已有多种单片采样保持电路的产品。

图5.4-72是单片采样保持电路LF398。

该电路在作为单位增益跟随器使用时,其DC增益精度为0.002%到0.01%时获得时间为6US。

输入阻抗为10的10次方欧姆。

在保持电容为1UF时,输入下降特性为5MV/MIN。

该芯片在±5~±18V之间的任何一种电源电压下工作。

LF198/298/398是单片采样保持放大器,它利用BI-FET技术获得超高的直流(DC)精度,具有信号快速采样和低下降率。

作为单位增益跟随器工作,DC增益精确度典型值为0.002%,采样时间低于6μs时达到0.01%。

一个双极性输入级用于完成低失调电压和宽频带,一个信号输入端实现输入失调的调节而不会降低输入失调漂移的要求。

宽的频带允许LF198/298/398内部包含1MHz反馈环路运算放大器,而不会出现不稳定问题。

输入阻抗1010Ω允许将其用于高阻信号源而不会降低精度。

在输出放大器中采用P沟道结型场效应管(JFET)与双极性器件结合,用一个1μF保持电容器时可获得5mV/分钟的低下降率。

JFET与早期设计使用的MOS器件相比噪声低得多,并且高温稳定性好。

整个芯片设计确保在保持模式下,不存在从输入到输出的直通,即使在信号等于电源电压时也是如此。

LF198/298/398逻辑输入端是具有低输入电流的完全差分输入,允许直接连接TTL、PMOS、CMOS信号电平,差分阈值为1.4V。

LF198/298/398及LF198A/398A等的引脚排列如图所示。

采样时间为20US的中速采样和保持电路功能及原理分析电路的功能所谓采样和保持电路,就是以任意时间取出不断变化的模拟信号,并将其电压加以保持的电路,把该电路作为A-D变换器的前级,固定变换中的模拟电压,取出瞬时值,这样使用速度较低的A-D变换器,也能处理变化速度快的信号。

此外使采样信号与基准相们同步,即可实现采样同步检波以低纹波整流超低频信号。

单片机ADC DAC模数转换原理及应用

单片机ADC DAC模数转换原理及应用单片机是一种集成电路,拥有微处理器、内存和输入输出设备等多个功能模块。

其中,ADC(Analog-to-Digital Converter,模数转换器)和DAC(Digital-to-Analog Converter,数模转换器)模块是单片机中非常重要的功能模块。

本文将介绍单片机ADC DAC模数转换原理以及其应用。

一、ADC模数转换原理ADC模数转换器负责将连续变化的模拟信号转换为相应的数字信号。

其基本原理是通过对连续模拟信号进行采样,然后将采样值转换为离散的数字信号。

ADC一般包括采样保持电路、量化电路和编码电路。

1. 采样保持电路采样保持电路主要用于对输入信号进行持久采样。

当外部输入信号经过开关控制后,先通过采样保持电路进行存储,然后再对存储的信号进行采样和转换,以确保准确性和稳定性。

2. 量化电路量化电路根据模拟信号的幅值幅度进行离散化处理。

它将连续的模拟信号分为若干个离散的电平,然后对每个电平进行精确的表示。

量化电路的精度越高,转换的数字信号越准确。

3. 编码电路编码电路将量化电路输出的离散信号转换为相应的二进制码。

通常使用二进制编码表示,其中每个量化电平都对应一个二进制码。

编码电路将模拟信号通过ADC转换为数字信号,供单片机进行处理。

二、DAC数模转换原理DAC数模转换器是将数字信号转换为相应的模拟信号,用于将单片机处理的数字信号转换为可用于模拟环境的连续变化的模拟信号。

DAC的基本原理是通过数模转换,将离散的数字信号转换为连续变化的模拟信号。

1. 数字输入DAC的数字输入是单片机输出的数字信号,通常为二进制码。

数字输入信号决定了模拟输出信号的幅值大小。

2. 数模转换电路数模转换电路将数字输入信号转换为相应的模拟信号。

它根据数字输入信号的二进制码选择合适的电平输出,通过电流或电压形式输出连续变化的模拟信号。

3. 滤波电路滤波电路用于过滤数模转换电路输出的模拟信号,以确保输出信号的质量。

采样保持电路

一、采样保持电路的引入在A/D转换期间,为了使输入信号不变,保持在开始转换时的值,通常要采用一个采样保持电路。

对于MCS-96单片机的A/D转换器,启动转换实际上是把采样开关接通,进行采样,过一段时间后,开关断开,采样电路进入保持模式,才是A/D真正开始转换二、采样保持电路的原理A/D转换需要一定时间,在转换过程中,如果送给ADC的模拟量发生变化,则不能保证精度。

为此,在ADC前加入采样保持电路,如图下所示。

采样保持电路有两种工作状态:采样状态和保持状态。

1、采样状态:控制开关K闭合,输出跟随输入变化。

2、保持状态:控制开关K断开,由保持电容C维持该电路的输出不变。

运算放大器A2:典型的跟随器接法。

输入阻抗:高阻。

保持状态(K分)下Ch放电小,保持电压不变。

输出阻抗:小。

采样保持电路的负载能力大。

运算放大器A1:K闭合时为跟随器。

(不关心K断开的情况)。

输入阻抗:高阻。

对输入信号的负载能力要求小。

输出阻抗:小。

采样状态时,Ch上的电压快速跟随输入变化。

控制开关K:由接口电路控制。

三、采样采样脉冲的频率由下图可知,采样脉冲的频率fs(fs=1/Ts)越高,采样越密,采样值越多,采样信号的包络线越接近输入信号的波形.假设输入信号的最高频率为fm,则根据采样定理知:当采样频率fs>2fm时,采样信号可正确反映输入信号。

通常对直流或缓变低频信号进行采样时可不用采样保持电路。

三、加入S/H后模/数转换控制过程加入S/H后,整个模/数转换过程如下图所示。

1、CPU经接口电路使K闭合(启动采样)。

2、CPU经接口电路使K断开(保持)。

(*)3、CPU向ADC发出启动转换信号(转换或称量化)。

(*)4、查询A/D转换完成否,或使用中断方式。

5、读取转换后的数字。

6、在实际硬件设计中,一般第②、③步设计为用一条指令完成。

四、多路转换模拟开关1、原理由于计算机在任一时刻只能接收一路模拟量信号的采集输入,当有多路模拟量信号时需通过模拟转换开关,按一定顺序选取其中一路进行采集。

3.1、采样保持电路

第三章高性能的ADC和DAC模数转换时一种将模拟输入信号转换成N位数字输入信号的技术。

在进行AD转换时通常需要输入信号保持不变,才能保证转换的正确性。

因此需要对输入信号进行采样和保持。

先介绍采样和保持放大器(简称采保)。

问题:一般在哪几种情况下必须使用采保?3.1采样与保持放大器(Sample & Hold Amplifier)1.框图采样与保持放大器是一种具有2个输入(信号输入和控制输入),一个输出的电路。

两种工作模式(1)采样Sample(跟踪Track)模式:输出精确地跟踪输入的变化,直到出现保持命令。

(2)保持模式(Hold):输出保持控制命令出现时刻的输入信号的最终值。

2.S/H放大器的用途(1)最主要的用途:作为ADC的驱动器。

如:逐次比较和分量程ADC都要求在数模转换期间输入信号保持不变(像直流)。

(2)多通道同步采样系统。

(3)峰值检波器,延迟线。

3.S/H放大器的基本电路电路构成:四部分。

输入放大器A1,储能元件(保持电容,外接)C,输出缓冲器A2和开关驱动器(1)储能元件:是S/H放大器的心脏,其上的电压在保持期间要求基本不变,在采样期间要能精确跟踪输入信号的变化。

(2)输入放大器:要求具有高输入阻抗,以减少对前级影响。

其输出可作为一个低输出阻抗的信号源,用来对保持电容充电。

(3)输出放大器:要求其输入阻抗极高,以减少保持期间对保持电容的放电。

(4)开关驱动器:用来切换两种工作模式。

要求导通时开关内阻小,关断时阻抗大。

保持电容的容值:大,利于保持不利于跟踪;小,利于跟踪不利于保持;4.S/H放大器的技术指标分两种模式来讨论技术指标,分为静态和动态两类。

(1)跟踪模式(和普通的放大器一样)1)失调:对零输入,输出随时间和温度对零点的偏移。

2)非线性:输出作为输入的函数,该曲线对理想直线的偏差,一般用满标度的百分数表示。

3)增益:输入到输出的直流传递函数的值。

4)调整时间:输入为满标度阶跃信号时输出达到规定的满标度范围内所要求的时间(也称为:acquisition time)。

采样保持器 AD783应用电路

AD783的电路1、AD783高速采样保持放大器简介AD783是高速单片采样保持放大器(SHA),提供典型250ns采样时间达到0.01%,在最高输入频率100kHz时规定和测试保持模式总谐波失真。

AD783的基本特点与AD781相同。

AD783采用模拟器件公司的ABCMOS制造工艺,ABCMOS工艺综合了高性能、低噪声双极性电路和低功率CMOS逻辑,提供一个精确、高速和低功率的SHA。

AD783有J级、A级、S级3个温度等级,其引脚排列如图所示。

2、采样保持放大器AD783与AD670的接口电路如图所示为由AD783与低成本信号调节8位A/D转换器AD670构成的接口电路。

由于AD783具有15MHz小信号带宽,因此可以将其用于低于这个频率的信号采集的应用场合。

该电路输入信号为载波10.7MHz中频信号(IF),中频信号采用移频键控调制方式(FSK),调制信号频率为5kHz。

“时钟输入”直接接到AD783的S/H脚,向采样保持放大器发出采样或保持命令,AD783输出保持信号,送到8位A/D转换器AD670,由AD670将模拟信号转换为8位数字信号输出。

“时钟输入”经过单稳(ONE-SHOT)延迟10μs后加到AD670的R/W端(21脚),延迟的目的在于适应AD783保持模式150ns的建立时间,因此整个系统的传输时间为10.15μs。

输入信号为载波10.7MHz中频信号(IF)的全幅度范围为255mV,在此基础上变换器AD670有全8位的动态范围。

AD670的最大采样率为10μs,因此符合最大信号带宽50kHz的要求。

3、采样保持放大器AD783与AD671的接口电路4、数据采集系统基本接地和耦合电路(采样保持放大器AD783)如图所示为数据采集系统基本接地和耦合电路。

作为任何一个高速、高分辨率数据采集系统,电源都必须很好地调节,对额外的高频噪声(纹波)必须予以抑制。

图中AD783电源连接可以很好地实现上述要求,同时有能力传输瞬间电流给器件。

单片机ADC采样的原理

单片机ADC采样的原理

单片机ADC采样的原理是通过将模拟信号转换为数字信号来进行采样。

其基本原理如下:

1. 选择参考电压:单片机ADC模块需要一个参考电压来将模拟信号转换为数字信号。

参考电压可以是单片机供电电压的一部分,或者外部提供的固定电压。

2. 采样保持:采样保持电路用于稳定模拟信号的电平,在ADC转换期间保持其值不变。

当ADC开始转换时,采样保持电路将模拟信号的电压保持在一个恒定的水平上。

3. 量化:ADC模块将连续的模拟信号转化为离散的数字信号。

它将模拟信号的幅度划分为若干个等间隔的离散值,并将每个值用二进制表示。

4. 转换:ADC通过逐个采样每个量化值,并将其转换为二进制数字。

这是通过将模拟信号与参考电压进行比较,并产生一个数字输出来实现的。

5. 输出:ADC将转换后的数字信号输出给单片机的内部总线,以供后续处理。

总之,单片机ADC采样的过程涉及参考电压的选择、采样保持、量化、转换和输出等步骤,以实现模拟信号到数字信号的转换。

采样保持电路

➢ 在这种条件下,V1的漏电流大约减小两个数量级。

-E

V ui

R V1

∞

-

+

+N

uo

C

Uc

➢ 可见采用V1后能将V与存储电容C隔离, ➢ 一方面使V的漏电流不流经存储电容, ➢ 另一方面又有效地降低了V1的漏流,从而提高了存储电容的

保持精度。

二、采样保持实用电路

(2)电容校正方法 ➢ 应用补偿电容C1来减小开关漏电流及运算放大器偏

对采样保持电路的主要 要求:

基本原理

精度和速度,充电快、 放电慢

导通电阻、截止电 阻、延迟时间

∞

-

+Biblioteka ui+ N1

∞

-

S

+

+

C UC

为提高实际电路的精度 和速度,需同时从元件 和电路两方面着手解决。

uo

带宽,上升速 率、最大输出 电流和漂移

漏电流

输入阻抗、上升速 率、漂移

采样保持电路

基本原理

采样保持电路的主要性能指标: 捕捉时间:从发出采样指令的时刻起,到输出值达到

处于采样状态,等效电路如图。

Uc

R1

VD1

VD2 V2

C1

V1

∞

∞ -

R2

+

R3 V

-

+

+ N2

uo

ui

+ N1

C

二、采样保持实用电路

当Uc为高电平时:

Ron2

C1

等效电路如图。

∞

∞

-

-

Ron

+

uo

+

(完整)采样保持电路

采样-保持电路采样一保持(S/H )电路具有采集某一瞬间的模拟输入信号,并根据需要保持并输出 所采集的电压数值的功能。

S / H 电路广泛应用于多路快速数据检测系统。

采样一保持电路基本工作原理及性能1、S/H 电路基本工作原理S/H 电路的原理电路、电路符号及波形如图所示。

S/H 电路的原理电路、电路符号及波形 电路中,SW 为模拟电子开关,其状态由逻辑控制信号vc 控制.CH 为保持电容,其两端电压即为S/H 电路输出电压vo.当控制信号vc 为高电平“1”时,模拟电子开关SW 闭合S/H 电路进入采样状态,输入信号vs (t ) 迅速对CH 充电,vo (t )精确地跟踪输入信号;当vc 为低电平“0”时,SW 断开CH 立即停止充电S/H 电路进入保持状态,vo (t )保持SW 断开瞬间的输入信号电压值不变。

理想采样一保持特性如图(c ) 所示,其数学表达式为5(力Qc = T”,采样期)v s (t D )(玫=“0”,保持期)式中,to 为逻辑控制信号vc 从“1”变为“0”的时间。

实际的采样一保持电路,常需设置缓冲级把模拟开关SW/保持电容CH 与信号源及负载隔离开,以 提高采样一保持电路的性能.2、S/H 电路性能指标6)电路符号(。

)波弗S/H电路的主要性能指标有采样时间、断开时间;采样精度、保持精度等.(1)采样时间和断开时间S/H电路由保持状态变为采样状态,或由采样状态变为保持状态并不是瞬间完成,需要一定的时间。

从发出采样指令开始到输出信号达到所规定的误差范围内的数值为止,所需的时间称为采样时间(又称捕捉时间),一般为0。

1~10^$数量级。

从发出保持指令开始到模拟开关断开,输出稳定下来为止,所需的时间称为断开时间(又称孔径时间),一般为10〜150门$数量级.采样时间长,电路的跟踪特性差;断开时间长,电路的保持特性不好。

两者都限制了5 /H电路工作频率的提高,即限制了电路工作速度。

采样保持电路

3.3.2 放大电路实例

3、热电耦测量放大电路

由于热电偶Tc 的电压输出决定于热端与

冷端的温度差,理论上应使冷端温度为基 点即0℃,而实际上冷端温度通常为室温, 所以图中利用PN结的结电压随温度上升而 线性下降的特性来进行补偿。

3.3.2 放大电路实例

3、热电耦测量放大电路 热端每变化1℃,K型热电偶有40mV的电

3.4.1 DAC与微机接口的一般方法

1、8位DAC接口 典型的CPU系统与DAC的接口如下图所示:

图 3-21 8位DAC接口

3.4.1 DAC与微机接口的一般方法

1、8位DAC接口 通过74100锁存器把8位DAC连接到CPU系

统。 CPU把数字存入锁存器。 DAC把二进制数变换为输出电流。 741型集成运放把电流变换为0~1V的输出

的测温电路,如下图。输出电压Vo=10mV×t(t为测量温

度值),温度测量范围为-20℃~+100℃。

图3-7 温度传感器测温电路

3.2.2 传感器应用实例

2、 LM35系列电压输出式集成温度传感器 2)温度/频率变换电路

用V/F变换器LM131、集成温度传感器LM35或 LM45及光偶4N128,组成输入输出隔离的温度/ 频率变换电路,如图3-8。光偶还进行电平转换。

电压,该输出模拟电压与数字量成比例。

3.4.1 DAC与微机接口的一般方法

1、8位DAC接口 下列程序可产生一个线性增加的斜波电压。

MOV SP,#53H

CLR A

MOV R1,#17H LOOP: MOVX @R1,A

ACALL DELAY

INC A

AJMP LOOP

DELAY: …

采样保持电路

采样保持电路基本知识1、采样保持电路原理采样保持电路能够跟踪或者保持输入模拟信号的电平值。

在理想状况下,当处于采样状态时,采样保持电路的输出信号跟随输入信号变化而变化;当处于保持状态时,采样保持电路的输出信号保持为接到保持命令的瞬间的输入信号电平值。

一个典型的采样保持电路模型如图1 所示。

图1 采样保持电路基本模型当电路处于采样状态时开关导通,这时电容充电,如果电容值很小,电容可以在很短的时间内完成充放电,这时,输出端输出信号跟随输入信号的变化而变化;当电路处于保持状态时开关断开,这是由于开关断开,以及集成运放的输入端呈高阻状态,电容放电缓慢,由于电容一端接由集成运放构成的信号跟随电路,所以输出信号基本保持为断开瞬间的信号电平值。

2、采样保持电路的主要技术指标采样保持电路有采样和保持两种工作状态,这两种工作状态对于电路的性能,整个A/D转换部分性能都有很大的影响。

在这两种不同的模式下,电路的特点也有一定的差别,下面根据采样保持电路两种不同的工作状态来分析其主要技术指标。

2.1采样状态下的主要技术指标偏移电压,是指在采样模式下,当输入端电压为零时,输出端的输出电压值。

为了保证A/D转化芯片能够准确地采样,偏移电压的值应当满足Vof<Vfs/2^(n+1)其中,Vof为偏移电压,Vfs为A/D 芯片的满量程电压,n 为A/D芯片的位数。

最大变化频率,是指在采样模式下,输出电压最高的变化频率。

这个频率值受到保持电容容值大小的影响,对系统的工作频率有一定的限制作用。

2.2保持状态下的主要技术指标降压速率,是指在保持模式下,输出端的输出电压值随输入时间变化的速率。

降压速率满足:dVc/dt = Ic/Ch其中,Vc为电容两端的电压值,Ic为流经电容的电流值,Ch为保持电容的容值。

馈通衰减量,是指在保持模式下,输入信号的电压值到经过采样保持电路后,在输出端输出时的减少量。

为了使A/D芯片能够准确地采样出信号,馈通衰减量小于A/D芯片的最低有效位LSB 的1/2。

采样保持电路

采样保持电路

采样保持电路常用于输入信号变化较快或具有多路输入信号的数据采集系统中,也可用于其它一切要求对信号进行瞬时采样和存储的场合。

在A/D转换过程中,因为每次转换过程需要一定的时间,所以需要采样保持电路的配合,以便有一个稳定的采集量。

采样保持器的工作过程由外部控制信号来决定,工作过程分“采样”和“保持”两个周期。

“采样”就是要求输出信号能快速而准确地跟随信号的变化;而“保持” 则是在两次采样间隔时间内保持上一次采样结束时的状态。

采样保持电路工作原理图如上图所示,其主要由场效应管T,电容C、电阻R和运放组成。

工作原理:在采样过程中,控制信号L为高电平,场效应管相当于一个开关导通,输入电压迅速对电容C充电,此时充电电阻很小〔近似为0〕,电容电压与输入电压ui相等,经过运放电压跟随器输出到输出端uo。

在保持过程中,L为低电平,场效应管关断,电容电荷没有放电回路〔运放输入电阻为无穷大〕。

因此输出电压uo就保持在场效应管关断时的输入电压值不变。

采样保持电路图(五款采样保持电路设计原理图详解)

采样保持电路图(五款采样保持电路设计原理图详解)采样保持电路(采样/保持器)又称为采样保持放大器。

当对模拟信号进行A/D转换时,需要一定的转换时间,在这个转换时间内,模拟信号要保持基本不变,这样才能保证转换精度。

采样保持电路即为实现这种功能的电路。

采样保持电路能够跟踪或者保持输入模拟信号的电平值。

在理想状况下,当处于采样状态时,采样保持电路的输出信号跟随输入信号变化而变化;当处于保持状态时,采样保持电路的输出信号保持为接到保持命令的瞬间的输入信号电平值。

当电路处于采样状态时开关导通,这时电容充电,如果电容值很小,电容可以在很短的时间内完成充放电,这时,输出端输出信号跟随输入信号的变化而变化;当电路处于保持状态时开关断开,这是由于开关断开,以及集成运放的输入端呈高阻状态,电容放电缓慢,由于电容一端接由集成运放构成的信号跟随电路,所以输出信号基本保持为断开瞬间的信号电平值。

采样保持电路图设计(一)采样保持放大器SMP04用做多路输出选择器电路图如图所示为SMP04用做多路输出选择器,与解码器、D/A转换器构成的四路数字-模拟转换电路。

数字信号输入模数转换器DAC8228,输出产生5~10V模拟电压送副SMP04,地址输入通道解码器,不同的地址解码后分别控制四路开关,以分别输出四模拟信号。

采用DAC8228产生DAC电压输出可以使电路得以最大的简化。

为了将输出电压干扰减小到最小,在采样信号被确认之前,必须保证有5μs的最后电压建立时间。

每一个采样保持放大器必须在每一秒钟或更低时问刷新一次,以确保输出电压下降率不超过10mV或1/2LSB(最小有效位)。

采样保持电路图设计(二)如图所示为由SMP04与运放构成的增益为10的采样保持放大电路。

电路中将SMP04置于运放OP490的反馈回路中,当S非/H=0时,SMP04内部开关闭合,运放OP490的反馈回路接通,电路增益由运放本身及反馈电阻决定,图中增益设置为10,输出端输出放大后的采样电压。

基于AD783的采样保持电路

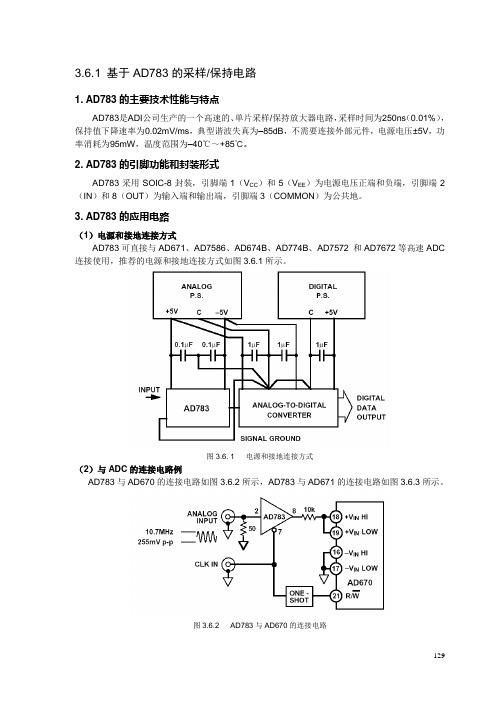

1293.6.1 基于AD783的采样/保持电路1. AD783的主要技术性能与特点AD783是ADI 公司生产的一个高速的、单片采样/保持放大器电路,采样时间为250ns (0.01%),保持值下降速率为0.02mV/ms ,典型谐波失真为–85dB ,不需要连接外部元件,电源电压±5V ,功率消耗为95mW ,温度范围为–40℃~+85℃。

2. AD783的引脚功能和封装形式AD783采用SOIC-8封装,引脚端1(V CC )和5(V EE )为电源电压正端和负端,引脚端2(IN )和8(OUT )为输入端和输出端,引脚端3(COMMON )为公共地。

3. AD783的应用电路(1)电源和接地连接方式AD783可直接与AD671、AD7586、AD674B 、AD774B 、AD7572 和AD7672等高速ADC 连接使用,推荐的电源和接地连接方式如图3.6.1所示。

图3.6. 1 电源和接地连接方式(2)与ADC 的连接电路例AD783与AD670的连接电路如图3.6.2所示,AD783与AD671的连接电路如图3.6.3所示。

图3.6.2 AD783与AD670的连接电路130图3.6.3 AD783与AD671的连接电路3.6.2基于SHC5320的采样/保持电路1. SHC5320的主要技术性能与特点SHC5320是TI 公司生产的(原BURR-BROWN 公司)是双极性单片采样/保持器电路,模拟输入范围为-10V ~+10V ,共模电压范围为-10V ~+10V ,输入阻抗大于1M Ω,失调电流小于±300nA ,输出电压范围为-10V ~+10V ,输出电流大于±10mA ,输出阻抗小于1Ω,输入漂移小于±20μV /℃,共模抑制比大于72dB ,电源抑制比大于65dB ,压摆率典型值为45V /μs ,采样时间小于1.5μs ,从采样到保持的切换时间为165~350ns ,下降速率典型值为0.5μV /μs (在25℃时),差分输入,控制接口与TTL 逻辑电平兼容,工作电源电压±12V ~±18V ,电流消耗±13mA ,工作温度范围-40℃~+80℃,可广泛地应用于高精度数据采集系统、自动调零电路和D/A 转换等电路中。

3.4 采样保持电路解析

第三章 数据采集技术

采样保持电路

3.4.3 采样/保持器的类型和主要性能参数

1. 采样/保持器的类型

按结构分为两种类型:

串联型采样/保持器

UK A1 K + A2 UO

Ui

+

CH

模拟地

串联型采样/保持器的结构

A1和A2分别是输入和输出缓冲放大器,用以提高采样/保 持器的输入阻抗,减小输出阻抗,以便与信号源和负载连 接。

第三章 数据采集技术

采样保持电路

3.4.3 采样/保持器的类型和主要性能参 数

1. 采样/保持器的类型

按结构分为两种类型:

串联型采样/保持器 优点:结构简单。

缺点: 其失调电压为两个运放失调电 压之和,比较大,影响到采样 /保持器的精度。 跟踪速度也较低。

第三章 数据采集技术

采样保持电路

电容CH对精度的影响:

如果电容值过大,则其时间常数大,当模拟信号频 率高时,由于电容充放电时间长,将会影响电容对 在选择电容时,容量大小要适宜,以保证其时间常 输入信号的跟踪特性,而且在跟踪的瞬间,电容两 数适中,并选用泄露小的电容。 端的电压会与输入信号电压有一定的误差。 另外,一般在输入端和输出端均采用缓冲器,以减 如果电容值过小,在保持状态时,由于电容漏电流 少信号源的输出阻抗,增加负载的输入阻抗。 的存在或者负载内阻太小的影响,会引起保持信号 电平的变化。

第三章 数据采集技术

采样保持电路

3.4.3 采样/保持器的类型和主要性能参数

1. 采样/保持器的类型

按结构分为两种类型:

串联型采样/保持器

UK A1 K + A2 UO

Ui

+

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

矿产资源开发利用方案编写内容要求及审查大纲

矿产资源开发利用方案编写内容要求及《矿产资源开发利用方案》审查大纲一、概述

㈠矿区位置、隶属关系和企业性质。

如为改扩建矿山, 应说明矿山现状、

特点及存在的主要问题。

㈡编制依据

(1简述项目前期工作进展情况及与有关方面对项目的意向性协议情况。

(2 列出开发利用方案编制所依据的主要基础性资料的名称。

如经储量管理部门认定的矿区地质勘探报告、选矿试验报告、加工利用试验报告、工程地质初评资料、矿区水文资料和供水资料等。

对改、扩建矿山应有生产实际资料, 如矿山总平面现状图、矿床开拓系统图、采场现状图和主要采选设备清单等。

二、矿产品需求现状和预测

㈠该矿产在国内需求情况和市场供应情况

1、矿产品现状及加工利用趋向。

2、国内近、远期的需求量及主要销向预测。

㈡产品价格分析

1、国内矿产品价格现状。

2、矿产品价格稳定性及变化趋势。

三、矿产资源概况

㈠矿区总体概况

1、矿区总体规划情况。

2、矿区矿产资源概况。

3、该设计与矿区总体开发的关系。

㈡该设计项目的资源概况

1、矿床地质及构造特征。

2、矿床开采技术条件及水文地质条件。