加法器的设计与仿真

实验二 全加器的设计与仿真

实验二全加器的设计与仿真全加器是非常典型的数字单元电路,在数字系统中常常用到全加器。

一般认为加法器是纯组合逻辑电路,只要用一些基本门电路就可以设计出全加器。

通常情况下,全加器是数字系统中的一个子模块,为了使加法器能与系统在时钟的驱动下同步工作,我们把全加器设计成由时钟控制带一级流水线的加法器。

需要指出的是,在数字集成电路设计中,大多数公司使用VerilogHDL进行RTL设计,较少使用VHDL,主要的原因是VerilogHDL语法简单易学,底层库支持好,EDA工具支持全面,集成电路发达的国家和地区应用广泛。

而VHDL的发展逐渐式微,越来越多的公司正逐渐向VerilogHDL转移。

建议使用VerilogHDL进行RTL设计,便于交流。

集成电路设计中心实验室的工作站运行环境为:•Sun Blade2000两台•双64-bit CPU, 内存4GB ,•硬盘73GB用户可以通过Xmanager 登录,每个用户拥有50MB的磁盘配额。

2.1设计文件准备和编译按可综合风格写出VerilogHDL代码如下(仅供参考):module Adder8 (ain, bin, cin, sout, cout, clk,rst);/* Eight Bit Adder Module */output [7:0] sout;output cout;input [7:0] ain, bin;input cin, clk,rst;wire [7:0] sout_tmp, ain, bin;wire cout_tmp;reg [7:0] sout, ain_tmp, bin_tmp;reg cout, cin_tmp;always @(posedge clk)beginif (rst==1)beginsout=0;cout=0;ain_tmp=ain;bin_tmp=bin;cin_tmp=cin;endelsebegincout = cout_tmp;sout = sout_tmp;ain_tmp = ain;bin_tmp = bin;cin_tmp = cin;endendassign {cout_tmp,sout_tmp} = ain_tmp + bin_tmp + cin_tmp;endmodule上述代码在Unix/Linux 系统中,在用户目录下,建文件夹Adder8_full, 下建src,sim,syn,pr四个目录。

加法器电路设计实验报告

加法器电路设计实验报告【加法器电路设计实验报告】一、实验目的本实验的主要目标是通过实际操作,设计并实现一个基础的加法器电路,以深入理解数字逻辑电路的设计原理和工作方式。

通过对半加器、全加器以及多位加法器的设计与搭建,进一步熟悉集成门电路的应用,掌握组合逻辑电路的设计方法,并能对电路的逻辑功能进行有效的验证与分析。

二、实验原理加法器是数字系统中的基本运算单元,其核心工作原理基于二进制数的加法规则。

在最基础的层面上,一个半加器(Half Adder)用于计算两个一位二进制数的和,同时产生一个进位输出;而全加器(Full Adder)在此基础上增加了处理来自低位的进位输入,可以完成三位二进制数的相加。

对于多位二进制数的加法,可以通过级联多个全加器来实现。

1. 半加器:由两个异或门(XOR)实现“和”输出,一个与门(AND)实现“进位”输出,即S=A XOR B,Cout=A AND B。

2. 全加器:除了接收两个数据输入A和B外,还接收一个进位输入Cin,同样由异或门计算“和”,但“进位”输出需要考虑三个输入的与或逻辑关系,即S=A XOR B XOR Cin,Cout=(A AND B) OR (B AND Cin) OR (A AND Cin)。

三、实验步骤1. 半加器设计:首先,利用集成电路库中的逻辑门元件构建半加器,将A 和B作为异或门的输入得到和信号S,将A和B分别连接到与门的两个输入端得到进位信号Cout。

2. 全加器设计:在半加器的基础上,增加一个输入端Cin代表低位的进位,同样运用异或门和与门组合形成全加器的逻辑结构,根据全加器的逻辑表达式连接各门电路。

3. 多位加法器设计:为了实现多位二进制数的加法,将若干个全加器按照从低位到高位的顺序级联起来,每级全加器的进位输出连接到下一级的进位输入。

四、实验结果及分析经过电路设计与仿真测试,成功实现了从半加器到多位加法器的功能转化。

当给定两组多位二进制数后,所设计的加法器电路能够准确无误地计算出它们的和,并正确显示进位信息。

加法器电路的设计

加法器电路的设计加法器是数字电路中常见的一种逻辑电路,用于实现多个数字信号的加法运算。

它是计算机中基本的运算器件之一,广泛应用于各种计算机及数字电子设备中。

加法器的设计首先要考虑的是输入和输出的位数。

一般情况下,我们需要设计一个n位的加法器,其中n可以是任意正整数。

接下来,我们将详细介绍一个4位加法器的设计过程。

4位加法器的设计可以通过级联多个1位加法器实现。

每个1位加法器有两个输入A和B,以及一个进位输入Cin,两个输出之和S和进位输出Cout。

首先,我们需要实现1位全加器。

1位全加器可以通过两个半加器(Half Adder)和一个或门(OR gate)组合而成。

半加器有两个输入A和B,以及一个进位输入Cin,和两个输出之和S和进位输出Cout。

它的真值表如下所示:```A B Cin S Cout0000001010100101100100110011011010111111```其中,S代表两个输入的和,Cout代表进位输出。

半加器可以用逻辑门来实现。

S可以通过一个异或门(XOR gate)实现,Cout可以通过一个与门(AND gate)实现。

具体实现如下所示:S=A⊕BCout = A ∧ B接下来,我们将两个半加器级联成一个1位全加器。

如下所示:```__________________A---_____B--->,Half , AND ,---->CouCin->, Adder , Gate,________________________,XOR,---->, Gat,_____```在该电路中,两个输入A和B直接连接到两个半加器的对应输入上,进位输入Cin只连接到第一个半加器的进位输入上。

两个半加器的和输出S通过异或门连接在一起,同时使用与门实现进位输出Cout。

有了1位全加器的设计,我们就可以开始组合多个1位全加器来实现4位加法器了。

具体的设计思路是:1.将四个输入A0-A3和B0-B3连接到四个1位全加器的对应输入上。

实验二 加法器的设计与仿真实验报告

实验二加法器的设计与仿真一、实验目的:实现加法器的设计与仿真。

二、实验内容1.用逻辑图和VHDL语言设计全加器;2.利用设计的全加器组成串行加法器;3.用逻辑图和VHDL语言设计并行加法器。

三、实验步骤。

(一)、全加器、串行加法器和并行加法器的逻辑图。

1.全加器:2.串行加法器:3.74283:4位先行进位全加器逻辑框图:逻辑图:(二)、全加器、串行加法器和并行加法器的VHDL。

1.全加器:LIBRARY ieee;USE ieee.std_logic_1164.all;LIBRARY work;ENTITY quanjiaqi ISPORT(X : IN STD_LOGIC;Y : IN STD_LOGIC;CIN : IN STD_LOGIC;S : OUT STD_LOGIC;COUT : OUT STD_LOGIC);END quanjiaqi;ARCHITECTURE bdf_type OF quanjiaqi ISSIGNAL SYNTHESIZED_WIRE_0 : STD_LOGIC;SIGNAL SYNTHESIZED_WIRE_1 : STD_LOGIC;SIGNAL SYNTHESIZED_WIRE_2 : STD_LOGIC;SIGNAL SYNTHESIZED_WIRE_3 : STD_LOGIC;BEGINSYNTHESIZED_WIRE_2 <= Y AND X;SYNTHESIZED_WIRE_1 <= CIN AND Y;SYNTHESIZED_WIRE_3 <= CIN AND X;SYNTHESIZED_WIRE_0 <= X XOR Y;S <= SYNTHESIZED_WIRE_0 XOR CIN;COUT <= SYNTHESIZED_WIRE_1 OR SYNTHESIZED_WIRE_2 OR SYNTHESIZED_WIRE_3; END bdf_type;2.串行加法器:LIBRARY ieee;USE ieee.std_logic_1164.all;LIBRARY work;ENTITY chuanxingjiafaqi ISPORT(x0 : IN STD_LOGIC;y0 : IN STD_LOGIC;cin : IN STD_LOGIC;x1 : IN STD_LOGIC;x2 : IN STD_LOGIC;y2 : IN STD_LOGIC;x3 : IN STD_LOGIC;y3 : IN STD_LOGIC;y1 : IN STD_LOGIC;s0 : OUT STD_LOGIC;s1 : OUT STD_LOGIC;s2 : OUT STD_LOGIC;s3 : OUT STD_LOGIC;cout : OUT STD_LOGIC);END chuanxingjiafaqi;ARCHITECTURE bdf_type OF chuanxingjiafaqi ISCOMPONENT quanjiaqiPORT(X : IN STD_LOGIC;Y : IN STD_LOGIC;CIN : IN STD_LOGIC;S : OUT STD_LOGIC;COUT : OUT STD_LOGIC);END COMPONENT;SIGNAL SYNTHESIZED_WIRE_0 : STD_LOGIC; SIGNAL SYNTHESIZED_WIRE_1 : STD_LOGIC; SIGNAL SYNTHESIZED_WIRE_2 : STD_LOGIC;BEGINb2v_inst : quanjiaqiPORT MAP(X => x0,Y => y0,CIN => cin,S => s0,COUT => SYNTHESIZED_WIRE_0); b2v_inst1 : quanjiaqiPORT MAP(X => x1,Y => y1,CIN => SYNTHESIZED_WIRE_0,S => s1,COUT => SYNTHESIZED_WIRE_1); b2v_inst2 : quanjiaqiPORT MAP(X => x2,Y => y2,CIN => SYNTHESIZED_WIRE_1,S => s2,COUT => SYNTHESIZED_WIRE_2); b2v_inst3 : quanjiaqiPORT MAP(X => x3,Y => y3,CIN => SYNTHESIZED_WIRE_2,S => s3,COUT => cout);END bdf_type;3.74283:4位先行进位全加器LIBRARY ieee;USE ieee.std_logic_1164.all;LIBRARY work;ENTITY 74283_0 ISPORT(CIN : IN STD_LOGIC;A1 : IN STD_LOGIC;A2 : IN STD_LOGIC;B2 : IN STD_LOGIC;A3 : IN STD_LOGIC;A4 : IN STD_LOGIC;B4 : IN STD_LOGIC;B1 : IN STD_LOGIC;B3 : IN STD_LOGIC;SUM4 : OUT STD_LOGIC;COUT : OUT STD_LOGIC;SUM1 : OUT STD_LOGIC;SUM2 : OUT STD_LOGIC;SUM3 : OUT STD_LOGIC );END 74283_0;ARCHITECTURE bdf_type OF 74283_0 IS BEGIN-- instantiate macrofunctionb2v_inst : 74283PORT MAP(CIN => CIN,A1 => A1,A2 => A2,B2 => B2,A3 => A3,A4 => A4,B4 => B4,B1 => B1,B3 => B3,SUM4 => SUM4,COUT => COUT,SUM1 => SUM1,SUM2 => SUM2,SUM3 => SUM3);END bdf_type;四、实验仿真结果。

2.1加法器实验 报告 A5

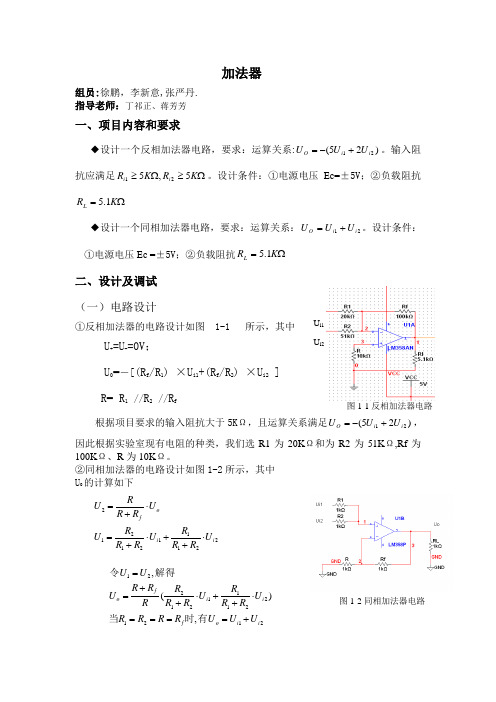

加法器组员:徐鹏,李新意,张严丹. 指导老师:丁祁正、蒋芳芳一、项目内容和要求◆设计一个反相加法器电路,要求:运算关系:)25(21i i O U U U +-=。

输入阻抗应满足Ω≥Ω≥K R K R i i 5,521。

设计条件:①电源电压Ec=±5V ;②负载阻抗Ω=K R L 1.5◆设计一个同相加法器电路,要求:运算关系:21i i O U U U +=。

设计条件: ①电源电压Ec =±5V ;②负载阻抗Ω=K R L 1.5二、设计及调试 (一)电路设计①反相加法器的电路设计如图 1-1 所示,其中U +=U -=0V ;U 0=-[(R f /R 1) ×U i1+(R f /R 2) ×U i2 ] R = R 1 //R 2 //R f根据项目要求的输入阻抗大于5K Ω,且运算关系满足)25(21i i O U U U +-=,因此根据实验室现有电阻的种类,我们选R1为20K Ω和为R2为51K Ω,Rf 为100K Ω、R 为10K Ω。

②同相加法器的电路设计如图1-2所示,其中 U 0的计算如下图1-1反相加法器电路U i1 U i22211121212i i o fU R R R U R R R U U R R RU ⋅++⋅+=⋅+=21212211121221,)(,i i o f i i f o U U U R R R R U R R R U R R R R R R U U U +====⋅++⋅++==有时当解得令图1-2同相加法器电路根据项目要求的输入阻抗大于5K Ω,且运算关系满足21i i O U U U +=,因此根据实验室现有电阻的种类,我们选R1、R2、R 和Rf 都是10K Ω.(二)电路仿真1、反相加法器的电路仿真测试A :输入信号V U V U i i 5.0,5.021±=±=,测试4种组合下的输出电压如下;①反相加法器 U i1=+0.5v ,U i2=+0.5v ,输出电压U 0=-3.464V.②反相加法器 U i1=+0.5v ,U i2=-0.5v ,输出电压U 0=-1.503V.③反相加法器U i1=-0.5v,U i2=-0.5v ,输出电压U0=3.496V.④反相加法器U i1=-0.5v,U i2=+0.5v ,输出电压U0=1.536V.B :输入信号V KHz U V U i i 1.0,1,5.021为正弦波±=信号,测试两种输入组合情况下的输出电压波形如下。

加法器的设计与仿真

实验三加法器的设计与仿真

一、实验内容

1.用逻辑图和VHDL语言设计全加器;

2.利用设计的全加器组成串行加法器;

3.用逻辑图和VHDL语言设计并行加法器。

二、电路要求

1.进实验室前,请写一份预习报告;进实验室时经指导老师检查后,才可上机操作。

2.预习报告内容有:

全加器的逻辑图;

用VHDL语言设计全加器;

3.实验结束前,要填写实验卡,将以上3种电路的仿真波形画在实验卡上。

三、电路功能介绍

1.全加器

用途:实现一位全加操作

逻辑图

真值表

X Y CIN S COUT

00000

00110

01010

01101

10010

10101

11001

11111 VHDL程序

数据流描述:

波形图

2.四位串行加法器

逻辑图

波形图

3.74283:4位先行进位全加器(4-Bit Full Adder)

逻辑框图

逻辑功能表

注:1、输入信号和输出信号采用两位对折列表,节省表格占用的空间,如:[A1/A3]对应的列取值相同,结果和值[Σ1/Σ3]对应的运算是Σ1=A1+B1和

Σ3=A3+B3。

请自行验证一下。

2、C2是低两位相加产生的半进位,C4是高两位相加后产生的进位输出,C0是低位级加法器向本级加法器的进位输入。

友情提示:本资料代表个人观点,如有帮助请下载,谢谢您的浏览!。

三位十进制加法器设计及仿真

三位十进制加法器设计及仿真

三位十进制加法器是一种计算机电路,用于将三个十进制数字相加。

以下是一种基本的三位十进制加法器设计及仿真示例:

1. 设计:

- 使用三个4位BCD(Binary-Coded Decimal)加法器来实现三个十进制数字的相加。

- 将输入的三个十进制数字转换为BCD码,并将其作为输入传递给BCD加法器。

- 使用一个4位BCD加法器作为主加法器,用于计算BCD码的和。

- 同时,使用一个进位传递位(Carry Ripple)电路,将进位从低位传递到高位。

2. 仿真:

- 使用电路设计软件(如Verilog或VHDL)进行仿真。

- 编写设计代码,包括BCD加法器、主加法器和进位传递位电路的功能描述。

- 使用仿真工具激励设计代码,为输入信号提供测试数据,观察输出结果。

- 检查仿真波形,确保设计的正确性和功能性。

需要注意的是,具体的设计和仿真细节可能因使用的电路软件和硬件平台而有所不同。

以上只是一个简单示例,可以根据具体需求进行更复杂的设计和仿真。

对于实际的电路设计和仿真,请确保遵守相关标准和规范,并咨询专业的电路工程师。

基于Multisim加法计数器的仿真(设计)

(题目:基于Multisim加法计数器的仿真)姓名:学号:专业:通信工程院系:电子通信工程学院指导老师:职称学位:完成时间:2013年5月教务处制安徽新华学院本科毕业论文(设计)独创承诺书本人按照毕业论文(设计)进度计划积极开展实验(调查)研究活动,实事求是地做好实验(调查)记录,所呈交的毕业论文(设计)是我个人在导师指导下进行的研究工作及取得的研究成果。

据我所知,除文中特别加以标注引用参考文献资料外,论文(设计)中所有数据均为自己研究成果,不包含其他人已经发表或撰写过的研究成果。

与我一同工作的同志对本研究所做的工作已在论文中作了明确说明并表示谢意。

毕业论文(设计)作者签名:日期:基于Multisim加法计数器的仿真摘要计数器是数字系统中最基本的要素,本课题研究了任意进制计数器的设计方法,并利用Multisim进行软件仿真。

本文详细介绍了集成计数器芯片74LS161的原理和结构以及Multisim软件的使用方法。

通过对集成芯片的级联以及附加门电路的连接,以实现任意进制的计数器。

这里我们采用的是两片4位二进制加法计数器74LS161芯片进行级联,通过置数法来实现256以内的任意进制的计数器。

并用Multisim软件对设计的计数器进行仿真,观察结果正确,从而得出整个设计是正确的。

关键词:计数器;Multisim;级连法;置数法Simulation of the addition counter based on MultisimAbstractThe counter is the most basic elements of a digital system.This article introduces the design method of arbitrary hexadecimal counter and how to realize the simulation with Multisim software.This article introduces the principle and structure of integrated chip counter 74LS161,as well as the use-method of Multisim software.With the cascade connection of integrated chips and the connection of gate circuits,the arbitrary hexadecimal counter comes true.Here we make two chips of the four bit binary adder counter 74LS161 cascade and then achieve the counter of the arbitrary hexadecimal which is less than 256 by setting the number of law.We also use the Multisim software to simulate the counter,and if the result of observation is correct,so that the whole design is correct.Keyword:Counter; Multisim; Cascade method; Set the number of law目录1绪论 (1)2计数器 (1)2.1 计数器简介 (2)2.2 计数器的分类 (2)2.3 计数器集成芯片 (2)3Multisim的简介 (4)3.1使用简介 (5)3.2 Multisim对元器件的管理 (6)4设计思路和方法 (7)4.1 N>M时的设计方法 (7)4.1.1 复位法 (7)4.1.2 预置数法 (8)4.2 N<M的设计方法 (9)4.2.1 M不是素数 (9)4.2.2 M是素数 (10)5设计与仿真 (12)5.1 模256以内任意进制的计数器设计 (12)5.1.1 预置数的设计 (12)5.1.2 芯片级联 (12)5.1.3 连接七段显示管 (13)5.1.4 逻辑分析仪的连接 (14)5.2 总电路图 (15)5.3 电路的仿真 (16)5.3.1 模256的仿真 (16)5.3.2 模232的仿真 (18)6 总结 (20)致谢 (20)参考文献 (22)1 绪论计数器是一种最常用的时序电路。

加法器的设计与仿真

实验三加法器的设计与仿真一、实验内容1.用VHDL语言设计全加器;2.利用设计的全加器组成串行加法器;3.用VHDL语言设计并行加法器。

二、实验原理、波形仿真及波形分析1、全加器(1)VHDL语言LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;ENTITY f_adder ISPORT(x,y,cin : IN STD_LOGIC;s,cout : OUT STD_LOGIC);END ENTITY f_adder;ARCHITECTURE bhv OF f_adder ISBEGINs<=x XOR y XOR cin;cout<=(x AND y)OR(x AND cin)OR(y AND cin); END ARCHITECTURE bhv;(3)真值表X Y CIN S COUT0 0 0 0 00 0 1 1 00 1 0 1 00 1 1 0 11 0 0 1 01 0 1 0 11 1 0 0 11 1 1 1 1(2)仿真波形图(3)波形分析当cin输入为低电平时,x+y需要进位时cout输出为高电平,s输出为低电平;当cin输入为高电平时,x+y不需要进位时cout输出为高电平;2、四位串行加法器(1)逻辑电路图(2)仿真波形图(3)波形分析x与y代表两个输入,s代表输出。

x与y直接相加,当之和大于16时按照16进制数规则,进一位,同时Cout显示为高电平。

3、四位先行进位全加器(1)逻辑原理图(2)仿真波形图(2)波形分析当cin为高电平时,s=x+y+1,当cin为高电平时,s=x+y,同四位串行加法器一样,实现进位相加。

三、实验感想本次试验主要设计、实现和验证了全加器、四位串行加法器以及四位先行进位全加器。

通过实验进一步熟悉了Quartus的使用,并学会了如何封装并调用元件,学会了如何分析仿真波形图。

实验七:四位加法器电路设计与模拟

12

通过在 T-SPICE 文件中进行如下设置,可得输入信号 B 的波形图,如下图所示。

输入信号波形,从上到下一次是 B0,B1,B2,B3

13

通过在 T-SPICE 文件中进行如下设置,可得输出信号 S,Cout 的波形图,如下图所示。

输出信号波形,从上到下一次是 S0,S1,S2,S3,Cout

0

0

1

0

0

0

1

1

0

1

0

1

1

1

0

1

1

0

1

1

Cout

Cout

Cout

Cout

14

name 下面输入 add4,在 Create in folder 下面空白的右边点击 面板上选中 E 盘里的 ex7 文件夹,点击“确定” 。如下图所示。 ,在弹出的“浏览文件夹”

完成“确定”之后,New Design 面板如下图所示,点击“OK”按钮即可,新设计就建 立好了。

2

4.建立新单元:新设计建立好后,接下来就是要建立新单元,一个设计可以包含很多个

建立符号图视图模式如下操作。 选择 Cell——New View, 弹出如下对话框。 在 view type 选项中选择“symbol” ,点击“OK”按钮即可,会出现画符号图的面板。

5.从元件库引用元件:新单元建立好后,就可以在新单元的电路图模式下画电路图了。

实验二 加减法运算器的设计实验报告

加减法运算器的设计实验报告实验二加减法运算器的设计一、实验目的1、理解加减法运算器的原理图设计方法2、掌握加减法运算器的VERILOG语言描述方法3、理解超前进位算法的基本原理4、掌握基于模块的多位加减运算器的层次化设计方法5、掌握溢出检测方法和标志线的生成技术6、掌握加减运算器的宏模块设计方法二、实验任务1、用VERILOG设计完成一个4位行波进位的加减法运算器,要求有溢出和进位标志,并封装成模块。

模块的端口描述如下:module lab2_RippleCarry 宽度可定制(默认为4位)的行波进位有符号数的加减法器。

#(parameter WIDTH=4)( input signed [WIDTH-1:0] dataa,input signed [WIDTH-1:0] datab,input add_sub, // if this is 1, add; else subtractinput clk,input cclr,input carry_in, //1 表示有进位或借位output overflow,output carry_out,output reg [WIDTH-1:0] result)2、修改上述运算器的进位算法,设计超前进位无符号加法算法器并封装成模块。

模块的端口描述如下:module lab2_LookaheadCarry // 4位超前进位无符号加法器(input [3:0] a,input [3:0] b,input c0, //carry_ininput clk,input cclr,output reg carry_out,output reg [3:0]sum);3、在上述超前进位加法运算器的基础上,用基于模块的层次化设计方法,完成一个32位的加法运算器,组内超前进位,组间行波进位。

4、用宏模块的方法实现一个32位加减运算器。

三、实验内容1、用VERILOG设计完成一个4位行波进位的加减法运算器,要求有溢出和进位标志,并封装成模块。

加法器的设计与仿真 湖南大学实验报告

数字电路实验报告实验名称加法器的设计与仿真一、实验内容:1.用VHDL语言设计全加器;2.利用设计的全加器组成串行加法器;3.用VHDL语言设计并行加法器。

二、实验条件:实验室Maxplus II 数字设计软件VHDL语言三、实验原理与实验电路:1.全加器VHDL语言描述:LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;ENTITY f_adder ISPORT(x,y,Cin:IN STD_LOGIC;S,Cout:OUT STD_LOGIC);END f_adder;ARCHITECTURE bhv OF f_adder ISBEGINS<=x XOR y XOR Cin;Cout<=(x AND y)OR(x AND Cin)OR(y AND Cin);END ARCHITECTURE bhv;2.四位串行加法器VHDL语言:LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;ENTITY f_adder4 ISPORT(x0,x1,x2,x3:IN STD_LOGIC;y0,y1,y2,y3:IN STD_LOGIC;Cin:IN STD_LOGIC;S0,S1,S2,S3:OUT STD_LOGIC;Cout:OUT STD_LOGIC);END f_adder4;ARCHITECTURE f_adder4men OF f_adder4 IS COMPONENT f_adderPORT(x,y,cin:IN STD_LOGIC;s,cout:OUT STD_LOGIC);END COMPONENT;SIGNAL A,B,C:std_logic;BEGINU1:f_adder PORT MAP(Cin,x0,y0,S0,A);U2:f_adder PORT MAP(A,x1,y1,S1,B);U3: f_adder PORT MAP(B,x2,y2,S2,C);U4: f_adder PORT MAP(C,x3,y3,S3,Cout); END f_adder4men;3.74283:4位先行进位全加器(4-Bit Full Adder)VHDL语言:LIBRARY IEEE;USE ieee.std_logic_1164.ALL;ENTITY multi41 ISPORT(A0,A1,A2,A3,B0,B1,B2,B3: IN std_logic;P0,P1,P2,P3,P4,P5,P6,P7: OUT std_logic);END ENTITY;ARCHITECTURE multi1 of multi41 ISCOMPONENT f_adder4 ISPORT(x0,x1,x2,x3:IN STD_LOGIC;y0,y1,y2,y3:IN STD_LOGIC;Cin:IN STD_LOGIC;S0,S1,S2,S3:OUT STD_LOGIC;Cout:OUT STD_LOGIC);END COMPONENT;SIGNAL B01,B02,B03,B11,B12,B13,B14,B21,B22,B23,B24,B31,B32,B33,B34,U11,U12,U13,CI1,U21,U22,U23,CI2,GND: std_logic;BEGINGND<='0';-----------B0------------------P0<=A0 and B0;B01<=A1 and B0;B02<=A2 and B0;B03<=A3 and B0;------------B1-------------------B11<=A0 and B1;B12<=A1 and B1;B13<=A2 and B1;B14<=A3 and B1;U1:f_adder4 PORT MAP(x0=>B01,x1=>B02,x2=>B03,x3=>GND,Cin=>GND,y0=>B11,y1=>B12,y2=>B13,y3=>B14,S0=>P1,S1=>U11,S2=>U12,S3=>U13,Cout=>CI1);------------B2--------------------B21<=A0 and B2;B22<=A1 and B2;B23<=A2 and B2;B24<=A3 and B2;U2:f_adder4 PORT MAP(x0=>U11,x1=>U12,x2=>U13,x3=>CI1,Cin=>GND,y0=>B21,y1=>B22,y2=>B23,y3=>B24,S0=>P2,S1=>U21,S2=>U22,S3=>U23,Cout=>CI2);--------------B3------------------------B31<=A0 and B3;B32<=A1 and B3;B33<=A2 and B3;B34<=A3 and B3;U3:f_adder4 PORT MAP(x0=>U21,x1=>U22,x2=>U23,x3=>CI2,Cin=>GND,y0=>B31,y1=>B32,y2=>B33,y3=>B34,S0=>P3,S1=>P4,S2=>P5,S3=>P6,Cout=>P7);end multi1;四、实验测试数据记录表:全加器:四位串行加法器:四位先行进位全加器:四、实验总结(问题、看法、建议和创意):实际实验结果与理论结果有一定的不同,体现了逻辑电路的延缓性。

模电加法器仿真实验报告

1、学习加法器的设计方法。

2、掌握加法器的调试方法。

3、熟练焊接技术。

二、实验仪器信号源,示波器,直流稳压源,交流毫伏表,万用表,电路板。

三、试验器件编号名称型号数量R1、R2、R3、R4、R7 电阻10K 5R5、R6、Rf1、Rf2 电阻20K 4T1、T2 集成运放HA17741 2四、实验原理集成运算放大器是提高电压增益的直流放大器。

在它的输入端和输出端之间加上不同的反馈网络,就可以实现各种不同的电路功能。

可实现放大功能及加、减、微分、积分等模拟信号运算功能。

本实验着重以输入和输出之间施加线性负反馈网络后所具有的功能运算的研究。

理性运放在线性运用时具有以下重要特性:1、理想运放的同向和反向输入端电流近似为零,即I+≈0,I-≈0。

2、理想运放在线性放大区时,两端输入电压近似相等,即:U+≈U-。

加法器根据信号输入端的不同有同相加法器和反向加法器两种形式。

原理如图所示:图1 同相加法器图2 反相加法器图2的反向加法器,运放的输入端一端接地,另一端由于理想运放的“虚地”特性,使得加在此输入端的多路输入电压可以彼此独立地通过自身输入回路电阻转换为电流,精确地进行代数相加运算,实现加法功能。

同相加法器的输出电压为Uo=(1+Rf/R1)Rp(Ui1/R2+Ui2/R3)式中,Rp=R2//R3。

因此Rp与每个回路电阻均有关,要求满足一定的比例关系,调节不便。

反相加法器的输出电压为Uo=-【(Rf/R1)Ui1+(Rf/R1)Ui2)】,当R1=R2=Rf时,Uo=-(Ui1+Ui2)。

五、实验电路图Uo1=-Rf1(Ui1/R1+Ui2/R2)Uo =(-Rf2/R4)Uo1= (Rf2 Rf1/R4 R1)Ui1+(Rf2 Rf1/R4 R2)Ui2六、实验内容及步骤1、实验内容用两个HA17741运算放大器,10K,20K,100K电阻设计一个加法器。

工作电压为+12V、-12V。

设计出的加法器电路如上图所示。

加法器实验报告

加法器实验报告加法器实验报告随着社会一步步向前发展,报告与我们的生活紧密相连,报告具有双向沟通性的特点。

在写之前,可以先参考范文,以下是小编为大家整理的加法器实验报告,仅供参考,大家一起来看看吧。

加法器实验报告1一、实验目的1、了解加法器的基本原理。

掌握组合逻辑电路在Quartus Ⅱ中的图形输入方法及文本输入方法。

2、学习和掌握半加器、全加器的工作和设计原理3、熟悉EDA工具Quartus II和Modelsim的'使用,能够熟练运用Vrilog HDL语言在Quartus II下进行工程开发、调试和仿真。

4、掌握半加器设计方法5、掌握全加器的工作原理和使用方法二、实验内容1、建立一个Project。

2、图形输入设计:要求用VHDL结构描述的方法设计一个半加器3、进行编译,修改错误。

4、建立一个波形文件。

(根据真值表)5、对该VHDL程序进行功能仿真和时序仿真Simulation三、实验步骤1、启动QuartusⅡ2、建立新工程NEW PROJECT3、设定项目保存路径\项目名称\顶层实体名称4、建立新文件Blok Diagram/Schematic File5、保存文件FILE /SAVE6、原理图设计输入元件符号放置通过EDIT>SYMBOL插入元件或点击图标元件复制元件转动元件删除管脚命名PINNAME元件之间连线(直接连接,引线连接)7、保存原理图8 、编译:顶层文件设置,PROJECT>Set as TopLevel开始编译processing>Start Compilation编译有两种:全编译包括分析与综合(Analysis&Synthesis)、适配(Fitter)、编程(assembler)时序分析(Classical Timing Analysis)4个环节,而这4个环节各自对应相应菜单命令,可单独发布执行也可以分步执行9 、逻辑符号生成FILECreat/update>create Symbol File forCurrent File10 、仿真建立仿真wenjian添加需要的输入输出管脚设置仿真时间设置栅格的大小设置输入信号的波形保存文件,仿真功能仿真:主要检查逻辑功能是否正确,功能仿真方法如下:1TOOL/SIMULATOR TOOL,在SIMULATOR MODE下选择Functional,在SIMULATION INPUT栏中指定波形激励文件,单击Gencrator Functional Simulator Netist,生成功能仿真网表文件。

16位加法器设计报告(1)

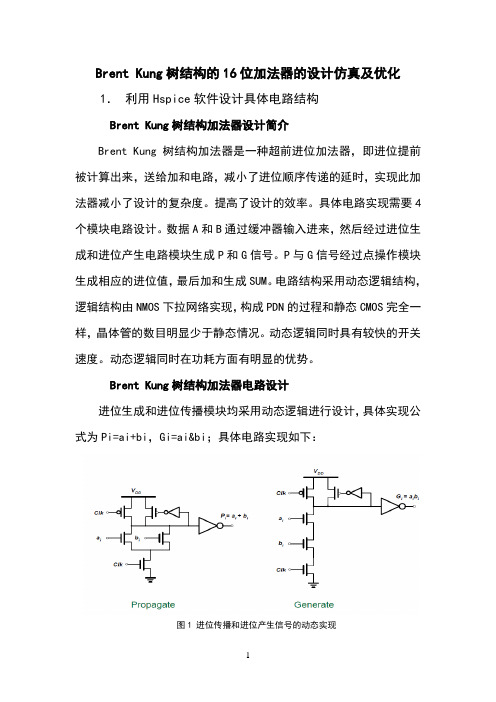

Brent Kung树结构的16位加法器的设计仿真及优化1.利用Hspice软件设计具体电路结构Brent Kung树结构加法器设计简介Brent Kung树结构加法器是一种超前进位加法器,即进位提前被计算出来,送给加和电路,减小了进位顺序传递的延时,实现此加法器减小了设计的复杂度。

提高了设计的效率。

具体电路实现需要4个模块电路设计。

数据A和B通过缓冲器输入进来,然后经过进位生成和进位产生电路模块生成P和G信号。

P与G信号经过点操作模块生成相应的进位值,最后加和生成SUM。

电路结构采用动态逻辑结构,逻辑结构由NMOS下拉网络实现,构成PDN的过程和静态CMOS完全一样,晶体管的数目明显少于静态情况。

动态逻辑同时具有较快的开关速度。

动态逻辑同时在功耗方面有明显的优势。

Brent Kung树结构加法器电路设计进位生成和进位传播模块均采用动态逻辑进行设计,具体实现公式为Pi=ai+bi,Gi=ai&bi;具体电路实现如下:图1 进位传播和进位产生信号的动态实现图中的反相器为对称的,p生成电路的逻辑努力为2/3,g生成电路的逻辑努力为1。

点计算模块具体生成对应的进位传播和进位产生Gi j和Pi j;其对应的具体公式为:Gi j=Gi k+Pi k*Gk-1 j。

采用动态逻辑减小复杂度具体电路结构如下:图2点模块电路产生信号的动态实现求和电路利用多米诺实现求和即利用选择电路实现电路结构,在此电路中求和的两种条件计算为:Si0为ai与bi的同或,Si1为ai 与bi的异或,具体电路结构如下:图5动态逻辑实现和选择电路电路中利用两个时钟,由clk产生clkd是由下面的电路实现的,传输门总是导通,时钟路径的延时可以通过这些器件的尺寸来调整。

因为延时必须有一个严格的界限,即第二个门的所有输入必须在clkd的上升沿之前完成翻转,因此可能需要使clk进过多个以下的延时电路才能满足时序要求。

时钟延时利用反向器的缓冲器和传输门来实现。

EDA实验二(加法器设计)

实验一、EDA软件及PLD器件的设计应用

2015级电子信息工程

1515212024 罗宏刚

一、四位加法计数器的设计

1.VHDL语言输入。

2.全程编译成功。

3.功能仿真。

4.仿真波形及结果。

5.封装

二、七段数码显示译码器的设计

1.VHDL语言输入。

2.全程编译成功。

3.功能仿真。

4.仿真波形及结果。

5.封装

三、含七段数码显示译码的4位加法器的设计

1.原理图输入。

2.全程编译成功。

3.功能仿真。

4.仿真波形及结果。

5.封装。

四、硬件验证部分

1.将实验箱与电脑相连接,点击菜单栏的TOOL中的Programmer进行硬件实验。

2.在电路结构图中设置,找出引脚名和然后找出引脚名所对应的位置的引脚号,然后将此引脚号输入quarts中pins端口的芯片位置。

(结构管脚电路图)(电路引脚对照图)

3.这里选择键6键7键8分别作为时钟、使能、重置端,分别对应PIN28、PIN30、PIN31。

4.设置硬件,并下载到FPGA进行硬件验证。

5.将数码管设置到模式6,开通电源后,通过键7使能打开,按键6可以在数码管看到跳变的数字,依次显示为:1,2,3,4,5,6,7,8,9,A,B,C,D,E,F,按键8可置零。

硬件验证成功。

加法器的设计与仿真实验报告

加法器的设计与仿真一、实验内容1、用逻辑图和VHDL语言设计全加器。

2、利用设计的全加器组成串行加法器。

3、用逻辑图和VHDL语言设计并行加法器。

4、应用MaxplusII软件对全加器和串行加法器进行编译、仿真和模拟。

5、在“MaxplusII软件的基本操作”实验的基础上,能更加熟练的掌握应用MaxplusII软件,从而更形象更深层次的理解全加器和串行加法器。

二、实验平台及实验方法用VHDL语言编写全加器和串行加法器的程序,运用MaxplusII软件进行仿真,再结合FPGA(即对实验箱的芯片进行编译)进行验证。

也可以用原理图进行文本设计,波形设计。

逻辑符号图:真值表:电路图:三、实验过程1.启动MaxplusII软件;2.新建一个文本编辑文件,输入全加器的VHDL语言;3.编译。

点击file save as,保存文件名为f-adder名称,扩展名为vhd,选择芯片类型为EPF10K20TI144-4,保存并进行编译,若编译结果出现0 error,0 warnings则说明编译通过。

4.仿真波形。

点Max+plus II→Waveform editor,出现波形图的设置界面,然后点Node→Enter Nodes from SNF→list,将输入输出端添加到界面,并设置其周期和输入波形,保存后,点Max+plus II→Simulator,即可仿真出输出的波形。

5.配置芯片。

点Max+plus II→Floorplan editor,将Unassigned Nodes & 栏中,电路的输入输出节点标号直接用鼠标“拖到” 想分配的引脚上,Max+plusII→programmer→configuer,然后就可以操作试验箱,观察全加器的工作情况。

四、实验结果实验步骤:1、用VHDL语言编写全加器的程序LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;ENTITY f_adder ISPORT(x,y,cin:IN STD_LOGIC;s,cout:OUT STD_LOGIC);END ENTITY f_adder;ARCHITECTURE bhv OF f_adder ISBEGINs<=x XOR y XOR cin;cout<=(x AND y)OR(x AND cin)OR(y AND cin);END ARCHITECTURE bhv;2、将上述程序保存为文件名为f_adder的文件,点击Maxplus里的compiler进行编译,点击start,如果出现0 error,0 warnings,则编译成功。

03实验三 加法器的设计与应用

4位二进制加 数A 输入端

向高位片的 进位输出 本位和输出端 相加结果读数为 C0S3S2S1S0

4位二进制加 数B 输入端 低位片进位输入端

74LS283逻辑符号

四、实验内容及步骤

1.用基本门电路实现全加器电路。

解:①逻辑抽象 输入变量: 被加数为A,加数为B 由低位来的进位为Ci 输出变量: 相加后本位和为S 往高位的进位为Co

i i

1

1

BCi A 00 01 0 1 1

11 1

1

10

1

Co A BC i A B C i AB C i ABC ( A B ) C i AB ( A B ) C i AB

四、实验内容及步骤

③逻辑电路图

用一片74LS00和一片74LS86即可实现。

四、实验内容及步骤

如:

要考虑低位 来的进位

0 0 0 1

全加器实现

+ 0 0 1 1

进位

1 1 01 0 0

不考虑低位 来的进位

半加器实现

三、实验原理

多个一位全加器进行级联可以得到多位全加器。 74ls283是采用快速进位的四位二进制全加器.与之 类似的还有 74ls83等。

83管脚图

三、实验原理

A4 A3 A2 A1 B4 B3 B2 B1 CI ∑ CO S4 S3 S2 S1 S4 S3 S2 S1

END

兰州交通大学 国家级电工电子实验教学示范中心

真值表

A 0 0 0 0 1 1 1 1

B 0 0 1 1 0 0 1 1

Ci 0 1 0 1 0 1 0 1

S 0 1 1 0 1 0 0 1

Co 0 0 0 1 0 1 1 1

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

加法器的设计与仿真

1.实验目的

a.用逻辑图和VHDL语言设计全加器;

b.利用设计的全加器组成串行加法器;

c.用逻辑图和VHDL语言设计并行加法器。

2.实验内容的详细说明

2.1 全加器

2.1.1 设计思想

先定义三个输入两个输出的实体,再定义结构体,一端输出等于三个输入信号之间的异或,另一个输出端等于三个输入信号每两个的乘积之和。

2.1.2 实验原理

1)全加器逻辑图

全加器逻辑图

2)全加器真值表

2.1.3 VHDL程序(详见附录1)

2.1.4 仿真结果

全加器VHDL仿真波形图

全加器画图仿真波形图

2.2 四位串行加法器

2.2.1 设计思想

利用四个全加器,每一个全加器对应二进制的一个位数的计算,上一个位数的进位输出接入下一个的进位输入。

2.2.2 实验原理

1)四位串行加法器逻辑图

四位串行加法器逻辑图

2)四位串行加法器真值表(略)

2.2.3 VHDL程序(略)

2.2.4 仿真结果

四位串行加法器功能仿真波形图

2.3 74283:4位先行进位全加器(4-Bit Full Adder)

2.3.1 设计思想

使用74283芯片,CIN=0时,每一个S等于对应A和B以及上一个位的进位相加。

2.3.2 实验原理

1)4位先行进位全加器逻辑图

4位先行进位全加器逻辑图

2)4位先行进位全加器逻辑功能表

2.3.3 VHDL程序(略)

2.3.4 仿真结果

4位先行进位全加器仿真波形图

3.实验总结:

通过本次实验,我对三态门和OC门的逻辑功能有进一步的了解,觉得三态门用在总线传输上,有效而又灵活地控制多组数据在总线上通行,起着交通信号灯的作用,而OC门则可以实现线与的功能。

4.附录(VHDL程序)

4.1 附录1

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

ENTITY f_adder IS

PORT(

x,y,cin : IN STD_LOGIC;

s,cout : OUT STD_LOGIC

);

END ENTITY f_adder;

ARCHITECTURE bhv OF f_adder IS

BEGIN

s<=x XOR y XOR cin;

cout<=(x AND y)OR(x AND cin)OR(y AND cin);

END ARCHITECTURE bhv;。