飞思卡尔单片机寄存器及汇编指令详解

(整理)飞思卡尔寄存器整理

S12的输入/输入端口(I/O口)I/O端口功能可设置为通用I/O口、驱动、内部上拉/下拉、中断输入等功能。

设置I/O口工作方式的寄存器有:DDR、IO、RDR、PE、IE和PS。

DDR:设定I/O口的数据方向。

IO :设定输出电平的高低。

RDR:选择I/O口的驱动能力。

PE:选择上拉/下拉。

IE:允许或禁止端口中断。

PS:1、中断允许位置位时,选择上升沿/下降沿触发中断;2、中断禁止时且PE有效时,用于选择上拉还是下拉。

I/O端口设置1、A口、B口、E口寄存器(1)数据方向寄存器DDRA、DDRB、DDREDDRA、DDRB、DDRE均为8位寄存器,复位后其值均为0。

当DDRA=0、DDRB=0、DDRE=0 时A口、B口和E口均为输入口。

否则,A口、B口、E口为输出口。

当DDRA、DDRB、DDRE的任何一位置1时,则该位对应的引脚被设置为输出。

例如,将A口设置为输出口,则其C语言程序的语句为:DDRA=0xff;(2)A口、B口、E口上拉控制寄存器PUCRPUCR为8位寄存器,复位后的值为0。

当PUPAE、PUPBE、PUPEE被设置为1时,A口、B口、E口具有内部上拉功能;为0时,上拉无效。

当A口、B口、E口为地址/数据总线时,PUPAE和PUPBE无效。

(3)A口、B口、E口降功率驱动控制寄存器RDRIVRDRIV为8位寄存器,复位后的值为0,此时,A口、B口、E口驱动保持全功率;当RDPA、RDPB、RDPE为1时,A口、B口、E口输出引脚的驱动功率下降(4)数据寄存器PORTA、PORTB、PORTEPORTA、PORTB、PORTE均为8位寄存器,复位后的值为0,端口引脚输出低电平;要使引脚输出高电平,相应端口对应位应该置1。

由于PE0是/XIRQ、PE1是IRQ,因此,PE0和PE1只能设置为输入。

2、H口寄存器(1)H口I/O寄存器PTH任意时间读/写。

当某一引脚对就的数据方向位设置为1时,读操作返回的是这个端口寄存器的值;否则,读的是引脚的值。

飞思卡尔MC9S12XS128单片机各模块使用方法及寄存器配置

飞思卡尔MC9S12XS128单片机各模块使用方法及寄存器配置手把手教你写S12XS128程序--PWM模块介绍该教程以MC9S12XS128单片机为核心进行讲解,全面阐释该16位单片机资源。

本文为第一讲,开始介绍该MCU的PWM模块。

PWM 调制波有8个输出通道,每一个输出通道都可以独立的进行输出。

每一个输出通道都有一个精确的计数器(计算脉冲的个数),一个周期控制寄存器和两个可供选择的时钟源。

每一个P WM 输出通道都能调制出占空比从0—100% 变化的波形。

PWM 的主要特点有:1、它有8个独立的输出通道,并且通过编程可控制其输出波形的周期。

2、每一个输出通道都有一个精确的计数器。

3、每一个通道的P WM 输出使能都可以由编程来控制。

4、PWM 输出波形的翻转控制可以通过编程来实现。

5、周期和脉宽可以被双缓冲。

当通道关闭或PWM 计数器为0时,改变周期和脉宽才起作用。

6、8 字节或16 字节的通道协议。

7、有4个时钟源可供选择(A、SA、B、SB),他们提供了一个宽范围的时钟频率。

8、通过编程可以实现希望的时钟周期。

9、具有遇到紧急情况关闭程序的功能。

10、每一个通道都可以通过编程实现左对齐输出还是居中对齐输出。

1、PWM启动寄存器PWMEPWME 寄存器每一位如图1所示:复位默认值:0000 0000B图1 PWME 寄存器每一个PWM 的输出通道都有一个使能位P WMEx 。

它相当于一个开关,用来启动和关闭相应通道的PWM 波形输出。

当任意的P WMEx 位置1,则相关的P WM 输出通道就立刻可用。

用法:PWME7=1 --- 通道7 可对外输出波形PWME7=0 --- 通道7 不能对外输出波形注意:在通道使能后所输出的第一个波形可能是不规则的。

当输出通道工作在串联模式时(PWMCTL 寄存器中的CONxx置1),那么)使能相应的16位PWM 输出通道是由PWMEx 的高位控制的,例如:设置PWMCTL_CON01 = 1,通道0、1级联,形成一个16位PWM 通道,由通道 1 的使能位控制PWM 的输出。

飞思卡尔单片机快速上手指南说明书

Freescale Semiconductor, Inc.Document Number: 用户指南 Rev. 0, 09/2014Confidentiality statement, as appropriate to document/part status.___________________________________________________________________飞思卡尔单片机快速上手指南作者:飞思卡尔半导体IMM FAE 团队飞思卡尔半导体是全球领先的单片机供应商,其单片机产品包含多种内核,有数百个系列。

为支持用户使用这些产品,飞思卡尔提供了丰富的网站资源、文档及软硬件工具,另外,我们还有众多的第三方合作伙伴及公共平台的支持。

对于不熟悉飞思卡尔产品和网站的初学者来说,了解和使用这些资源这无疑是一个令人望而生畏的浩瀚工程。

本指南的目的,就是给初学者提供一个指导,让他们不被这些海量信息淹没;用户根据本指导提供的操作步骤,能迅速找到所需的资源,了解如何使用相关的工具。

在本指南中,我们以飞思卡尔的新一代Kinetis 单片机K22系列为例,介绍了如何获取与之相关的资源,如何对其进行软硬件设计和开发。

实际上,这些方法也适用于其它的单片机系列。

当然,对于其它有较多不同之处的产品,我们也会继续推出相应的文档,供广大用户参考。

目录1 如何获取技术资料与支持 ..........................................................2 2 如何选择产品、申请样片及购买少量芯片和开发工具 ........... 93 飞思卡尔单片机的开发环境、开发工具和生态系统 ............. 224 如何阅读飞思卡尔的技术文档 ................................................ 45 5 飞思卡尔单片机硬件设计指南 ................................................ 55 6飞思卡尔单片机软件开发指南 (67)飞思卡尔单片机快速上手指南, Rev. 1, 09/20142Freescale Semiconductor, Inc.1 如何获取技术资料与支持1.1 概述当用户使用飞思卡尔单片机芯片时,如何获取芯片的数据手册(Datasheet )、参考设计(Reference Manual )和官方例程等资源呢?另外当用户遇到了技术问题该如何获得帮助和解答呢?这里以Kinetis 的K22系列芯片为例为大家介绍如何解决这些问题。

飞思卡尔16位单片机寄存器总结

一、输入输出端口寄存器I/O接口包括PORTA、B、E、K、T、S、M、P、H、J、AD。

其中PORTA、B、E、K属于复用扩展总线接口,单片机在扩展方式下工作时,作为总线信号。

1、PORTT、S、M、P、H、JI/O寄存器PTx如果对应位数据方向寄存器DDRx为“0”,输入,读取该寄存器返回引脚值;“1”,输出,读取该寄存器返回I/O寄存器的内容。

数据方向寄存器DDRx决定对应引脚为输出还是输入,“0”为输入,“1”为输出,复位后,默认为输入。

上拉/下拉使能寄存器PERx选择使用内置上拉/下拉器件,“1”允许,“0”禁用。

中断使能寄存器PIExPORTP、H、J三个端口具有中断功能。

“1”对应引脚允许中断,“0”禁止,复位后,所有端口中断关闭。

中断标志寄存器PIFxPORTP、H、J三个端口具有中断功能。

“1”对应引脚允许中断,“0”禁止,复位后,所有端口中断关闭。

2、PORTA、B、E、KI/O寄存器Px若某端口的引脚被定义为输出,写入I/O寄存器中的数值会从对应引脚输出;输入,通过I/O寄存器读取对应引脚电平。

数据方向寄存器DDRx决定对应引脚为输出还是输入,“0”为输入,“1”为输出,复位后,默认为输入。

PORTE最低两位只能为输入。

上拉电阻控制寄存器PERx第7、4、1、0位分别控制K、E、B、A端口,“1”允许使用对应端口的上拉电阻,“0”禁止,复位后,PK、PE端口使能,PB、PA禁止。

二、中断系统中断控制寄存器INTCR第7位IRQE,中断电平/边沿有效选择,0为低电平有效,1为下降沿有效;第6位IRQEN,外部中断IRQ中断请求使能,0关闭,1允许。

三、PWM模块PWM允许寄存器PWME对应每一位PWMEx,1启动输出,0停止输出,读写任意时刻。

PWM预分频时钟选择寄存器PWMPRCLK为Clock A和B选择独立的预分频因子,读写任意时刻。

Clock B对应6、5、4三位,Clock A对应2、1、0三位,分别可以实现2、4、8、16、32、64、128分频。

飞思卡尔8位单片机MC9S08第5章 HC08 CPU与汇编基础

5.2 寻址方式

(6)八位偏移量变址方式(IX1,Indexed,8-bit offset addressing mode)

8位偏移量变址是双字节指令,CPU把变址寄存器HX的内容和指令 第二个字节内容相加,其和便是操作数地址。下述指令属于IX1寻址方 式。

5.1 HC08 CPU基本构成

(4)程序计数器PC(Program Counter)

程序计数器PC也是16位的,可寻址范围达64KB。PC存放下一 条指令的地址,在执行转移指令时存放转移地址,在执行中断指令时 存放中断子程序入口地址。复位时,程序计数器PC装入地址$FFFE 和$FFFF中的内容。一般地,地址$FFFE和$FFFF中的内容是复位的 入口地址,这样,复位后,程序能够从复位入口地址开始执行程序。 复位入口地址也称复位向量地址或复位矢量地址(Reset vector address),意味着复位状态过后,PC指向该处,从这里执行程序。

(9)存储器:直接地址—直接地址寻址方式(DD, Direct to direct addressing Mode)

在存储器的四种数据直接传送的寻址方式中,欲传送的数据直接从 源存储单元送向目的存储单元,勿需寄存器中转。在本寻址方式中,源 地址与目标地址由指令直接给出。只有一条指令为DD寻址方式:

CBEQ addr8,X+,rel ;若A=(HX+addr8)则转移,HX+1→HX

(2)立即寻址方式(IMM,Immediate addressing mode)

立即寻址,是在指令中直接给出操作数。这种指令是双字节指令, 第一个字节是操作码,第二个字节是参与操作的立即数。立即寻址指令 通常是对立即数和累加器内容或变址寄存器内进行操作。下述指令属于 IMM寻址方式。

飞思卡尔单片机 第1节-CPU寄存器

CPU寄存器

CPU寄存器

累加器 (A) 累加器A是一个通用8位寄存器。经常用于暂存一个输入到算 术逻辑单元(ALU)的操作数,并且用于存放(ALU)的计算结果。 复位对累加器A的内容没有影响。 索引寄存器(H:X) 这个16位寄存器实际上分为两个8位寄存器(H和X),它们作为 一个16位的地址指针一起工作,H存放一个地址的高位字节 和X存放地址的低位字节。所有索引寻址模式指令利用H:X中 全部16位值作为一个索引参考指针;然后,为了与早先 M68HC05家族兼容,一些指令只在低8位(X)中运行,并且H在 复位过程中强制为0x00。复位对X的内容没有影响。

HCS08 CPU的特点包括:

▪目标代码完全向上兼容M68HC05和M68HC08家族 ▪所有寄存器和存储器映射在单块64 Kbyte地址空间 ▪16位堆栈指针SP(64 Kbyte地址空间中的任意大小堆栈) ▪16位索引寄存器(H:X)的强大的寻址索引模式 ▪多种寻址模式 ▪8位累加器(A) ▪支持存储器到存储器的数据传送 ▪高效的位操作指令 ▪快速的8位乘8位和16位除以 8位指令 ▪STOP和WAIT指令唤醒低功耗运行状态

条件代码寄存器(CCR) 条件代码寄存器 8位条件代码寄存器存放中断屏蔽位(I)和5个指出刚执行指令 结果的标志。第5和第6位永远设置为1。如图:

I 位是中断屏蔽控制位,与其他位不同的是它在CCR 中不是处 理器状况位。在CCR的六个可执行位中,I 位也是复位后唯一可 被初始化的位。I 位复位后置为1,这使得中断被屏蔽直到堆栈 指针被初始化。其他五个状态位(V、H、N、Z 和C)在复位后是 未知的,只有在执行一个指令后才能知道。复位后无须强制这 些位为特定的值,因为直到执行了一个影响它们的指令后,与 这些位相关的条件转移才有意义。 这五个状态位标志了运算和其他指令的结果。条件转移指令 根据CCR 内状态位的值来决定是直接转移到一个新的程序地址, 还是继续执行下一个指令。简单的条件转移指令(BCC、BCS、 BNE、BEQ、BHCC、BHCS、BMC、BMS、BPL 和BMI)所导 致的转移取决于单一的CCR 位状态,而其他转移指令则被两三 个更复杂的CCR 位控制。例如,若布尔表达式[(Z) | (N⊕V)]真, 则将产生小于等于转移(BLE).

飞思卡尔8位单片机—飞思卡尔8位单片机基础知识

2.2、单片机的命名规则及选择

2.2.1、单片机选型需要关心的事项

供电电压、速度及功耗 管脚数量、并口与串口、功能复用、外扩能力 存储器资源:ROM、RAM、是否分页 外设接口 定时器数量、PWM、捕捉、比较 SPI、IIC、UART、CAN、USB、YITAI 中断源 模拟量处理 特殊接口:VGA、LCD、MOTOR 封装

选型要学会查找资源差异表

Freescale的08系列单片机型号有一百多种。在 这些不同型号的单片机中,资源各不相同,即使 是同一种型号的单片机,也有多种封装形式,其 I/O引脚数目也不相同。如MC68HC908JB8就有 20脚的DIP、28脚的SOIC、44脚的QFP和20脚 的SOIC四种封装形式。

7〉 管脚的复用

注意: 0、管脚功能复用时的优先 级见右表,高优先级接管管 脚时,对低优先级模块会产 生杂乱信号,因此切换前应 先停止不使用的功能。 1、PTA5作为只能输入管脚 而言,输入电压不能超过 VDD。 2、IIC使用的端口可以通过 设置SOPT2 寄存器中的 IICPS位重新定位到PTB6和 PTB7,复位时缺省使用 PTA2 and PTA3。 3、如果ACMP和ADC被同 时使能,管脚PTA0和PTA1 可同时使用。

第二章 飞思卡尔8位单片机基础知识

2.1、飞思卡尔8位单片机系列简介 2.2、飞思卡尔单片机命名规则与单片机选型 2.3、 MC9S08QG8硬件结构

8bit 单片机的Core type

HC08系列、HCS08系列、RS08系列。 HC08是1999年开始推出的产品,种类多,针对不同场合 的应用都可以选到合适的型号。 HCS08是2004年左右推出的8位MCU,资源丰富,功耗 低,性价比高,是08系列单片机的发展趋势。HC08与 HCS08的最大区别是调试方法不同与最高频率的变化 。 RS08是HCS08架构的简化版本,2006年推出,其内核体 积比传统的内核小30%,带有精简指令集,满足用户对 体积更小、更加经济高效的解决方案的需求。RAM及 Flash空间大小差异、封装形式不同、温度范围不同、 频率不同、I/O资源差异等形成了不同型号,为嵌入式 应用产品的开发提供了丰富的选型。

飞思卡尔单片机 DG128 Timer寄存器说明

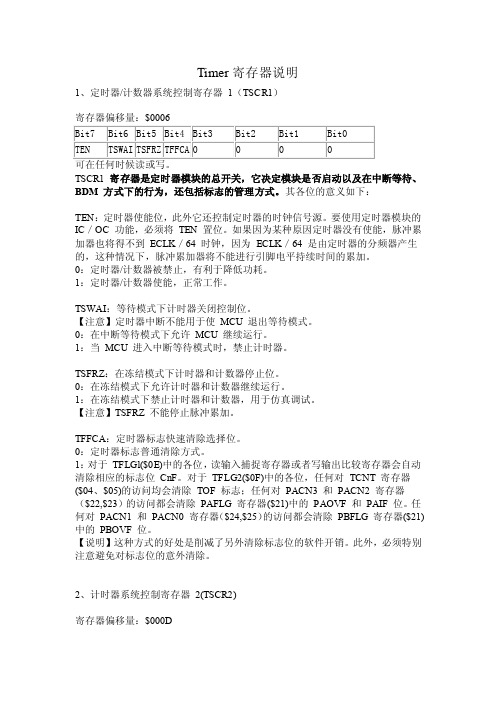

Timer寄存器说明1、定时器/计数器系统控制寄存器1(TSCR1)TSCR1 寄存器是定时器模块的总开关,它决定模块是否启动以及在中断等待、BDM 方式下的行为,还包括标志的管理方式。

其各位的意义如下:TEN:定时器使能位,此外它还控制定时器的时钟信号源。

要使用定时器模块的IC/OC 功能,必须将TEN 置位。

如果因为某种原因定时器没有使能,脉冲累加器也将得不到ECLK/64 时钟,因为ECLK/64 是由定时器的分频器产生的,这种情况下,脉冲累加器将不能进行引脚电平持续时间的累加。

0:定时器/计数器被禁止,有利于降低功耗。

1:定时器/计数器使能,正常工作。

TSWAI:等待模式下计时器关闭控制位。

【注意】定时器中断不能用于使MCU 退出等待模式。

0:在中断等待模式下允许MCU 继续运行。

1:当MCU 进入中断等待模式时,禁止计时器。

TSFRZ:在冻结模式下计时器和计数器停止位。

0:在冻结模式下允许计时器和计数器继续运行。

1:在冻结模式下禁止计时器和计数器,用于仿真调试。

【注意】TSFRZ 不能停止脉冲累加。

TFFCA:定时器标志快速清除选择位。

0:定时器标志普通清除方式。

1:对于TFLGl($0E)中的各位,读输入捕捉寄存器或者写输出比较寄存器会自动清除相应的标志位CnF。

对于TFLG2($0F)中的各位,任何对TCNT 寄存器($04、$05)的访问均会清除TOF 标志;任何对PACN3 和PACN2 寄存器($22,$23)的访问都会清除PAFLG 寄存器($21)中的PAOVF 和PAIF 位。

任何对PACN1 和PACN0 寄存器($24,$25)的访问都会清除PBFLG 寄存器($21)中的PBOVF 位。

【说明】这种方式的好处是削减了另外清除标志位的软件开销。

此外,必须特别注意避免对标志位的意外清除。

2、计时器系统控制寄存器2(TSCR2)寄存器偏移量:$000DTOI:定时器/计时器溢出中断使能。

飞思卡尔单片机教程

注 : A/D模块的时钟频率要在500KHz和2MHz之间, 所以在选择分频因子时一定要注意。

采样时间选择

SMP [1 :0]

采样时间

00

2个 A/D时钟周期

01

4个A/D时钟周期

ATDclock= ( (BusClock) / (PRS+1) ) /2

10

8个A/D时钟周期

11

16个A/D时钟周期

设CCBCA = 000,转换序列从通道

0开始;ATD0DR0,

ATD0DR1,ATD0DR2存放转换结果

设CCBCA = 0 10,转换序列从通道 2开始。 仍然是ATD0DR0,

ATD0DR1,ATD0DR2存放转换结果

S8C 、S4C 、S2C 、S1C:定义转换队列的长度 。默认长度为4。 FIFO: 结果寄存器先进先出模式 。1=FIFO模式 ,转换结果是连续 存放的;0=非FIFO模式 ,转换结果放在对应的寄存器中。 FRZ1、FRZ0:背景调试冻结模式允许 。这两个控制位就决定了,

{ while (ATD1STAT0_SCF ==0) ;

ad_value [0] = ATD1DR0; ad_value [4] = ATD1DR4;//使用 PORTB= (byte) ad_value [4] ;

}}

void ATDInit(void)

{ATD1CTL2=0xC0;//AD模块上电,快速清零,无等待模式,禁止外部触发, 中断禁止 // ADPU AFFC AWAI ETRIGLE --- ETRIGP ETRIGE ASCIE ASCIF

PRS=3

ATD1CTL5=0xA4; //右对齐无符号 ,单通道采样 ,通道0

飞思卡尔单片机 DG128 SCI寄存器说明

SCI寄存器说明1、波特率控制寄存器(SCIBDH、SCIBDL)IREN:红外调制模式使能位1 使能0 禁止TNP[0..1]:窄脉冲发射位SBR[0..12]:波特率设置位When IREN = 0 then,SCI baud rate = SCI bus clock / (16 x SBR[12:0])When IREN = 1 then,SCI baud rate = SCI bus clock / (32 x SBR[12:1])【说明】波特率发生器在复位后是禁止的,在设置TE、RE(在SCICR2寄存器中)后才会工作。

当(SBR[12:0] = 0 and IREN = 0) 或者(SBR[12:1] = 0 andIREN = 1),波特率发生器不工作。

【注意】在未写入SCIBDL,写SCIBDH没有反应。

一般地,设置IREN=0,SR=52(总线频率8MHz),波特率为9600。

2、数据寄存器(SCIDRH、SCIDRL)SCI 内部分别设有发送和接收两个数据寄存器,其低位都通过SCIDRL 访问,读操作返回接收数据寄存器RDR 的内容,写操作数据置入发送数据寄存器。

TDR。

当M=1 即运行在9 位数据模式时,SCIDRL 和SCIDRH 形成9 位的SCI数据字,这时必须先写入SCIDRH,以便与低位字节(SCIDRL)一起进入发送移位器。

如果M=0 即SCI 只用于7 位或8 位的数据传送,可以只访问SCIDRL。

当PE=1 即奇偶校验允许时,奇偶校验位由硬件负责,无需软件干预。

R8:接收到的位8,该位写操作无效。

当SCI 设置成9 位数据运行模式时,该位是从串行数据流中接收到的第9 位。

T8:发送位8,任何时候可写。

当SCI 设置成9 位数据模式时,该位是送到串行数据流的第9 位。

该位不必为每个数据重新设置,每次发送可重复使用。

R[0..7]T[0..7]:收/发数据位7-0,读操作返回只读寄存器RDR 的内容,写操作写入只写寄存器TDR。

飞思卡尔单片机寄存器及汇编指令详解

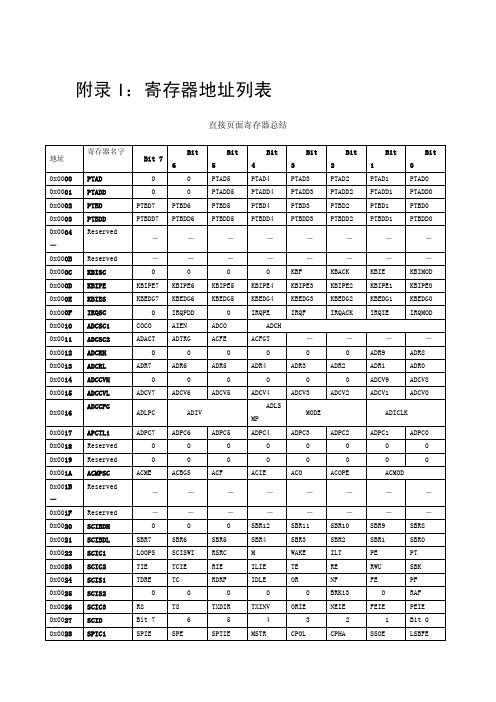

附录I:寄存器地址列表直接页面寄存器总结高页面寄存器总结非易失寄存器总结注:直接页面寄存器表地址的低字节用粗体显示,直接寻址对其访问时,仅写地址低字节即可。

第2列中寄存器名用粗体显示以区别右边的位名。

有0的单元格表示未用到的位总是读为0,有破折号的单元格表示未用或者保留,对其读不定。

附录II 指令接与寻址方式HCS08指令集概括运算符() = 括号种表示寄存器或存储器位置的内容← = 用……加载(读: “得到”)& = 布尔与| = 布尔或⊕= 布尔异或×= 乘÷ = 除: = 串联+ = 加- = 求反(二进制补码)CPU registersA =>累加器CCR =>条件代码寄存器H =>索引寄存器,高8位X => 索引寄存器,低8位PC =>程序计数器PCH =>程序计数器,高8位PCL =>程序计数器,低8位SP =>堆栈指针存储器和寻址M =>一个存储区位置或者绝对值数据,视寻址模式而定M:M + 0x0001 => 两个连续存储位置的16位值.高8位位于M的地址,低8位位于更高的连续地址.条件代码寄存器(CCR)位V => 二进制补码溢出指示,第7位H => 半进位,第4位I => 中断屏蔽,第 3位N => 求反指示器, 第2位Z => 置零指示器, 第1位C => 进/借, 第0位 (进位第 7位 )CCR工作性符号– => 位不受影响0 = > 位强制为01 = > 位强制为1= >根据运算结果设置或清除位U = > 运算后没有定义机器编码符号dd =>一个直接寻址0x0000–0x00FF的低8位(高字节假设为0x00)ee => 16位偏移量的高8位ff => 16位偏移量的低8位ii => 立即数的一个字节jj => 16位立即数值的高位字节kk => 16位立即数值的低位字节hh => 16位扩展寻址的高位字节ll => 16位扩展寻址的低位字节rr => 相对偏移量n —任何表达范围在0–7之间的一个有符号数的标号或表达式opr8i —任何一个表达8位立即值的标号或表达式opr16 —任何一个表达16位立即值的标号或表达式opr8a —任何一个表达一个8位值的标号或表达式.指令对待这个8位值为直接页面64K 字节地址空间(0x00xx)中地址的低8位.opr16a —任何一个表达16位值的标号或表达式.指令对待这个值为直接页面64K字节地址空间.oprx8 —任何一个表达8位无符号值的标号或表达式,用于索引寻址.oprx16 —任何一个16位值的标号或表达式.因为HCS08有一个16位地址总线,这可以为一个有符号或者无符号值.rel —任何指引在当前指令目标代码最后一个字节之后–128 to +127个字节之内的标号或表达式.汇编器会计算包括当前指令目标代码在内的8位有符号偏移量. 寻址方式隐含寻址(Inherent)如CLRA,只有操作码,无操作数,需要操作的数据一般为CPU寄存器,因此不需要再去找操作数了。

飞思卡尔单片机教学

串联方式(PE7引脚要拉低)

并联方式(PE7引脚要拉高)

a

29 29

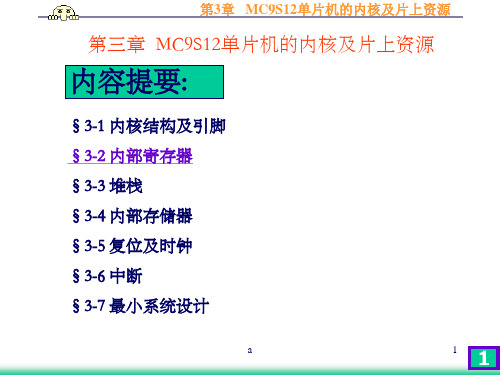

第3章 MC9S12单片机的内核及片上资源

时钟初始化寄存器-共5个

(1)锁相环控制寄存器(PLLCTL)

时钟监控允许位 1=允许 0=禁止

锁相环电路允许位 1=允许 0=禁止

注:其余各位的描述见教材49页。

a

30 30

第3章 MC9S12单片机的内核及片上资源

注:其余各位的描述

见教材49页和50页。

a

32 32

第3章 MC9S12单片机的内核及片上资源

PLL例子

CLKSEL=0x00; //禁止PLL PLLCTL=0xe1; //PLL电路允许 SYNR=2;REFDV=1; //设置倍频参数 PLLCTL=0x60; //时钟监控禁止 while(0==(CRGFLG&0x08));//等待稳定 CLKSEL=0x80; //选择PLL作为时钟 //若晶振为16M,则PLLCLK=2*16*3/2=48MHz,则总线频率是

R/W:读写信号,指示总线上数据方向 LSTRB:总线模式下低位字节(奇地址)选通 ECLK:内部总线时钟输出,一般在宽扩展模式下地址锁存用 BKGD(MODC)、MODB、MODA:模式选择 NOACC/XCLKS:当前外部总线操作无效

a

55

第3章 MC9S12单片机的内核及片上资源

模式选择

a

66

Block3

$C000~$FF00 16K($3F) Block2 Block1 Block0

16KB

$30 $31 $32 $33 $34 $35 $36 $37 $38 $39 $3A $3B $3C $3D $3E $3F

飞思卡尔单片机寄存器及汇编指令详解

附录I:寄存器地址列表直接页面寄存器总结高页面寄存器总结非易失寄存器总结注:直接页面寄存器表地址的低字节用粗体显示,直接寻址对其访问时,仅写地址低字节即可。

第2列中寄存器名用粗体显示以区别右边的位名。

有0的单元格表示未用到的位总是读为0,有破折号的单元格表示未用或者保留,对其读不定。

附录II 指令接与寻址方式HCS08指令集概括运算符() = 括号种表示寄存器或存储器位置的内容← = 用……加载(读: “得到”)& = 布尔与| = 布尔或⊕= 布尔异或×= 乘÷ = 除: = 串联+ = 加- = 求反(二进制补码)CPU registersA =>累加器CCR =>条件代码寄存器H =>索引寄存器,高8位X => 索引寄存器,低8位PC =>程序计数器PCH =>程序计数器,高8位PCL =>程序计数器,低8位SP =>堆栈指针存储器和寻址M =>一个存储区位置或者绝对值数据,视寻址模式而定M:M + 0x0001 => 两个连续存储位置的16位值.高8位位于M的地址,低8位位于更高的连续地址.条件代码寄存器(CCR)位V => 二进制补码溢出指示,第7位H => 半进位,第4位I => 中断屏蔽,第 3位N => 求反指示器, 第2位Z => 置零指示器, 第1位C => 进/借, 第0位 (进位第 7位 )CCR工作性符号– => 位不受影响0 = > 位强制为01 = > 位强制为1= >根据运算结果设置或清除位U = > 运算后没有定义机器编码符号dd =>一个直接寻址0x0000–0x00FF的低8位(高字节假设为0x00)ee => 16位偏移量的高8位ff => 16位偏移量的低8位ii => 立即数的一个字节jj => 16位立即数值的高位字节kk => 16位立即数值的低位字节hh => 16位扩展寻址的高位字节ll => 16位扩展寻址的低位字节rr => 相对偏移量n —任何表达范围在0–7之间的一个有符号数的标号或表达式opr8i —任何一个表达8位立即值的标号或表达式opr16 —任何一个表达16位立即值的标号或表达式opr8a —任何一个表达一个8位值的标号或表达式.指令对待这个8位值为直接页面64K 字节地址空间(0x00xx)中地址的低8位.opr16a —任何一个表达16位值的标号或表达式.指令对待这个值为直接页面64K字节地址空间.oprx8 —任何一个表达8位无符号值的标号或表达式,用于索引寻址.oprx16 —任何一个16位值的标号或表达式.因为HCS08有一个16位地址总线,这可以为一个有符号或者无符号值.rel —任何指引在当前指令目标代码最后一个字节之后–128 to +127个字节之内的标号或表达式.汇编器会计算包括当前指令目标代码在内的8位有符号偏移量. 寻址方式隐含寻址(Inherent)如CLRA,只有操作码,无操作数,需要操作的数据一般为CPU寄存器,因此不需要再去找操作数了。

飞思卡尔8位单片机MC9S08 06 通用IO与第一个汇编程序

主要内容 MC68HC908GP32的普通I/O 汇编程序编程框架 08汇编语言编译过程所涉及的文件 SD-HC08嵌入式MCU在线编程集成开发系统

6.1 MC68HC908GP32的普通 的普通I/O 的普通

所谓普通I/O,即基本的输入 输出 有时也称为并行I/O。 输出, 所谓普通 ,即基本的输入/输出,有时也称为并行 。作为普 通输入引脚, 内部程序可以读取该引脚, 通输入引脚,MCU内部程序可以读取该引脚,知道该引脚是“1”(高 内部程序可以读取该引脚 知道该引脚是“ ( 电平) ),即开关量输入 电平)或“0”(低电平),即开关量输入。作为普通输出引脚,MCU (低电平),即开关量输入。作为普通输出引脚, 内部程序向该引脚输出“ (高电平) ),即开关量 内部程序向该引脚输出“1”(高电平)或“0”(低电平),即开关量 (低电平), 输出。 单片机有5个普通 输出。MC68HC908GP32单片机有 个普通 口,分别是 口、B口、 单片机有 个普通I/O口 分别是A口 口 C口、D口、E口。它们中的大部分具有双功能,本节仅讨论它们作为 口 口 口 它们中的大部分具有双功能, 普通I/O功能时的编程方法。 普通 功能时的编程方法。 功能时的编程方法

6.1 MC68HC908GP32的普通I/O

6.1.1 A口 口

A口的 根引脚与键盘中断模块的引脚复用,这里只讨论 口作为 口的8根引脚与键盘中断模块的引脚复用 这里只讨论A口作为 口的 根引脚与键盘中断模块的引脚复用, 普通I/O口的功能 口的功能。 普通 口的功能。

(1)A口的寄存器 ) 口的寄存器

6.1 MC68HC908GP32的普通I/O

口数据方向寄存器( C,DDRC) ① C口数据方向寄存器(Data Direction Register C,DDRC) C口数据方向寄存器(DDRC)的地址是:$0006,由于对应引脚只 口数据方向寄存器( 口数据方向寄存器 )的地址是: , 的第6~ 位分别记为 位分别记为DDRC6~DDRC0, 有7根,最高位没有意义。DDRC的第 ~0位分别记为 根 最高位没有意义。 的第 ~ , 这些位分别控制着C口引脚 口引脚PTC6~PTC0是输入还是输出,含义参考 口 是输入还是输出, 这些位分别控制着 口引脚 ~ 是输入还是输出 含义参考A口 说明。复位时DDRC为$00。 说明。复位时 为 。 口数据寄存器( Register,PTC) ② C口数据寄存器(Port C Data Register,PTC) C口数据寄存器(PTC)的地址是:$0002,PTC的第 ~0位分别记 口数据寄存器( 的第6~ 位分别记 口数据寄存器 )的地址是: , 的第 口的相应说明。 为PTC6~PTC0。含义请类比 口、B口的相应说明。 ~ 。含义请类比A口 口的相应说明 口上拉电阻允许寄存器( ③ C口上拉电阻允许寄存器(Port C Input Pullup Enable Register,PTCPUE) Register,PTCPUE) C口上拉电阻允许寄存器(PTCPUE)的地址是:$000E。PTCPUE 口上拉电阻允许寄存器( 口上拉电阻允许寄存器 )的地址是: 。 的第6~ 位分别记为 位分别记为PTCPUE6~PTAPUE0。含义请类比 口的相应说明。 口的相应说明。 的第 ~0位分别记为 ~ 。含义请类比A口的相应说明

单片机飞思卡尔微处理器和指令集

B D

X Y

27

乘除法指令

EMUL Multiply(unsigned) EMULS Multiply(signed)

MUL Multiply(unsigned)

16 by 16 (D)×(Y)→Y:D 16 by 16 (D)×(Y)→Y:D 8 by 8 (A)×(B)→A:B

28

乘除法指令

LDAB LDD LDS LDX LDY LEAS LEAX LEAY Load Load Load Load Load Load Load Load

Load Accumulator A

B (M) →B D (M:M+1)→(A:B) SP (M:M+1)→(SPH:SPL) index register X index register Y Effective Address into SP Effective Address into X Effective Address into Y

3

16bit MCU Register file (11,12,S12)

7 15 6 GPAGE * 0 15 15 15 15 A 0 7 D X Y SP PC B 0 8-Bit Accumulators A and B 0 or 16-Bit Double Accumulator D 0 Index Register X 0 Index Register Y 0 Stack Pointer 0 Program Counter

飞思卡尔单片机外设模块寄存器翻译

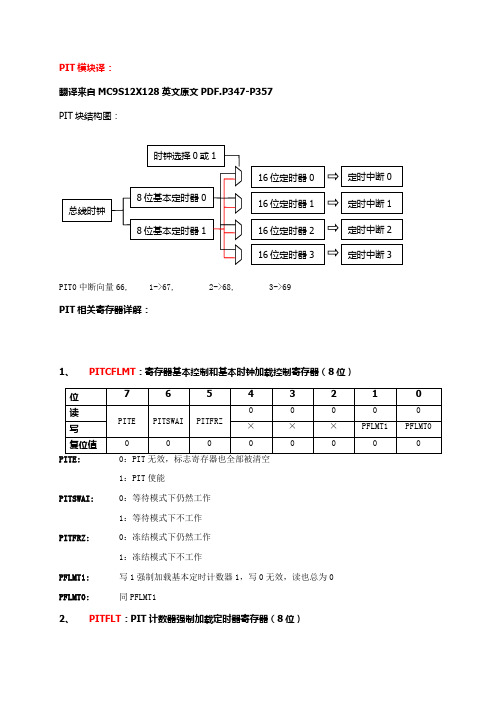

PIT 模块译:翻译来自MC9S12X128英文原文PDF.P347-P357 PIT 块结构图:PIT0中断向量66,1->67,2->68,3->69PIT 相关寄存器详解: 1、 PITCFLMT :寄存器基本控制和基本时钟加载控制寄存器(8位)1:PIT 使能PITSWAI: 0:等待模式下仍然工作1:等待模式下不工作 PITFRZ: 0:冻结模式下仍然工作1:冻结模式下不工作PFLMT1: 写1强制加载基本定时计数器1,写0无效,读也总为0 PFLMT0:同PFLMT12、 PITFLT :PIT 计数器强制加载定时器寄存器(8位)PFLT[3:0]写1相对应的16位计数寄存器会立即载入相对应的16位计数加载寄存器(PITLDn)中的值。

3、PITCE:PIT通道使能存器(8位)PCE[3:0]:如果PITE已经使能,对寄存器PCEn写1后,每输入一个时钟相对应的计数寄存器开始递减,写0无效。

4、PITMUX:PIT基本时钟通道选择寄存器(8位)PMUX[3:0]:对PMUXn写1,则对应定时器通道选择基本时钟1作为输入,写0则选择基本时钟0为输入。

5、PITINTE:PIT定时中断使能寄存器(8位)PINTE[3:0]:对PINTEn写1,当相对应的计数寄存器和基本计数寄存器归0时,产生中断请求,否则无效。

6、PITTF:PIT时钟输出标志寄存器(8位)7、PITMTLD0-1:PIT基本时钟计数器预加载寄存器(8位)会被加载到基本定时器n,无论什么时刻PFLMTn置“1”会立即更新基本定时器寄存器的值.8、PITLD0–3:PIT0-3计数器预加载寄存器(16位)PITLD0-3的值用来加载到相对应计数器0-3的寄存器中。

当相应通道计数器归零时,或PITFLT寄存器中相应的强制加载位置“1”时,PITLDn中的值将会被立即加载到PITCNTn。

9、PITCNT0–3:PIT0-3计数寄存器(16位)变计数周期。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

附录I:寄存器地址列表

直接页面寄存器总结

高页面寄存器总结

非易失寄存器总结

注:直接页面寄存器表地址的低字节用粗体显示,直接寻址对其访问时,仅写地址低字节即可。

第2列中寄存器名用粗体显示以区别右边的位名。

有0的单元格表示未用到的位总是读为0,有破折号的单元格表示未用或者保留,对其读不定。

附录II 指令接与寻址方式

HCS08指令集概括

运算符

() = 括号种表示寄存器或存储器位置的内容

← = 用……加载(读: “得到”)

& = 布尔与

| = 布尔或

⊕= 布尔异或

×= 乘

÷ = 除

: = 串联

+ = 加

- = 求反(二进制补码)

CPU registers

A =>累加器

CCR =>条件代码寄存器

H =>索引寄存器,高8位

X => 索引寄存器,低8位

PC =>程序计数器

PCH =>程序计数器,高8位

PCL =>程序计数器,低8位

SP =>堆栈指针

存储器和寻址

M =>一个存储区位置或者绝对值数据,视寻址模式而定

M:M + 0x0001 => 两个连续存储位置的16位值.高8位位于M的地址,低8位位于更高的连续地址.

条件代码寄存器(CCR)位

V => 二进制补码溢出指示,第7位

H => 半进位,第4位

I => 中断屏蔽,第 3位

N => 求反指示器, 第2位

Z => 置零指示器, 第1位

C => 进/借, 第0位 (进位第 7位 )

CCR工作性符号

– => 位不受影响

0 = > 位强制为0

1 = > 位强制为1

= >根据运算结果设置或清除位

U = > 运算后没有定义

机器编码符号

dd =>一个直接寻址0x0000–0x00FF的低8位(高字节假设为0x00)

ee => 16位偏移量的高8位

ff => 16位偏移量的低8位

ii => 立即数的一个字节

jj => 16位立即数值的高位字节

kk => 16位立即数值的低位字节

hh => 16位扩展寻址的高位字节

ll => 16位扩展寻址的低位字节

rr => 相对偏移量

n —任何表达范围在0–7之间的一个有符号数的标号或表达式

opr8i —任何一个表达8位立即值的标号或表达式

opr16 —任何一个表达16位立即值的标号或表达式

opr8a —任何一个表达一个8位值的标号或表达式.指令对待这个8位值为直接页面64K 字节地址空间(0x00xx)中地址的低8位.

opr16a —任何一个表达16位值的标号或表达式.指令对待这个值为直接页面64K字节地址空间.

oprx8 —任何一个表达8位无符号值的标号或表达式,用于索引寻址.

oprx16 —任何一个16位值的标号或表达式.因为HCS08有一个16位地址总线,这可以为一个有符号或者无符号值.

rel —任何指引在当前指令目标代码最后一个字节之后–128 to +127个字节之内的标号或表达式.汇编器会计算包括当前指令目标代码在内的8位有符号偏移量. 寻址方式

隐含寻址(Inherent)如CLRA,只有操作码,无操作数,需要操作的数据一般为CPU寄存器,因此不需要再去找操作数了。

(INH)

立即寻址 (Immediate)如LDA #$0A,“$”表示16进制,此时操作数位于FLASH空间,与程序一起存放。

(IMM)

直接寻址 (Direct)如 LDA $88,只能访问$0000-$00FF的存储器空间,指令短速度快; (DIR)

扩展寻址 (Extended)如果操作数地址超出了$00FF,自动为扩展寻址;(EXT)

相对寻址(Relative)如BRA LOOP,指令中一般给出8位有符号数表示的偏移量。

(REL)

变址寻址 (Indexed) 采用[H:X]或SP作为指针的间接寻址方式。

( IX )( IX1 )( IX2 )

变址寻址 (Indexed)

1〉无偏移量:CLR ,X 简写(IX)

2〉无偏移量,指令完成后指针加1(H:X = H:X + 0x0001) ,简写(IX+)只用于指令MOV和CBEQ指令中;

3〉8位偏移量:CLR $10,X 简写(IX1)

4〉8位偏移量,指令完成后指针加1,只用于CBEQ;简写(IX1+)5〉16位偏移量,如STA $0100,X 简写(IX2)

6〉堆栈指针加8位偏移量,如LDA $88,SP 简写(SP1)7〉堆栈指针加16位偏移量简写(SP2)

存储器到存储器寻址方式(Memory to Memory)

1〉直接地址到直接地址如: MOV $00,$20 简写(DD)2〉直接地址到变址、变址加1:MOV $80,X+ 简写(DIX+)3〉立即数到直接地址: MOV #$AA,$00F0 简写(IMD)4〉变址、变址加1到直接地址:MOV X+,$20 简写(IX+D)

寻址方式总结

INH => 固定(无操作数)

IMM => 8位或16位立即数

DIR => 直接8位

EXT => 扩展16位

IX => 16位无偏移索引

IX+ => 16位无偏移索引,后递增 (仅仅CBEQ和MOV)

IX1 => H:X中的带8位偏移的16位索引

IX1+ => 带8位偏移的16位索引,后递增 (仅仅CBEQ)

IX2 => H:X中的带16位偏移的16位索引

REL => 8位相对偏移

SP1 => 带8位偏移r的堆栈指针

SP2 => 带16位偏移的堆栈指针

HCS08指令集概括(图表)。