程控交换与宽带交换 第二章 数字交换和数字交换网络

11程控数字交换与交换网(第二版)

幻灯片1程控数字交换与交换网(第二版)叶敏编著幻灯片2目录●第1章绪论●第2章话音信号的数字化基础●第3章数字交换机的话路部分●第4章程控交换系统控制部件的组成特点●第5章程控交换机软件概况●第6章呼叫处理的基本原理●第7章交换技术基础●第8章电话通信网●第9章信令方式●第10章部分有关通信网简介幻灯片3第1章绪论● 1.1 自动电话交换机的发展●史端乔交换机●西门子式自动交换机●旋转制和升降制交换机●纵横制交换机●电子交换机●程序控制交换机●数字交换机● 1.2 自动电话交换机的分类●模拟交换机●数字交换机●布线逻辑控制交换机●存储程序控制交换机幻灯片4● 1.3 程控交换机的基本概念●图中所示的中继器和用户电路包括收号器都受中央处理机控制。

这样就可以得出结论:程控交换机实质上是数字电子计算机控制的交换机。

幻灯片5● 1.4 程控交换机的优越性●技术上的优越性●能提供许多新的用户服务性能●维护管理方便,可靠性高●灵活性大●便于向综合业务数字网方向发展●有可能采用公共信号系统●便于利用电子器件的最新成果,使整机技术的先进性得到发挥●经济上的优越性●交换设备方面●线路设备方面●维护和生产方面幻灯片6● 1.5 程控交换机的服务性能●给一般用户的服务●给各种用户交换机用户的服务●在管理和维护上的新业务● 1.6 程控交换技术的发展幻灯片7● 1.7 当前世界通信的发展● 1.7.1 当前世界通信产业发展的特点●世界通信技术进步越来越快●世界通信市场竞争日趋激烈● 1.7.2 当代通信技术综观●传送网技术●接入网技术●ISDN技术和ATM技术●移动通信和个人通信技术●智能网技术●多媒体通信技术●支撑网技术●因特网技术●下一代的通信技术幻灯片8第2章话音信号的数字化基础● 2.1 时间分割多路复用原理幻灯片9幻灯片10● 2.2 模拟信号的抽样和抽样定理●抽样定理是这样规定的:传送限带连续信号时,只要传送信号的单个抽样值(脉冲)的序列就足够了。

程控数字交换技术第2章ppt课件解读

相比传统的模拟交换技术,程控数字 交换技术具有更高的通话质量和更强 的抗干扰能力。

程控技术的引入

计算机技术的普及使得程控交换成为 可能,提高了交换设备的灵活性和自 动化水平。

技术发展历程

01

02

03

早期数字交换技术

20世纪70年代,程控数字 交换技术开始出现,主要 用于大中型城市的电话网 络。

技术成熟与普及

程控数字交换技术第2 章ppt课件解读

contents

目录

• 程控数字交换技术概述 • 程控数字交换技术原理 • 程控数字交换技术的实现 • 程控数字交换技术的优势与挑战 • 程控数字交换技术的应用案例

01

程控数字交换技术概述

技术背景

数字通信技术的兴起

程控数字交换技术的优势

随着数字信号处理和微电子技术的进 步,数字通信逐渐取代模拟通信。

呼叫中心

电信运营商利用程控数字交换机建立呼叫中心,提供客户服务、技 术支持和销售代表等业务,提高客户满意度和忠诚度。

移动通信

移动通信网络中的交换机采用程控数字交换技术,实现移动设备的语 音和数据交换,支持移动设备的通信需求。

企业内部通信的应用案例

企业电话系统

01

企业内部电话系统采用程控数字交换机,提供高效、可靠的电

实现过程中的关键技术问题

实时性

程控数字交换机需要处理大量实时数据,因此需要保证硬件和软 件的实时性,以满足通信系统的要求。

可靠性

程控数字交换机是通信系统中的关键设备,需要具备高可靠性,以 保证通信的稳定性和不间断性。

可扩展性

随着通信技术的发展,程控数字交换机需要具备可扩展性,以适应 新的业务需求和技术变化。

智能农业

数字交换讲义和数字交换网络

(a)串行码

TS1

TS0

HW7 HW6 HW5 HW4 HW3 HW2 HW1 HW0 HW7 HW6 HW5 HW4 HW3 HW2 HW1 HW0

(b)并行码

图2.7 8端脉码输入的串行码和并行码

每一端的脉码传输速率是2.048Mbit/s, 若8端PCM脉码输入以串行传输时,其传 输速率将达到16.384Mbit/s,若16端输入时, 其传输速率将达到32.768Mbit/s,这样高的 传输速率会带来许多问题。

2.1.2 时隙交换原理

时序开关K入和K出每秒旋转8000周, 每周所需时间是125s。

在TS1时隙时,K入和K出分别与接点 1#入和2#出相连,即K入和1#存储单元相连, K出与2#存储单元输出相连,此时在TS1时 隙里传送来的a话音信息就存入话音存储器 的1#单元,而话音存储器的2#单元内存放 的b话音信息就在此时通过K出的1#接点送 出,也就是输出端在TS1时隙送出b话音信 息给TS1用户。

2.控制时序

8端PCM脉码输入的256个时隙排列方 式 应 是 H W 0 的 T S 0,HW1 的 T S 0,HW2 的 T S 0,…,HW7 的 T S 0;HW0 的 T S 1,HW1 的TS1,HW2的TS1,…,HW7的TS1等等。

3.串/并变换

在图2.6所示的复用器中,每一条HW 接一个移位寄存器,移位寄存器的输入端 为一条线,线上传输的是32个时隙的串行 码。

一、读出控制方式

读出控制方式的T接线器是顺序写入 控制读出的,如图2.3所示,它的话音存储 器SM的写入是在定时脉冲控制下顺序写入, 其读出是受控制存储器的控制读出的。

SM

0

1

a

2

c

数字交换和数字交换网络

AB

分 路

B

器

33 B

87 A

器

A

127

TS21

W

R

时钟

地址计数器 乙E

0

33 87

87 33 127

CPU控制 W CM R 地址计数器

单T型数字交换网络-- 输入控制

3-29

单T型数字交换网络典型芯片

MT8980/ MT89801(加拿大Mitel公司) 美国Motorola公司的MC145601 意大利SGS公司的M-088

❖用复用器、分路器与T接线器组成单T交换网络

3-27

HW1 TS8 HW3 TS21 !

甲M

TS33 TS87 TS87 TS33

UHW0

TS8

SM

A

复 用

TS87

B

TAS330

TS87 TS33

AB

分 路

器

33 A

器

B

UHW3

87 B

TS21

乙M

时钟 地址计数器

127 W

R

0

33 87

甲E

工作速度:输入总线的速度/并行线数 实质:通过空间分割的手段来完成时隙交换。

3-14

复用器与分路器

!

一、复用器

当单端PCM数不能满足需要时,需用多条PCM,如何 实现?(先将它们合并成一条PCM,再送入T接线器。) 它会有哪些变化,有哪些要求?如何复用?

HW0 HW1 HW2 HW3

复 用 new HW 器

3-5

多端PCM交换

TS2 A UHW0 UHW1 UHW2 UHW3 PCM入

交换网络

DHW0

DHW1 A TS16

现代通信网第2章-2程控交换技术1028

测试子系统: 负责软件的规范性检测。包括测试 与仿真。

生产子系统: 生成交换局运行所需的软件。包括 局数据、用户数据和局程序文件的生成。 维护子系统: 负责对现场修改或补丁存档与管理。

《交换技术 》

软件组成

3、交换局数据

局数据

用户数据 系接口电路(SLIC)

分为模拟用户电路和数字用户电路。 模拟用户电路:提供交换机与模拟话机之间的 接口。数量多,投资大。 数字用户电路:提供与数字用户终端的接口。

《交换技术 》

话路系统

(一)本地用户级(用户模块)

1、模拟用户电路功能 B(Battery feed)馈电;

O(Over-voltage protection)过压保护;

《交换技术 》

话路系统 (二)远端用户级(Remote

Module)

远端用户级是部署在距离电话局较远的用

户点上,其基本功能与局内用户级相似,

包括用户电路和话务集中器。

远端用户级不再进行D/A转换,直接经数

字中继接口进入数字交换网络进行交换。

《交换技术 》

话路系统

(三)选组级(数字交换网络)

2.1.1 程控交换机的硬件组成

2.1.2 程控交换机的软件组成

《交换技术 》

2.1.2 程控交换机的软件组成

话路部分

输入/输出设备

系统软件

执行管理程序 系统监视和 故障处理程序 故障诊断程序 I/O和人机 通信程序

应用软件

呼叫处理程序 维护管理程序

《交换技术 》

2.1.2 交换机的软件组成

呼叫处理程序 执行管理程序 故障处理程序 故障诊断程序 维护管理程序 设计子系统 支援程序 局数据 数据 用户数据 系统数据

现代交换技术--Chapter2 数字交换网络

数 字 交 换 技 术 基 础

用

端: 端:

模拟

愃 模拟量

第 2 章 数字交换网络

语音信号数字化过程 2.1

数 字 交 换 技 术 基 础

第 2 章 数字交换网络

主要功能单元包括三种功能: 主要功能单元包括三种功能: 2.1

数 字 交 换 技 术 基 础

抽 样

量化

编码

抽样:把话路信号(300-3400HZ) 抽样:把话路信号(300-3400HZ)变成脉冲调幅信 PAM) 号(PAM) 量化( 量化( 幅 脉冲调幅信号(PAM) ): 脉冲调幅信号(PAM)量化 量化信号( 量化信号( ( ) ) 量化信号变 成 编

ln( + µ | Vi |) 1 V0 = (0 ≤| Vi |≤ 1) ln( + µ) 1

(压缩特性

惊

)

第 2 章 数字交换网络

A律13折线采用8位编码

2.1

数 字 交 换 技 术 基 础

第 2 章 数字交换网络

2.1

数 字 交 换 技 术 基 础

第 2 章 数字交换网络

2.1.2 时分多路通信

数 字 交 换 技 术 基 础

第 2 章 数字交换网络

2.1

数 字 交 换 技 术 基 础

第 2 章 数字交换网络

2.1

数 字 交 换 技 术 基 础

第 2 章 数字交换网络

32路PCM的帧结构 2.1.3 32路PCM的帧结构

2.1

数 字 交 换 技 术 基 础

第 2 章 数字交换网络

2.1

数 字 交 换 技 术 基 础

第 2 章 数字交换网络

2.1

第2章-数字交换和数字交换网络PPT课件

2.1.3 数字交换网络

►时隙交换的实质就是将一个话音信息由某个时隙搬 移至另一个时隙,由时分接线器来完成的。 ►数字交换网络仅使用时分接线器是不够的,还必须 利用空间交换来扩大其容量。 ►空间交换是将信息由这一条复用线上交换到另一条 复用线上,时隙不变。

►数字交换网络包括时分接线器和空间接线器两种基 本部件,分别用于完成时间交换和空间交换。

HW7 D0

D0

锁存器

移位寄存器

至话音存储器输入

HW7

移位寄存器

锁存器

D0

D0

HW0 8→1

D7

D7

D7

D7

HW7

CP

CP∧TD7

CP1

► TD7=A2∧A1 ∧ A0,是一个位脉冲。 ►CP ∧TD7是为了8位并行码全部出齐的稍后时间 (半个位脉冲)进行数据锁存。

一、复用器

3、并路复用 ►把8个HW的并行码按一定的次序排列送到8条输出 线上。 ►8选1选择器完成8条HW线(每位)复用到1条新的 输出线上,8位并行码分别在8条输出线上。

自控存

DI0

DI1

DI7

输入数据 由串/并变换电路来

三、话音存储器

定时脉冲

2、控制读出

A0 A1 A7

+ B7 B1 B0

自控存

读出控制 写入控制

+

+

+

至并/串变换电路输出数据

DO0

DO1

DO7

A0

话音存储器

A1 RAM 256×1

RAM 256×1

RAM 256×1

►A7 C P 后 半 期 时 , C M 送 数 据 ,

HW7

8端输入的T接线器

255

程控数字交换与交换网 第2章 复用与交换基本原理

TSTSTSTSTSTSTSTSTSTSTSTSTSTSTSTSTSTSTSTSTSTSTSTSTSTSTSTSTSTSTSTS 0 1 2 3 4 5 6 7 8 9 10111213141516171819202122232425262728293031

同步时隙

标志信号时隙

话路时隙

偶帧

10011011 帧定位码组

接收方,在发送方同步信号的作用下,在时隙1时接收第1 路信号,时隙2时接收第2路信号……….

发送

接收

第1路

第1路

第2路 第n路

4

传输介质

第2路 第n路

4 August 2020

时分复用原理(2)

用户

时分复用

Aa

at ①

B bb

②

t

ab

bc

ca

dt

③

C

cc

t

④

#1

#2

#3

#4

D

dt

四个时分复用帧

TDM按帧结构(固定时长,时隙个数固定)传送 每个用户分配固定时隙(在帧结构中占固定位置)

4 August 2020

帧结构描述

帧重复频率=抽样频率=8kHz 抽样周期=125us 时隙数=32,时隙编号TS0-TS31 每路时隙=3.91us 每路时隙传送8位码组,位时间=488ns 每帧传送位数=32×8=256 每路数码率=8bit/125us=64kbit/s 总码率=256bit/125us=2048kbit/s

12 13

量化

1 011 2 010 3 001 4 000 5 000 6 001 7 010 8 011

9 100 10 101 11 110 12 111 13 111 14 110 15 101 16 100

第2章数字交换和数字交换网络

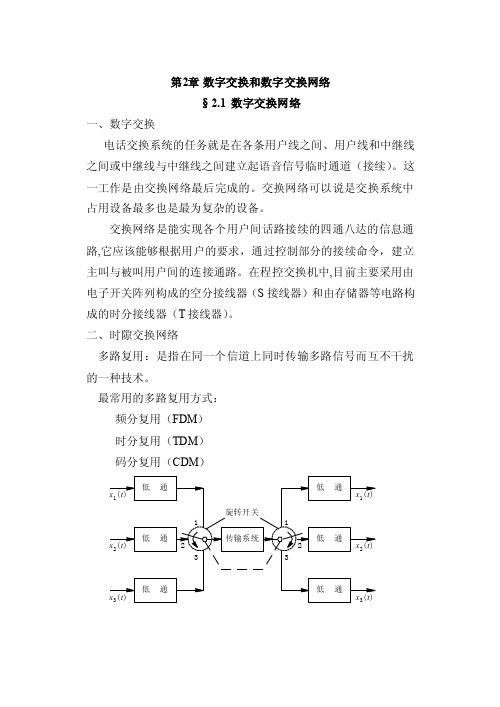

第2章 数字交换和数字交换网络§2.1 数字交换网络一、数字交换电话交换系统的任务就是在各条用户线之间、用户线和中继线之间或中继线与中继线之间建立起语音信号临时通道(接续)。

这一工作是由交换网络最后完成的。

交换网络可以说是交换系统中占用设备最多也是最为复杂的设备。

交换网络是能实现各个用户间话路接续的四通八达的信息通路,它应该能够根据用户的要求,通过控制部分的接续命令,建立主叫与被叫用户间的连接通路。

在程控交换机中,目前主要采用由电子开关阵列构成的空分接线器(S 接线器)和由存储器等电路构成的时分接线器(T 接线器)。

二、时隙交换网络多路复用:是指在同一个信道上同时传输多路信号而互不干扰的一种技术。

最常用的多路复用方式:频分复用(FDM )时分复用(TDM )码分复用(CDM )传输系统旋转开关112233低 通x 2(t )低 通x 1(t )x 3(t )低 通低 通x 2(t )低 通x 1(t )x 3(t )低 通三、PCM30/32路系统的帧结构对于多路数字电话系统,国际上有两种标准化制式,即PCM 30/32路制式(E体系)和PCM 24路制式(T体系)。

我国规定采用的是PCM 30/32路制式,一帧共有32个时隙,可以传送30路电话,即复用的路数n=32路,其中话路数为30。

抽样频率为8 kHz,则抽样周期125μs。

每个时隙占125us/32=3.9μs。

32个时隙构成一个“帧”,16帧合成一个“复帧”,一个复帧占125μs*16=2ms。

(1) 时隙分配。

在PCM30/32路的制式中,抽样周期为1/8 000=125μs,它被称为一个帧周期,即125μs为一帧。

一帧内要时分复用32路,每路占用的时隙为125/32=3.9μs,称为一个时隙。

因此一帧有32个时隙,按顺序编号为TS0、TS1、……、TS31。

时隙的使用分配为①TS1~TS15, TS17~TS31为30个话路时隙。

第二章数字交换原理与数字交换网络

(1)集中级 (2)分配级 (3)扩展级

集中级和扩展级,在实际的程控交换系

统中,一般置于用户级(机框或模块)内,例如, 将n个用户机框的输出总线物理地复连起来便 可实现n倍的集中比,这样做虽然服务等级在 特殊情况下降低了,但换取的是设备数量的 大大减少。而分配级即为由上述T、S接线器 构成的数字交换网络。

(1)S型接线器的基本组成

S型接线器由m×n交叉点矩阵和控制存储 器组成。在每条入线i和出线j之间都有一个交叉 点Kij,当某个交叉点在控制存储器控制下接通 时,相应的入线即可与相应的出线相连,但必 须建立在一定时隙的基础上。

(2)S型接线器的工作原理

根据控制存储器是控制输出线上交叉接 点闭合还是控制输入线上交叉接点的闭合, 可分为输出控制方式和输入控制方式两种。

2.2.1 时隙交换的基本概念

图2-10 30 话路交换的随机存储器

在同一条PCM复用线内进行时隙交换,对于 30/32路PCM的一次群来说,最多只能提供30个 话路时隙。数字交换机给每个用户分配一个固定 时隙,因此,要在任意两个用户(两个不同时隙) 间进行数字交换。数字交换网络需具有两种基本 功能:

(3)T接线器的工作原理 ①读出控制方式

读出控制方式的T接线器是顺序写入控制 读出的,如图2-16所示,它的话音存储器SM 的写入是在定时脉冲控制下顺序写入,其读出 是受控制存储器的控制读出的。

SM

0

1

a

2

c

3

b

ca

8

b

TS8

TS2 TS1 TS0

…

31

ca

b

TS15 TS8 TS1

W

R

0

定1

8

图2-26 T-T-T型三级时分交换网络

第二章 数字交换和数字交换网络

TS1 TS2 TS1 TS0

TS31

PCM

第1路 第2路

TS1

发群 设备

32路

入线 话音 存储器

0 1 2

(TS1)

第30路

解码

第1路

TS2

PCM

TS2

第2路

收群 设备

TS31

32路

出线

TS2 TS1 TS0

第30路

(TS2)

解码

换 术 Modern Switch Technology

-16-

3.1数字交换的基本概念

现代交换技术 Modern Switch Technology

Modern Switch Technology

现

换 术

hcli@ 学

第三章 数字交换和数字交换网络

数字交换的基本概念 T型时分接线器 S型时分接线器 多级时分交换网络 阻塞的概念和计算

现

换 术 Modern Switch Technology

同步/异步时分复用信号的交换 0 1 2 3 4 2 1 2

现

入线

0 1 2 3 4 0 0 0 1 2 2 0

出线

0 入线 1 2

0 1 2

-4-

出线

换 术 Modern Switch Technology

3.1数字交换的基本概念

交换单元的分类 • 按使用需要 0 入线 M-1 集中型 入线 0 M-1 连接型

现

换 术 Modern Switch Technology

-10-

3.1数字交换的基本概念

空分交换单元

交换单元由空间上分离的多个小的交换部件或开关部件按一定 的规律连接构成。开关阵列在拓扑结构上可排成方形或矩形二维 阵列。 • 实际的开关阵列 继电器:可构成无向交换单元,交换模拟或数字信 息,但干扰和噪声大,动作慢 模拟电子开关:MC142100、MC145100等,单向传 输,时延和损耗大 数字电子开关:数字交换,交换速度快且无信号损 失,采用多路选择器实现

程控数字交换与交换网

程控数字交换与交换网《现代交换技术》第1章概述1、交换的基本概念:交换广义定义:(1)在公共网络的各终端用户之间互相传递语音、文本、数据、图像、视频的信息。

(2)以电话交换来说明交换的概念:电话交换是电信交换中最基本的一种交换业务,也称语音交换、电路交换。

最早,电话的发明:1876年Bell A.G.,基于点对点之间的通话。

之后,产生一群用户之间互相通话的需求。

(3)交换节点的基本功能:交换节点需要控制以下四种接续类型:1)本局接续:是本局用户之间的接续。

比如在电话交换系统A中,电话用户1要打给电话用户22)出局接续:是本局用户与出中继线之间的接续。

比如电话交换系统A中的电话用户1要打给电话交换系统B中的电话用户3时,电话用户1的语音需要从电话交换系统A发出,送入中继线a。

3)入局接续:是入中继线与本局用户之间的接续。

比如由中继线b来的语音需要经过电话交换系统B才能到达其下属电话用户。

4)转接接续:是入中继线与出中继线之间的接续。

比如电话交换系统A的电话用户打给电话交换系统B的电话用户,需由中继线a、b在电话交换系统C中进行接续。

2、当前交换中,最常用的两种方式是电路交换和分组交换。

电路交换是最早出现的交换方式,基本过程包过建立阶段,信息传送阶段,连接释放阶段。

是以电路连接为目的的方式。

公共交换电话网(PSTN)和移动网(PLMN)核心,程控中采用的都是电路交换技术。

优点:在通信过程中可以保证为用户提供固定足够的带宽,并且实时性强,时延小。

缺点:网络的带宽利用率不高,一旦电路被建立不管通信双方是否处于通话状态,分配的电路都一直被占用;没有差错控制措施,可靠性有所欠缺。

因此电路交换适合于电话交换、文件传送、高速传真,不适合突发(burst)业务和对差错敏感的数据业务。

(二)分组交换采用存储转发方式,在数据传输中使用,将用户要传送的信息分割为若干个分组(packet),每个分组中有一个分组头,含有可供选路的信息和其他控制信息。

程控交换与综合业务通信网第二章信息交换与传输技术基础

011 111

010 000

001

110

101

100

图 2-16 8DPSK的载波相移矢量图

作业 1.简述常用的三种信息交换技术,它们有什么特

点? 2.什么是PCM?熟悉PCM E1复帧的结构。 3.简要说明FDM和TDM的原理。 4.掌握差分码、曼彻斯特码、密勒码等几种常用

二进制信息 定时

1

1

1

0

1

0

0

1

曼彻斯特码差分曼彻斯特码ຫໍສະໝຸດ 图 2-10 曼彻斯特码的波形

(3)传号交替反转码 传号交替反转码(AMI,alternative mark

inversive)码中,原输入数据0变换为三电平中的0; 数据1则交替地变换为+1或-1电平。显然,AMI码不 含有直流分量。

(5)传号反转码 传号反转码(CMI,coded mark inversion)码与

科学,你是国力的灵魂;同时又是社 会发展 的标志 。上午2时37分 51秒上 午2时37分02: 37:5120.12.3

每天都是美好的一天,新的一天开启 。20.12.320.12.302:3702:37: 5102:37:51Dec -20

人生不是自发的自我发展,而是一长 串机缘 。事件 和决定 ,这些 机缘、 事件和 决定在 它们实 现的当 时是取 决于我 们的意 志的。2020年12月3日 星期四 2时37分51秒 Thursday, December 03, 2020

,根据抽样定理,采样频率为8kHz。如图2-4所示

。

图 2-4 模拟信号的抽样

(2)量化:为了解决线性量化时小信号音质 差的矛盾,采用不均匀量化,即小信号时量化间 隔小,大信号时间隔大,如图2-5所示。通常采 用两种对数形式的压缩特性,我国采用A律。

程控数字交换技术

第一章交换的概念·1.1 交换的概念通信作为信息产业的基础,在推进社会信息化进程中发挥着先导和带动作用。

随着通信技术的飞速发展,通信新业务不断涌现,电话通信和数据通信已成为现代社会应用最广泛的信息交流方式,是人们日常生活和工作中不可缺少的一部分。

通信是指利用有线、无线的电磁系统或者光电系统,传送、发射或者接收语音、文字、数据、图像以及其它任何形式信息的活动。

一个有效的通信,能够让用户不管在何时、何地都可与任何其它用户互相传递信息。

为了实现一个有效的通信就需要采用交换技术。

所谓交换,就是通过交换局的交换设备在通信网络大量的终端用户之间,根据用户的呼叫请求建立连接,相互传送话音、数据、图像等信息。

任何一个主叫用户的信息,可以通过通信网络中的交换设备和传输设备发送到任何一个或多个被叫用户。

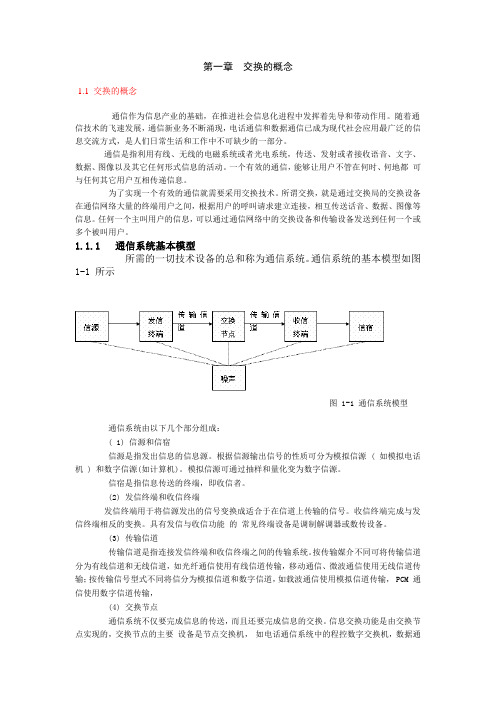

1.1.1 通信系统基本模型所需的一切技术设备的总和称为通信系统。

通信系统的基本模型如图 1-1 所示图 1-1 通信系统模型通信系统由以下几个部分组成:( 1) 信源和信宿信源是指发出信息的信息源。

根据信源输出信号的性质可分为模拟信源 ( 如模拟电话机 ) 和数字信源(如计算机)。

模拟信源可通过抽样和量化变为数字信源。

信宿是指信息传送的终端,即收信者。

(2) 发信终端和收信终端发信终端用于将信源发出的信号变换成适合于在信道上传输的信号。

收信终端完成与发信终端相反的变换。

具有发信与收信功能的常见终端设备是调制解调器或数传设备。

(3) 传输信道传输信道是指连接发信终端和收信终端之间的传输系统。

按传输媒介不同可将传输信道分为有线信道和无线信道,如光纤通信使用有线信道传输,移动通信、微波通信使用无线信道传输;按传输信号型式不同将信分为模拟信道和数字信道,如载波通信使用模拟信道传输, PCM 通信使用数字信道传输,(4) 交换节点通信系统不仅要完成信息的传送,而且还要完成信息的交换。

信息交换功能是由交换节点实现的,交换节点的主要设备是节点交换机,如电话通信系统中的程控数字交换机,数据通信系统中的分组交换机、 DDN 节点机,宽带通信系统中的 ATM 交换机、帧中继交换机,光纤通信系统中的光交换机等。

3第二章数字交换与交换机

现代交换原理

复用器时隙变换关系计算举例:

HW0 HW1 HW2 HW3

TS2

C

TS18

B

A

TS30

TS9 TS74 TS123

复

CB A

用

器

HHW

C: 4*2+1=9 B: 4*18+2=74 A: 4*30+3=123

2012.04 通信工程系 王琳珠

现代交换原理

分路器 HHW TS号=(n+1)TS号+HW’号 举例:HHW TS号=50 n+1=16 50÷16=商3 余2 被除数HHW TS号; 除数n+1; 商是TS号;余数是HW号

顺序写入,控制读出(或输出控制) 控制写入,顺序读出(或输入控制)

2012.04 通信工程系 王琳珠

现代交换原理

顺序写入、控制读出的T接线器的结构示意图

SM

TS2

0

以TS2→TS8的实现, TS8

1

A

2

A

A

介绍T接线器的工作原理。

输入时隙号

•

* 要实现TS2→TS8的交换,

•

首先要由处理机在CM的8号

2012.04 通信工程系 王琳珠

现代交换原理

课堂练习: 已知16条(HW0~HW15)PCM母线,

接入复用器,试求: 1.复用后高速母线上一帧时隙数(复用度)。 2.高速母线由多少条传输线组成。 3.HW2 TS18、HW6 TS14复用后时隙数。

2012.04 通信工程系 王琳珠

现代交换原理

存储器0

B0 B1

B2

PCM1

来自控制 选通

2第二章 数字交换与交换机(1)

2012.04

通信工程系

王琳珠

现代交换原理

DTMF收号,可利用专用 模拟用户接口

单片电路分路接收,也可 以设置集中的收号器通过 交换网络选择连接进行集 中收号。

编译码C,数字交换机只进行数字 信号交换,外线用户环路采用模拟 方式传送话音信号,需采用PCM编 译码器完成相互转换。

a b

测试 T

振铃 R

外部存储器

远端接口

数字程控交换机的硬件功能组织结构

2012.04

通信工程系

王琳珠

现代交换原理

2.2 话路子系统 2.2.1模拟用户接口 模拟用户接口 是连接普通电话机的接口电路,每个用户一套 普通电话机的特点 是一个无源电声转换装置; 通过对绞线以二线模拟方式连接到交换机; 利用二线上直流环路状态表示忙闲; 利用号盘DP或DTMF方式发送呼叫号码。 用户级(用户集线器LC) 话务集中作用—提高交换网的利用率

2012.04

通信工程系

王琳珠

现代交换原理

模拟用户线 模拟用户接口 远端模块 数字用户线 数字中继线 模拟中继线 数字用户接口 数字中继接口 模拟中继接口 话路子系统 信令设备 用户级 模拟用户接口 数字中继接口 中继线 用户级 数 数字中继接口

字

交 换 网 络

控制子系统

内部存储器

处理机

外部设备

维护终端

2012.04

通信工程系

王琳珠

现代交换原理

测试T,通过继电器分别将外线或内侧电路连 接到测试设备。 模拟用户接口 外线测试可检测用户线短路、断路、碰地、搭 接电力线等故障; 内侧测试模仿话机的操作过程检验各功能电路 是否正常。

a b

测试 T

振铃 R

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

输

D0 D1 D7 (b)并行码

图2.7 8端脉码输入的串行码和并行码 端脉码输入的串行码和并行码

每一端的脉码传输速率是2.048Mbit/s, , 每一端的脉码传输速率是 脉码输入以串行传输时, 若8端PCM脉码输入以串行传输时,其传 端 脉码输入以串行传输时 输速率将达到16.384Mbit/s,若16端输入时, 端输入时, 输速率将达到 , 端输入时 其传输速率将达到32.768Mbit/s,这样高的 其传输速率将达到 , 传输速率会带来许多问题。 传输速率会带来许多问题。 2.控制时序 8端PCM脉码输入的 脉码输入的256个时隙排列方 端 脉码输入的 个时隙排列方 式 应 是 HW0 的 TS0,HW1 的 TS0,HW2 的 TS0,…,HW7 的 TS0;HW0 的 TS1,HW1 , 的 TS1,HW2 的 TS1,…,HW7 的 TS1 等等 。 ,

2.3 S型时分接线器

S型时分接线器是空间型接线器 型时分接线器是空间型接线器(space 型时分接线器是空间型接线器 switch),其功能是完成“空间交换”。即 ,其功能是完成“空间交换” 在一根入线中, 在一根入线中,可以选择任何一根出线与 之连通。 之连通。

2.3.1 S型接线器的基本组成

3.串/并变换 在图2.6所示的复用器中 每一条HW 所示的复用器中, 在图 所示的复用器中,每一条 接一个移位寄存器, 接一个移位寄存器 , 移位寄存器的输入端 为一条线,线上传输的是32个时隙的串行 为一条线 , 线上传输的是 个时隙的串行 码。 4.并路复用 在图2.6所示的复用器中,8选1的电子 在图 所示的复用器中, 选 的电子 所示的复用器中 选择器的功能是把8个 选择器的功能是把 个HW的并行码按一定 的并行码按一定 的次序进行排列,一个一个地送出。 的次序进行排列,一个一个地送出。

S型接线器由 ×n交叉点矩阵和控制 型接线器由m× 交叉点矩阵和控制 型接线器由 存储器组成。在每条入线i和出线 和出线j之间都有 存储器组成。在每条入线 和出线 之间都有 一个交叉点Kij,当某个交叉点在控制存储 一个交叉点 器控制下接通时,相应的入线即可与相应 器控制下接通时, 的出线相连, 的出线相连,但必须建立在一定时隙的基 础上。 础上。

TS 1 D7 D6 D5 D4 D3 D2 D1 D0 D7 D6 D5

TS 0 D4 D3 D2 D1 D0

输 入

HW 0 HW 1

HW 7 TS 1

(a)串行码 TS 0

HW 7 HW 6 HW 5 HW 4 HW 3 HW 2 HW 1 HW 0 HW 7 HW 6 HW 5 HW 4 HW 3 HW 2 HW 1 HW 0

最简单的数字交换方法是给这两个要 求通话的用户之间分配一个公共时隙( 求通话的用户之间分配一个公共时隙(时 分通路), ),两个用户的模拟话音信号经数 分通路),两个用户的模拟话音信号经数 字化后都进入这个特定的时隙( 字化后都进入这个特定的时隙(Time Slot, , TS),这就是动态分配时隙的方法。 ),这就是动态分配时隙的方法。 ),这就是动态分配时隙的方法

2.2.3 T接线器的电路组成

时分接线器的交换容量主要取决于组 成该接线器的存储器容量和速度,多以8端 成该接线器的存储器容量和速度,多以 端 或16端PCM交换来构成一个交换单元,每 端 交换来构成一个交换单元, 交换来构成一个交换单元 一条PCM线称 线称HW(Highway)。 一条 线称 ( ) 端脉码输入的T接线器方框 图 2.5是 8端脉码输入的 接线器方框 是 端脉码输入的 由复用器、话音存储器( 图,由复用器、话音存储器(SM)、控制 ) 存储器( 存储器(CM)和分路器所组成。 )和分路器所组成。

话音存储器( ) 话音存储器(SM)用于暂存经过 PCM编码的数字化话音信息,由随机存取 编码的数字化话音信息, 编码的数字化话音信息 存储器( 存储器(Random Access Memory,RAM) , ) 构成。 构成。 控制存储器( 构成, 控制存储器(CM)也由 )也由RAM构成, 构成 用于控制话音存储器信息的写入或读出。 用于控制话音存储器信息的写入或读出。 话音存储器存储的是话音信息, 话音存储器存储的是话音信息,控制 存储器存储的是话音存储器的地址。 存储器存储的是话音存储器的地址。

2.1.2 时隙交换原理

时序开关K 每秒旋转8000周, 时序开关 入和K出每秒旋转 周 每周所需时间是125µs。 每周所需时间是 µ。

时隙时, 在TS1时隙时,K入和K出分别与接点 1#入和2#出相连,即K入和1#存储单元相连, 相连, 存储单元相连, 存储单元相连 K出与2#存储单元输出相连,此时在 1时 存储单元输出相连, 存储单元输出相连 此时在TS 隙里传送来的a话音信息就存入话音存储器 隙里传送来的 话音信息就存入话音存储器 的1#单元,而话音存储器的2#单元内存放 单元,而话音存储器的 单元内存放 单元 话音信息就在此时通过K 的b话音信息就在此时通过 出的1#接点送 话音信息就在此时通过 接点送 也就是输出端在TS 时隙送出b话音信 出,也就是输出端在 1时隙送出 话音信 息给TS 用户。 息给 1用户。

至并/串变换电路输出数据 DO0 DO1

…

DO7

A0

+

A0

定 时 脉 冲

A1

+

写 读 入 控 制 制 控 出

A1 RAM RAM RAM

…

…

A7

+

256×1

256×1

256×1

A7 R/W

+

…

B7 B1 B0

DI0

DI1

…

DI7

输入数据 由串/并变换电路来

来自控制存储器

图 2.10 读出控制方式的话音存储器

SM 0 1 2 3 b TS 8 c a 8 a c c TS 15 a TS 8 b TS 1

b

31 W R 0 1 8 1 2 CM

定 时 脉 冲

A4

…

8 A0 15 31

TS 2 TS 1 TS 0

2.3

T

话音存储器中每个存储单元内存入的 是发话人的话音信息编码,通常是8位编码 位编码。 是发话人的话音信息编码,通常是 位编码。 T接线器的工作是在中央处理机的控 接线器的工作是在中央处理机的控 制下进行。 制下进行 。 当中央处理机得知用户的要求 拨号号码) 首先通过用户的忙闲表, ( 拨号号码 ) 后 , 首先通过用户的忙闲表 , 查被叫是否空闲,若空闲, 就置忙, 查被叫是否空闲 , 若空闲 , 就置忙 , 占用 这条链路。中央处理机CPU根据用户要求, 根据用户要求, 这条链路 。 中央处理机 根据用户要求 向控制存储器发出“ 命令, 向控制存储器发出 “ 写 ” 命令 , 将控制信 息写入控制存储器。 息写入控制存储器。

2.2.2 T接线器的工作原理 一、读出控制方式

读出控制方式的T接线器是顺序写入 读出控制方式的 接线器是顺序写入 控制读出的,如图2.3所示 所示, 控制读出的,如图 所示,它的话音存储 的写入是在定时脉冲控制下顺序写入, 器SM的写入是在定时脉冲控制下顺序写入, 的写入是在定时脉冲控制下顺序写入 其读出是受控制存储器的控制读出的。 其读出是受控制存储器的控制读出的。

SM 0 1 8 b TS 8 c a 15 b a c c TS 15 a TS 8 b TS 1

31

W 0 1 2 8 31 8 15

…

TS 2 TS 1 TS 0

R

定 时 脉 冲

A4 A0

Байду номын сангаас

1 CM

2.4

T

当中央处理机( 当中央处理机(Central Processing Unit,CPU)得知用户要求后,即向控制 , )得知用户要求后, 存储器下“写”令,命令在控制存储器的 存储器下“ 1#单元写入“8”,在8#单元写入“1”。 单元写入“ ” 单元写入“ ” 单元写入 单元写入

用户B的回话信息 如何传送 用户 的回话信息b如何传送,也要由 的回话信息 如何传送, 中央处理机控制,向控制存储器下达“ 中央处理机控制,向控制存储器下达“写” 命令,令其在1#单元中写入 ” 单元中写入“ 命令,令其在 单元中写入“8”。

二、写入控制方式

T接线器采用写入控制方式时 , 如图 接线器采用写入控制方式时, 接线器采用写入控制方式时 2.4所示 , 它的话音存储器 所示, 所示 它的话音存储器SM的写入受控 的写入受控 制存储器控制, 制存储器控制 , 它的读出则是在定时脉冲 的控制下顺序读出。 的控制下顺序读出。

SM HW 0 HW 1

…

TS 1 TS 0

0 复 用 器 分 路 器

HW 0 HW 1

TS 1

TS 0

HW 7

…

TS 1 TS 0 255

…

…

HW 7

A7~A0

0

255

CM

图2.5 8端输入的 接线器 端输入的T接线器 端输入的

一、复用器

复用器的基本功能是串/并变换和并路 复用器的基本功能是串 并变换和并路 复用。其目的是减低数据传输速率, 复用 。 其目的是减低数据传输速率 , 便于 半导体存储器件的存储和取出操作; 半导体存储器件的存储和取出操作 ; 尽可 能利用半导体器件的高速特性, 能利用半导体器件的高速特性 , 使在每条 数字通道中能够传送更多的信息, 数字通道中能够传送更多的信息 , 提高数 字通道的利用率。 字通道的利用率。

输 入

D0

D7

锁 存 器 (0)

(0)

HW0

D7

输

TD0 CP

TD7 CP HW7 锁 存 器 HW7 (7)

2.9 器

CP D0

出

移 位 寄 存 器

S

D7

(0)

HW7