genesis资料制作详解

genesis全套最快速制作操作步骤

genesis全套最快速制作操作步骤Revised by BLUE on the afternoon of December 12,2020.Designer By:AnjieDate:2015-09-09资料整理1.检查整理资料(解压缩.Zip,打印客户PDF等资料).2.INPUT资料(注意钻孔D-C0DE属性设置)3.更改层命名,定义层属性及排序.4.层对齐及归原点(最左下角).5.存0RG.整理原始网络6.钻孔核对分孔图(MAP)7.挑选成型线至outline层8.工作层outline层移到0层.9.整理钻孔(例如:将大于钻孔移动到outline层,其它层NPTH, SLOT移动到DRL层)10.整理成型线(断线、缺口、R8)11.整理outline(将outline层需要钻孔的移动到drl层)12.创建Profile.13.板外物移动到0层.14.核对0层成型线及板外物是否移除正确.15.内层网络检查(如负性假性隔离)16.防焊转PAD17.线路转PAD18.分析钻孔(检查线路PAD是否有漏孔、重孔修正,内层short)19.定义SMD属性20.存NET21.打印原稿图纸.编辑钻孔22.补偿钻孔(1)检查原始孔径是否正确(不能有“ ”号)(2)合刀排序(3)输入板厚与补偿值(PTH+4 /PTH+6)(4)定义钻孔属性(VIA, PTH, NPTH)主要定义VIA属性NPTH在整理原始网络前定义・(5)输入公差(注意单位).(6)检查最大与最小孔是否符合规范(7)短SLOT孔分刀,8字孔分刀。

(尾数+1或-1)23•校对钻孔中心(参照TOP防焊及TOP线路)24.分析钻孔25.短SLOT孔加预钻孔26.挑选NPTH属性的孔移动到新建NPTH层.内层负片编辑1.检查有无负性物件(负性物件需要合并)2.层属性是否为NEG3.对齐钻孔(内层负片为影响层,参考钻孔层对齐)4.隔离线宽检查修正。

genesis全套最快速制作操作步骤

g e n e s i s全套最快速制作操作步骤SANY标准化小组 #QS8QHH-HHGX8Q8-GNHHJ8-HHMHGN#Designer By:AnjieDate:2015-09-09资料整理1.检查整理资料(解压缩.zip,打印客户PDF等资料).2.INPUT资料(注意钻孔D-CODE属性设置)3.更改层命名,定义层属性及排序.4.层对齐及归原点(最左下角).5.存ORG.整理原始网络6.钻孔核对分孔图(MAP)7.挑选成型线至outline层8.工作层outline层移到0层.9.整理钻孔(例如:将大于钻孔移动到outline层, 其它层NPTH,SLOT移动到DRL层)10.整理成型线(断线、缺口、R8)11.整理outline(将outline层需要钻孔的移动到drl层)12.创建Profile.13.板外物移动到0层.14.核对0层成型线及板外物是否移除正确.15.内层网络检查(如负性假性隔离)16.防焊转PAD17.线路转PAD18.分析钻孔(检查线路PAD是否有漏孔、重孔修正,内层short)19.定义SMD属性20.存NET21.打印原稿图纸.编辑钻孔22.补偿钻孔(1)检查原始孔径是否正确(不能有“”号)(2)合刀排序(3)输入板厚与补偿值(PTH+4 /PTH+6)(4)定义钻孔属性(VIA,PTH,NPTH)主要定义VIA属性NPTH在整理原始网络前定义.(5)输入公差(注意单位).(6)检查最大与最小孔是否符合规范(7)短SLOT孔分刀,8字孔分刀。

(尾数+1 或-1)23.校对钻孔中心(参照TOP防焊及TOP线路)24.分析钻孔25.短SLOT孔加预钻孔26.挑选NPTH属性的孔移动到新建NPTH层.内层负片编辑1.检查有无负性物件(负性物件需要合并)2.层属性是否为NEG3.对齐钻孔(内层负片为影响层,参考钻孔层对齐)4.隔离线宽检查修正。

5.检查隔离PAD检查修正。

GENESIS基本操作步骤及要点

GENESIS基本操作步骤及要点一、查看客户的所有文件,提取相关信息,有矛盾的地方要确认。

注意以下要点:外单,特殊顾客,板材,板厚,外形尺寸,提供报告,内外层基铜厚度,镀层工艺,过孔工艺(塞孔,开窗,盖孔),快捷标记及位置要求,外形要求,阻焊颜色,字符颜色,叠层要求,验收标准,镀金手指,阻抗要求,印蓝胶、碳油或序列号,使用挡油菲林,使用镀孔菲林。

二、原始文件的导入,创建CAD,特别注意钻孔格式。

三、复制CAD为NET四、NET中的操作1,根据叠层要求进行排序,注意客户文件中有多处叠层说明时,要求是否一致。

2,命名修改为GENESIS认可的名字3,新建rout层4,执行actions→re-arrange rows,定义各层属性。

系统误定义属性的层要改正5,察看各层对位情况,相关层的比较,察看底层字符是否为反字等,将贴片层与阻焊层比较,保证贴片都有阻焊开窗,注意贴片与线路盘形状是否一致。

确认文件整体上无大错。

6,查看文件中的GKO层、GM1层等是否有做钻孔或槽孔的要求。

客户提供的多个边框层是否一致。

7,如果是铣开交货,将单元板间距调整为0.1inch。

8,选择合适的边框,判断尺寸正确后COPY至rout层,注意外形公差要求,rout层的形状要与客户要求相同。

9,修改边框,边框一定要光滑,无断线、重复的线,无尖角。

调整线宽为10mil。

10,定义profile,坐标原点和基准点11,剪切profile以外的物体,此步骤一定要谨慎处理,确保线路层的导线没有被剪切掉,字符层剩下字符和字符框的完整性。

12,利用宏命令(F10、F11)对复合层进行处理。

13,阻焊参照字符的检查,察看有无阻焊少开窗,是否有做槽孔的标志。

14,执行线转盘,察看各层线盘属性是否正确,格式是否正确。

15,线转面。

16,执行立体网络检查,察看客户原文件是否存在分离元器件短路。

17,钻孔处理(1)钻孔与孔位图对照,看是否少孔,是否多孔,是否有槽孔,记录槽孔完成尺寸,钻孔与孔位图不符时要确认(2)孔径补偿,注意孔径公差要求,孤立的钻孔考虑多补偿(3)定义钻孔属性,以客户定义的钻孔属性为主A、定义VIA属性后要察看VIA的环宽、察看VIA的开窗情况是否与客户要求一致。

GENESIS2000制作资料步骤

GENESIS2000制作資料步驟清單一.鑽孔的制作:1.去重復孔2.校正鑽孔3.定義VIA孔屬性4.孔徑補償5.短槽孔制作6.BGA分刀7.CPU跳鑽制作(當此板無插件式CPU時可省略此步驟)8.對雙面開窗的VIA孔進行處理9.鑽孔總測10.COPY AOI-NPTH層(特別注意孔數是否同DD中相符)11.機器比對原稿(公差設5mil)二.內層負片的制作1.去除成型線以外的物件2.優化正負片資料(若客戶設計隔離線非正負片疊加而成,可省略此步驟)3.去除比鑽孔小的蜘蛛PAD4.將指示分層的字母加大1MIL制作5.放大隔離PAD6.檢測隔離PAD放大的結果7.補細絲8.看導通寬度9.成型削銅10.總測11.比對原稿12.測網絡13.機器比對原稿三. 內層正片無線路的制作1.去除成型線以外的物件2.去重復PAD3.去獨立PAD4.換銅面5.套隔離6.檢測銅皮的寬度7.放大PAD的Ring邊,補償線寬,將指示分層字母加大1mil制作8.將銅面分別移回相應內層中(移回時不改極性)9.成型削銅10.總測11.比對原稿12.測網絡13.機器比對原稿四. 內層正片有線路的制作1.去除成型線以外的物件2.去重復PAD3.去獨立PAD4.換銅面5.套隔離6.放大PAD的Ring邊,補償線寬,加淚滴7.套銅面8.檢測銅皮的寬度9.將銅面分別移回相應內層中(移回時不改極性)10.削PAD11.成型削銅12.總測13.比對原稿14.測網絡15.機器比對原稿五. 外層制作1.去除成型線以外的物件2.分析資料3.去NPTH孔上的PAD4.換PAD5.換銅面6.定義SMD屬性7.PAD的補償8. 放大PAD的Ring邊9. 檢測PAD的Ring邊放大的結果10. 線寬的補償(當資料間距較小需用蝕刻補償制作時,此時可補最小線寬)11. 套銅面(注意處理銅皮寬度是否有做到5mil以上)12. 將銅面COPY至相應的線路層13. 削間距,看IC縮線14.加淚滴,補針孔15.蝕刻補線(若前面補線已符合要求達到最佳值時可省略此步驟)16.獨立線的加補17.成型削銅的處理18.檢測PTH孔上的PAD間距是否有6MIL以上19.加UL MARK(若UL MARK需以文字方式添加可省略此步驟)20.總測21.比對原稿22.測網絡23.機器比對原稿六. 防焊制作1. 刪除工作稿M1及M4層中的資料2.手動制作M1及M43.挑pad的狀態4.挑ON PAD的狀態5.削防焊PAD間的間距6.削BGA pad的間距7.防焊爆油的檢測8.防焊VIA孔單面開窗的處理9.比對原稿10.總測11.機器比對原稿七. 擋點的制作1.按要求挑擋點的狀態2.削擋點的間距3.擋點的檢測4.檢查八.文字制作1.去除成型線以外的物件2.查看文字的線寬是否在5mil以上,不足的要加寬至5MIL.3.加大文字框4.移文字,看是否有鏡象字體5.用防焊反套文字6.加廠內料號及UL MARK7.比對原稿8.總測9.加模序號。

精编CAM工程师Genesis基础─阻抗设计资料

阻抗设计如果我们制作的资料有阻抗的话,我们要新建阻抗条的STEP单元,如有多个阻抗条,我们依次命名为,ic、ic1、ic2...等等,如下图所示:然后我们一个个阻抗条的去编辑,打开一个阻抗编辑窗口,先建一个阻抗条大小的PROFILE线,一般情况下阻抗条的尺寸为0.6〞* 8〞,具体见资料夹中一页的Planner的指示。

如下图所示:如排在折断边的阻抗条大小要根据折断边的大小去设定。

在确定阻抗条大小后,执行菜单命令Step Panelization Panel size...,执行上图命令打开如下图所示对话框窗口:在这里输入阻抗条的宽度,在这里输入阻抗条的高度,直接点击按钮即可,如下图所示:然后再根据PROFILE线去建OUTLINE线,执行菜单命令Step Profile Create Rout...,如下图所示:执行上图所示命令打下如下图所示的对话框窗口:在上图的这里点击选择OUTLINE 层,在这里输入建OUTLINE的宽度,直接点击按钮即可。

如下图所示:然后打开钻孔层,根据Planner的指示,根据阻抗示意图在钻孔层添加阻抗孔和定位孔,如下图所示:43.3mil的孔为阻抗孔,126mil的孔为阻抗条成型定位孔,添加阻抗孔和定位孔可以通过增加物件命令去实现,点击增加物件按钮,再选择增加PAD按钮,然后在输入阻抗孔的大小,如43.3mil,在添加钻孔的时候尽量先把孔的属性加上去,阻抗孔肯定是PTH孔,而定位孔肯定是NPTH孔,点击这里,然后再点击后面的“”处,弹出如下图所示的对话框:然后在上图输入“drill”并回车,如下图:然后用鼠标点击上图的处,显示如下图所示:然后再用鼠标双击处,在上图的右边窗口会有如下图所示显示:然后关闭上图的对话框,如下图所示:现在加上去的钻孔就有孔属性了。

然后点击如下图所示位置,选择Profile的左下角,将阻抗孔先加于Profile线的左下角,如下图所示:再选择这里并双击后,然后点击窗口下方的执行按钮,将阻抗孔加于Profile线的左下角,如下图所示:然后根据示意图上的坐标我们将上图加的阻抗孔移到相应的位置,如坐标为(0.25、0.25),然后选择并移动,在窗口左下角处选择相对坐标按钮,然后输入我们的坐标值并回车即可,如下图所示:移动后的钻孔如下图所示:然后根据示意图上所示阻抗孔的个数,将上图所加的孔在X方向和Y 方向上复制几个,注意我们阻抗孔的测试孔和参考孔的中心间距一定是100mil,特殊情况依Planner的指示,然后我们执行阵列COPY 的菜单命令Edit Copy Step&Repeat...,如下图所示:打开上图阵列复制对话窗口,如下图所示:在输入X 方向的阻抗孔个数,在输入Y方向阻抗孔的个数,在输入X、Y方向阻抗孔的中心距,数据填好后,直接点按钮即可将原先选中的一个阻抗孔在X和Y方向按要求复制出来。

genesis教程

初步处理前提条件1:检查D码是否有误。

2:查看GERBER图形资料是否有误。

3:注意钻孔的读入是否有误。

就是保证资料正确的读入了。

制作要求1:对应MI查看层别命名是否有误。

2:对应MI查看各层图形资料是否有误或明显错误之处。

3:查看层别的排列及属性定义是否有误一般流程操作详解1,层的命名统一命名是为了方便分工协作,比如后工序知道菲林属于那一层根据各个工厂的内部规定不同,有各自的命名规则。

正确命名是自动排序的前提下面以欣强命名规则举例:假设有一块六层板,其中第二和第五层为内层负片。

欣强命名如下顶层文字Top Silk Screen CM1顶层防焊Top Solder Mask SM1外层的顶层Top Layer L1内层第一层Power Ground (GND) PG2内层第二层Signal Layer L3内层第三层Signal Layer L4内层第四层Power Ground (VCC) PG5外层的底层Bottom Layer L6底层防焊Bottom Solder Mask SM6底层文字Bottom Silk Screen CM6附注:能否根据原来文件名就可看出该层属于那一层?详见《CAD资料转CAM资料》一般来说是可以的,要看你的CAM文件是用那种CAD软件输出的,因为每种CAD软件输出CAM文件时,都会按它自己默认的规则去给文件取名,更详细的说明见有关转资料的文章,常用CAD软件有PowerPcb、Protel99,CAM软件有Genesis、CAM350、V2001等2,层排序为了方便做板,按一块成品板的结构从上到下排列层的顺序,如上面列表中的顺序。

Ctrl--X 可以把选中的一层移动到鼠标点击处的上一位置 Job Matrix 可叫为层别特性表(工作矩阵),用来对层进行命名、排序、定义属性。

3。

定义层的属性(共三种属性)为了让系统正确处理某层,比如优化时的表达式能指定符合条件的层进行优化A> 层范围 ContextBoard 板层,属于物理板的一部分的层都要定义此属性Misc 附属层,任何层和文档说明的层都可定义此属性(默认属性)B> 层类型 TypeSignal 信号层(默认) Mixed 混合层 Solder Mask 防焊(绿油)层 Silk Screen 文字层 Drill 钻孔层 Rout 锣带(成型)层Solder Paste 贴片(锡膏)层 Docunment 文字说明用的层Power Ground 用做接地(隔离)或散热的那些内层负片一般应定义此属性C> 层极性 Polarity Positive 正片Negative 负片(用颜色标识的地方是无铜区,即基材,正片与之相反而已) 无论那一层都应具备以上三种属性。

GENESIS全套资料制作流程

进入pcs中点击Job Matrix,将原稿线路、防焊、文字、钻孔选中,按ctrl +c复

制一份+1层再ctrl +v粘贴到原稿区上端,并将此+1层更改层名、层位并定义

点 其相应的属性。则此被修改前为+1层的为修稿编辑层,原稿层仅供制作修稿

击 此

时的核对参考。

处

属性栏

厂 内 工 作 稿

原 稿

Job Matrix 操作在下面 两页有讲述

执

点击此

行

栏

后

删除重孔:在DFM菜单下选红色框示中的命令出现此对话框,参数按上图调整。点击红色 框的指令,执行后 会有不同的颜色显示,需点击放大镜查看结果。(执行此命令后系 统会自动生成一层执行命令前未改变内容的层,后缀为+++)

工作层 参照层(线路或者原稿孔位图)

偏差?Mil以内自动对正 偏差?Mil以内报告出来

线路参照防焊转Pad:在DFM菜单下Cleanup—Construct Pads (Auto.)会出现如上图的对话

框,参数按上图调配。若自动转Pad不成功,则选中它采取手动转Pad命令.Construct Pads (Ref.) 两层外层线路均需转Pad

选择 不选择

POS 极性为正性 NEG 极性为负性

Matrix概述

点击層名格即显 示出该层修正欄 (在修正栏中更改 层名、定义其相

应的属性)

鑽孔貫 穿情形

不同顏色代表 不同層次特性

Steps

綠色表該 層含資料

(双击该格 会显示该格 中的内容)

调整层位方法:1. 选择欲移动之层 2. 按ctrl +x(移动快捷键) 3. 点击要移去的位置 1

Genesis制作资料步骤

二 Matrix制作以标准4层板为例定义各层属性按制板顺序用<Ctrl>X命令对各层进行排序表1positive 钻孔 board drill外形 board rout positive 组件面字符 board silk_screenpositivepositive 组件面阻焊 board solder_mask组件面线路 board signal positivenegativepower_ground地层 boardnegativepower_ground电层 board焊接面线路 board signal positivepositive 焊接面阻焊 board solder_maskpositive 焊接面字符 board silk_screen1 正确排列层次的依据有以下几种a 客户提供层次排列顺序b 板外有层次标识c 板内有数字符号标识如12342 判断每层为正负性的一般性依据为焊盘中心为实体是正性焊盘中心为空心是负性三 orig制作orig制作由以下三部分组成1 层对位制作步骤a 选中所有层以钻孔为参考层用register功能使线路地电阻焊与钻孔实现自动对位b 其它层包括字符层需手工移动整层使外边框与组件面线路层的外边框重合必要时需镜像检查方法a 各层焊盘中心应与钻孔中心对齐b 各层外边框应相互重合c 组件面字符为正字焊接面字符为反字2 line转pad制作步骤a 打开阻焊层的Features Histogram在Lines List中选中所有按Highlight对照线路字符判断是否需要转焊盘b 同时选中并打开组件面线路和组件面阻焊按<Ctrl>W命令至骨架显示方式用面板中↖选定需转换的line一般在线的末端然后用DFM Cleanup Constructpads(Ref.)功能逐类进行转换焊接面方法相同c 用步骤a的方法检查除边框线和大面积喷锡块外line均已转换完毕d 如有r形line被转为oval形pad运用Actions reference Selection功能将线路层所有oval参考阻焊层选择将被阻焊层Covered的oval移出和阻焊层oval数量相同其余oval用Edit Reshape Break命令打断回line最后将移出的oval移回线路层此操作在有正负性迭加时慎用3 定义SMD运用DFM Cleanup Set SMD attribute功能参数Types Other设为*自动将外层线路未钻孔的焊盘设定为SMD在Matrix中将原edit删除复制orig为edit以下操作如未特殊注明均在edit 中进行四外形制作外形制作有两种方式1 按客户光绘文件制作步骤a 用面板中Select by net选定组件面线路边框复制到rout层b 删除所有圆弧c 检查线的数量例如长方形应有四根线删除多余的线d 检查线的角度常规线的角度应为0﹑90和45如为0.1,多为客户设计失误需征求市场部的处理意见e 用Rout Connections功能重新连接线线交点和倒角圆弧线属性应为arcf 将线宽改为r10mil2 按客户标注尺寸制作步骤a 在Matrix中创建rout层b 在Options Line parameters功能中选定第5项c 用面板中Add feature功能在rout层中按客户标注尺寸手工绘制外形线宽设为r10mild 用Rout Connections功能辅助连接线线交点和倒角至外形完成e 如果Rout层有Rect 或Oval等实体需将其转化为轮廓线方法先选中实体点击EditÆReshapeÆcontourise 变成Surface ,执行Surface to outline,输入线宽值即可转化为轮廓线外形完成之后用Select by net命令选中外形图形然后用Edit Create Profile 命令创建Profile五钻孔编辑1钻孔制作步骤a 打开Drill Tools Manager对照客户提供的钻孔图检查钻孔文件中孔径孔数和孔属性是否正确如无钻孔图则直接以钻孔文件为准b 将孔径较小分布不规则的过孔属性由plt改为viac 按钻孔刀具补偿规则输入每种孔对应的钻孔孔径d 用Analysis Fabrication Drill Checks功能分析钻孔层检查分析结果是否异常e 如有重孔用NFP Removal功能参数Delete选Duplicate自动将钻孔及相应层的重盘去除f 如有交叉孔手工删除交叉孔中较小的过孔及各层相应焊盘若为器件孔交叉不可删除需在交叉孔两端增加两个与交叉孔相切的预钻孔理论上预钻孔孔径=交叉孔中心距+交叉孔孔径/2然后用去尾法选择孔径原则上选板内已有钻孔孔径例两交叉孔孔径为2.15mm中心距为1.00mm计算出孔径为1.575mm则选预钻孔孔径为1.55mm2 钻槽制作a 在钻孔层将所需钻槽形状用Edit Reshape Change Symbol命令改为oval例钻槽3.00X1.00形状为oval3X1b 将oval用Edit Reshape Break命令打断成linec 若所需钻槽长宽比2需在槽两端增加两个预钻孔方法同交叉孔六钻孔外形图制作制作步骤a 将rout层用Edit Copy Other Layer命令复制到新一层tmp并加大5milb 在tmp层中用Add feature功能标注完整正确的外形尺寸尺寸线和尺寸界线线宽为r5mil箭头用special symbol jian/jian45尺寸值Text参数按XY均为80mil线宽为5milc 用Creat Drill Map功能自动产生钻孔图单位定为mm钻孔图命名为mapd 将tmp层中所有图形移至map层客户钻孔图中的说明文字也移至map层合并成钻孔外形图e 删除tmp层七线路层制作1 板外图形删除a 选中除rout层外的所有board层用面板中↖逐一选定外形边框并删除b 运用Clip Area功能参数Method选profile参数Clip area选outside自动删除板外图形c 检查并删除板边未除净的图形2 挑表面贴a 选中组件面线路层在面板中打开Feature selection filter功能在Attributes 中选smd后按select即可选中组件面线路层所有表面贴b 将组件面线路层所有表面贴移出至新一层gtl检查组件面线路层剩下的焊盘数量是否等于钻孔数如数量相等则证明表面贴属性定义完全如不相等需找出未定义表面贴属性的焊盘选Edit attributes Chang功能在attributes中选smd然后按OK手工定义剩下的表面贴并移至gtl层c 将gtl层所有图形移回组件面线路层如需补偿SMD可在移动同时按要求加大d 选中组件面线路层所有表面贴加大11mil复制到新一层D10参见字符制作规范e 在D10层r形D码中找出识别点确定识别点位置将组件面线路层板边识别点加铜环铜环外径比内径大1mm内径比识别点阻焊开窗大1mm不可碰到周围图形f 焊接面线路层制作方法同上3 线宽补偿a 选中所有线路层在面板中打开Feature selection filter功能关闭PadsSurfaces Text和Negative elements按钮按select选中所有需补偿的线然后用Edit Resize Global功能加大加大值见b 对阻抗控制线按阻抗要求进行单独补偿4 盘对位选中所有board层用DFM Pad Snapping功能使各层焊盘参考钻孔层对位偏位在2mil以上不会移动制作人员需提出5 线路层孔焊盘优化a 选中组件面线路层采用DFM Signal Layer Opt功能按默认参数优化焊盘检查优化结果如出现ARG violation(min)报告则说明由于间距不够有焊盘未被优化先Undo此优化步骤再打开柱形图查看未被优化焊盘的孔径属于Via还是Plt然后以0.5mil为一级逐级降低此孔对应的焊环参数重新优化直至优化完成焊环可接受参数见外层制作规范维持现有参数对焊接面线路层进行优化b 内层焊盘优化方法与外层相同焊环可接受参数见内层制作规范c 将组件面线路层孔焊盘移出至gtl层将gtl层属性改为board+ signal+ positive 用DFM Signal Layer Opt功能对gtl层焊盘重新优化参数PTH AR和VIA AR维持原设定参数Spacing和Drill to cu改为0优化完成后将gtl层中所有图形移回组件面线路层焊接面也重复此步骤注所有外层使用相同的优化参数所有内层也使用相同的优化参数外层与内层参数可以不同6 无功能焊盘去除a 用DFM NFP Removal功能自动去除内层未连线焊盘将参数Drill中PTH和Via 选项关闭参数Remove undrilled Pads改为No自动去除外层NPTH焊盘b 检查去除的外层NPTH焊盘数是否和NPTH孔数一致c 如NPTH落在大焊盘上大焊盘不可去除NPTH落在大焊盘和大铜皮上需挖开单边挖开值见表二孔径外层掩孔工艺外层图电工艺内层表二NPTH距周围铜皮的最小距离孔径外层掩孔工艺外层图电工艺内层0.20mm2.0mm 0.20mm 0.20mm2.0mm3.0mm 0.20mm 0.30mm 0.20mm0.20mm3.0mm 0.20mm 0.40mm表三NPTH距焊盘的最小距离孔径外层掩孔工艺外层图电工艺内层0.20mm2.0mm 0.30mm 0.20mm2.0mm3.0mm 0.35mm 0.30mm 0.20mm3.0mm 0.40mm 0.40mm0.20mm表四NPTH距线条的最小距离7 外形露铜问题处理外形不允许露铜将Rout层用Edit Copy Other Layer功能复制到各线路层并按要求加大参数Invert选Yes检查不可有线被迭到表五为不同外形加工方式下内外层图形距外形线中心的最小距离表五外形允许露铜对于外形铣方式外层图形距外形5mil采用其它外形加工方式时视具体情况而定8 图形电镀工艺时网格处理a 选中有网格的外层若大部份网格宽度8mil使用DFM Pinhole Elimination 功能参数Max Size设为8mil Select By选width Action只选Cover holes 自动进行糊网格处理若大部份网格宽度8mil需视具体情况而定b 相同网络的小缝隙若宽度3mil需手工糊实9 线路层分析用Analysis Fabrication Signal Layer Checks功能分析所有线路层对分析不合格处进行单独处理完成后重新分析直至结果合格表六线路层分析结果的可接受值10 过孔环宽按最大制作按最大制作思路在保证最小间距的条件下将过孔环宽做成最大值所谓最大值就是将过孔环宽按文件规范中最优值制作时间距无法满足加工要求的地方按最小值处理外其余的过孔环宽均按最优值加大CAM单板具体制作方法及步骤按原线路层制作规范对其调整完毕后点击DFMÆSignal Layer Opt将PTH AR Min Æ0 mil PTH AR Opt Æ0 mil VIA AR Min Æ(该板的过孔最小环宽值) mil VIA AR Opt Æ(7 & 8) mil;Spacing MinÆ4mil;Space Opt Æ4mil;其余参数均为缺省值自动完成优化即可八地电层制作a 将rout层复制到所有地电层并加大90milb 选中所有地电层按不同孔径调整对应梅花盘的内径和外径见表七按梅花盘的不同外径选择开口宽度见表八梅花盘的开口角度为45表七表八当客户设计梅花盘外径大于表七中值保持客户设计外径按外径-内径=内径-孔径的规则调整内径c 按不同孔径调整对应隔离盘的大小见表九d 当隔离盘间距小于5mil时如某些BGA处需改小隔离环至0.25mme 梅花盘开口需2个如不满足要求可改梅花盘的开口角度为0如仍不满足要求删除此梅花盘f 用Analysis Fabrication power/ground Checks功能分析所有地电层如不满足要求经手工调整后再分析如此循环直至分析结果合格g 肉眼检查无明显孤岛表十地电层分析结果的可接受值九 D11制作a 将组件面阻焊层中所有Lines移出至新一层gts检查是否有开小窗现象阻焊开窗比对应焊盘小将小窗焊盘也移至gtsb 选中钻孔层用Actions reference Selection功能参考组件面阻焊层进行选择参数Mode选Disjoint选出与组件面阻焊层不相碰的孔复制到新一层1此层为阻焊覆盖的孔参数Mode改为covered选出被组件面阻焊层覆盖的孔复制到新一层2此层为阻焊露出的孔c 检查1+2层的焊盘数应等于钻孔数d 选中12层在面板中打开Feature selection filter功能在Attributes中选NPTH Drills后按select选中所有NPTH孔移至新一层3e 将123层焊盘分别复制到新一层jobc-a.d11(即组件面D11)并相应加大加大值见过线孔阻焊制作规程将jobc-a.d11层的属性改为board+ document+positivef 焊接面D11按相同做法制作层名为jobs-a.d11十阻焊层制作a 选中组件面线路层用DFM Solder Mask Opt功能进行阻焊优化ERF参数选SHENNAN-E80Clearance Opt参数设定见bb 在间距允许的条件下阻焊开窗尽可能大(单边阻焊开窗3mil铜箔厚度3OZ除外)以此解决现场板对位困难及油墨上焊盘问题CAM单板具体制作方法及步骤阻焊优化参数选取的依焊盘开窗处线路最小值间距来确定我们现在使用的GENESIS 2000 CAM软件阻焊开窗只能按一个值来优化阻焊优化参数clearance (min)+ coverage(min) = spacing(min) ,其中clearance 焊盘阻焊开窗coverage开窗到线条的距离spacing线路的最小间距阻焊优化参数选取方法为当线路间距4mil时clearance (min)Æ2.5mil; clearance (opt)Æ3.0mil视间距而定可3mil缺省为3mil;coverage(min)Æ1.5mil; coverage(opt)Æ1.5mil这样一来板内间距大的地方阻焊开窗就可以做到3mil,间距较小的地方无法达到3mil按2.5mil制作c 同时打开组件面阻焊层优化前和优化后的图形肉眼检查无明显的尺寸与形状变化d 用Analysis Fabrication Solder Mask Checks功能分析优化后的组件面阻焊是否符合表十一要求如不符合需手工调整直至分析合格项目最小值备注NPTH annular Ring Clearance Opt参数值SMD annular Ring Clearance Opt参数值Pad annular Ring Clearance Opt参数值针对非同一网络CoverageSM Slivers表十一阻焊层分析结果的可接受值e 选中1层用Actions reference Selection功能参考gts层进行选择参数Mode 选Disjoint关闭lines Surfaces Text Arcs Circles按钮选出阻焊未开窗的孔复制到新一层tmp在tmp中将孔径改为成品孔径后移至组件面阻焊层删除tmp层f 将gts层中的Pads移回组件面阻焊层g 将gts层中的Lines移回组件面阻焊层h 检查组件面阻焊层的焊盘数等于组件面线路层的焊盘数+NPTH孔数i 焊接面阻焊层按相同做法制作十一 BGA塞孔制作a 将组件面线路层和焊接面线路层的BGA焊盘复制到新一层2mmb 将2mm层中的所有焊盘大小改为s4000m方块中间空白处需填实c 选中钻孔层用Actions reference Selection功能参考2mm层进行选择参数Mode选Touch将所有与2mm层相碰的孔即BGA2mm范围内需塞的孔复制到Job.bga并复制Job.bga为Job.sdbd 按过线孔阻焊制作规程更改Job.bga塞孔模板和Job.sdb塞孔垫板中的孔径e 选中D11层用Actions reference Selection功能参考Job.bga层进行选择参数Mode选Touch将所有与Job.bga层相碰的焊盘删除删除数量应与塞孔数量相同f 选中阻焊层在面板中打开Feature selection filter功能在Include Symbols 中选阻焊层中与成品孔等大焊盘和开小窗焊盘用Actions reference Selection 功能参考Job.bga层进行选择参数Mode选Touch将与Job.bga层相碰的焊盘删除十二字符层制作a 按工艺通知关于字符宽度的工程CAM制作要求修改字符线宽b 在Special symbols中选择标记按客户要求放置标记应加在空白处不可碰到阻焊外形和线路面铜字c 按字符制作规范制作D10d 将D10层复制到对应字符层Invert选No十三网络比较a 打开Actions Netlist Analyzer功能Step分别选orig和edit Type均选current分别按Recalc按钮b Recalc完成后将上一个current改为Reference按Update弹出Ref Netlist Update对话框在Action中选Set to CUR netlist后按OKc 按compare即可比较orig和edit之间的网络关系如果shorted和broken未变红则说明结果正确。

genesis入门基础.0

基础知识下面为PCB基本流程图,后面附有文字解说:值得说明的是:上图中有的地方可因各个工厂的机器设备不同或采用的技术不同而有出入,即使是一个厂内,有时也可以针对性的改进流程设备,这也会不同于上面所说的。

而且,有时某种板不需要某步或按不同的流程制作,同样会不同于上图所述。

一、工具/资料制作MI组/客户Gerber资料检查客户资料完整性,可制造性(即与本厂制程能力的一致性),有疑问时问客户核对此步没做好会影响GENESIS读资料时不完全MI组/QAE 依客户要求并结合本厂实际定出工艺路线及基本要求、拼版、开料图、成型图等,后工序则根据其中的相关资料去制作这些都是GENESIS处理CAM资料的依据,每个厂都有自己的这方面的规定:包括一般情况下的要求(MI没规定时按此要求处理,因为这些要求符合本厂机器设备的制程能力)和特殊情况下的要求(即MI注明的要求),显然MI要求优先CAM 用某种CAM软件,依MI要求做出相关机器用的文件:内层菲林光绘文件、外层菲林光绘文件、钻孔文件文字菲林(碳油)光绘文件、成型(锣带)文件等。

后面实际制作时,机器就是读进相应的文件,按文件内容自动进行操作,比如钻孔机读进钻孔文件后就是按钻孔文件的内容去钻孔。

因为线路板厂机器不能直接读客户原始资料,再加上存在误差,所以CAM就是用来把客户原始资料处理为本厂机器能识别的文件,当然在处理时进行了误差方面的补偿。

本教程的重点所在,讲述如何用GENESIS软件来设计生产线路板要用的资料文件E-TEST组制作测试程式光绘用光绘机读进制作好的光绘文件,绘出所有生产时图象转移要用的菲林检查组/QAE 检查所有菲林、钻孔程式、成型程式等与MI要求的一致性1、内层菲林:一般为负片(即爆光时,线路位爆光,显影后膜保留),但其对应的Gerber文件的极性却有正负之分。

2、外层菲林:碱蚀时为正片(即爆光时线路位不爆光,显影后干膜去除);酸蚀时内层菲林.但其对应的Gerber文件的极性都为正的.3、防焊菲林:正片4、文字菲林:正片注意:各层面必要时需要镜像的还需根据复棕片面考虑镜像二、工艺流程开料裁板基板(又名覆铜板)一般尺寸为41″*49″37″*49″、43″*49″(这影响GENESIS的排版)铜箔厚度不同(这影响GENESIS里的蚀刻补偿)内层磨板增加板面粗糙度,使铜面与内层感光油或干膜的结合力加强辘油或贴膜辘油是用辘油机给板面涂上感光油,机内后段一般为烘干段(因此要冷却后继续下工序)贴膜是用贴膜机在板面贴上感光用的膜显然,只需采用上面一种方式加感光材料爆光用爆光机将内层菲林上的图像转移到有感光材料的板面上(这里用的内层菲林就是GENESIS处理好的内层Gerber文件通过光绘机绘出来的,涉及对位孔)显影将未爆光部分的油墨除去,露出铜面蚀刻/去膜显影后露出的铜经过蚀刻段将被蚀刻掉,再经过退膜、水洗、烘干,除去残余油墨,露出需要的线路(这里就要蚀刻补偿,即用GENESIS处理内层文件时加大其中过小的线路)AOI或目视关位层目视残铜;线路层AOI检查开路、短路、缺口、残铜等缺陷(涉及光学点、关位孔)棕化线路铜面经化学反应在表面形成一层棕色膜,增强内层板与PP间的结合力压合预排按MI规定,选用正确型号的PP与内层板组合,并在最外层放置铜箔,叠齐放在钢盘中热压/冷压通过施加压力和高温, PP会融化并重新固化,使各层结合为一体,再通过冷却加压使板减少变形拆板/分割整盘的板分割成WP钻靶将钻孔要用的定位孔钻出(涉及钻孔用定位孔)锣边/磨边将四板边用成型机锣整齐,并把板边磨成弧形,减少后工序刮伤板面钻孔依CAM制作好的钻孔程式,钻机钻出所有需要的孔,以便镀铜后连通所需层面及工具孔(涉及钻孔制作和加工艺孔)PTH磨板除去钻孔时产生的披除胶渍除去孔壁因钻孔时高温产生的胶渍PTH 化学方法使孔壁上沉一层薄铜,以做后续电镀铜的基础电镀加厚孔壁及表面铜,使之符合MI要求,最后烘干板面,减少氧化(以上涉及PTH孔)外层磨刷增加板面粗糙度,以增强干膜与铜面的结合力贴膜在铜面上贴上感光材料:干膜爆光将外层线路菲林上的图象转移到板面上显影将板面未爆光部位的干膜用药水除去,露出需加厚的铜(此为碱蚀工艺;若酸蚀则跟内层线路蚀刻一样)图形电镀把露出的铜加厚,再镀上纯锡做为防蚀刻用褪膜/蚀刻褪去干膜后,把未被锡盖住的铜蚀刻掉褪锡把蚀刻后的板面上的锡褪掉,就得到所要的线路(涉及外层设计,如外层令环宽度<5.5mil时应走碱蚀)AOI或目视防焊磨板加强线路铜面粗糙度,以增强油墨与铜面的结合力丝印将油墨印于板面,并烘干对位/爆光用防焊菲林拍板后,将图形转移到板面显影将未爆光部位的油墨除去,烤干后充分固化,使油墨附于板面(涉及防焊设计)化金磨板除去氧化及板面粧污化学镍/金于未上防焊的铜面上镀上镍/金,以利客户贴元件或插元件,最后烘干,防止氧化电金手指插接位使用电镀金,加厚使其更耐插拨(涉及金手指制作和电金引线)喷锡(HAL)在接点面上喷熄,平滑度适合SMD装配线文字按MI要求印出零件指示字符,方便客户生产图象转移流程同上面(涉及文字设计)成型按要求锣出外围(涉及锣带制作、V-CUT)电测即通/断路测试,确保电气性能目视外观检查,确保符合客户要求包装附:图象转移酸蚀与碱蚀制造印制板过程中的一道工序就是将照相底版上的电路图像转移到覆铜箔层压板上,形成一种抗蚀或抗电镀的掩膜图像。

Genesis操作概述(钻孔层制作)

Genesis操作概述__鑽孔層製作1、建立相關層及outline層製作1)建立相關層:shfit+F4→第2個→next(此部份在原稿製作時已完成)2)outline層製作a.找出有成型框的層,并選取其成型線b.利用Edit→ Copy → Other layer(圖1) →在layer name后的方框內輸入outline(做好后與機構圖再比對下,防止客戶製作資料的成型線不完整)c.放大新建outline層之成型線線寬至10mil,操作如下:Edit→Reshape→ change symbol(圖2)把outline的成型線改成10mil(輸入r10,右下角單位選inch),原來各層的成型線都不需變動,之後若需要放大成型線或套成型線負片都只使用outline層的即可。

(圖1) Edit > Copy > Other layer copy(圖2) Edit > Reshape > change symbol注:若以單pcs出貨時,則成型線製作成方形方法:用+shift單選4個邊最外圍的線,并執行edit→create→profile2、定profile及datum(確認原點座標)1)將成型線Profile化(輪廓化)用連線功能選擇成型線,并執行Edit→Create→Profile自動產生出圍繞成型框的Profile 。

若是遇到成型框較複雜時可能無法自動產生,可利用Step → Profile → Rectangle指令,在座標區輸入成型框左下角與右上角兩點的座標(或者直接於圖面中點還),即可產生矩形的profile。

2)、定datum(確認原點座標)利用ctrl+x功能將角度歸零3、刪除工作稿板外物(清除pcb 成型線外不需要的物件),outline 層不選將鑽孔、內層、外層、防焊、文字、錫漿層的板外物刪除(成型線外的)1)在影響層區按右鍵,選擇Affected layer (若有機構圖層,該層可不勾選予以保留)。

Genesis制作资料步骤

Genesis制作资料步骤 时间:2005-03-22 15:48 来源:中国PCB论坛网点击: 3862次一Matrix制作以标准4层板为例,定义各层属性,按制板顺序用CtrlX命令对各层进行排序。

(表1)钻孔board drill positive 外形board rout positive 元件面字符board silk_screen positive 元件面阻焊board solder_mask positive 元件面线路board signal positiv一 Matrix制作以标准4层板为例,定义各层属性,按制板顺序用<Ctrl>X命令对各层进行排序。

(表1)钻孔 board drill positive外形 board rout positive元件面字符 board silk_screen positive元件面阻焊 board solder_mask positive元件面线路 board signal positive地层 board power_ground negative电层 board power_ground negative焊接面线路 board signal positive焊接面阻焊 board solder_mask positive焊接面字符 board silk_screen positive1 正确排列层次的依据有以下几种:a 客户提供层次排列顺序;b 板外有层次标识;c 板内有数字符号标识,如“1、2、3、4……”。

2 判断每层为正、负性的一般性依据为:焊盘中心为实体是正性,焊盘中心为空心是负性。

二 orig制作orig制作由以下三部分组成:1 层对位制作步骤:a 选中所有层,以钻孔为参考层,用register功能使线路、地电、阻焊与钻孔实现自动对位;b 其它层(包括字符层)需手工移动整层,使外边框与元件面线路层的外边框重合,必要时需镜像。

GENESIS全套资料制作流程解析

再双击鼠标左键进入steps下,然后再File---Create建立org.

原稿存放的路径

点击Windows菜单中Input,将原稿从所在路径中调出,Job栏填写料号名,step栏填写org,然后 分别按Identify和Translate两个命令即可调入原稿(注意:当调入资料颜色非绿色时,则要查看报告说 明或上报处理).

点击此 栏

执 行 后

删除重孔:在DFM菜单下选红色框示中的命令出现此对话框,参数按上图调整。点击红色 框的指令,执行后 会有不同的颜色显示,需点击放大镜查看结果。(执行此命令后系 统会自动生成一层执行命令前未改变内容的层,后缀为+++)

孔 属 性 栏

成 品 孔 径 栏

补 偿 后 孔 径 栏

输钻孔表:在钻孔层单击右键,选Drill tools manager 即出现钻孔表,根据生产指示钻孔 表中对应的成品孔径、孔数输入补偿后的孔径(NC孔径)及属性,输好后点击Apply。需注 意单位为mm。

形状 X尺寸 Y尺寸

自动抓点

配合锁点功 能手动抓点

工作层 (必须是显示层) 层別的显示颜色, 方形最多可显示四層 锁点层 (必须是显示层) 层別的显示顏色, 圆形代表可显示非常多层

层別显示区 影响层区 层別功能区

影响层 (可不是显示层)

箭头, 代表有物件选择

箭头, 代表有物件选择 (可不是显示层)

右 键 点 此 处 出 现 如 下 多 选 框

此 参 数 可 调 配

如在内层Gerber中没有线路和Thermal pad,则需上报上级判断正负片

回復上次動作 刪除 移動 複製 修改尺寸 變形 連接 暫存區 修改形狀 極性 新增 修改 屬性

同層移動 移動到其它層 平行線伸縮 直角的伸縮移動

genesis制作

一、Matrixr制作(定义各层属性)以标准4层板为例,定义各层属性,按制板顺序ctrl+X命令对各层进行排序。

钻孔: board drill positive外形: board rout positive元件面字符 board silk screen positive元件面阻焊 board sold mask positive元件面线路 board siginal positive地层 board power ground positive电层 board power ground positive焊接面线路 board siginal positive positive焊接面阻焊 board sold mask positive焊接面字符 board silk screen positive内层正图定层属性跟外层一致:1.正确排列层次的依据有以下几种:a:客户提供层次排列顺序。

b:板外有层次分别标识。

c:板内数字符号标识。

如:1、2、3、4……等2.判断每层为正、负性的一般性依据为:焊盘中心为实体是正性,焊盘中心为空心是负性。

内层有花盘的为负性。

二、Orig制作:1.层对位制作步骤:a:选中所有层,以钻孔为参考层,用register功能,使线路、地电、阻焊与钻孔实现自动对位。

b:其它层(包括字符层)需手工移动整层,使外边框与元件面线路层的外边框重合,必要时需镜向。

检查方法:a:各层焊盘中心应与钻孔中心对齐。

b:各层外边框应互相重合。

c:元件面字符为正字,焊接面字符为反面。

2.将所有层设为影响层,执行ctrl+X移动命令,捕捉板的最外点到零点。

3.设有外框线的层为工作层,若外框线不规范则需整理,用网络选取命令,选择外框线再定义profile(edit-creaet-profile)三、Edit前处理1.把板层设为影响层,用Clip Area功能,参数Clip Area选affected layets参数Method选profile,参数Clip Area选outside margin设20um,自动删除板外图形。

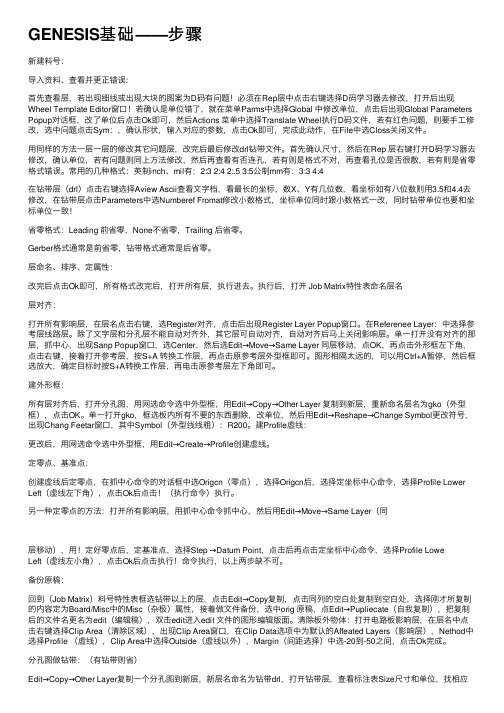

GENESIS基础——步骤

GENESIS基础——步骤新建料号:导⼊资料、查看并更正错误:⾸先查看层,若出现细线或出现⼤块的图案为D码有问题!必须在Rep层中点击右键选择D码学习器去修改,打开后出现Wheel Template Editor窗⼝!若确认是单位错了,就在菜单Parms中选择Global 中修改单位,点击后出现Global Parameters Popup对话框,改了单位后点击Ok即可,然后Actions 菜单中选择Translate Wheel执⾏D码⽂件,若有红⾊问题,则要⼿⼯修改,选中问题点击Sym:,确认形状,输⼊对应的参数,点击Ok即可,完成此动作,在File中选Closs关闭⽂件。

⽤同样的⽅法⼀层⼀层的修改其它问题层,改完后最后修改drl钻带⽂件。

⾸先确认尺⼨,然后在Rep 层右键打开D码学习器去修改,确认单位,若有问题则同上⽅法修改,然后再查看有否连孔,若有则是格式不对,再查看孔位是否很散,若有则是省零格式错误。

常⽤的⼏种格式:英制inch、mil有:2:3 2:4 2:.5 3:5公制mm有:3:3 4:4在钻带层(drl)点击右键选择Aview Ascii查看⽂字档,看最长的坐标,数X、Y有⼏位数,看坐标如有⼋位数则⽤3.5和4.4去修改,在钻带层点击Parameters中选Numberef Fromat修改⼩数格式,坐标单位同时跟⼩数格式⼀改,同时钻带单位也要和坐标单位⼀致!省零格式:Leading 前省零,None不省零,Trailing 后省零。

Gerber格式通常是前省零,钻带格式通常是后省零。

层命名、排序、定属性:改完后点击Ok即可,所有格式改完后,打开所有层,执⾏进去。

执⾏后,打开 Job Matrix特性表命名层名层对齐:打开所有影响层,在层名点击右键,选Register对齐,点击后出现Register Layer Popup窗⼝。

在Referenee Layer:中选择参考层线路层。

GENESIS全套资料制作流程教学提纲

进入pcs中点击Job Matrix,将原稿线路、防焊、文字、钻孔选中,按ctrl +c复

制一份+1层再ctrl +v粘贴到原稿区上端,并将此+1层更改层名、层位并定义

点 其相应的属性。则此被修改前为+1层的为修稿编辑层,原稿层仅供制作修稿

击 此

时的核对参考。

处

属性栏

厂 内 工 作 稿

原 稿

Job Matrix 操作在下面 两页有讲述

槽长1.5mm(槽的真正长度2.35-槽宽0.85)

槽角度 槽属性

鑽孔的真正槽長

CAM 的槽長

槽孔制作:方法(2)选中要做的槽孔(注意必需是Pad属性),Edit-Change-Pads To Slots…在Symbol栏 中输入槽宽,在Length栏输入槽长(注意此处的槽长是槽真正长度-槽宽),在Angle (deg)栏中填槽角 度,确定此类槽孔的属性Plated/Non plated,最后点击Apply。

欲维持的最小间距 SMD Pad是否要对正

此为系统自 动生成的层

工作层 (必须是显示层) 层別的显示颜色, 方形最多可显示四層

锁点层 (必须是显示层) 层別的显示顏色, 圆形代表可显示非常多层

影响层 (可不是显示层)

箭头, 代表有物件选择

箭头, 代表有物件选择 (可不是显示层)

右

键

点

此

处

出

此

现

参

如 下 多

数 可

选

调

框

配

鼠标右键点击指定处--Affected Board即选择板内的(含钻孔、线路、防焊、文字或其它 须制作的工作稿资料层),然后在层别处单击右键即出现该层命令目录栏,选择Clip area 出现其工作框,其参数按照上图调整(此工作框参数可按不同需求调整)点击OK 即可切除Profile以外内容

GENESIS2000制作流程

Genesis 2000 制作流程一、解genber将客户资料解压缩存放到指定的目录建立工作料号点选工作料号,进入input画面path:解压客户资料的目录job:刚creat的料号名step:单一pcs之原稿origindentify:确认之gerber在genesis2000是否可认,查看gerber格式是否正确translate:转换成genesis2000可读的格式close备注:做indentify后,若d-code有问题,会出现红色,代表d-code有问题,再进行修改二、层的命名从step-job-matix,开启各层认识各层的性质,命名层名再定义属性(包括:字符,防焊,线路,钻孔,rout)三、层对正,建立rout,定义profile检查层与层是否对正从gerber中选中边框copy到rout层中改rout线为10mil,create profile四、归零点以及copy原稿目的:归零点是为层间对位,后续排版copy原稿是为与工作层对比,避免产生错误五、删board外feature目的:将profile线(包括边框线)外的feature删除步骤:影响board层(除rout、drill层)选定任意一层为工作层,按m3,选clip area参数method:profileclip area:outsidemargin:-5mil点ok!五、测量rout层的尺寸与mi对比六、定义drill的属性选drill层为工作层,按m3,选auto drill manger依次判断drill的属性,若不能自动补偿则手动补偿pth、vai补偿4mil(沉金、电金),喷锡补偿6mil(via可依线路pad补偿)npth补偿2mil检查drill层是否slotok只后点apply六、钻孔的analysis分析analysis—drill checks看分析报告如存在duplicate、touch,则删少留大!七、drill与pad的对正dfm—repair—pad snapping设计好参数run就ok八、copy orig 到edit再进入edit九、自动转paddfm—cleanup—construct pad(auto)..先选erf参数为mask,runok后选erf参数为outer,run检查转pad的正确性,若存在没转的pad,则dfm—cleanup—construct pad (ref)..选择没转好的pad再run一○、内层负片的制作方法步骤:先修改散热pad为genesis内认的格式把rout层copy到负片层并resize 30mil把drill层的npth copy到负片层并resize 20mil优化:dfm—optimization—power/ground opt…设置好参数点run检查:analysis—power/ground checks依检查后的报告进行修改一一、内层正片的制作方法步骤:删独立pad:dfm—redundancy cleanup—nfp removal 参数选isolate 点run补偿:edit—resize—global 一般补偿1mil优化:dfm—optimization—signal layer opt…设置好参数点run把rout层copy到负片层并resize 26mil ,极性为负把drill层的npth copy到负片层并resize 20mil,极性为负检查:analysis—signal layer checks依检查后的报告进行修改一二、外层线路的制作方法步骤:补偿:edit—resize—global 一般补偿1mil优化:dfm—optimization—signal layer opt…设置好参数点run备注:mi要求走酸蚀流程,则pth、via孔的ring单边至少为5.5milmi要求走碱蚀流程,则pth、via孔的ring可适当做少l把rout层copy到负片层并resize 4mil (若该边为v-cut,则resize 26mil),极性为负把drill层的npth copy到负片层并resize 16mil,极性为负检查:analysis—signal layer checks依检查后的报告进行修改一三、防焊的制作方法步骤:检查防焊层所有的feature是否转pad优化:dfm—optimization—sloder mask opt…设置好参数点run检查:analysis—sloder mask checks依检查后的报告进行修改备注:满足的优先级别:coverage—bridge—clearance一四、字符的制作方法步骤:检查字符线宽>5mil,字高>25milcopy防焊层的正feature到新建一层并加大6mil以字符层为工作层,新建层为参考层一起对比,与防焊接触的移动到适当位置备注:能移动的则移,不能移动则削!以mi或客户要求加厂内标志一五、原稿对比同时display处理ok层与备份层一起对比(如存在影响电气性能)一六、网络对比步骤:进入actions—netlist analyzer对话框,参数依次往下:job:当前jobstep:origtpye:先选curret 点选recalc再tpye:选reference,点选update(参数选set to cur netlist)okjob;当前jobstep:edit点选recalc再点选compare 看report只要short 、open不报错误,代表网络是ok的。

Genesis全套教程之文字制作

3、因文字需距外层 PAD 最小 6mil 以上,为了方便起见,我们将防焊层加 大 16mil Copy 到别一层(建议命名 cmask+16)辅助文字制作.(外层防焊开窗一般 均比外层大单边 2mil 以上),在将防焊层加 16milCopy 到别一层时应注意 将防焊层的负片关闭,点击过滤器按钮 ,如下图所示:

旋转 镜像

点击选择第三项,然后在 栏中输入你想放大的 X 轴倍数, 栏中输入 Y 轴要放大的倍数.将需放大的文字框用 这个框选命令选中 ,

XVII

学习使人进步!态度决定学习效果!

如下图所示:

再用鼠标左键点击“Transformation Popup”对话框中的

白色区域的任一部分,然 后再移动鼠标至所需放大文字框的中心位置,点击 OK 即可放大,放大后效 果如下图所示:

Genesis 全套教程之文字制作

一、普通客户文字制作方法 1 、进入一个料号,打开文字层(Csilk or Ssilk),首先是要将成型线

上和成型线外的字符等实体去除,将鼠标指向文字层上,单击鼠标右键 , 选择 Clip area 项,如下图所示:

打开下图所示窗口,参数设置如下图所示:

单击 OK 即可删除 Profile 线以外及在 Profile 线上的文字字符.(注意板

套负片之后

打开文字层和工作稿防焊比对:

XXXII

学习使人进步!态度决定学习效果!

如上图,红色文字到绿色防焊间距为 8mil. 12、文字制作完成后,需跑检查,检查文字到防焊的间距够不够 8mil,执

行 Analysis Fabrication Silk screen cheahs 命令,如下 图所示:

XXIV

学习使人进步!态度决定学习效果!

超详细Genesis作业流程

CAM作业流程备注11分层:一般客户命名为一般PCB 厂家命名为:(1): SILKTOP LAYER 丝印顶层CM1或CMTMASKTOP LAYER 防焊顶层SM1 或SMTTOP LAYER 线路顶层L1 或LT GND LAYER 接地层L2 或1X2 POWER (或VCC) LAYER 信号层L3 或IN3BOTTOM LAYER 线路底层L4 或LBMASKBOTTOM LAYER 防焊底层SM4 或SMBSILKBOTTOM LAYER 丝印底层CM4 或CMBPASTETOP 钢网顶层GW1或STN1PASTEBOTTOM 钢网底层GW4 或STN4Dril IDrawing:孔径图一用不同标记标识不同孔径及位置六层SILKTOP LAYER 丝印顶层CM1 或CMTMASKTOP LAYER 防焊顶层SM1 或SMTTOP LAYER 线路顶层L1 或LTGND LAYER 接地层L2 或1X2 INNT1 L3 或I\3INNT2 L4 或I\4POWER (或VCC) LAYER 信号层L5 或IN5BOTTOM LAYER 线路底层L6 或LBMASKBOTTOM LAYER 防焊底层SM6 或SMBSILKBOTTOM LAYER 丝印底层CM6 或CMBPASTETOP 钢网顶层GW1或STN1PASTEBOTTOM 钢网底层GW6或STN6(2): COMPONENT SIDE SILKSCREEN 丝印顶层COMPONENT SIDE SOLDER MASK 防焊顶层COMPONENT SIDE OF LAYER 线路顶层GROUND PLANE OF LAYER2 接地层INNER TRACK OF LAYER3 信号层INNER TRACK OF LAYER4 信号层VCC PLANE OF LAYER5 接地层SLIDER SIDE LAYER 线路底层SOLDER SIDE SOLDER MASK 防焊底层SOLDER SIDE SILKSCREEN 丝印底层COMPONENT SIDE STENCIL 钢网SOLDER SIDE STEXCIL(3). GTL 线路顶层LI 或LTGTS 防焊顶层SMI 或SMTGTO 丝印顶层CM1 或CMTG1 接地层L2 或1X2G2 信号层L3 或1X3 GBL 线路底层L4 或LB GBS 防焊底层SM4 或SMB GBO 丝印底层CM4 或CMB GKO 边框线既成形线ROUTGDI 孔符图(包含孔数,大小,是否为金属化孔)GG1 孔位图DRILL 钻带GTP 或GPT 钢网顶层GW1 或STN1GBP 或GPB 钢网底层GW4 或STN4G为GERBER缩写,T为TOP缩耳,B为BOTTOM缩写,等.命名是从我们看到的顺序和线路板的叠加顺序排列一般线路板厂命名为兰胶BG* 碳膜CB* (CARBON)GTO 丝印顶层CM1 或CMT 文字CM* 防焊SM* 线路L* 纲网GW* (或STN*)兰胶BG* 碳膜CB* (CARBON)关于制前CAM组输出文件的命名规则及特殊做法光绘压缩文件中必须包括以下文件,其对应关系如下:层名规则:UV? 碳阻盖UV油菲林(比防焊层开窗加大6mil,中间不能有桥,只印碳阻位)B L? 线路层整体加大8mil与其相邻内层合并,并取消内层的阻流点与折断边铜条(印黑油修补菲林,BLACK缩写)BLU? (印兰胶菲林,BLUE缩写)CB? (印碳膜菲林,CARBOY缩写)22Q 21X56m订10Q 23X40milGW? (钢网菲林,拼音缩写)L ? (线路,英文LAYER缩写)SM? (防焊,英文SOLDERMASK 缩写)CM? (文字,英文Component mark缩写)MAP (板点图,外型图+钻孔文件)Ag? (印银油菲林,Ag化学符号缩写,菲林为负片比防焊菲林单边大10MIL)注:“?”表示层数二、钻孔文件的前后缀名规则,料号名+后缀后缀定义:・OUT 主程序(外层钻孔).0T? ?变更版本号(外层钻孔).INN 栽PIN程序.REP 主程序的孔径.孔数孔序报告.MDK 钏钉孔(拼音缩写).JXB 夹心板程序(拼音缩写),钻钏钉孔与电测PIN孔4)157mil.PIN 电测定位孔.BGA BGA塞孔.VIA VIA塞孔备注2钻孔:孔径分三种,VIA (导通孔)乂叫过孔,PTH (元件孔)NPTH (零件孔或叫螺丝孔).导通孔为把儿层线路连接作用,并不插元件,一般防焊不开窗,喷锡板要加挡点,目的是防止锡珠进塞孔,影响客户插件。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

钻孔制作方法:一.读入Gerber file:Windows→input→Identify Open wheeltemplate→All→????→???Illegal???→sym修改完毕→File→Close→修改ncdrill格式,将光标移到此处,按右键→Parameters…→修改格式后→OK→Translate→Path:genesis/input/691040a21Job:691040a21 step:oriExclude:*.zip;*.gap….注:1.识别:绿色表示识别成功;蓝色表示无法识别;粉红色表示部分有问题。

2.转换:红色表示失败。

二.建立PCB文件:点击job matrix…→ori→edit→copy→出现ori+1,在ori+1处按左键,修改step:ori+1为pcb→file→save→close→file→close一.更改层名:job matrix….→在Layer处修改层名二.排序:将光标移到需移动的层→左键→Ctrl+x→光标移至目的层。

反复上述动作,直到与实物板迭构相同为止。

三.定义属性:1.除map层外,其余均定义为Board。

2.将skc、sks定义为silk-screen;smc、s ms定义为solder-mask;vc2、gn3定义为power-ground,若内层为负片,则需定义为negative,否则定义为positive。

3.File→save→close。

四.归零点:1.打开map层→选中PCB外围框→Edit→Copy→other layer→Layer name:outline→ok,将框线改为10mil。

2.用单项选择钮点取outline层左下角二条线→Rout→connections…→选择直角钮→Corner→best→close。

3.将所有层设为影响层→将网格设为交点→点击outline层左下角交点处→Ctrl+x→在X,Y处键入0 0后回车→关闭影响层。

五.定义Profile:选中outline层→Edit→create→profile。

六.钻孔处理:1.打开map层,将drill chart部分放大,按CTRL+P打印。

2.打开dr1层,光标移至此处按右键→Drill tool manager…→与drill chart图纸仔细核对顺序及孔径大小是否一致→定义np孔→Apply→ok→close。

3.在dr1层处按右键→Hole sizes→键入孔径→OK→OK。

以上3步可通过下列方式实现:将ncdrill.tap另存新檔至ncdrill-1.tap中,但只保留孔径大小部分,其余全部删除,则可自动input孔径大小。

4.槽孔处理:打开map与dr1层,并将dr1层设为工作层→Edit→Reshap→change symbol→symbol→选中槽孔符号→输入width及值→OK→Apply→Close。

5.Include symbol:oval*→select→Edit→reshape→break。

6.→Redundancy cleanup→NFP Removal…→Duplicate。

7.检查钻孔与其它层状态:Analysis→Drill checks→运行。

8.检查钻孔孔距:Analysis→Board-Drill-Check→运行。

9.孔位校正:DFM→Repair→pad snapping→Ref layer:top→运行。

10.将CPU及BGA处刀与其它部位刀分开处理:a. 选中欲分刀之孔→Edit→Resize→Glolav…→Size:-0.1my。

b. Size:+0.1my。

11.设定np User filer...→no plated hole→将线钮按下→Select→Edit→copy→layer name:np→ok。

12.设定11a.将dr1层和outline层分别Copy到11层。

b.将np层Copy至11层,Invert项选Y es,Resize处键入-20mil→OK。

七〃削到VIA PAD 选出方法:1. 将外层按工作片方式加大(线加大1mil,PA D加大0.5mil)2. 打开原稿dr1层,将成品径<=18mil的孔选出并定义为via层3. top(只选PAD)、via(ref)→touch→move → 001层4. top(只选PAD)、s mc(ref)→touch→ Copy并加大9.1mil→002 层5. 001 、002(ref)→touch→move →0036. top、001(ref)→touch→Ctrl+B7. 001(+7.1mil)、top(ref)→touch →(-7.1mil)Move → 0038. bot(只选PAD)、via(ref)→touch→move → 004层9. bot(只选PAD)、s ms(ref)→touch→ Copy并加大9.1mil→005 层10. 004 、005(ref)→touch →move → 00311. bot、004(ref)→touch→Ctrl+B12. 004(+7.1mil)、bot(ref)→touch →(-7.1mil)Move → 00313. dr1、003(ref)→Touch →减小0.1my八.钻孔输出:1. 增加End:打开PANEL→Step→panelization→Drill/Rout verification→Edit…→New→Step: End ;width(最大钻孔径):;Height(End长度):→OK→Table→new step…→End→OK→点击End→将Angle设为90→放置合理位置→击End,此时step处出现End→Type选择drill→Mode选择End→Layer name输入dr1→Method选择Automatic→Distance: 40 ml Spacing ; Min size: 0 ml ; Max size(最大钻孔径): ml ;Min hits:0→OK→OK。

2. 自动钻孔程序管理:○1退出PANEL→Actions→Auto Drill Manager…→选择Job名、Step选择panel、Layer选择dr1、NC-set输入001→点击Machine→选择yufo1_excellon(英制)或yufo2_excellon(公制)→OK→OK→点击Register→进入PANEL,按special coordinates→选择profile coner left,将其中数据填入X Origin和Y Origin中→OK→运行○2按住Drill 1.1不放→选择create layer→在layer处输入dr1chk,可在panel中生成dr1chk层。

○3按住NC-File不放→选择open file,可显示End所加位置。

○4选择Export file→在Directory处输入导出路径全名(如:/genesis/output)→在File name处输入文件名(如:625B83A0.dr1)→OK3. 修改输出文件:打开Text Editor popup,在/genesis/output下找到钻孔(如:625B83A0.dr1)并打开该文件→将T1改为3.175;T2改为3.000→删除T1和T2的检测孔→将切片孔刀径改为1.000并删除切片孔检测孔→将程序中最后一把刀(即料号孔)刀径修改为范围有0.4~0.6mm内的刀径→在料号孔刀径下方加入:M98;XXX *C→删除检测孔中大于或等于6.0mm的孔。

注意事项:加End时,要避开靶孔、喷锡挂钩孔所加位置,不许太靠近板边和成型边。

内层制作方法:Surface迭加时,可执行:将Surface、“+”及“-”钮按下,其余钮全部按起→Select→将线、PAD及“-”钮按下,其余钮全部按起→ select。

2.Edit→Reshape→Con tourize…→ok。

(檢查是否與原來一致)3.切除成型区外对象:将光标移至该层,按右键→Clip area…→clip data:affecter layer、method:profile、clip area:outside、cut as contour:no、margin:20mil→ok4.去除比钻孔径小的Thernal pad。

內層、dr1(ref)→coverd→Ctrl+B。

5.校正内层PAD(可同时打开内层):DFM→Repair→pad snapping→layer:affecter、ref layer:drill→运行。

6.PA D缩小1mil(Thermal pad除外):Exclude symbols:ths*→select→edit→rezise→global…→size:-1mil→ok。

1.切除成型区外对象:将光标移至该层,按右键→Clip area…→clip data:affecter layer、method:profile、clip area:outside、cut as contour:no、margin:20mil→ok2.去除比钻孔径小的Thernal pad。

內層、dr1(ref)→coverd→Ctrl+B。

3.校正内层PAD(可同时打开内层):DFM→Repair→pad snapping→layer:affecter、ref layer:drill→运行。

4.PA D缩小1mil(Thermal pad除外):Exclude symbols:ths*→select→edit→rezise→global…→size:-1mil→ok。

(同时打开内层及钻孔层):Analysis→Drill check→Test list只打开Power/Ground shorts项→勾选PTH及Via项→运行→看报告。

四.优化隔离PAD:DFM→Optimization→Power/Ground Opt…→Via/pth clearance Min:9.1 opt:9.1Via/pth A R Min:3.1 opt:3.1Via/pth Thermal Airgap:6Via/pth NFP spacing:10Npth clearance Min:9.1 opt:9.1Thermal Min Ties:0.25→运行→看报告。

五.对未优化部分,可手工放大隔离PAD。

若为Thermal pad未放大,则执行:Edit→Resize→Resize Thermal And Donuts..→在Size处输入需单边放大值→OK。