allegro各层

Allegro操作说明(中文) Word 文档

26、非电气引脚零件的制作1、建圆形钻孔:(1)、parameter:没有电器属性(non-plated)(2)、layer:只需要设置顶层和底层的regular pad,中间层以及阻焊层和加焊层都是null。

注意:regular pad要比drill hole大一点27、Allegro建立电路板板框步骤:1、设置绘图区参数,包括单位,大小。

2、定义outline区域3、定义route keepin区域(可使用Z-copy操作)4、定义package keepin区域5、添加定位孔28、Allegro定义层叠结构对于最简单的四层板,只需要添加电源层和底层,步骤如下:1、Setup –> cross-section2、添加层,电源层和地层都要设置为plane,同时还要在电气层之间加入电介质,一般为FR-43、指定电源层和地层都为负片(negtive)4、设置完成可以再Visibility看到多出了两层:GND和POWER5、铺铜(可以放到布局后再做)6、z-copy –> find面板选shape(因为铺铜是shape)–> option面板的copy to class/subclass选择ETCH/GND(注意选择create dynamic shape)完成GND层覆铜7、相同的方法完成POWER层覆铜Allegro生成网表1、重新生成索引编号:tools –> annotate2、DRC检查:tools –> Design Rules Check,查看session log。

3、生成网表:tools –> create netlist,产生的网表会保存到allegro文件夹,可以看一下session log内容。

29、Allegro导入网表1、file –> import –> logic –> design entry CIS(这里有一些选项可以设置导入网表对当前设计的影响)2、选择网表路径,在allegro文件夹。

焊盘详解

技术员 发表于 2013-4-30 20:33:18 7481 查看 16 回复只看该作者倒序浏览 分享Allegro 中焊盘结构在Allegro 中焊盘的结构如下图:Soldermask_TOPSoldermask _BOTTOM是指阻焊层我们常说的绿油层(不过阻焊层的颜色,不只是绿色的,还有红色、蓝色、黑色和白色的等等),是电路板的非布线层,用于制成丝网漏印板,将不需要焊接的地方涂上阻焊剂。

由于焊接电路板时焊锡在高温下的流动性,所以必须在不需要焊接的地方涂一层阻焊物质,防止焊锡流动、溢出引起短路。

在阻焊层上预留的焊盘大小,要比实际焊盘大一些,其差值一般为10~20mil ,在Pad_Design 工具中可以进行设定。

Pastemask_TOPPastemask _BOTTOM锡膏防护层(Paste Mask ):为非布线层,该层用来制作钢膜(片),而钢膜上的孔就对应着电路板上的SMD 器件的焊点。

在表面贴装(SMD )器件焊接时,先将钢膜盖在电路板上(与实际焊盘对应),然后将锡膏涂上,用刮片将多余的锡膏刮去,移除钢膜,这样SMD 器件的焊盘就加上了锡膏,之后将SMD 器件贴附到锡膏上去(手工或贴片机),最后通过回流焊机完成SMD 器件的焊接。

通常钢膜上孔径的大小会比电路板上实际的焊点小一些,这个差值在Pad_Design 工具中可以进行设定。

Thermal relief(花焊盘/热风焊盘):也叫热风焊盘,防散热热分焊盘。

热风焊盘有以下两个作用:(1)防止散热。

由于电路板上电源和地是由大片的铜箔提供的,所以为了防止因为散热太快而造成虚焊,故电源和接地过孔采用热风焊盘形式;(2)防止大片铜箔由于热胀冷缩作用而造成对过孔及孔壁的挤压,导致孔壁变形。

Anti pad,隔离PAD:起一个绝缘的作用,使焊盘和该层铜之间形成一个电气隔离,同时在电路板中证明一下焊盘所占的电气空间。

正片和负片的概念:正片和负片只是指一个层的两种不同的显示效果。

ALLEGRO基本使用指南

ALLEGRO基本使用指南一.常用术语和概念PCB(Printed Circuit Board):印刷电路板,指所有具有互关系的元器件放在一块指定大小、形状、由特殊材料叠加而成、实现一定电路功能的线路板。

Symbol:器件封装Pad:焊盘Etch: 线,用于接各pin点以实现物理电路功能。

Line width :线宽,连接线的宽度。

Spacing: 线距,连接线与连接线、pin等之间的距离。

Outline: 板边Rats:飞线,指释各pin点间连接关系的虚线。

DRC:PCB板上产生短路及各种不符合约束规则时产生的报错标志。

Shape:铜铂Via:过孔Text :丝印,也称文字.Top 层:PCB板表面层.Bot 层:PCB板底面层.内层:压合在PCB板内的,用于布线和电源使用。

spacingtopFR4In1FR4 内层FR4二.ALLEGRO 菜单的使用File 菜单:File\new命令:建一个文档,如图2—1-1…进行选择;在在Drawing Name 中输入新文档的保存路径及名称,可点击B B r r o o w w s s e e…Drawing_Type:的下拉栏中选择要新建的文档的格式,主要有以下几种:Board/board(wizard):新建一个。

brd文档;Module:Package symbol:/Package symbol(wizard):Mechanical symbol:Format symbol:Shape symbol:Flash symbol:本文只介召.brd 文档的建立,其它各模块暂不说明。

File\open命令:打开一个已经存在的文档。

File\save命令:保存一个文档。

File\save as…命令:将文档以其它名字保存。

注意:ALLEGRO 进行此命令后,当前正在编辑的文档也将随这更名。

Import/export命令:此部份将在后面中会介召。

Viewlog…/File viewer…命令:查看ALLEGRO一些命令运行后产生的错误信息,信息以。

Allegro菜单介绍

基础培训教程

Allegro菜单介绍

2012-10-17

一博科技 内部资料

1

基础培训教程

2012-10-17 一博科技 内部资料 11

基础培训教程

Setup(2)

Electrical Constraint Spreadsheet:电气规则设置 DFA Constraint Spreadsheet:DFA规则设置 Property Definitions:追加用户自定的属性 Define Lists:Symbol、Net的定义 Areas:设置区域;器件禁布、器件限高、走线禁布等 Outlines:绘制PCB板框等; User Preferences:用户自定义环境变量界面;高亮模式、 DRC显示模式、封装库路径等

2012-10-17

一博科技 内部资料

8

基础培训教程

Add

Line:添加指示线; Arc w/Radius:两点画弧; 3pt Arc:三点画弧; Circle:画圆; Rectangle:画一矩形框,有时与 Frectangle同效; Frectangle:画一矩形框,有时与 Rectangle同效; Text:添加文字;

一博科技 内部资料 10

2012-10-17

基础培训教程

Setup (1)

Drawing Size:设置工作区大小,原点坐 标,单位等; Drawing Options:显示Layout状态信息; 设置Pad显示模式及DRC大小等 Text Sizes:设置丝印的字体大小; Grides:设置设计格点及偏移量; Subclasses:追加特殊显示层(用户自定 的Layer); Cross-section:层叠设置,(布线层、电 源层); Materials:PCB板材设置 Vias:特殊过孔设置(盲孔、埋孔); Constraints…:规则设置;线宽、线距等

Allegro层次原理图(模块reuse)设计流程

Allegro层次原理图(模块reuse)设计流程Module reuse1.在orcad中画好模块的原理图,设定好封装,做好drc,做好元件编号。

2.在annotate-->allegro reuse中,选中generate reuse module, renumber design forusing modules不选,选中unconditional,其它不选。

3.⽣成netlist.4.将netlist导⼊到allegro,布线,布局,若⽆rename等需要与orcad交互的动作,,选tools-->create modules⽣成mdd⽂件.mdd⽂件的⽂件名⼀定要定义为:DSN NAME_ROOT SCHEMATIC NAME.mdd。

DSN NAME为你定义的orcad中的dsn⽂件名,ROOT SCHEMATIC NAME是这个⽂件中的页名字。

这⾥若定义不对,在reuse时找不到mdd⽂件。

之后跳到第6步。

5.在orcad中back annotate,之后回到第2步。

6.模块制作完成。

使⽤⽣成的模块1.在新的orcad设计中,选place-->herarhical block,reference中填⼊BLK?(注意,这⾥不能⽤BLK是为了与原理图中的U?R?C?区别,保证BLK这个名字专⽤于moduel,不然在做完allegro后,rename时,导回到orcad中出问题。

)在implementation type中选schematic view,在implementtation name中填⼊先前模块的页名称ROOT SCHEMATIC NAME,在path and file name中选择相应的dsn⽂件,之后在你的原理图中出现⼀个block.2.继续其它设计(包括放⼊其它block),当你双击任⼀个BLOCK时会发现都将进⼊到模块原理图中,注意每个模块位号现在还是⼀样的。

ALLEGRO使用教程

ALLEGRO使用教程一. PCB窗口介面介绍运行PCB EDIT 出现对话框注:不同的选项能实现的功能有所不同,一般P C B画板时选择A l l e g r o E x p e r t1.P C B介面2.工具栏其中工具栏的图标在相应的菜单栏中都可以找到,其对应关系如下:红色的文字对应菜单栏的选项。

如果工具栏图标太多或者太少,可以通过菜单View=>Customization=>Toolbar 自己增加或者减少一些不常用的图标3.控制栏说明控制栏主要有三大选择项:Option、Find 和Visibility通过控制面板的Option 标签可选择被激活的类或子类,在Allegro 数据库中,所有元素都有一个类属性(CLASS)或子类属性(SUBCLASS)。

通过控制面板的Find 标签,可以选择各种元素,如Nets、Lines、Vias等,当执行各种命令时,都需要在Find 标签中选择好相应的元素。

以移动命令为例,说明一下“Find”选项含义。

选择菜单Edit=>Move,再看“Find”选项如图所示,其中有多个复选框可供选择,想移动什么东西,一定要将其对应的复选框钩上“√”,比如,如果想要移动元件,首先点击一下“All Off”按钮,关闭所有的复选框,然后再将复选框“Symbols”钩上“√”,就可以对元件进行移动了。

如果要查看某个元件的信息,可以通过Display->Element,或单击图标,然后在Find 标签中选择好相应的元素。

通过控制面板的Visibility 标签,可以选择Etch 、Pin、Via、DRC 的各个子类的可视性。

“Visibility”下的“Views”可以用于快速切换窗口显示,其中的列表项内容是在进行过光绘的输出设置之后,就可以显示出来。

“Visibility”下的“layer”的意思就是对各层进行打开或者关闭显示,将小方框里打上“√”表示打开这层的显示,取消“√”表示不显示该层。

Cadenceallegro菜单使用说明

Cadenceallegro菜单使用说明Cadence Allegro菜单使用说明1. 简介本文档旨在向使用Cadence Allegro软件的用户提供菜单使用说明。

Cadence Allegro是一款常用的电子设计自动化(EDA)软件,有助于进行电路设计和 PCB 布局。

2. 界面概述Cadence Allegro的界面主要由工具栏、菜单栏和主编辑区组成。

菜单栏包含了软件的各种功能和工具,方便用户进行设计和布局操作。

3. 菜单使用Cadence Allegro的菜单栏提供了丰富的功能和工具,方便用户进行电路设计和布局。

以下是一些常用菜单和其功能的介绍:3.1 文件菜单文件菜单可以用于新建、打开和保存设计文件,以及进行打印和导出等操作。

- 新建设计文件: `文件` -> `新建`- 打开设计文件: `文件` -> `打开`- 保存设计文件: `文件` -> `保存`- 打印设计文件: `文件` -> `打印`- 导出设计文件: `文件` -> `导出`3.2 编辑菜单编辑菜单提供了一系列用于编辑和处理设计文件的功能和工具。

- 撤销上一步操作: `编辑` -> `撤销`- 复制选定的元件或图形: `编辑` -> `复制`- 粘贴剪贴板的内容: `编辑` -> `粘贴`- 删除选定的元件或图形: `编辑` -> `删除`- 查找和替换元件或图形: `编辑` -> `查找和替换`3.3 视图菜单视图菜单用于控制设计的可见性和显示方式。

- 放大或缩小设计: `视图` -> `放大` / `视图` -> `缩小`- 移动设计视图: `视图` -> `移动`- 显示或隐藏参考层: `视图` -> `参考层`- 显示或隐藏网络标签: `视图` -> `网络标签`3.4 工具菜单工具菜单提供了一些实用的辅助工具和功能。

- 进行电路仿真: `工具` -> `电路仿真`- 进行电路布局和线路连接: `工具` -> `布局和线路连接`- 进行信号完整性分析: `工具` -> `信号完整性分析`- 进行功率完整性分析: `工具` -> `功率完整性分析`4. 其他说明以上仅是一些常用菜单和功能的介绍,Cadence Allegro软件还提供了许多其他有用的功能和工具,用户可以根据自己的需求进行探索和使用。

Allegro-PCB层叠设置

Allegro-PCB层叠设置Cadence Allegro 16.5层叠设置——孙海峰对于刚学习Cadence Allegro ,或者刚从其他EDA软件(如Protel)转为Allegro使用上的朋友,其颜色设置、层叠意义往往使人望而却步。

如此多的额叠层,更细致的、更可靠的层叠设置,如何更好的理解和把握,哪些层叠对于我们设计是常用或必需的呢,我将在以下做详细的介绍。

打开Cadence Allegro 16.5,进入Cadence PCB设计环境,点击工具栏的按钮,或执行菜单Display/Color/Visibility命令,打开层叠颜色设置的界面,以此为基础,我来介绍详细的层叠意义。

在弹出的颜色设置对话框中可以看到,Cadence Allegro 16.5设计环境将颜色设置分为不同类型层叠,根据个人习惯分别进行设置,要设置好,先必须了解各个层叠的具体意义。

1、PCB基本叠层Stack-up设置a) Subclass子层叠,表示PCB中具体层叠,包括:Top层、Bottom层、内层(POW/GND)、阻焊层(Soldermask_Top/Soldermask_Bottom)、加焊层(Pastemak_Top/Pastemask_Bottom),其他Subclass子层叠目前设计中不需要用到,包括底片应用层(Filmmasktop/Filmmaskbottom)等,这些不常用的层叠不用花时间去了解的,与目前无关。

b) 子层叠相应的对象Objects,与上述的Subclass一起使用,用以显示不同子层叠上相应对象,包括子层叠上对应的Pin引脚、Via过孔、Etch走线、DRC规则错误、Plan覆铜平面、Anti Etch隔离走线(用于铜皮分割),这样既可配合子层叠,设置对应层不同对象的颜色。

此外,Boundary轮廓、Cativy埋入式器件腔体等对象暂时不用去考虑,与现在大部分PCB设计暂时没有关系。

AllegroCB层叠设置

Cade nee Allegro 层叠设置-- 孙海峰对于刚学习Cade nee Allegro ,或者刚从其他 EDA 软件(如Protel )转为 Allegro 使用上的朋友,其颜色设置、层叠意义往往使人望而却步。

如此多的额 叠层,更细致的、更可靠的层叠设置,如何更好的理解和把握,哪些层叠对于我 们设计是常用或必需的呢,我将在以下做详细的介绍。

亠 皿打开Cade nee Allegro ,进入Cade nee PCB 设计环境,点击工具栏的 按钮,或执行菜单Display/Color/Visibility 命令,打开层叠颜色设置的界面,以 此为基础,我来介绍详细的层叠意义。

Cfilftr IH曲 I 啊[三 f 口宅^氓3iffi Lai-ws*OfW=5 I —DEdbb Cu^gmGlnhai Vkjfcbifc ~dQjJLQ I O置分为不同类型层叠,根据个人习惯分别进行设置,要设置好,先必须了解各个 层叠的具体意义。

lj B T»vnr ■ t •_Cl piEjJar , -Ss St Iftclr]5p :■■ L J '■ F 击北MTO P :UXL If 7-n-r p^.-bj点:・N iA-:: Pin vsi. I lun SreT&Jr」L-」Ftf]r4£4 ・・ i7 T>j«riBnl s Hiiiuf act^s IKf WViiig f Mn-iLt AfiL«lTTL3CkLd血葩0,:. 臨带GHSei 弓 LTTFBH .J T 1" 写olif T 3B3 -F^E-jTtDSJ JHI —inI/5fepdrlF4=rinriJ*匚 ■ L ■nnwn □□rm □□□□□ 匚■■■ rar nnr □□□■ n n □ i ■■■■■n.-i-r nnnn - c ■口□口 r uuini r i 在弹出的颜色设置对话框中可以看到, Cade nee Allegro 设计环境将颜色设fLlp*革丄亠二■亠L. tot - q 杠二二LLrl —Lu厂匚□口Plii厂StlrCteJnJ□□1 JRs nzit-_.K1 E J I<i >lZEK / ~3 口Tl ri I|Cu^kn >t»4w.高速PCB 设计经常会用到区域的概念,包括:Constraint Region 高速区域 约束的特殊规则区域、Route Keep Out 禁止布线区域、Via Keep Out 禁止放置 过孔区域、Package Keep Out 禁止布局区域、Package Keep In 允许布局区域、1、PCB 基本叠层Stack-up 设置a) Subclass 子层叠,表示PCB 中具体层叠,包括:Top 层、Bottom 层、 内层(POW/GND )、阻焊层(Soldermask_Top/Soldermask_Bottom )、加焊 层(Pastemak_Top/Pastemask_Bottom ),其他 Subclass 子层叠目前设计中 不需要用到,包括底片应用层(Filmmasktop/Filmmaskbottom )等,这些不常 用的层叠不用花时间去了解的,与目前无关□ My Favori tes rh Di 理1岂 $ £3 SticlrUp-* Cl ConductorFn rimPl Fcn-ConduBoard. G&cwnetry Packige Geoin . _ .Embedded ・-Component EM anuf acturingDrawing F Qrmat區□□□□□□□口 :一出 lirw —-'.: “--==:Tit Si pull ■S -nd ftot-aaSul d E ras sk_T op Sol^trsaxk_&Dtto= Pafit«KiGk_T{>t> Psst ~a;ic_5c-tt:?. F il^asktcp乙庄zcFcCka^_Dctt jnD«nii tr_V*rT_Hithb)子层叠相应的对象 Objects ,与上述的Subclass 一起使用,用以显示不 同子层叠上相应对象,包括子层叠上对应的Pin 引脚、Via 过孔、Etch 走线、DRC 规则错误、Plan 覆铜平面、Anti Etch 隔离走线(用于铜皮分割),这样既 可配合子层叠,设置对应层不同对象的颜色。

培训教材-allegro基本操作

解释一下常用层信息: ANTIETCH_GND 地层走线及铜皮信息

ANTIETCH_PWR 电源层走线及铜皮信息

DRC

PCB板错误信息

DRILL

PCB钻孔信息

ETCH_BOT

bottom层走线,零件,网络信息

ETCH_TOP

top层走线,零件,网络信息

SILK_BOT

bottom层零件丝印

SILK_TOP

Allegro 基本操作培训

一、allegro 界面介 绍

图标解释:

图1

第1组:移动,复制,删除,撤销,锁定,解锁

第2组:关闭所有鼠线,打开所有鼠线,视图的放大缩小

第3组:格点,设定层面颜色,阴影显示模式(点击这个按键会使全部对象颜色变暗,除了被

高亮的对象),层叠设置,走线约束规则管理器

第4组:显示属性,测量,高亮,取消高亮

要查看结构图的时候,请注意做以下的选择,点击菜单 ,按照图11进行操作

图11

2.导入网表

①根据所导入的结构图,给PCB增加板框。板框绘制步骤如下:点击增加线段图标 ;在控制面板Opitions,按照图12进行操作:上面的红框内,显示的是要操作的层 面,在Board Geometry层的Outline子层,Line width(线宽)是6mil

图7

图8

Visibility:快速、直接地代开或者关掉与走线相关层面的颜色。需要换层,查 看不同层面的走线的时候,要先选择在这个选项内

例如:想看Bottom层走线信息,先点到Visibility界面,在Views选择File: ETCH_BOT(如图7),就可以看到Bottom层的信息了。在图8,红圈内,同样可以选 择所需了解的信息。(需要看哪个层面就在方框内打勾,不需要看的就不要勾上。 )

allegro差分对布线规则中的每个参数的意思

allegro差分对布线规则中的每个参数的意思Allegro是一款广泛应用于电子设计自动化(EDA)领域的PCB设计软件,其强大的差分对布线功能在高速信号设计中尤为突出。

在使用Allegro进行差分对布线时,需要遵循一定的规则,并设置多个参数以确保信号完整性。

本文将对这些参数进行详细解析,以帮助读者更好地理解其意义。

一、差分对布线规则参数概述在Allegro中,差分对布线规则主要包括以下参数:1.差分对名称(Diff Pair Name)2.差分对层(Diff Pair Layer)3.差分对间距(Diff Pair Spacing)4.差分对宽度(Diff Pair Width)5.差分对长度匹配(Diff Pair Length Match)6.差分对阻抗(Diff Pair Impedance)二、各参数意义解析1.差分对名称(Diff Pair Name)差分对名称用于标识差分对,方便在布线过程中对其进行识别和管理。

差分对名称应具有一定的意义,便于理解。

2.差分对层(Diff Pair Layer)差分对层用于指定差分对所在的布线层。

通常情况下,差分对应在同一层进行布线,以减小层间耦合对信号完整性的影响。

3.差分对间距(Diff Pair Spacing)差分对间距是指差分对两个信号线之间的距离。

合适的间距有助于减小信号线之间的相互干扰,提高信号完整性。

通常,差分对间距应大于等于两倍线宽。

4.差分对宽度(Diff Pair Width)差分对宽度是指差分对两个信号线的宽度。

在高速信号设计中,差分对宽度对信号完整性有很大影响。

通常,差分对宽度应保持一致,以减小信号线之间的阻抗差异。

5.差分对长度匹配(Diff Pair Length Match)差分对长度匹配是指差分对两个信号线的长度差异。

在高速信号设计中,长度匹配对信号完整性至关重要。

为了减小信号延迟和相位差,应尽量使差分对两个信号线的长度相等。

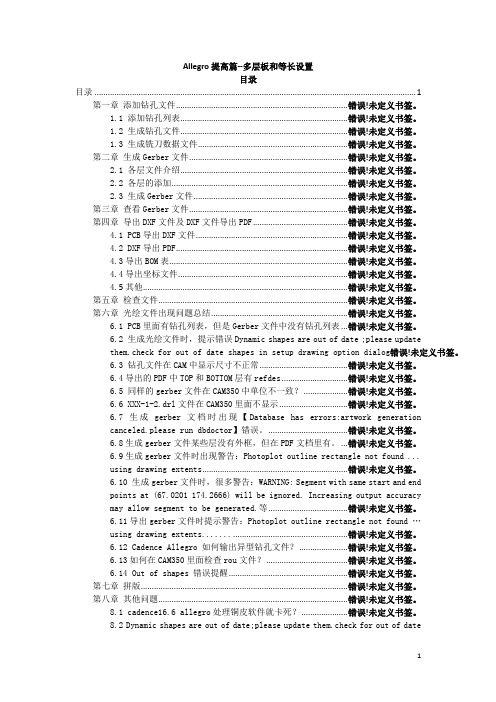

Allegro提高篇--多层板和等长设置

Allegro提高篇--多层板和等长设置目录目录 (1)第一章添加钻孔文件.............................................................................. 错误!未定义书签。

1.1 添加钻孔列表............................................................................ 错误!未定义书签。

1.2 生成钻孔文件............................................................................ 错误!未定义书签。

1.3 生成铣刀数据文件.................................................................... 错误!未定义书签。

第二章生成Gerber文件........................................................................ 错误!未定义书签。

2.1 各层文件介绍............................................................................ 错误!未定义书签。

2.2 各层的添加................................................................................ 错误!未定义书签。

2.3 生成Gerber文件...................................................................... 错误!未定义书签。

第三章查看Gerber文件........................................................................ 错误!未定义书签。

焊盘各层的解释及设定规则

在Allegro 中,制作一个零件(Symbol)之前,必须先建立零件的管脚(Pin)。

元件封装大致分两种:标贴和直插。

不同的封装需要不同的焊盘(Padstack)。

Allegro中的Padstack主要包括1、元件的物理焊盘1)规则焊盘(Regular Pad)。

有圆形、方形、椭圆形、矩形、八边形、任意形状(Shape)2)热风焊盘(Thermal Relief)。

有圆形、方形、椭圆形、矩形、八边形、任意形状(Shape)3)抗电边距(Anti Pad)。

用于防止管脚和其他网络相连。

有圆形、方形、椭圆形、矩形、八边形、任意形状(Shape)。

2、阻焊层(soldermask):阻焊盘就是solder mask,是指板子上要上绿油的部分。

实际上这阻焊层使用的是负片输出,所以在阻焊层的形状映射到板子上以后,并不是上了绿油阻焊,反而是露出了铜皮。

通常为了增大铜皮的厚度,采用阻焊层上划线去绿油,然后加锡达到增加铜线厚度的效果。

3、助焊层(Pastemask):机器贴片的时候用的。

对应着所以贴片元件的焊盘、在SMT加工是,通常采用一块钢板,将PCB上对应着元器件焊盘的地方打孔,然后钢板上上锡膏,PCB在钢板下的时候,锡膏漏下去,也就刚好每个焊盘上都能沾上焊锡,所以通常阻焊层不能大于实际的焊盘的尺寸。

用“<=”最恰当不过。

4、预留层(Filmmask)用于添加用户自定义信息。

表贴元件的封装、焊盘,需要设置的层面以及尺寸Regular Pad:具体尺寸更具实际封装的大小进行设置。

推荐参照《IPC-SM-782A Surface Mount Design and Land Pattern Standard》。

Thermal Relief:通常要比规则焊盘尺寸大20mil,如果Regular Pad尺寸小于40mil,需要适当减小尺寸差异。

Anti Pad:通常要比规则焊盘尺寸大20mil,如果Regular Pad尺寸小于40mil,需要适当减小尺寸差异。

allegro隔层参考技巧

在Cadence Allegro软件中,进行隔层参考的技巧如下:

1. 切换线路层:使用change_layer.il脚本,放在.brd同路径下,然后在allegro中执行skill load("change_layer.il")后可以使用。

通过这个脚本,你可以切换不同的线路层。

2. 添加shape、铜皮:选择适当的shape和铜皮,进行添加操作。

3. 选择适当的网络属性:在添加shape或铜皮时,需要选择适当的网络属性,以便正确地连接各个层之间的信号。

4. 添加过孔:如果需要在不同的层之间进行连接,可以添加过孔。

过孔可以参考射频走线周围或者孤立的GND和其他GND之间互联,这样既有射频线,也有第三层孤立的GND,打GND孔可以让射频线有低阻抗回流,以及让第三层孤立的GND和其他层GND有更好的连接。

以上是allegro隔层参考的基本步骤和技巧,实际操作中可能还需要根据具体情况进行调整和优化。

allegro 统计顶层器件

allegro 统计顶层器件

allegro是一家知名的电子元件制造商,其产品线涵盖了各种顶层器件。

顶层器件是指在电路板设计中位于最上层的器件,通常包括处理器、存储器、接口芯片等。

在allegro的产品线中,顶层器件主要包括微控制器、模拟集成电路、数字信号处理器、以太网控制器、存储器芯片等。

这些器件在电子系统中起着至关重要的作用,能够实现各种功能,例如控制、通信、数据处理等。

从功能角度来看,allegro的顶层器件涵盖了各种应用领域,例如汽车电子、工业控制、消费类电子产品等。

这些器件在不同的应用场景下具有不同的特点和要求,allegro针对不同的市场需求推出了多种顶层器件产品,以满足客户的多样化需求。

从技术角度来看,allegro的顶层器件产品具有先进的制造工艺和技术,能够提供高性能、低功耗、稳定可靠的特性。

同时,allegro还提供了丰富的技术支持和解决方案,帮助客户在设计和应用过程中充分发挥顶层器件的性能优势。

总的来说,allegro的顶层器件产品线丰富多样,涵盖了多种

功能和应用领域,具有先进的技术和稳定可靠的特性,能够满足客户的不同需求,并在各种电子系统中发挥重要作用。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

5、定义封装高度(可以选择)

选择Setup->Areas->Package Boundary Height;

class和subclass 为 PACKAGE GEOMETRY/PLACE_BOUND_TOP;

点击刚才画的封装边界,输入高度;

6、添加测试点不能添加的区域(可以选择),点击SHAPE ADD;添加阻止测试点放置的区域;

class和subclass 为 Manufacturing/No_Probe_TOP;

PCB封装的一些规范:

1、在LOLDERMASK_TOP层定义的大小规则:在尺寸允许的范围下,相对BEGIN LAYER层,可以大10mil(两边相加,

ห้องสมุดไป่ตู้

class和subclass 为 REFDES/SILKSCREEN_TOP;输入U*;放在器件的上侧中央;

class和subclass 为 Device Type/SILKSCREEN_TOP;输入DEV;放在器件的上侧中央;

4、生成封装边界,点击SHAPE ADD;画出封装的边界。可以检测器件没有放重叠;

一边就是5mil);在小尺寸下,大6mil;

2、对于普通的通孔器件,REGULAR PAD 比DRILL 大20mil; 其它特殊通孔视情况而定,比如说打的过孔可以只大10mil;

3、对于普通的通孔器件,THERMAL RELIEF、ANTI PAD比REGULAR PAD大20mil;其它特殊通孔视情况而定;

4、做器件时必须把DATASHEET做上标记,DATASHEET的名称改为所做器件的名称,然后拷贝到集中的目录;

做双排封装的时候

1、 e = e;

2、 e1 = Hmax + 24mil(0.6mm) - 焊盘的长度;

3、 E = Emin - 20mil(0.5mm);

4、 D = Dmax;

添加丝印

class/subclass为PACKAGE GEOMETRY/SILKSCREEN_TOP;

3、添加标号RefDes

class和subclass 为 REFDES/ASSEMBLY_TOP;输入U*;放在器件的中央;

class和subclass 为 Device Type/ASSEMBLY_TOP;输入DEV;放在器件的中央;

Allegro画元件封装时各层的含义

pad目录

psm目录(或者把PSM目录分为:shape目录、flash目录、package目录)

1、添加管脚,可用 x 0 0 命令来定义第一个点的位置;

2、添加装配外形,设置栅格25mil,选择ADD->Line

class和subclass 为 PACKAGE GEOMETRY/ASSEMBLY_TOP;