器件管脚图及功能表

常用电子器件管脚排列图

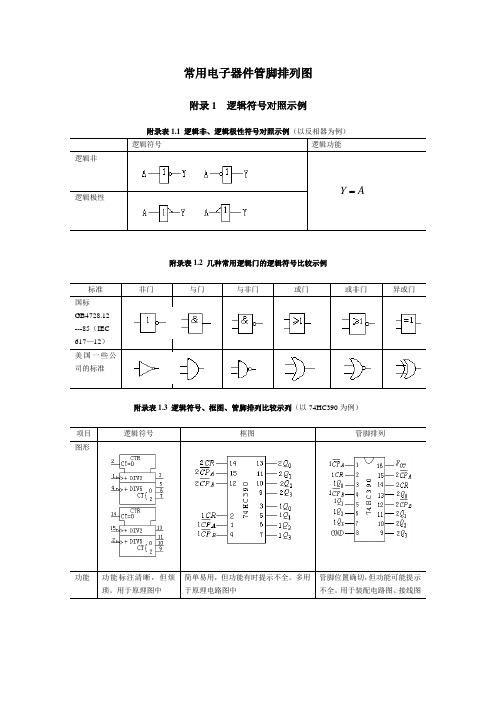

常用电子器件管脚排列图附录1 逻辑符号对照示例附录表1.1 逻辑非、逻辑极性符号对照示例(以反相器为例)附录表1.2 几种常用逻辑门的逻辑符号比较示例附录表1.3 逻辑符号、框图、管脚排列比较示列(以74HC390为例)附录2 集成电路1. 集成电路命名方法集成电路命名方法见附录表2.1附录表2.1 国产半导体集成电路型号命名法(GB3430-82)2.集成电路介绍集成电路IC 是封在单个封装件中的一组互连电路。

装在陶瓷衬底上的分立元件或电路有时还和单个集成电路连在一起,称为混合集成电路。

把全部元件和电路成型在单片晶体硅材料上称单片集成电路。

单片集成电路现在已成为最普及的集成电路形式,它可以封装成各种类型的固态器件,也可以封装成特殊的集成电路。

通用集成电路分为模拟(线性)和数字两大类。

模拟电路根据输入的各种电平,在输出端产生各种相应的电平;而数字电路是开关器件,以规定的电平响应导通和截止。

有时候集成电路标有LM (线性类型) 或DM(数字类型)符号。

集成电路都有二或三个电源接线端:用CC V 、DD V 、SS V 、V +、V -或GND 来表示。

这是一般应用所需要的。

双列直插式是集成电路最通用的封装形式。

其引脚标记有半圆形豁口、标志线、标志圆点 等,一般由半圆形豁口就可以确定各引脚的位置。

双列直插式的引脚排列图如附录图2.1所示。

3.使用TFL 集成电路与CMOS 集成电路的注意事项(1) 使用TYL 集成电路注意事项① TYL 集成电路的电源电压不能高于V 5.5+。

使用时,不能将电源与地颠倒错接,否则将会因为过大电流而造成器件损坏。

附录图 2.1双列直插式集成电路的引脚排列②电路的各输入端不能直接与高于V 5.5+和低于V 5.0-的低内阻电源连接,因为低内阻电源能提供较大的电流,导致器件过热而烧坏。

③除三态和集电极开路的电路外,输出端不允许并联使用。

如果将集电极开路的门电路输出端并联使用而使电路具有线与功能时,应在其输出端加一个预先计算好的上拉负载电阻到CC V 端。

STM32F103引脚功能定义

2.1 器件一览表二:器件功能和配置(STM32F103xx增强型)图一.STM32F103xx增强型模块框图工作温度=-40至+105°C (结温达125°C) AF: I/O口上的其他功能3管脚定义图二.STM32F103xx增强型VFQFPN36管脚图四.STM32F103xx增强型LQFP64管脚表三. 管脚定义表三.管脚定义(续)注:1. I :输入, O:输出, S:电源, HiZ:高阻2. FT:兼容5V3. 其中部分功能仅在部分型号芯片中支持,具体信息请参考表2。

4. PC13,PC14和PC15引脚通过电源开关进行供电,因此这三个引脚作为输出引脚时有以下限制:9作为输出脚时只能工作在2MHz模式下9最大驱动负载为30pF9同一时间,三个引脚中只有一个引脚能作为输出引脚。

5. 仅在内嵌大等于64K Flash的型号中支持此类功能。

6. VFQFPN36封装的2号,3号引脚和LQFP48,LQFP64封装的5号,6号引脚在芯片复位后默认配置为OSC_IN和OSC_OUT功能脚。

软件可以重新设置这两个引脚为PD0和PD1功能脚。

但对于LQFP100封装,由于PD0和PD1为固有的功能脚,因此没有必要再由软件进行设置。

更多详细信息请参考STM32F10xxx参考手册的复用功能I/O章节和调试设置章节。

PD0和PD1作为输出引脚只能工作在50MHz模式下。

7. 此类复用功能能够由软件配置到其他引脚上,详细信息请参考STM32F10xxx参考手册的复用功能I/O章节和调试设置章节。

4存储器映像图七存储器图5电气特性请参考英文版数据手册6封装参数请参考英文版数据手册7订货代码表四. 订货代码型号闪存存储器K字节SRAM存储器K字节封装STM32F103C6T6 32 10STM32F103C8T6 64 20STM32F103CBT6 128 20LQFP48STM32F103R6T6 32 10STM32F103R8T6 64 20STM32F103RBT6 128 20LQFP64STM32F103V8T6 64 20STM32F103VBT6 128 20LQFP100STM32F103V8H6 64 20STM32F103VBH6 128 20LFBGA100STM32F103T6U6 32 6STM32F103T8U6 64 10VFQFPN367.1 后续的产品系列后续的STM32F103xx增强型系列产品将会有更广泛的型号选择,芯片将会有更大的封装尺寸并内嵌多达512KB的Flash和48KB的SRAM。

LED显示屏常用IC管脚说明

LED显示屏常用器件的介绍1.IC的管脚功能IC芯片分别:74HC245、74HC595、74HC138、74HC04、4953。

各IC管脚功能如下:A: 74HC245功能是放大及缓冲。

各引脚如图20 和1接电源(+5V)19脚和10脚接电源地(GND)当电源是以上接时:输入脚分别为2、3、4、5、6、7、8、9。

输出脚分别为11、12、13、14、15、16、17、18注:2脚输入时,18脚输出。

其它脚以此类推。

B:74HC138功能是8选1译码器,输出为8行。

控制行数据。

各引脚如图第8脚GND,电源地。

第15脚VCC,电源正极第1-3脚A、B、C,输入脚。

第4-6脚选通输入端,(一般第5脚为EN )9-15脚和第7脚输出端。

C:74HC595功能是8位串入串、并出移位寄存器。

控制列数据。

各引脚如图16脚和10脚接电源(+5V),13脚和8脚接电源地(GND)。

列信号输出脚:1、2、3、4、5、6、7、15。

第一列输出脚为7脚,以此类推。

另第八列输出脚为15脚。

数据信号输入脚(Din)为14,数据信号输出脚(Din)为9。

锁存信号脚(L)为12脚,移位信号脚为11脚。

D:74HC04功能是六带缓冲反相器,控制使零信号(EN)。

各引脚如下图15脚接电源(+5V),7脚电源地(GND)。

信号输入脚为:1、3、5、9、11、13。

信号输出脚为:2、4、6、8、10、12。

E:4953行管功能是开关作用,每个行管控制2行。

1脚和3脚接电源(+5V)。

信号输入脚:2、4。

信号输出脚:5、6、7、8。

5脚和6脚为一组输入,7脚和8脚、5脚和6脚为一组输出。

TB62726与5026 5024 16126的作用:LED驱动芯片,16位移位锁存器。

第1脚GND,电源地。

第24脚VCC,电源正极第2脚DATA,串行数据输入第3脚CLK,时钟输入.第4脚STB,锁存输入 .第23脚输出电流调整端,接电阻调整第22脚DOUT,串行数据输出第21脚EN,使能输入第5-12脚和13-20脚驱动输出端。

LM系列芯片管脚分布及其功能

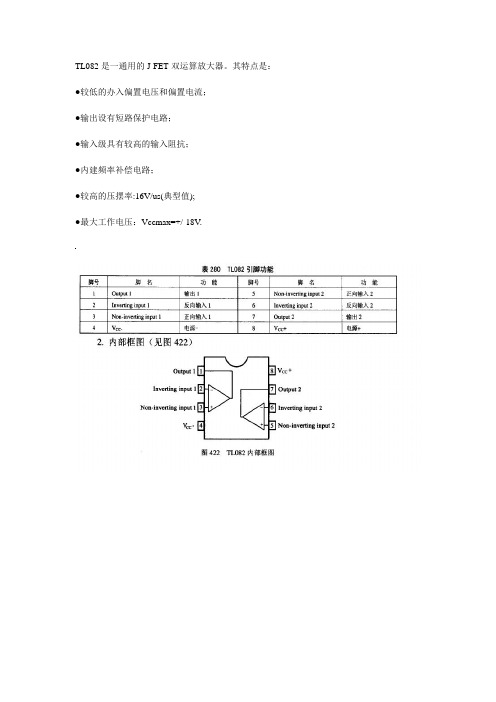

TL082是一通用的J-FET双运算放大器。

其特点是:●较低的办入偏置电压和偏置电流;●输出设有短路保护电路;●输入级具有较高的输入阻抗;●内建频率补偿电路;●较高的压摆率:16V/us(典型值);●最大工作电压:Vccmax=+/-18V.TL082典型应用电路LM324LM324引脚图简介:LM324系列器件为价格便宜的带有真差动输入的四运算放大器。

与单电源应用场合的标准运算放大器相比,它们有一些显著优点。

该四放大器可以工作在低到3.0伏或者高到32伏的电源下,静态电流为MC1741的静态电流的五分之一。

共模输入范围包括负电源,因而消除了在许多应用场合中采用外部偏置元件的必要性。

每一组运算放大器可用图1所示的符号来表示,它有5个引出脚,其中“+”、“-”为两个信号输入端,“V+”、“V-”为正、负电源端,“Vo”为输出端。

两个信号输入端中,Vi-(-)为反相输入端,表示运放输出端Vo的信号与该输入端的位相反;Vi+(+)为同相输入端,表示运放输出端Vo的信号与该输入端的相位相同。

LM324的引脚排列见图2。

参数描述:运放类型:低功率放大器数目:4 带宽:1.2MHz 针脚数:14 工作温度范围:0°C to +70°C 封装类型:SOIC 3dB带宽增益乘积:1.2MHz 变化斜率:0.5V/μs 器件标号:324 器件标记:LM324AD 增益带宽:1.2MHz 工作温度最低:0°C 工作温度最高:70°C 放大器类型:低功耗温度范围:商用电源电压最大:32V 电源电压最小:3V 芯片标号:324 表面安装器件:表面安装输入偏移电压最大:7mV 运放特点:高增益频率补偿运算逻辑功能号:324 额定电源电压, +:15V LM324的特点: 1.短路保护输出 2.真差动输入级 3.可单电源工作:3V-32V 4.低偏置电流:最大100nA 5.每封装含四个运算放大器。

器件管脚图及功能表上课讲义

器件管脚图及功能表收集于网络,如有侵权请联系管理员删除附录6 器件管脚图及功能表74LS74双D 正沿触发器 74LS273八D 触发器74LS377八D 触发器74LS374八D 触发器(三态输出) 74LS175双输出四D 触发器74LS24574LS161四位二进制同步计数器 74LS139双2:4译码器收集于网络,如有侵权请联系管理员删除74LS151八选一选择器74LS157四个二选一选择器74LS257 四个二选一选择器2106116 2K*8 RAM2716 2K*8 ROM2732 4K*8 ROM74LS138 3:8译码器74LS148 8:3八进制优先编码器附录9微指令寄存器的各字段微操作信号输出去向及功能收集于网络,如有侵权请联系管理员删除附录10 联机通讯指南一、准备1、准备一台PC机。

2、把TEC-2机在实验台上放好打开,将TEC-2的随机电源放在TEC-2的左侧,并确认电源开关处在关断的位置。

二、连接电源线1、将TEC-2机电源的直流输出插头P8插在TEC-2机垂直板左侧的插座P8上;将TEC-2机电源的直流输出插头P9插在TEC-2水平板左侧的插座P9上。

特别提醒注意:不要接反P8和P9,否则会烧机器或电源。

2、将TEC-2电源的电源线一端接电源的交流输入插孔,另一端接220V交流电源接线盒。

注意:TEC-2电源的交流电源线必须和计算机的电源线接在同一个有地线的电源接线盒上,以保证两设备共地,否则可能烧毁电源或机器。

三、连接TEC-2和PC1、准备好随机提供的TEC-2和PC的串口通讯电缆。

该电缆一端是9孔的插头,另一端是25孔的插头。

注意:TEC-2随机提供多条通讯电缆,请务必正确选用,以免错误连接造成联机失败。

收集于网络,如有侵权请联系管理员删除2、把串口通讯电缆的9孔插头接在TEC-2机的上板左下角V70插座上,25孔插头插在计算机的串口上(COM1或COM2)。

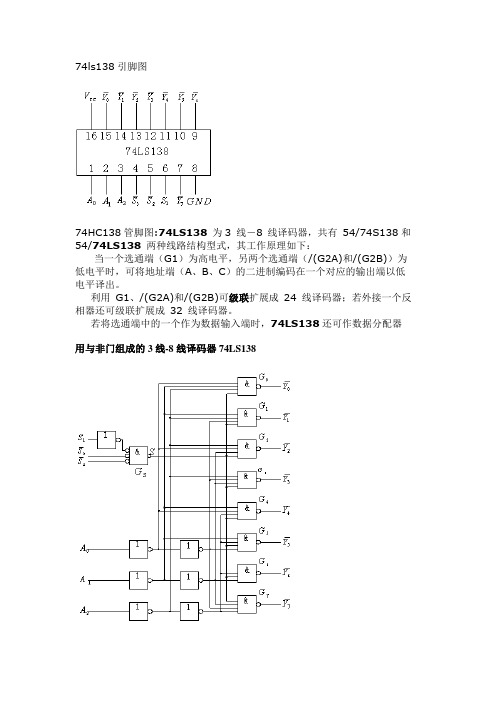

74LS138管脚功能.

74ls138引脚图74HC138管脚图:74LS138为3 线-8 线译码器,共有54/74S138和54/74LS138两种线路结构型式,其工作原理如下:当一个选通端(G1)为高电平,另两个选通端(/(G2A)和/(G2B))为低电平时,可将地址端(A、B、C)的二进制编码在一个对应的输出端以低电平译出。

利用G1、/(G2A)和/(G2B)可级联扩展成24 线译码器;若外接一个反相器还可级联扩展成32 线译码器。

若将选通端中的一个作为数据输入端时,74LS138还可作数据分配器用与非门组成的3线-8线译码器74LS1383线-8线译码器74LS138的功能表无论从逻辑图还是功能表我们都可以看到74LS138的八个输出引脚,任何时刻要么全为高电平1—芯片处于不工作状态,要么只有一个为低电平0,其余7个输出引脚全为高电平1。

如果出现两个输出引脚同时为0的情况,说明该芯片已经损坏。

当附加控制门的输出为高电平(S=1)时,可由逻辑图写出由上式可以看出,同时又是这三个变量的全部最小项的译码输出,所以也把这种译码器叫做最小项译码器。

71LS138有三个附加的控制端、和。

当、时,输出为高电平(S=1),译码器处于工作状态。

否则,译码器被禁止,所有的输出端被封锁在高电平,如表3.3.5所示。

这三个控制端也叫做“片选”输入端,利用片选的作用可以将多篇连接起来以扩展译码器的功能。

带控制输入端的译码器又是一个完整的数据分配器。

在图3.3.8电路中如果把作为“数据”输入端(同时),而将作为“地址”输入端,那么从送来的数据只能通过所指定的一根输出线送出去。

这就不难理解为什么把叫做地址输入了。

例如当=101时,门的输入端除了接至输出端的一个以外全是高电平,因此的数据以反码的形式从输出,而不会被送到其他任何一个输出端上。

【例3.3.2】试用两片3线-8线译码器74LS138组成4线-16线译码器,将输入的4位二进制代码译成16个独立的低电平信号。

元器件封装及基本管脚定义说明(精)

元器件封装及基本管脚定义说明以下收录说明的元件为常规元件A: 零件封装是指实际零件焊接到电路板时所指示的外观和焊点的位置。

包括了实际元件的外型尺寸,所占空间位置,各管脚之间的间距等,是纯粹的空间概念。

因此不同的元件可共用同一零件封装,同种元件也可有不同的零件封装. 普通的元件封装有针脚式封装(DIP与表面贴片式封装(SMD两大类.(像电阻,有传统的针脚式,这种元件体积较大,电路板必须钻孔才能安置元件,完成钻孔后,插入元件,再过锡炉或喷锡(也可手焊),成本较高,较新的设计都是采用体积小的表面贴片式元件(SMD )这种元件不必钻孔,用钢膜将半熔状锡膏倒入电路板,再把SMD 元件放上,即可焊接在电路板上了。

元件按电气性能分类为:电阻, 电容(有极性, 无极性, 电感, 晶体管(二极管, 三极管, 集成电路IC, 端口(输入输出端口, 连接器, 插槽, 开关系列, 晶振,OTHER(显示器件, 蜂鸣器, 传感器, 扬声器, 受话器1. 电阻: I.直插式 [1/20W 1/16W 1/10W 1/8W 1/4W] AXIAL0.3 0.4II. 贴片式 [0201 0402 0603 0805 1206]贴片电阻0603表示的是封装尺寸与具体阻值没有关系但封装尺寸与功率有关通常来说0201 1/20W0402 1/16W0603 1/10W0805 1/8W1206 1/4W电容电阻外形尺寸与封装的对应关系是:0402=1.0x0.50603=1.6x0.80805=2.0x1.21206=3.2x1.61210=3.2x2.51812=4.5x3.22225=5.6x6.5III. 整合式 [0402 0603 4合一或8合一排阻]IIII. 可调式[VR1~VR5]2. 电容: I.无极性电容[0402 0603 0805 1206 1210 1812 2225]II. 有极性电容分两种:电解电容 [一般为铝电解电容, 分为DIP 与SMD 两种]钽电容 [为SMD 型: A TYPE (3216 10V B TYPE (3528 16V C TYPE (6032 25VD TYPE (7343 35V]3. 电感: I.DIP型电感II.SMD 型电感4. 晶体管: I.二极管[1N4148 (小功率 1N4007(大功率发光二极管 (都分为SMD DIP两大类]II. 三极管 [SOT23 SOT223 SOT252 SOT263]常见的to-18(普通三极管)to-22 (大功率三极管to-3 (大功率达林顿管5. 端口: I.输入输出端口[AUDIO KB/MS(组合与分立 LAN COM(DB-9RGB(DB-15 LPT DVI USB(常规, 微型 TUNER(高频头 GAME 1394 SATA POWER_JACK等]II. 排针[单排双排 (分不同间距, 不同针脚类型, 不同角度过 IDE FDD, 与其它各类连接排线.III. 插槽 [DDR (DDR分为SMD 与DIP 两类 CPU座 PCIE PCI CNR SD MD CF AGP PCMCIA]6. 开关:I.按键式II. 点按式III. 拔动式IIII. 其它类型7. 晶振: I. 有源晶振 (分为DIP 与SMD 两种包装,一個電源PIN ,一個GND PIN,一個訊號PINII.无源晶振(分为四种包装, 只有接兩個訊號PIN ,另有外売接GND )8. 集成电路IC:I.DIP (Dual In-line Package):双列直插封装。

LM系列芯片管脚分布及功能

TL082是一通用的J-FET双运算放大器。

其特点是:●较低的办入偏置电压和偏置电流;●输出设有短路保护电路;●输入级具有较高的输入阻抗;●内建频率补偿电路;●较高的压摆率:16V/us(典型值);●最大工作电压:Vccmax=+/-18V.TL082典型应用电路LM324LM324引脚图简介:LM324系列器件为价格便宜的带有真差动输入的四运算放大器。

与单电源应用场合的标准运算放大器相比,它们有一些显著优点。

该四放大器可以工作在低到3.0伏或者高到32伏的电源下,静态电流为MC1741的静态电流的五分之一。

共模输入范围包括负电源,因而消除了在许多应用场合中采用外部偏置元件的必要性。

每一组运算放大器可用图1所示的符号来表示,它有5个引出脚,其中“+”、“-”为两个信号输入端,“V+”、“V-”为正、负电源端,“Vo”为输出端。

两个信号输入端中,Vi-(-)为反相输入端,表示运放输出端Vo的信号与该输入端的位相反;Vi+(+)为同相输入端,表示运放输出端Vo的信号与该输入端的相位相同。

LM324的引脚排列见图2。

参数描述:运放类型:低功率放大器数目:4 带宽:1.2MHz 针脚数:14 工作温度范围:0°C to +70°C 封装类型:SOIC 3dB带宽增益乘积:1.2MHz 变化斜率:0.5V/μs 器件标号:324 器件标记:LM324AD 增益带宽:1.2MHz 工作温度最低:0°C 工作温度最高:70°C 放大器类型:低功耗温度范围:商用电源电压最大:32V 电源电压最小:3V 芯片标号:324 表面安装器件:表面安装输入偏移电压最大:7mV 运放特点:高增益频率补偿运算逻辑功能号:324 额定电源电压, +:15V LM324的特点: 1.短路保护输出 2.真差动输入级 3.可单电源工作:3V-32V 4.低偏置电流:最大100nA 5.每封装含四个运算放大器。

74hc595的引脚功能和作用

描述74HC59574HC595是硅结构的CMOS器件,兼容低电压TTL电路,遵守JEDEC标准。

74HC595是具有8位移位寄存器和一个存储器,三态输出功能。

移位寄存器和存储器是分别的时钟。

数据在SHcp的上升沿输入,在STcp的上升沿进入的存储寄存器中去。

如果两个时钟连在一起,则移位寄存器总是比存储寄存器早一个脉冲。

移位寄存器有一个串行移位输入(Ds),和一个串行输出(Q7’),和一个异步的低电平复位,存储寄存器有一个并行8位的,具备三态的总线输出,当使能OE时(为低电平),存储寄存器的数据输出到总线。

8位串行输入/输出或者并行输出移位寄存器,具有高阻关断状态。

三态。

[编辑本段]特点8位串行输入/8位串行或并行输出存储状态寄存器,三种状态输出寄存器可以直接清除100MHz的移位频率[编辑本段]输出能力并行输出,总线驱动;串行输出;标准中等规模集成电路595移位寄存器有一个串行移位输入(Ds),和一个串行输出(Q7’),和一个异步的低电平复位,存储寄存器有一个并行8位的,具备三态的总线输出,当使能OE时(为低电平),存储寄存器的数据输出到总线。

[编辑本段]参考数据CPD决定动态的能耗,PD=CPD×VCC×f1+∑(CL×VCC2×f0) F1=输入频率,CL=输出电容f0=输出频率(MHz)Vcc=电源电压[编辑本段]引脚说明符号引脚描述Q0…Q7 15,1,7 并行数据输出GND 8 地Q7’ 9 串行数据输出MR 10 主复位(低电平)SHCP 11 移位寄存器时钟输入STCP 12 存储寄存器时钟输入OE 13 输出有效(低电平)DS 14 串行数据输入VCC 16 电源[编辑本段]功能表输入输出功能SHCP STCP OE MR DS Q7’ Qn × × L ↓ × L NC MR为低电平时仅仅影响移位寄存器× ↑ L L × L L 空移位寄存器到输出寄存器×× H L × L Z 清空移位寄存器,并行输出为高阻状态↑ × L H H Q6 NC 逻辑高电平移入移位寄存器状态0,包含所有的移位寄存器状态移入,例如,以前的状态6(内部Q6”)出现在串行输出位。

74hc595的引脚功能和作用

描述74HC59574HC595是硅结构的CMOS器件,兼容低电压TTL电路,遵守JEDEC标准。

74HC595是具有8位移位寄存器和一个存储器,三态输出功能。

移位寄存器和存储器是分别的时钟。

数据在SHcp的上升沿输入,在STcp的上升沿进入的存储寄存器中去。

如果两个时钟连在一起,则移位寄存器总是比存储寄存器早一个脉冲。

移位寄存器有一个串行移位输入(Ds),和一个串行输出(Q7’),和一个异步的低电平复位,存储寄存器有一个并行8位的,具备三态的总线输出,当使能OE时(为低电平),存储寄存器的数据输出到总线。

8位串行输入/输出或者并行输出移位寄存器,具有高阻关断状态。

三态。

[编辑本段]特点8位串行输入/8位串行或并行输出存储状态寄存器,三种状态输出寄存器可以直接清除100MHz的移位频率[编辑本段]输出能力并行输出,总线驱动;串行输出;标准中等规模集成电路595移位寄存器有一个串行移位输入(Ds),和一个串行输出(Q7’),和一个异步的低电平复位,存储寄存器有一个并行8位的,具备三态的总线输出,当使能OE时(为低电平),存储寄存器的数据输出到总线。

[编辑本段]参考数据CPD决定动态的能耗,PD=CPD×VCC×f1+∑(CL×VCC2×f0) F1=输入频率,CL=输出电容f0=输出频率(MHz)Vcc=电源电压[编辑本段]引脚说明符号引脚描述Q0…Q7 15,1,7 并行数据输出GND 8 地Q7’ 9 串行数据输出MR 10 主复位(低电平)SHCP 11 移位寄存器时钟输入STCP 12 存储寄存器时钟输入OE 13 输出有效(低电平)DS 14 串行数据输入VCC 16 电源[编辑本段]功能表输入输出功能SHCP STCP OE MR DS Q7’ Qn × × L ↓ × L NC MR为低电平时仅仅影响移位寄存器× ↑ L L × L L 空移位寄存器到输出寄存器×× H L × L Z 清空移位寄存器,并行输出为高阻状态↑ × L H H Q6 NC 逻辑高电平移入移位寄存器状态0,包含所有的移位寄存器状态移入,例如,以前的状态6(内部Q6”)出现在串行输出位。

CD4011工作原理及引脚图,功能,参数,作用详解

CD4011工作原理及引脚图,功能,参数,作用详解现在,很多朋友已经放弃单硅后极,转向MOS或IGBT等更节能,更轻便的斩波电路。

常规的单NE555调频调宽电路,调节的时候频率脉宽相互影响,用2片555可以实现独立可调,但线路相对复杂了,外围元件多了。

向大家推荐CD4011,四2输入与非门芯片CD4011内部由四2输入端与非门单元电路构成,采用N和P沟道增强型MOS 晶体管提供的对称电路,具有很高的抗干扰度。

一:CD4011工作原理及引脚图,功能,参数,作用详解---CD4011工作原理相信大部分的电子工程师都对CD4011有所涉猎,CD4011是应用广泛的数字IC之一,它们内含4个独立的2输入端与非门,其逻辑功能是:输入端全部为“1”时,输出为“0”;输入端只要有“0”,输出就为“1”,当两个输入端都为0时,输出是1。

cd4011内部为4组与非门,供电为14正,7负,123脚是一组与非,12脚同时高电平,3脚为低电平,12脚别的状态3脚都是高电平,另外三组在电路中为反相器,也就是11脚和3脚是相反的,3高11低,3低11高,1脚外接光控,2脚为触发延时。

CD4011属于数字电路,当将它一组的两个输入端相连时,这一组就变成了一个非门。

其特点是:输入高电平时,输出低电平,输入低电平时,输出高电平。

CD4011还能够放大电压,当运放的+接地,-只接高电平而不接电阻时,它的输出是什么,是低电平。

反之,-只接低电平而不接电阻时,它的输出是什么,是高电平。

注意到上面的比较没有,其实,CD4011在此时与运放的功能完全一样。

CD4011与两个电阻配合,其一为输入电阻,其二为反馈电阻,它的作用就是一个反向比例放大器。

因此,CD4011能放大电压。

二:CD4011工作原理及引脚图,功能,参数,作用详解---CD4011参数cd4011的直流电气特性与交流电气特性见下表:CD4011 BM -55℃ - +125℃CD4011 BC -40℃ - +85℃VDD电压范围:-0.5V ----- 18V功耗:双列普通封装 700mW 小型封装 500mW三:CD4011工作原理及引脚图,功能,参数,作用详解---CD4011的逻辑功能(1)当X=0、Y=0时,将使两个NAND门之输出均为1,违反触发器之功用,故禁止使用。

引脚功能与内部结构图

在生产制造过程中,引脚的设计 和制造工艺必须严格控制,以确 保其具有良好的导电性能、机械

强度和耐腐蚀性。

引脚与电路板或其他连接器的接 触性能也是影响产品性能的重要 因素,因此需要采取有效的措施

来确保良好的接触。

如何保证引脚的质量和可靠性

01 在生产过程中,应采用高精度的制造设备和工艺, 确保引脚的尺寸和形状精度符合要求。

03

内部结构对引脚的热设计有要 求,需要考虑到元件在工作时 的发热情况,合理设计引脚的 散热方式。

如何根据内部结构选择合适的引脚

01

根据电路板上的线路布局和焊接方式选择合适的引 脚,确保元件能够顺利安装和稳定工作。

02

根据元件的型号和参数选择相应的引脚,确保引脚 上印有的信息准确无误。

03

根据元件在工作时的发热情况选择合适的引脚材质 和尺寸,确保元件能够得到良好的散热效果。

模块化设计

通过使用不同规格和类型 的引脚,可以实现模块化 设计,方便组装和维修。

引脚设计

间距与规格

引脚的间距和规格需要根据具体的电路板和元件规格进行设计, 以满足电气性能和机械强度的要求。

材料选择

引脚的材料选择对其电气性能、机械强度和可靠性有着重要影响, 常用的材料有铜、不锈钢等。

长度与形状

引脚的长度和形状需要根据具体的应用场景进行设计,以满足信号 传输和连接稳定性的要求。

自动化生产中,引脚的加工、检测、组装等环节都可以通过自动化设备来完成,大 大提高了生产效率和产品质量。

谢谢观看

02

内部结构图解析

集成电路内部结构

集成电路是将多个电子元件集成在一块衬底上,实现一定的电路或系统功能的微型电子部件。其内部 结构包括输入输出引脚、逻辑门、触发器、存储器等电路元件,以及连接这些元件的导线和互连线。

详解场效应管管脚图接线图、引脚、检测方法、注意事项等

详解场效应管管脚图接线图、引脚、检测⽅法、注意事项等mos管三个引脚怎么区分G极,不⽤说⽐较好认。

S极,不论是p沟道还是N沟道,两根线相交的就是;D极,不论是p沟道还是N沟道,是单独引线的那边。

判定栅极G:场效应管管脚图接线图将万⽤表拨⾄R&TImes;1k档,⽤万⽤表的负极任意接⼀电极,另⼀只表笔依次去接触其余的两个极,测其电阻。

若两次测得的电阻值近似相等,则负表笔所接触的为栅极,另外两电极为漏极和源极。

漏极和源极互换,若两次测出的电阻都很⼤,则为N沟道;若两次测得的阻值都很⼩,则为P沟道。

判定源极S、漏极D:在源-漏之间有⼀个PN结,因此根据PN结正、反向电阻存在差异,可识别S极与D极。

⽤交换表笔法测两次电阻,其中电阻值较低(⼀般为⼏千欧⾄⼗⼏千欧)的⼀次为正向电阻,此时⿊表笔的是S极,红表笔接D极。

MOS管脚测定⽅法①栅极G的测定:⽤万⽤表R×100 档,测任意两脚之间正反向电阻,若其中某次测得电阻为数百Ω),该两脚是D、S,第三脚为G。

②漏极D、源极S及类型判定:⽤万⽤表 R ×10kΩ档测 D、S问正反向电阻,正向电阻约为0.2×10kΩ,反向电阻(5⼀∞)X100kΩ。

在测反向电阻时,红表笔不动,⿊表笔脱离引脚后,与G碰⼀下,然后回去再接原引脚,出现两种情况:a.若读数由原来较⼤值变为0(0×10kΩ),则红表笔所接为S,⿊表笔为D。

⽤⿊表笔接触G有效,使MOS管D、S间正反向电阻值均为0Ω,还可证明该管为N沟道。

b.若读数仍为较⼤值,⿊表笔不动,改⽤红表笔接触G,碰⼀下之后⽴即回到原脚,此时若读数为0Ω,则⿊表笔接的是S极、红表笔为D极,⽤红表笔接触G极有效,该MOS管为P沟道。

场效应管的检测和使⽤⼀、⽤指针式万⽤表对场效应管进⾏判别(1)⽤测电阻法判别结型场效应管的电极根据场效应管的PN结正、反向电阻值不⼀样的现象,可以判别出结型场效应管的三个电极。

引脚图

2.芯片简介 2.1Lm555用来输出连续脉冲,管脚分布如图3-7所示引脚编号 符号 功能说明① GND 地线 ② TR 触发 ③OUT 输出 ④RES 复位 ⑤ CV 控制电压 ⑥TH 阀值 ⑦DIS 放电 ⑧VCC 电源 电路特点:LM555 时基电路内部由分压器、比较器、触发器、输出管和放电管等组成,是模拟电路和数字电路的混合体。

其中 6 脚为阀值端(TH ),是上比较器的输入。

2 脚为触发端(TR ),是下比较器的输入。

3 脚为输出端(OUT ),有 0 和 1 两种状态,它的状态由输入端所加的电平决定。

7 脚为放电端(DIS ),是内部放电管的输出,它有悬空和接地两种状态,也是由输入端的状态决定。

4 脚为复位端(R ),叫上低电平(< 0.3V )时可使输出端为低电平。

5 脚为控制电压端(CV ),可以用它来改变上下触发电平值。

8 脚为电源(VCC ),1 脚为地(GND )。

2.2 CD4013用来产生单次脉冲,管脚分布如图3-8所示: 管脚作用:1Q 、1Q 、2Q 、2Q 分别为两个D 触发器的输入管脚。

RESET1、RESET2分别为两个D 触发器的复位端。

D1、D2为两个D 触发器的输出端。

SET1、SET2为两个D 触发器的使能端。

图3-8CD4510 图3-9 CD4510管脚图CD4510为可预置BCD 可逆计数器,该器件主要由四位具有同步时钟的D 型触发器(具有选通结构,提供T 型触发器功能)构成。

具有可预置数、加减计数器和多片级联使用等功能。

U/、时钟CP和CD4510具有复位CR,置数控制LD、并行数据D0~D3、加减控制D进位等CI输入。

CR为高电平时,计数器清零。

当LD为高电平时,D0~D3上的数据置入U/为高电平,计数器中,CI控制计数器的计数操作,CI=0时,允许计数。

此时,若D在CP时钟上升沿计数器加1计数;反之,在CP时钟上升沿减1计数。

除了四个Q输出外,CO/。

UC3875引脚及功能介绍

UC3875引脚及功能介绍UC3875是Unitrode公司生产的移相谐振全桥软开关控制器,它有4个独立的输出驱动端可以直接驱动四只功率MOSFET管,见图1,其中OUTA和OUTB相位相反,OUTC和OUTD相位相反,而OUTC和OUTD相对于OUTA和OUTB的相位θ是可调的,也正是通过调节θ的大小来进行PWM控制的。

图1管脚示意图UC3875的管脚功能UC3875有20脚和28脚两种,这里仅介绍20脚的UC3875的管脚功能,表1为管脚功能简要说明。

表1UC3875各个管脚的使用说明管脚1可输出精确的5V基准电压,其电流可以达到60mA。

当VIN比较低时,芯片进入欠压锁定状态VREF消失。

直到VREF达到4.75V以上时才脱离欠压锁定状态。

最好的办法是接一个0.1μF旁路电容到信号地。

管脚2为电压反馈增益控制端,当误差放大器的输出电压低于1V时实现0°相移。

管脚3为误差放大器的反相输入端,该脚通常利用分压电阻检测输出电源电压。

管脚4为误差放大器的同相输入端,该脚与基准电压相连,以检测E/A(-)端的输出电源电压。

管脚5为电流检测端,该脚为电流故障比较器的同相输入端,其基准设置为内部固定2.5V(由VREF分压)。

当该脚的电压超过2.5V时电流故障动作,输出被关断,软起动复位,此脚可实现过流保护。

管脚6为软起动端,当输入电压(VIN)低于欠压锁定阈值(10.75V)时,该脚保持低电平,当VIN正常时该脚通过内部9μA电流源上升到4.8V,如果出现电流故障时该脚电压从4.8V下降到0V,此脚可实现过压保护。

管脚7、15为输出延迟控制端,通过设置该脚到地之间的电流来设置死区,加于同一桥臂两管驱动脉冲之间,以实现两管零电压开通时的瞬态时间,两个半桥死区可单独提供以满足不同的瞬态时间。

管脚8、9、13、14为输出OUTA~OUTD端,该脚为2A的图腾柱输出,可驱动MOSFET 和变压器。

管脚10为驱动输出电源电压端(对应管脚12 PWRGND),该脚提供输出级所需电源,Vc通常接3V以上电源,最佳为12V。

常用电子器件管脚排列图

常用电子器件管脚排列图附录1 逻辑符号对照示例附录表1.1 逻辑非、逻辑极性符号对照示例(以反相器为例)附录表1.2 几种常用逻辑门的逻辑符号比较示例附录表1.3 逻辑符号、框图、管脚排列比较示列(以74HC 390为例)附录2 集成电路1. 集成电路命名方法 集成电路命名方法见附录表2.1附录表2.1 国产半导体集成电路型号命名法(GB3430-82)2.集成电路介绍 集成电路I C 是封在单个封装件中的一组互连电路。

装在陶瓷衬底上的分立元件或电路有时还和单个集成电路连在一起,称为混合集成电路。

把全部元件和电路成型在单片晶体硅材料上称单片集成电路。

单片集成电路现在已成为最普及的集成电路形式,它可以封装成各种类型的固态器件,也可以封装成特殊的集成电路。

通用集成电路分为模拟(线性)和数字两大类。

模拟电路根据输入的各种电平,在输出端产生各种相应的电平;而数字电路是开关器件,以规定的电平响应导通和截止。

有时候集成电路标有L M (线性类型) 或DM(数字类型)符号。

集成电路都有二或三个电源接线端:用CC V 、DD V 、SS V 、V +、V -或GND 来表示。

这是一般应用所需要的。

双列直插式是集成电路最通用的封装形式。

其引脚标记有半圆形豁口、标志线、标志圆点 等,一般由半圆形豁口就可以确定各引脚的位置。

双列直插式的引脚排列图如附录图2.1所示。

3.使用TFL 集成电路与C M OS 集成电路的注意事项 (1) 使用TYL 集成电路注意事项① TYL 集成电路的电源电压不能高于V 5.5+。

附录图 2.1双列直插式集成电路的引脚排使用时,不能将电源与地颠倒错接,否则将会因为过大电流而造成器件损坏。

②电路的各输入端不能直接与高于和V 5.5+低于的低内V 5.0-阻电源连接,因为低内阻电源能提供较大的电流,导致器件过热而烧坏。

STM32F103引脚功能定义

2.1

器件一览

表二:器件功能和配置(STM32F103xx 增强型)

外设 闪存(K字节) RAM(K字节) 通用 定时器 高级 SPI I2C 通信 USART USB CAN 通用I/O端口 12位同步ADC CPU频率 工作电压 工作温度 封装 VFQFPN36 1 1 2 1 1 26 2 10通道 1 2 2 3 1 1 1 1 2 1 1 1 2 2 3 1 1 32 2 10通道 72MHz 2.0至3.6V -40至+85°C / -40至+105°C LQFP48 LQFP64 LQFP100, BGA100 2 2 3 1 1 1 1 2 1 1 51 2 16通道 1 2 2 3 1 1 1 2 2 3 1 1 80 STM32F103Tx 32 10 2 64 20 3 32 10 2

PA4 PA5 PA6 PA7 PC4 PC5 PB0 PB1 PB2/BOOT1 PE7 PE8 PE9 PE10 PE11 PE12 PE13 PE14 PE15 PB10 PB11 VSS_1 VDD_1 PB12

J4 18 26 35 15 K4 19 27 36 16 G5 20 28 37 17 H5 - - 38 J5 - - 39 K5 - - 40 G6 - - 41 H6 - - 42 J6 - - 43 K6 - - 44 G7 - - 45 H7 - - 46 J7 21 29 47 K7 22 30 48 -

WKUP/USART2_CTS(6) ADC12_IN0/TIM2_CH1 _ETR(6) USART2_RTS(6)/ADC1 2_IN1/TIM2_CH2(6) USART2_TX(6)/ADC12 _IN2/TIM2_CH3(6) USART2_RX(6)/ADC12 _IN3/TIM2_CH4(6)

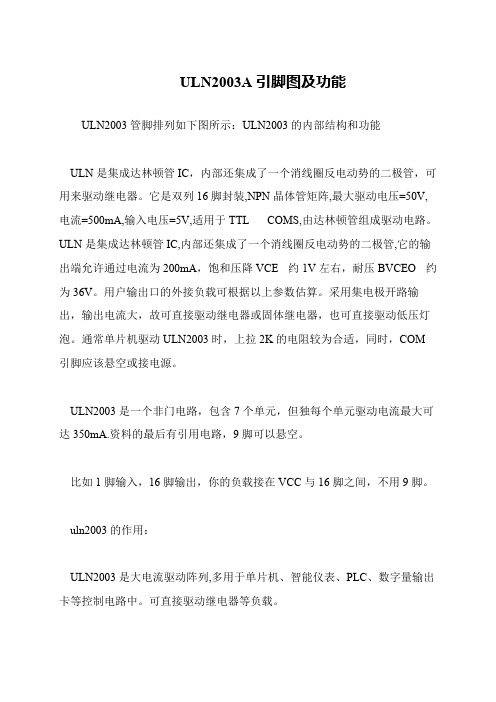

ULN2003A引脚图及功能

ULN2003A引脚图及功能ULN2003管脚排列如下图所示:ULN2003的内部结构和功能 ULN是集成达林顿管IC,内部还集成了一个消线圈反电动势的二极管,可用来驱动继电器。

它是双列16脚封装,NPN晶体管矩阵,最大驱动电压=50V,电流=500mA,输入电压=5V,适用于TTL COMS,由达林顿管组成驱动电路。

ULN是集成达林顿管IC,内部还集成了一个消线圈反电动势的二极管,它的输出端允许通过电流为200mA,饱和压降VCE 约1V左右,耐压BVCEO 约为36V。

用户输出口的外接负载可根据以上参数估算。

采用集电极开路输出,输出电流大,故可直接驱动继电器或固体继电器,也可直接驱动低压灯泡。

通常单片机驱动ULN2003时,上拉2K的电阻较为合适,同时,COM 引脚应该悬空或接电源。

ULN2003是一个非门电路,包含7个单元,但独每个单元驱动电流最大可达350mA.资料的最后有引用电路,9脚可以悬空。

比如1脚输入,16脚输出,你的负载接在VCC与16脚之间,不用9脚。

uln2003的作用: ULN2003是大电流驱动阵列,多用于单片机、智能仪表、PLC、数字量输出卡等控制电路中。

可直接驱动继电器等负载。

输入5VTTL电平,输出可达500mA/50V。

ULN2003是高耐压、大电流达林顿陈列,由七个硅NPN达林顿管组成。

该电路的特点如下: ULN2003的每一对达林顿都串联一个2.7K的基极电阻,在5V的工作电压下它能与TTL和CMOS电路直接相连,可以直接处理原先需要标准逻辑缓冲器。

ULN2003 是高压大电流达林顿晶体管阵列系列产品,具有电流增益高、工作电压高、温度范围宽、带负载能力强等特点,适应于各类要求高速大功率驱动的系统。

ULN2003A引脚图及功能 ULN2003 是高耐压、大电流、内部由七个硅NPN 达林顿管组成的驱动芯片。

经常在以下电路中使用,作为: 1、显示驱动 2、继电器驱动 3、照明灯驱动 4、电磁阀驱动 5、伺服电机、步进电机驱动等电路中。

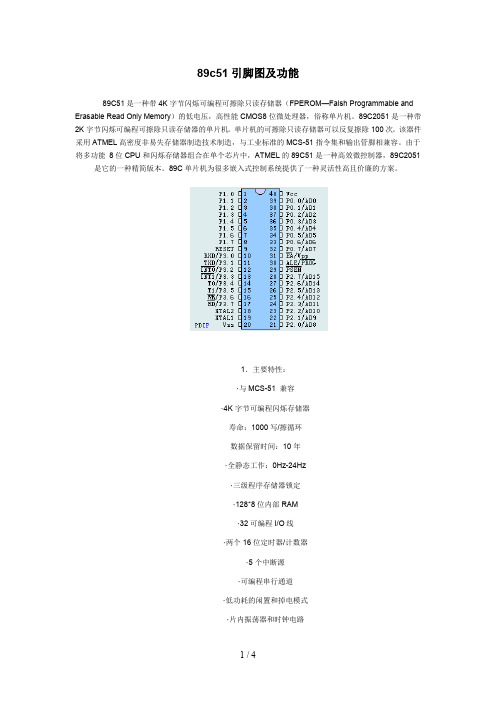

89c51引脚图及功能中文资料

89c51引脚图及功能89C51是一种带4K字节闪烁可编程可擦除只读存储器(FPEROM—Falsh Programmable and Erasable Read Only Memory)的低电压,高性能CMOS8位微处理器,俗称单片机。

89C2051是一种带2K字节闪烁可编程可擦除只读存储器的单片机。

单片机的可擦除只读存储器可以反复擦除100次。

该器件采用ATMEL高密度非易失存储器制造技术制造,与工业标准的MCS-51指令集和输出管脚相兼容。

由于将多功能8位CPU和闪烁存储器组合在单个芯片中,ATMEL的89C51是一种高效微控制器,89C2051是它的一种精简版本。

89C单片机为很多嵌入式控制系统提供了一种灵活性高且价廉的方案。

1.主要特性:·与MCS-51 兼容·4K字节可编程闪烁存储器寿命:1000写/擦循环数据保留时间:10年·全静态工作:0Hz-24Hz·三级程序存储器锁定·128*8位内部RAM·32可编程I/O线·两个16位定时器/计数器·5个中断源·可编程串行通道·低功耗的闲置和掉电模式·片内振荡器和时钟电路2.管脚说明:VCC:供电电压。

GND:接地。

P0口:P0口为一个8位漏级开路双向I/O口,每脚可吸收8TTL门电流。

当P1口的管脚第一次写1时,被定义为高阻输入。

P0能够用于外部程序数据存储器,它可以被定义为数据/地址的第八位。

在FIASH编程时,P0 口作为原码输入口,当FIASH进行校验时,P0输出原码,此时P0外部必须被拉高。

P1口:P1口是一个内部提供上拉电阻的8位双向I/O口,P1口缓冲器能接收输出4TTL门电流。

P1口管脚写入1后,被内部上拉为高,可用作输入,P1口被外部下拉为低电平时,将输出电流,这是由于内部上拉的缘故。

在FLASH编程和校验时,P1口作为第八位地址接收。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

1附录6 器件管脚图及功能表74LS74双D 正沿触发器 74LS273八D 触发器 74LS377八D 触发器74LS374八D 触发器(三态输出) 74LS175双输出四D 触发器74LS24574LS161四位二进制同步计数器 74LS139双2:4译码器274LS151 八选一选择器74LS157 四个二选一选择器74LS257 四个二选一选择器(非反相三态输出)注:i 等于d 2d 1d 0对应的十进制数6116 2K*8 RAM 2716 2K*8 ROM 2732 4K*8 ROM74LS138 3:8译码器 74LS148 8:3八进制优先编码器74LS85 四位幅度比较器附录9微指令寄存器的各字段微操作信号输出去向及功能指令字段IR7~03附录10 联机通讯指南一、准备1、准备一台PC机。

2、把TEC-2机在实验台上放好打开,将TEC-2的随机电源放在TEC-2的左侧,并确认电源开关处在关断的位置。

二、连接电源线1、将TEC-2机电源的直流输出插头P8插在TEC-2机垂直板左侧的插座P8上;将TEC-2机电源的直流输出插头P9插在TEC-2水平板左侧的插座P9上。

特别提醒注意:不要接反P8和P9,否则会烧机器或电源。

2、将TEC-2电源的电源线一端接电源的交流输入插孔,另一端接220V交流电源接线盒。

注意:TEC-2电源的交流电源线必须和计算机的电源线接在同一个有地线的电源接线盒上,以保证两设备共地,否则可能烧毁电源或机器。

三、连接TEC-2和PC1、准备好随机提供的TEC-2和PC的串口通讯电缆。

该电缆一端是9孔的插头,另一端是25孔的插头。

注意:TEC-2随机提供多条通讯电缆,请务必正确选用,以免错误连接造成联机失败。

2、把串口通讯电缆的9孔插头接在TEC-2机的上板左下角V70插座上,25孔插头插在计算机的串口上(COM1或COM2)。

如果PC上没有25针的串口或者25针的串口已被其它设备占用,TEC-2 随机提供一个9转25的转换器可以把25孔的插头转换成9孔的插头,接在9针的串口上。

四、TEC-2的初始设置将TEC-2大板下方钮子开关S2~S0拨成100(向上为“1”,向下为“0”);FS1~FS4拨成1010(向上为“1”,向下为“0”);将CONT/STEP钮子开关拨到CONT位置。

五、开机1、打开计算机电源开关,使计算机正常启动。

2、打开TEC-2电源开关,TEC-2大板左上角一排指示灯亮。

六、加载通讯软件1、用户可以根据联机PC的软件配置情况选择以下三种方法之一运行联机通讯软件。

45• 如果计算机没有硬盘,把用户程序盘插入软驱,并用它启动计算机,然后键入: A :\>CD TEC-2 A :\>PCEC• 如果计算机有硬盘并且装有DOS 操作系统,则进行以下操作: C :\>MD TEC-2C :\>COPY A :\TEC-2 C :\TEC-2 C :\>CD TEC-2 C :\TEC-2>PCEC• 如果计算机有硬盘并且装有WINDOWS 操作系统,把用户程序盘插入软驱,将软盘中的文件夹“TEC-2”拷贝到C :\盘,点击“开始→运行”,在弹出的窗口中键入:C :\TEC-2\PCEC ↙正确执行上述操作就会在计算机屏幕上出现以下界面:2、用计算机的串口COM1和TEC-2通讯,选择“1”,直接回车; 用计算机的串口COM2和TEC-2通讯,选择“2”,然后按回车键。

此时计算机屏幕上出现以下设置信息:*************************************************************Baud Rate = 9600 bits/second Parity = None Stop bit = 1 bitCharacter Length = 8 bits Change these characters ? (N )*************************************************************F10→Display Main MenuALT F10→Copy Screen to File SCA.TMPRS232 Serial Port Number [1/2]:1**********************************************************此界面的设置为推荐设置,键入“N”键后回车。

然后按压TEC-2大板左下角的LDMC/RESET键加载微程序。

这时计算机屏幕出现以下界面表示联机成功:****************************************************************TEC-2 CRT MONITORVersion 5.0, Jan. 1994Computer Architecture Lab., Tsinghua University>****************************************************************此时可以运行TEC-2计算机系统的指令,如U、D、T、P、A等或做TEC-2计算机组成原理的实验。

如果按压LDMC/RESET键后屏幕上没有任何反应,这时可按F10屏幕出现以下界面:****************************************************************0…Return to TEC-2 CRT Monitor1…Send a file to TEC-22…Receive a file from TEC-23…Return to PC (MS) –DOSEnter your choice:[0]****************************************************************选(3)或者按Ctrl+Pause键退出联机通讯程序,重新运行程序PCEC,并选择另一个串口再试。

注意:开机时先开计算机的电源,当计算机正常启动后,再打开TEC-2机的电源;关机时应先关掉TEC-2机的电源,再关掉计算机的电源。

任何时间一定不要带电操作。

67附录11 并行接口芯片8255A 简介1.8255A 的内部结构8255A 的内部结构如图3.11.1所示。

它由以下几个部分组成: (1)三个数据端口A 、B 、C8255A 芯片内部有三个8位的输入输出端口,分别为A 口、B 口和C 口,可用指令将它们分别设置成输入或输出端口。

它们在结构和功能上有各自的特点。

图 3.11.1 8255A 的内部结构及引脚端口A 包含一个8位数据输入锁存器和一个8位的数据输出锁存器/缓冲器。

端口A 无论用作输入口还是输出口,其数据均能受到锁存。

端口B 包含一个8位数据输入缓冲器和一个8位的数据输出锁存器/缓冲器。

用端口B 作为输出口时,其数据能得到锁存。

作为输入口时,它不具有锁存能力,因此外设输入的数据必须维持到被CPU 读取为止。

端口C 包含一个8位数据输入缓冲器和一个8位的数据输出锁存器/缓冲器,作为输入口时,它不具有锁存能力。

端口A 和端口B 一般作为独立的I/O 口使用,与外设的数据线相连。

端口C 可以作为一个独立的8位I/O 口,也可以拆分为高4位和低4位的两个4位端口,作为二个独立的4位I/O 口使用;端口C 拆分开的高4位和低4位还可以与端口A 和端口B 配合,用作它们的联络信号线。

(2)A 组控制、B 组控制8255A 将端口A 、B 、C 分为两组:端口A 和端口C 的高4位构成A 组,由A 组控制逻辑电路进行控制;端口B 和端口C 的低4位构成B 组,由B 组控制逻辑电路进行控制。

这两组控制逻辑都从读/写控制逻辑接收命令信号和读写信号,从内部数据总线接收控制字,并根据控制字确定各端口的工作方式。

(3)数据总线缓冲器数据总线缓冲器是一个双向三态的8位缓冲器,它直接与系统数据总线连接,是8255A 与CPU之间传输数据的必经之路,数据的输入输出以及控制字的写入都是通过这个缓冲器传递的。

(4)读/写控制逻辑读/写控制逻辑电路负责管理8255A的数据传输过程。

它接收来自控制总线的控制信号/WR、/RD、RESET和地址总线的A1、A0以及由地址译码输出的片选信号/CS,由这些信号形成对端口的读写控制,并通过A组控制和B组控制电路实现对数据、状态和控制信息的传输。

2.8255A的外部引脚8255A芯片采用NMOS工艺制造,是一个40引脚双列直插式(DIP)封装组件。

其引脚排列如图3.11.1所示,各引脚信号名称和含义如下。

(1)与CPU连接的信号线D7~D0:8255A的双向三态数据线,和系统的数据总线相连。

A1、A0、/RD、/WR、/CS信号组合所实现的各种端口操作见表3.11.1所示。

表 3.11.1(2)8255A与外部设备相连的信号线PA7~PA0:A口与外部设备连接的数据线,由A口的工作方式决定这些引脚用作输入、输出或双向。

PB7~PB0:B口与外部设备连接的数据线,由B口的工作方式决定这些引脚用作输入或输出。

89PC7~PC0:C 口输入输出数据线,这些引脚的用途由A 组,B 组的工作方式决定。

这24根信号线均可用来连接I/O 设备,它们可以传送数字量或开关量信号,C 端口还常常用来传递控制和状态信号。

3.8255A 的控制字8255A 有两类控制字:一类用于定义各端口的工作方式,称为方式选择控制字;另一类用于对C 端口的一位进行置位或复位操作,称为C 端口置位/复位控制字。

这里只介绍方式选择控制字。

(1)方式选择控制字8255A 共有三种基本工作方式,它们是: 方式0:基本的输入/输出方式。

方式1:选通输入/输出方式(应答方式)。

方式2:双向传输方式。

这里只介绍8255A 的方式0。

8255A 各数据端口的工作方式由方式选择控制字(如图3.11.2所示)进行设置。

对8255A 进行初始化编程时,通过向控制字寄存器写入方式选择控制字,可以让三个数据端口以需要的方式工作。

图 3.11.2 8255A 的方式选择控制字其中,D7位是方式选择控制字的标志位,它必须是1;D6D5位用于选择A 口的工作方式;D2位用于选择B 口的工作方式;D4、D3、D1、D0位分别用于选择A 口、C 口高四位、B 口和C 口低四位的输入输出功能,置1时输入,置0时输出。

端口A可工作在3种工作方式中的任何一种,端口B只能工作在方式0或方式1,端口C则常常配合端口A和端口B工作,为这两个端口的输入/输出传输提供控制信号和状态信号。