XIN第04章 主存储器与存储系统 4-2_图文.ppt

合集下载

第4章存储器系统

2019/12/16

7

• (3) 顺序存取存储器(SAM)

• SAM存储器所存信息的排列、寻址和读写操作 均是按顺序进行的,并且存取时间与信息在存 储器中的物理位置有关。如磁带存储器,信息 通常是以文件或数据块形式按顺序存放,信息 在载体上没有唯一对应的地址,完全按顺序存 放或读取。

• (4) 直接存取存储器(DAM)

2019/12/16

4

(2) 辅助存储器

• 为解决主存容量不足而设置的存储器, 用于存放当前不参加运行的程序和数据。 当需要运行程序和数据时,将它们成批 调入内存供CPU使用。CPU不能直接访问 辅助存储器。

• 辅助存储器属于外部设备,所以又称为 外存储器,简称外存或辅存。

2019/12/16

5

(3) 高速缓冲存储器(Cache)

• Cache是一种介于主存与CPU之间用于解 决CPU与主存间速度匹配问题的高速小容 量的存储器。

• Cache用于存放CPU立即要运行或刚使用 过的程序和数据。

2019/12/16

6

2.按存取方式分类

• (1) 随机存取存储器(RAM)

• RAM存储器中任何单元的内容均可按其地址随机地 读取或写入,且存取时间与单元的物理位置无关。

• 因为地址是用二进制进行编码的,所以又称为 地址码。

2019/12/16

21

• 存储单元的编址

• 编址单位:存储器中可寻址的最小单位。 • ① 按字节编址:相邻的两个单元是两个字节。 • ② 按字编址:相邻的两个单元是两个字。

• 例如一个32位字长的按字节寻址计算机,一个 存储器字中包含四个可单独寻址的字节单元。 当需要访问一个字,即同时访问4个字节时,可 以按地址的整数边界进行存取。即每个字的编 址中最低2位的二进制数必须是“00” ,这样 可以由地址的低两位来区分不同的字节。

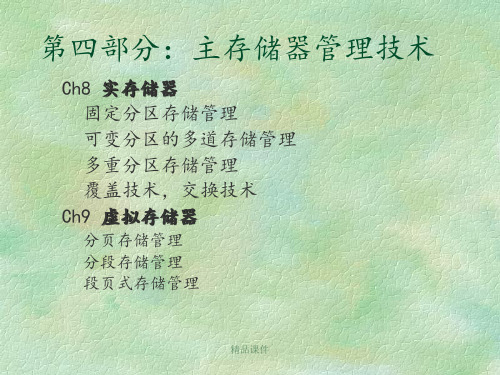

第四部分主存储器管理技术ppt课件

精品课件

①双表组织的可变分区数据库

UBT

FBT

区号 大小 位置 状态

区号 大小 位置

状态 1

8K

512K 已分 132K源自552K 自由 232K520K 已分 2 - - 空表目 3

-

-

空表目 3 520K 704K 自由 4

120K 584K 已分 4 - - 空表目 5

-

-

空表目 5 - - 空表目

状态:空表目,已分,自由

FBT 需要表格维护(排序:分区位置,分区大小); UBT不需表格维护(区号为存储保护键,不能随意变动)。

UNIX系统FBT:即主存可用资源表,50个表目,按地址排序, 采用最先适应法分配。

精品课件

②自由存储块链

每个自由存储块起始的若干字节分成两部分:

链指针next——指向下一个自由存储块的起始地址;最后一

动态重定位在指令执行过程中,每次访问内存前动态地

进行。从而程序可在主存中随意移动而不影响其正确执行, 可方便地进行存储器紧缩,较好地解决碎片问题。

128K

8K 2

未使用 584K

512K 32K 3

未使用

520K 32K 4

正使用

5

512K 精品课71件2K

正使用

存储分配算法

存储分配算法(固定分区,可变分区均适用):

最佳适应法,最先适应法,最坏适应法。

固定分区存储分配最佳方案:

最佳适应法和最先适应法的结合(MBT中各分区 按照分区大小排列,最小分区放在表头)。 存储保护和重定位:

特点:分区个数,分区大小均可变; 主存

中分布着个数,大小均是变化的自由分区或碎 片。

课题:如何管理已分配的和自由分区?

①双表组织的可变分区数据库

UBT

FBT

区号 大小 位置 状态

区号 大小 位置

状态 1

8K

512K 已分 132K源自552K 自由 232K520K 已分 2 - - 空表目 3

-

-

空表目 3 520K 704K 自由 4

120K 584K 已分 4 - - 空表目 5

-

-

空表目 5 - - 空表目

状态:空表目,已分,自由

FBT 需要表格维护(排序:分区位置,分区大小); UBT不需表格维护(区号为存储保护键,不能随意变动)。

UNIX系统FBT:即主存可用资源表,50个表目,按地址排序, 采用最先适应法分配。

精品课件

②自由存储块链

每个自由存储块起始的若干字节分成两部分:

链指针next——指向下一个自由存储块的起始地址;最后一

动态重定位在指令执行过程中,每次访问内存前动态地

进行。从而程序可在主存中随意移动而不影响其正确执行, 可方便地进行存储器紧缩,较好地解决碎片问题。

128K

8K 2

未使用 584K

512K 32K 3

未使用

520K 32K 4

正使用

5

512K 精品课71件2K

正使用

存储分配算法

存储分配算法(固定分区,可变分区均适用):

最佳适应法,最先适应法,最坏适应法。

固定分区存储分配最佳方案:

最佳适应法和最先适应法的结合(MBT中各分区 按照分区大小排列,最小分区放在表头)。 存储保护和重定位:

特点:分区个数,分区大小均可变; 主存

中分布着个数,大小均是变化的自由分区或碎 片。

课题:如何管理已分配的和自由分区?

计算机组成原理第四章ppt课件

EPROM是一种可擦除可编程只读存储器,用 户可以对其信息作任意次的改写。

采用紫外线进行擦除,擦除时间比较长(820分钟),但不能对个别需要改写的单元进行单 独擦除或重写。

可编辑课件PPT

36

2716 EPROM 的逻辑图和引脚

DO0 …

PD/Progr 控制逻辑

CS A10

数据缓冲区

……

…

…

Y 译码 A7 A6

X

译

码 A0

…

..

Y 控制

……

128 × 128

存储矩阵

… ………………

……………… ……

A7 1

24

A1 A0

DO0 DO1 DO2 VSS

2716 12 13

VCC A8 A9 VPP CS A10 PD/Progr DO7

DO3

PD/Progr 功率下降 / 编程输入端 读出时 为 低电平

可编辑课件PPT

5)与静态RAM比,集成度高,功耗低。

可编辑课件PPT

25

(1) 动态 RAM 基本单元电路

读选择线

T2

T1

T3 Cg

01

V DD

T4 预充电信号

10

无有电流 数据线

T

01

Cs

写选择线

字线

写数据线

读数据线

读出与原存信息相反

读出时数据线有电流 为 “1”

写入与输入信息相同 可编辑写课入件PP时T CS充电 为 “1” 放电 2为6 “0”

tC

刷新间隔 128 个读写周期

tC = tM + tR

无 “死区”

W/R REF

读写 刷新

可编(辑存课件取PPT周期为

采用紫外线进行擦除,擦除时间比较长(820分钟),但不能对个别需要改写的单元进行单 独擦除或重写。

可编辑课件PPT

36

2716 EPROM 的逻辑图和引脚

DO0 …

PD/Progr 控制逻辑

CS A10

数据缓冲区

……

…

…

Y 译码 A7 A6

X

译

码 A0

…

..

Y 控制

……

128 × 128

存储矩阵

… ………………

……………… ……

A7 1

24

A1 A0

DO0 DO1 DO2 VSS

2716 12 13

VCC A8 A9 VPP CS A10 PD/Progr DO7

DO3

PD/Progr 功率下降 / 编程输入端 读出时 为 低电平

可编辑课件PPT

5)与静态RAM比,集成度高,功耗低。

可编辑课件PPT

25

(1) 动态 RAM 基本单元电路

读选择线

T2

T1

T3 Cg

01

V DD

T4 预充电信号

10

无有电流 数据线

T

01

Cs

写选择线

字线

写数据线

读数据线

读出与原存信息相反

读出时数据线有电流 为 “1”

写入与输入信息相同 可编辑写课入件PP时T CS充电 为 “1” 放电 2为6 “0”

tC

刷新间隔 128 个读写周期

tC = tM + tR

无 “死区”

W/R REF

读写 刷新

可编(辑存课件取PPT周期为

计算机操作系统第4章存储器管理PPT课件

➢ 不支持多道程序

➢ 内存利用率不高

➢ 受内存容量限制

23

4.2.2 连续分区存储管理

➢ 将内存划分成若干个连续区域,称为分区 ➢ 每个分区只能存储一个程序,而且程序也只

能在它所驻留的分区中运行(连续性)

➢ 是实现多道程序的最简单的存储管理方案 ➢ 根据划定的分区是否可变,分为固定分区和

可变分区管理

编译/链接

地址映射

data1 3456

200

3456

1200

3456

15

三种装入方式

➢ 绝对装入

✓ 编译时给出绝对地址

✓ 相对地址与绝对地址相同,无须地址转换

✓ 适用于单道程序环境

➢ 静态重定位装入

✓ 相对地址与绝对地址不同

✓ 装入时一次性给出绝对地址

➢ 动态重定位装入

✓ 相对地址与绝对地址不同

✓ 地址的转换推迟到指令运行时才进行

24

1. 固定分区 ➢ 基本思想

✓ 由OS在初启时,将内存空间划分为若干连 续区域,一个区域称为一个分区

✓ 每个分区的大小固定不变,每个分区装一 个且只能装一个进程

✓ 每个分区大小可以相同也可以不同

25

➢ 数据结构 ✓ 分区说明表:分区号、起始地址、大小、状态 ✓ 分区请求表:进程号、内存大小

分区号 始址(K) 大小(K) 状态

要位置

➢ 任何一种存储装置,都无法同时从速度与

容量两方面,满足用户的需求

➢ 实际上它们组成了一个速度由快到慢,容

量由小到大的存储装置层次结构

5

存储器层次

存取时间减少

高速缓存

存取速度增加 存取成本增加

内存

存储容量减少

(精选)《主存储器》PPT课件

计算机组成原理

——第4章 主存储器

1

4.8 半导体存储器的组成与控制

1. 存储器容量扩展

位扩展 字扩展 字位扩展

2. 存储控制

集中刷新 分散刷新 异步刷新

3. 存储校验线路

2

复习(一)

❖RAM存储器芯片总结

RAM存储器芯片有多种型号,每一RAM存储器芯 片具有:

地址线Ai:引脚数与存储芯片的单元数有关; 数据线Di:引脚数与存储芯片的字长有关; 片选信号CS:只有CS有效时,芯片才被选中,

❖ 位扩展特点: 存储器的单元数不变,位数增加。

…

9

1、存储器容量扩展——字扩展

例3 使用16K×8位的RAM芯片组成一个 64K×8位的存储器。

分析: ①芯片的字数不够,需进行字扩展。 ②共需芯片数目是64K÷16K=4。将4片RAM的地 址线、数据线、读写线一一对应并联。 ③出现地址线不够问题,如何解决? 可以用高2位 地址作为选片端。 ④详细的连接见下图:

12

…

1、存储器容量扩展——字位扩展

❖ 实际存储器往往需要在字向、位向两个方向同时 扩展。

❖ 一个存储器的容量为M×N位,若使用L×K位的存 储芯片,则该存储器共需的芯片个数为:

M× N

L

K

❖ 需解决:芯片的选用、

…

地址分配与片选逻辑、

…

…

信号线的连接。 …

13

2114(1K×4)SRAM芯片组成容量为4K×8的存储器

10

16K×8位的RAM芯片组成一个64K×8位的存储器

10

地 CS

址 端

WE

地 CS

址 端

WE

地 CS

址 端

WE

——第4章 主存储器

1

4.8 半导体存储器的组成与控制

1. 存储器容量扩展

位扩展 字扩展 字位扩展

2. 存储控制

集中刷新 分散刷新 异步刷新

3. 存储校验线路

2

复习(一)

❖RAM存储器芯片总结

RAM存储器芯片有多种型号,每一RAM存储器芯 片具有:

地址线Ai:引脚数与存储芯片的单元数有关; 数据线Di:引脚数与存储芯片的字长有关; 片选信号CS:只有CS有效时,芯片才被选中,

❖ 位扩展特点: 存储器的单元数不变,位数增加。

…

9

1、存储器容量扩展——字扩展

例3 使用16K×8位的RAM芯片组成一个 64K×8位的存储器。

分析: ①芯片的字数不够,需进行字扩展。 ②共需芯片数目是64K÷16K=4。将4片RAM的地 址线、数据线、读写线一一对应并联。 ③出现地址线不够问题,如何解决? 可以用高2位 地址作为选片端。 ④详细的连接见下图:

12

…

1、存储器容量扩展——字位扩展

❖ 实际存储器往往需要在字向、位向两个方向同时 扩展。

❖ 一个存储器的容量为M×N位,若使用L×K位的存 储芯片,则该存储器共需的芯片个数为:

M× N

L

K

❖ 需解决:芯片的选用、

…

地址分配与片选逻辑、

…

…

信号线的连接。 …

13

2114(1K×4)SRAM芯片组成容量为4K×8的存储器

10

16K×8位的RAM芯片组成一个64K×8位的存储器

10

地 CS

址 端

WE

地 CS

址 端

WE

地 CS

址 端

WE

XIN第04章 主存储器与存储系统 4-2PPT课件

Y1

码

Y2

器

Y3

OE

2716

(2)

CE

OE

2716

(3)

CE

OE

2716

(4)

CE

15

部分译码法地址范围

芯片 #1 #2 #3 #4

A15 A14 A13 A12 A11 A10 …. A0

× × × 0 0 0 …. 0 × × × 0 0 1 …. 1

× × × 0 1 0 …. 0 × × × 0 1 1 …. 1

不同的片选方式对CPU剩余的5根地址线 的处理是不同的。

9

(1) 线选法

线选法是指利用地址总线的剩余高位地 址线直接作为存储器芯片的片选信号,低 位地址线和存储器地址线相连。用低位地 址线对每片内的存储单元进行寻址,所需 地址线由每片的单元数确定。

10

线选法扩展存储器容量

A10~A0

RD

CPU

A11 A12 A13 A14 D7~D0

(2)

OE I/O0 .. I/O7

18

全译码法地址范围

芯片 组1 组2

A19 A18 A17 A16 A15 A14 …. A0 0 0 0 0 0 0 …. 0 0 0 0 0 0 1 …. 1

0 0 0 0 1 0 …. 0 0 0 0 0 1 1 …. 1

地址范围

0000H~ 7FFFH

8000H~ FFFFH

计算机系统中, 存储器芯片与 CPU之间的连接, 读/写 实质上就是其与 数据总线、地址 总线和控制总线 三种系统总线的 连接。

CPU AR

k

DR n 地址总线

数据总线 控制总线

Ready

主存储器