逐次逼近型AD

逐次逼近型ADC

理解逐次逼近寄存器型ADC:与其它类型ADC 的架构对比Jul 02, 2009摘要:逐次逼近寄存器型(SAR)模数转换器(ADC)占据着大部分的中等至高分辨率ADC市场。

SAR ADC的采样速率最高可达5Msps,分辨率为8位至18位。

SAR架构允许高性能、低功耗ADC采用小尺寸封装,适合对尺寸要求严格的系统。

本文说明了SAR ADC的工作原理,采用二进制搜索算法,对输入信号进行转换。

本文还给出了SAR ADC的核心架构,即电容式DAC和高速比较器。

最后,对SAR架构与流水线、闪速型以及Σ-Δ ADC进行了对比。

引言SAR ADC的架构尽管实现SAR ADC的方式千差万别,但其基本结构非常简单(见图1)。

模拟输入电压(V IN)由采样/保持电路保持。

为实现二进制搜索算法,N位寄存器首先设置在中间刻度(即:100 (00)MSB设置为1)。

这样,DAC输出(V DAC)被设为V REF/2,V REF是提供给ADC的基准电压。

然后,比较判断V IN是小于还是大于V DAC。

如果V IN大于V DAC,则比较器输出逻辑高电平或1,N位寄存器的MSB保持为1。

相反,如果V IN小于V DAC,则比较器输出逻辑低电平,N位寄存器的MSB清0。

随后,SAR控制逻辑移至下一位,并将该位设置为高电平,进行下一次比较。

这个过程一直持续到LSB。

上述操作结束后,也就完成了转换,N位转换结果储存在寄存器内。

图1. 简单的N位SAR ADC架构图2给出了一个4位转换示例,y轴(和图中的粗线)表示DAC的输出电压。

本例中,第一次比较表明V IN < V DAC。

所以,位3置为0。

然后DAC被置为01002,并执行第二次比较。

由于V IN > V DAC,位2保持为1。

DAC置为01102,执行第三次比较。

根据比较结果,位1置0,DAC又设置为01012,执行最后一次比较。

最后,由于V IN > V DAC,位0确定为1。

结果表示逐次逼近型AD转换器原理框图

比较判断

8g<13g 12g<13g

砝码去留

留 留

结果表示

1 1

3

4

8g+4g+2g

8g+4g+1g

14g>13g

13g=13g

去

留

0

1

上页

下页

返回

第 7章

逐次逼近型A/D转换器原理框图

输出数字量

输 出 寄存器 节 拍 脉 冲 发 生 器 模拟信号输入 电 压 比 较 器

CP

逐次逼 近寄存器

D/A

拍 时钟 脉 脉冲 冲 发 生 器

C

C0 C1 C2 C3

0 • C3 • C 0

GND D9 D8 D7 D6 D5

4

5 6 7 8

RF UREF UDD D0 D1 D2 D3 D4

引脚功能 Iout1、Iout2:电流输出端 GND:接地端 D9~D0:数字信号输入端 UDD:电源输入端,5 ~ 10V

UREF:基准电源,–10V ~ +10V

RF:反馈信号输入端

CC7520 外部引脚图

上页

下页

返回

第 7章

CC7520 D/A转换器应用电路

UREF

15

UDD

14 16

D0 D1 D9 ……

13 12

CC7520

4 3

1

2

_ +

+

U0

UREF UO= – 210

(D9 29+D8 28+…+D121+D020)

上页 下页 返回

第 7章

程控三角波/方波发生器

AD转换

模拟电压输入 1LSB

模拟电压输入 1/2LSB

5

3、偏移误差

偏移误差是指输入信号为零时,输出信号不为零的 值,所以有时又称为零值误差。假定ADC没有非线 性误差,则其转换特性曲线各阶梯中点的连线必定 是直线,这条直线与横轴相交点所对应的输入电压 值就是偏移误差。

积分器输出

VIN

时钟

T1 T T2

t

3

三、A/D转换器的主要技术指标 1、分辨率 ADC的分辨率是指使输出数字量变化一个 相邻数码所需输入模拟电压的变化量。常用 二进制的位数表示。例如12位ADC的分辨率 就是12位,或者说分辨率为满刻度FS的 1/2 1 2 。一个10V满刻度的12位ADC能分辨输 入电压变化最小值是10V×1/ 2 1 2 =2.4mV。

ADC_CONTR寄存器

ADC_RES、 ADC_RESL寄存器

ADC中断控制寄存器

ADC典型应用电路

电压基准源

ADC实现按键输入功能

10VIN 20VIN AG

CE STS

-5V~+5V -10V~+10V

23

采用双极性输入方式,可对±5V或±10V的模拟信号

进行转换。当AD574A与80C31单片机配置时,由于 AD574A输出12位数据,所以当单片机读取转换结果 时,应分两次进行:当A0=0时,读取高8位;当A 0=1时,读取低4位。

需三组电源:+5V、VCC(+12V~+15V)、

VEE(-12V~-15V)。由于转换精度高,所 提供电源必须有良好的稳定性,并进行充分滤波, 以防止高频噪声的干扰。 低功耗:典型功耗为390mW。

AD 转换器概述

则 fs ≥ 2fimax

0

TG O(t)

S(t) S(t)=1:开关闭合 S(t)=0:开关断开

t

t

t

取样与保持电路及工作原理

采得模拟信号转换为数字信号都需要一定时间,为了给后续的量 化编码过程提供一个稳定的值,在取样电路后要求将所采样的模 拟信号保持一段时间。

I

A1

采样

S

A2

O

CH

开关驱 动电路

0 1 ·0 …· ·

0

数据寄存器

11 0…

···

0

Dn-1 1

Dn-2 0 数字

···

量输出 D1

D0

D/A 转换器

O 7.5V

• 转换原理 第三个CP:

A=6.84V

模拟 量输入

I

电压 比较器

I ≥6.25V 启

动 脉 冲

CP 时钟 控制逻 辑电路

VREF=10VVREF

移位寄位器

0 0 1·…· · 0

(2) 第一次积分:

S2

+I A S1

R

–VREF B

定 时

S

–

O

–

+

1

O

1

t 0

I

dt

1

VI T1

n 级计数器

+

C

C

信

F

1

FF

1

FF

1

FF

1

号 Q Fn 1J

Qn n-1 1J

Q 1 1J

0 1J

G

n

C < -1

1K R

C< 1K

R

1

C<

1K R

逐次逼近式AD转换原理

逐次逼近式AD转换原理逐次逼近式AD转换原理是一种常见的模拟信号转换为数字信号的方法,被广泛应用于数字信号处理、通信、仪器仪表和控制系统等领域。

该方法通过将模拟信号与一系列逐步增加或递减的参考电压进行比较,最终输出与模拟信号相对应的数字码。

下面将详细介绍逐次逼近式AD转换原理。

首先,模拟信号经过输入电路进入比较器。

比较器将模拟信号与DAC 输出的数字信号进行比较,判断两者的大小关系。

如果模拟信号大于DAC 输出的数字信号,则比较器输出高电平,否则输出低电平。

接下来,将比较器输出的电平信号进入一组逻辑电路,该逻辑电路根据比较器输出的高低电平信号,控制DAC输出电压的大小。

此时,DAC的输出电压与参考电压比较接近,但还不完全相等。

然后,将DAC输出的数字信号转换为模拟信号,通过反馈回路与模拟信号进行比较。

如果DAC输出的数字信号过小,则逻辑电路增加DAC的输入。

反之,如果DAC输出的数字信号过大,则逻辑电路减小DAC的输入。

通过逐步调整,DAC的输出电压逐渐逼近模拟信号大小。

最后,当DAC输出的数字信号与模拟信号足够接近时,逻辑电路停止对DAC输入的调整,DAC的输出被强制锁定。

此时,输出寄存器将DAC输出的数字码存储,即完成了模拟信号到数字信号的转换。

逐次逼近式AD转换器的工作原理是通过多次逼近逼近模拟信号的大小,以获取更高的转换精度。

其中,逼近的过程是通过比较器和逻辑电路的协同工作来实现的。

比较器用于比较模拟信号与DAC输出的数字信号的大小,并反馈给逻辑电路。

逻辑电路则根据比较器输出的高低电平信号,调整DAC的输入以逼近模拟信号。

然而,逐次逼近式AD转换器也存在一些缺点。

首先,由于需要多次逼近,转换速率相对较慢。

其次,由于逼近过程依赖于模拟信号的性质,因此对于非线性或非稳定信号,该转换器的精度可能受到影响。

此外,逐次逼近式AD转换器的精度也受限于比较器和DAC的性能。

总结起来,逐次逼近式AD转换原理是一种将模拟信号转换为数字信号的常见方法,通过比较器和逻辑电路的协同工作,逐步逼近模拟信号的大小,以获取更高的转换精度。

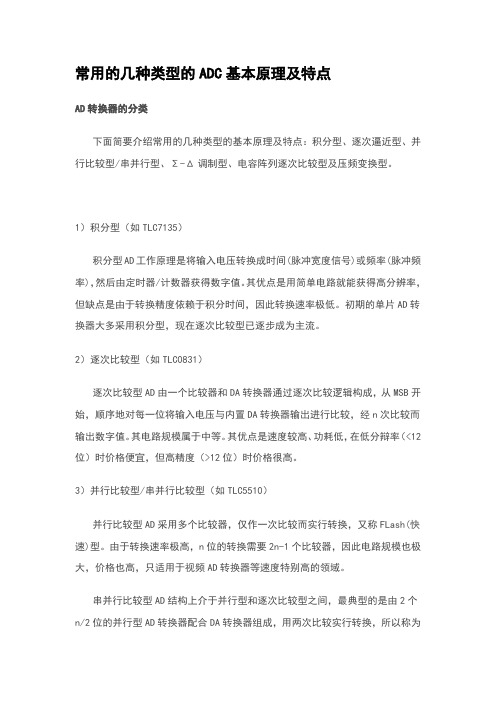

常用的几种类型的ADC基本原理及特点

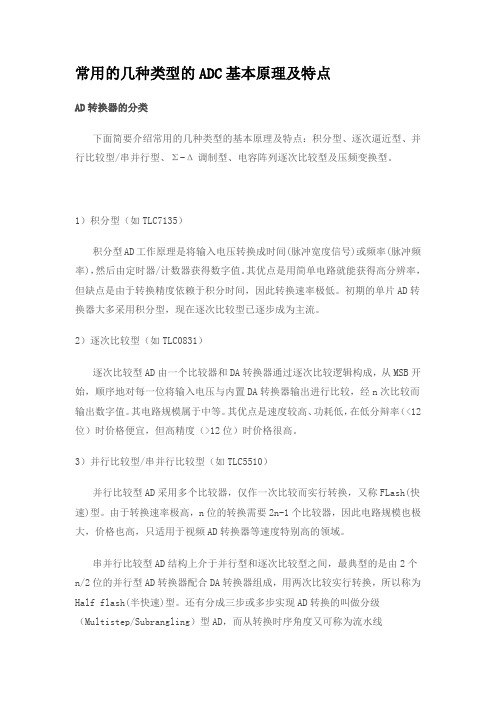

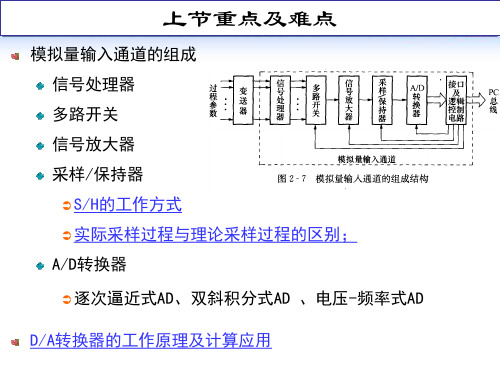

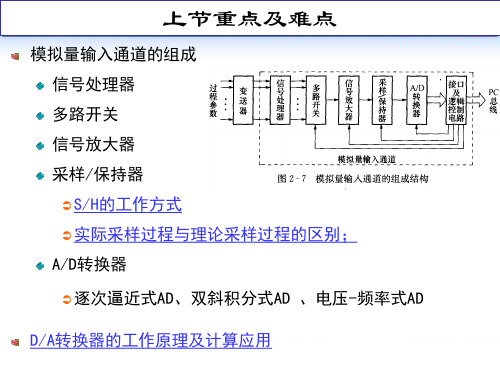

常用的几种类型的ADC基本原理及特点AD转换器的分类下面简要介绍常用的几种类型的基本原理及特点:积分型、逐次逼近型、并行比较型/串并行型、Σ-Δ调制型、电容阵列逐次比较型及压频变换型。

1)积分型(如TLC7135)积分型AD工作原理是将输入电压转换成时间(脉冲宽度信号)或频率(脉冲频率),然后由定时器/计数器获得数字值。

其优点是用简单电路就能获得高分辨率,但缺点是由于转换精度依赖于积分时间,因此转换速率极低。

初期的单片AD转换器大多采用积分型,现在逐次比较型已逐步成为主流。

2)逐次比较型(如TLC0831)逐次比较型AD由一个比较器和DA转换器通过逐次比较逻辑构成,从MSB开始,顺序地对每一位将输入电压与内置DA转换器输出进行比较,经n次比较而输出数字值。

其电路规模属于中等。

其优点是速度较高、功耗低,在低分辩率(<12位)时价格便宜,但高精度(>12位)时价格很高。

3)并行比较型/串并行比较型(如TLC5510)并行比较型AD采用多个比较器,仅作一次比较而实行转换,又称FLash(快速)型。

由于转换速率极高,n位的转换需要2n-1个比较器,因此电路规模也极大,价格也高,只适用于视频AD转换器等速度特别高的领域。

串并行比较型AD结构上介于并行型和逐次比较型之间,最典型的是由2个n/2位的并行型AD转换器配合DA转换器组成,用两次比较实行转换,所以称为Half flash(半快速)型。

还有分成三步或多步实现AD转换的叫做分级(Multistep/Subrangling)型AD,而从转换时序角度又可称为流水线(Pipelined)型AD,现代的分级型AD中还加入了对多次转换结果作数字运算而修正特性等功能。

这类AD速度比逐次比较型高,电路规模比并行型小。

4)Σ-Δ(Sigma?/FONT>delta)调制型(如AD7705)Σ-Δ型AD由积分器、比较器、1位DA转换器和数字滤波器等组成。

ADI实验室电路-16位、100kSPS逐次逼近型ADC系统

优势。

通常,选择高性能逐次逼近型ADC的驱动放大器处理宽范围的输入频

率。然而,当某个应用需要更低的采样速率时,便可节省大量功耗,因为降

低采样速率会相应地降低ADC功耗。

若要完全利用通过降低ADC采样速率使功耗下降的优势,则需要使用低

带宽、低功耗放大器。例如,推荐80MHz的ADA4841-1运算放大器(10V

AD7988-1是一款16位、100kSPSSARADC,其低功耗可随采样速率调整,

100kSPS时功耗为0.7mW。除了低功耗,它还具有业界领先的交流性能:

SNR=91dB,THD=-114dBc。

驱动放大器采用AD8641低功耗、精密器件,其电源电流为200μA,

增益带宽积为3MHz。AD8641可采用5V至26V的电源供电。ADC的基准

dBc)差不多。超过1kHz会加剧失真,因此不建议在更高的输入频率下使用

该电路,而由于较长的建立时间,亦不建议在多路复用器应用中使用该放大

器。注意,相对于正电源电压而言,AD8641需要至少2V的输入裕量。输

出级以轨到轨方式工作。

ADI实验室电路:16位、100kSPS逐次逼近型ADC

系统

AD7988-116位、100kSPSPulSARADC

AD8641R435超低噪声XFET5.0V基准电压源,具有吸电流和源电流能力

评估和设计支持

电路评估板

CN-0306电路评估板(EVAL-CN0306-SDPZ)

放大器(10V时功耗为2mW)可提供出色的信噪比(SNR)和总谐波失真

(THD)性能,并且在100kSPS时可将总系统功耗从17.35mW降低至7.35

ADC种类及参数选择

ADC的分类特性和参数选择尽管A/D转换器的种类很多,但目前广泛应用的主要有:逐次逼近式A/D转换器、双积分式A/D转换器、V/F变换式A/D转换器,新型的Σ-Δ型A/D转换器。

逐次逼近寄存器型(SAR)模拟数字转换器(ADC)是采样速率低于5Msps (每秒百万次采样)的中等至高分辨率应用的常见结构。

SAR ADC的分辨率一般为8位至16位,具有低功耗、小尺寸等特点。

这些特点使该类型ADC具有很宽的应用范围,例如便携/电池供电仪表、笔输入量化器、工业控制和数据/信号采集等。

顾名思义,SAR ADC实质上是实现一种二进制搜索算法。

所以,当内部电路运行在数兆赫兹(MHz)时,由于逐次逼近算法的缘故,ADC采样速率仅是该数值的几分之一。

SAR ADC的架构:尽管实现SAR ADC的方式千差万别,但其基本结构非常简单(见图1)。

模拟输入电压(VIN)由采样/保持电路保持。

为实现二进制搜索算法,N位寄存器首先设置在中间刻度(即:100... .00,MSB设置为1)。

这样,DAC输出(VDAC)被设为VREF/2,VREF是提供给ADC的基准电压。

然后,比较判断VIN是小于还是大于VDAC。

如果VIN大于VDAC,则比较器输出逻辑高电平或1,N位寄存器的MSB保持为1。

相反,如果VIN小于VDAC,则比较器输出逻辑低电平,N位寄存器的MSB清0。

随后,SAR控制逻辑移至下一位,并将该位设置为高电平,进行下一次比较。

这个过程一直持续到LSB。

上述操作结束后,也就完成了转换,N位转换结果储存在寄存器内。

图1. 简单的N位SAR ADC架构图2给出了一个4位转换示例,y轴(和图中的粗线)表示DAC的输出电压。

本例中,第一次比较表明VIN < VDAC。

所以,位3置为0。

然后DAC被置为01002,并执行第二次比较。

由于VIN > VDAC,位2保持为1。

DAC置为01102,执行第三次比较。

根据比较结果,位1置0,DAC又设置为01012,执行最后一次比较。

逐次逼近式ad转换原理

一、逐次逼近式AD转换器与计数式A/D转换类似,只是数字量由“逐次逼近寄存器SAR”产生。

SAR使用“对分搜索法”产生数字量,以8位数字量为例,SAR首先产生8位数字量的一半,即10000000B,试探模拟量Vi的大小,若Vo>Vi,清除最高位,若Vo<Vi,保留最高位。

在最高位确定后,SAR又以对分搜索法确定次高位,即以低7位的一半y1000000B(y为已确定位) 试探模拟量Vi的大小。

在bit6确定后,SAR以对分搜索法确定bit5位,即以低6位的一半yy100000B(y为已确定位) 试探模拟量的大小。

重复这一过程,直到最低位bit0被确定,转换结束。

转换过程:(1)首先发出“启动信号”信号S。

当S由高变低时,“逐次逼近寄存器SAR”清0,DAC输出Vo=0,“比较器”输出1。

当S变为高电平时,“控制电路”使SAR开始工作。

(2)SAR首先产生8位数字量的一半,即10000000B,试探模拟量的Vi大小,若Vo>Vi,“控制电路”清除最高位,若Vo<Vi,保留最高位。

(3)在最高位确定后,SAR又以对分搜索法确定次高位,即以低7位的一半y1000000B(y 为已确定位) 试探模拟量Vi的大小。

在bit6确定后,SAR以对分搜索法确定bit5位,即以低6位的一半yy100000B(y为已确定位) 试探模拟量Vi的大小。

重复这一过程,直到最低位bit0被确定。

(4)在最低位bit0确定后,转换结束,“控制电路”发出“转换结束”信号EOC。

该信号的下降沿把SAR的输出锁存在“缓冲寄存器”里,从而得到数字量输出。

从转换过程可以看出:启动信号为负脉冲有效。

转换结束信号为低电平。

我觉得,这有点像数学中的二分法,如给一个数a,先用8'b1000000(设为b)与a相比较,如果a大于b,则保留最高位1,即原来的范围变成了0-7'b1111111(第8位已确认)。

逐次逼近与积分AD区别

逐次逼近法逐次逼近式A/D是比较常见的一种A/D转换电路,转换的时间为微秒级。

其优点是速度较高、功耗低,在低分辩率(<12位)时价格便宜,但高精度(>12位)时价格很高。

采用逐次逼近法的A/D转换器是由一个比较器、D/A转换器、缓冲寄存器及控制逻辑电路组成,如图所示。

逐次逼近式AD转换器原理图基本原理是从高位到低位逐位试探比较,好像用天平称物体,从重到轻逐级增减砝码进行试探。

逐次逼近法转换过程是:初始化时将逐次逼近寄存器各位清零;转换开始时,先将逐次逼近寄存器最高位置1,送入D/A转换器,经D/A转换后生成的模拟量送入比较器,称为Vo,与送入比较器的待转换的模拟量Vi进行比较,若Vo<Vi,该位1被保留,否则被清除。

然后再置逐次逼近寄存器次高位为1,将寄存器中新的数字量送D/A转换器,输出的Vo再与Vi比较,若Vo<Vi,该位1被保留,否则被清除。

重复此过逐次逼近式A/D转换器原理图程,直至逼近寄存器最低位。

转换结束后,将逐次逼近寄存器中的数字量送入缓冲寄存器,得到数字量的输出。

逐次逼近的操作过程是在一个控制电路的控制下进行的。

积分法采用双积分法的A/D转换器由电子开关、积分器、比较器和控制逻辑等部件组成。

如下图所示。

基本原理是将输入电压变换成与其平均值成正比的时间间隔,再把此时双积分式AD转换器原理图间间隔转换成数字量,属于间接转换。

双积分法A/D转换的过程是:先将开关接通待转换的模拟量Vi,Vi采样输入到积分器,积分器从零开始进行固定时间T 的正向积分,时间T到后,开关再接通与Vi极性相反的基准电压VREF,将VREF输入到积分器,进行反向积分,直到输出为0V时停止积分。

Vi越大,积分器输出电压越大,反向积分时间也越长。

计数器在反向积分时间内所计的数值,就是输入模拟电压Vi所对应的数字量,实现了A/D转换。

积分式就是仪表盘上面的,电子秤上面的,低速,稳定,精度高。

双积分式AD转换原理图。

2.3 逐次逼近式AD与双积分AD解析

(010…0)小,即必在001…1——000…0之间,此时 反馈比较, 次高位应为0; 确定1/4搜索范围 若U ≥U ,说明模拟量输入电压比寄存器输出的数码

IN F

(010…0)大,即必在011…1 ——010…0之间,此时

次高位应为1 ;

解:U OUT U REF 解:U OUT U REF

D 1 1 1 1 1 1 10 ( 1 1 0 0 ) 10 ( 0 0) 7.25V 2n 2 22 23 24 2 4 D 1 1 1 1 1 1 1 10 ( 1 1 1 0 ) 10 ( 0) 8.75V 2n 2 22 23 24 2 4 8

《计算机控制系统》 第二章 过程通道

D/A转换器工作原理

对 n 位D/A转换器而言,当输 入数字量为 D=Dn-1…D1D0 时, 其输出电压为

U OUT

沈阳工程学院动力系 崔长春

U REF D n 1 1 0 ( D 2 D 2 D 2 ) U n -1 1 0 REF n 2n 2

《计算机控制系统》 第二章 过程通道

沈阳工程学院动力系 崔长春

自编2-2:四位D/A转换器,基准电压为10V,当输入数 字量D为1001时,其输出的模拟量为多少? (作业)

解:U OUT U REF

D 2n

1 1 1 1 10 (1 0 2 0 3 1 4 ) 2 2 2 2 1 1 10 ( 0 0 ) 2 16 5.625V

沈阳工程学院动力系 崔长春

1、S/H的作用 在采样时刻,采集过程变量; 保持A/D的输入值在转换时间内不变;

常用的几种类型的ADC基本原理及特点

常用的几种类型的ADC基本原理及特点AD转换器的分类下面简要介绍常用的几种类型的基本原理及特点:积分型、逐次逼近型、并行比较型/串并行型、Σ-Δ调制型、电容阵列逐次比较型及压频变换型。

1)积分型(如TLC7135)积分型AD工作原理是将输入电压转换成时间(脉冲宽度信号)或频率(脉冲频率),然后由定时器/计数器获得数字值。

其优点是用简单电路就能获得高分辨率,但缺点是由于转换精度依赖于积分时间,因此转换速率极低。

初期的单片AD转换器大多采用积分型,现在逐次比较型已逐步成为主流。

2)逐次比较型(如TLC0831)逐次比较型AD由一个比较器和DA转换器通过逐次比较逻辑构成,从MSB开始,顺序地对每一位将输入电压与内置DA转换器输出进行比较,经n次比较而输出数字值。

其电路规模属于中等。

其优点是速度较高、功耗低,在低分辩率(<12位)时价格便宜,但高精度(>12位)时价格很高。

3)并行比较型/串并行比较型(如TLC5510)并行比较型AD采用多个比较器,仅作一次比较而实行转换,又称FLash(快速)型。

由于转换速率极高,n位的转换需要2n-1个比较器,因此电路规模也极大,价格也高,只适用于视频AD转换器等速度特别高的领域。

串并行比较型AD结构上介于并行型和逐次比较型之间,最典型的是由2个n/2位的并行型AD转换器配合DA转换器组成,用两次比较实行转换,所以称为Half flash(半快速)型。

还有分成三步或多步实现AD转换的叫做分级(Multistep/Subrangling)型AD,而从转换时序角度又可称为流水线(Pipelined)型AD,现代的分级型AD中还加入了对多次转换结果作数字运算而修正特性等功能。

这类AD速度比逐次比较型高,电路规模比并行型小。

4)Σ-Δ(Sigma/FONT>del ta)调制型(如AD7705)Σ-Δ型AD由积分器、比较器、1位DA转换器和数字滤波器等组成。

逐次逼近式AD与双积分AD

1.设D4 1, D 10000 则U f 10 (1 0 0 0

2.设D3 1, D 01000

3.设D2 1, D 01100

4.设D1 1, D 01110

1 2 1 4 1 8 1 1 0 ) 5V 4.7V 16 32

同理,当假设已确定最高位 《计算机控制系统》 第二章 过程通道

沈阳工程学院动力系 崔长春

Dn-1=1时:

③确定次高位 Ⅰ)设定SAR中的次高位为“1”, 其余位为“0”,即D=110…0, 送往D/A转换成电压UF;

则 U F U REF (1 1 1 1 1 3 1 2 0 3 0 n ) U REF 2 2 2 2 4 找出了第二个中间值

则D1 1

1 1 则Vf 10 ( 0 0) 7.5V Vi 则D2 0 2.设D2 1, D 1100 2 4 1 1 3.设D3 1, D 1010 则Vf 10 ( 0 0) 6.25V Vi 则D3 0 2 8

4.设D4 1, D 1001 则Vf 10 ( 1 0 0 1 ) 5.625V Vi

2 16

则D 4 1

∴D=1001,这里误差为0.375v

《计算机控制系统》 第二章 过程通道

沈阳工程学院动力系 崔长春

自编2-3:4位逐位逼近式A/D转换器,满量程为10V,

3、电压-频率式A/D

模拟信号→频率F →数字量; 接口电路简单,转换速率较慢,精度较高; 适合远距离的数据传送。

《计算机控制系统》 第二章 过程通道 1、逐位逼近式A/D

逐次逼近型AD原理及应用

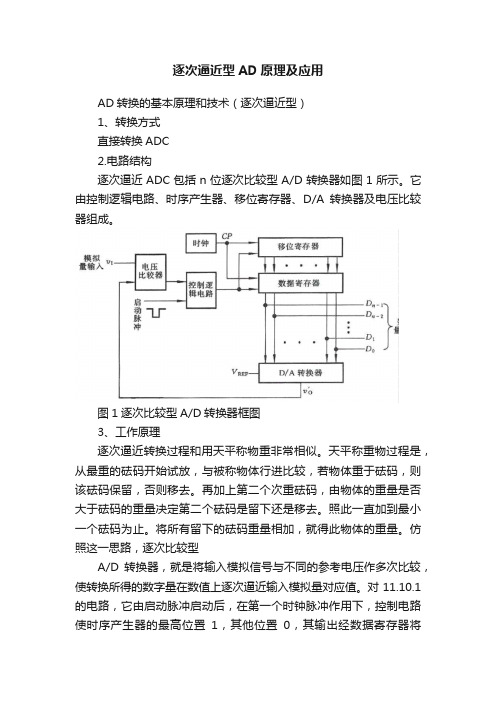

逐次逼近型AD原理及应用AD转换的基本原理和技术(逐次逼近型)1、转换方式直接转换ADC2.电路结构逐次逼近ADC包括n位逐次比较型A/D转换器如图1所示。

它由控制逻辑电路、时序产生器、移位寄存器、D/A转换器及电压比较器组成。

图1逐次比较型A/D转换器框图3、工作原理逐次逼近转换过程和用天平称物重非常相似。

天平称重物过程是,从最重的砝码开始试放,与被称物体行进比较,若物体重于砝码,则该砝码保留,否则移去。

再加上第二个次重砝码,由物体的重量是否大于砝码的重量决定第二个砝码是留下还是移去。

照此一直加到最小一个砝码为止。

将所有留下的砝码重量相加,就得此物体的重量。

仿照这一思路,逐次比较型A/D转换器,就是将输入模拟信号与不同的参考电压作多次比较,使转换所得的数字量在数值上逐次逼近输入模拟量对应值。

对11.10.1的电路,它由启动脉冲启动后,在第一个时钟脉冲作用下,控制电路使时序产生器的最高位置1,其他位置0,其输出经数据寄存器将1000……0,送入D/A转换器。

输入电压首先与D/A器输出电压(VREF/2)相比较,如v1≥VREF/2,比较器输出为1,若vI 设图11.10.1电路为8位A/D转换器,输入模拟量vA=6.84V,D/A转换器基准电压VREF=10V。

根据逐次比较D/A转换器的工作原理,可画出在转换过程中CP、启动脉冲、D7~D0及D/A转换器输出电压vO的波形,如图11.10.2所示。

由图11.10.2可见,当启动脉冲低电平到来后转换开始,在第一个CP作用下,数据寄存器将D7~D0=10000000送入D/A转换器,其输出电压v0=5V,vA与v0比较,vA>v0存1;第二个CP到来时,寄存器输出D7~D0=11000000,v0为7.5V,vA再与7.5V比较,因vA<7.5V,所以D6存0;输入第三个CP时,D7~D0=10100000,v0=6.25V;vA再与v0比较,……如此重复比较下去,经8个时钟周期,转换结束。

ADC种类及参数选择

ADC的分类特性和参数选择尽管A/D转换器的种类很多,但目前广泛应用的主要有:逐次逼近式A/D转换器、双积分式A/D转换器、V/F变换式A/D转换器,新型的Σ-Δ型A/D转换器。

逐次逼近寄存器型(SAR)模拟数字转换器(ADC)是采样速率低于5Msps (每秒百万次采样)的中等至高分辨率应用的常见结构。

SAR ADC的分辨率一般为8位至16位,具有低功耗、小尺寸等特点。

这些特点使该类型ADC具有很宽的应用范围,例如便携/电池供电仪表、笔输入量化器、工业控制和数据/信号采集等。

顾名思义,SAR ADC实质上是实现一种二进制搜索算法。

所以,当内部电路运行在数兆赫兹(MHz)时,由于逐次逼近算法的缘故,ADC采样速率仅是该数值的几分之一。

SAR ADC的架构:尽管实现SAR ADC的方式千差万别,但其基本结构非常简单(见图1)。

模拟输入电压(VIN)由采样/保持电路保持。

为实现二进制搜索算法,N位寄存器首先设置在中间刻度(即:100... .00,MSB设置为1)。

这样,DAC输出(VDAC)被设为VREF/2,VREF是提供给ADC的基准电压。

然后,比较判断VIN是小于还是大于VDAC。

如果VIN大于VDAC,则比较器输出逻辑高电平或1,N位寄存器的MSB保持为1。

相反,如果VIN小于VDAC,则比较器输出逻辑低电平,N位寄存器的MSB清0。

随后,SAR控制逻辑移至下一位,并将该位设置为高电平,进行下一次比较。

这个过程一直持续到LSB。

上述操作结束后,也就完成了转换,N位转换结果储存在寄存器内。

图1. 简单的N位SAR ADC架构图2给出了一个4位转换示例,y轴(和图中的粗线)表示DAC的输出电压。

本例中,第一次比较表明VIN < VDAC。

所以,位3置为0。

然后DAC被置为01002,并执行第二次比较。

由于VIN > VDAC,位2保持为1。

DAC置为01102,执行第三次比较。

根据比较结果,位1置0,DAC又设置为01012,执行最后一次比较。

AD7980

AD7980

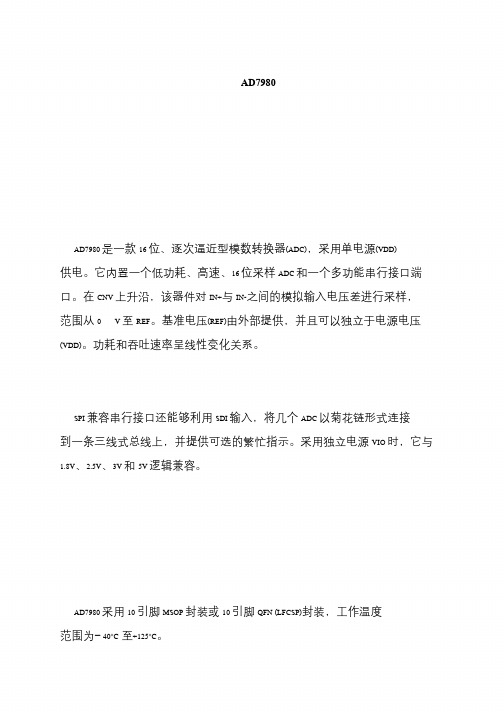

AD7980 是一款16 位、逐次逼近型模数转换器(ADC),采用单电源(VDD) 供电。

它内置一个低功耗、高速、16 位采样ADC 和一个多功能串行接口端口。

在CNV 上升沿,该器件对IN+与IN-之间的模拟输入电压差进行采样,

范围从0 V 至REF。

基准电压(REF)由外部提供,并且可以独立于电源电压(VDD)。

功耗和吞吐速率呈线性变化关系。

SPI 兼容串行接口还能够利用SDI 输入,将几个ADC 以菊花链形式连接

到一条三线式总线上,并提供可选的繁忙指示。

采用独立电源VIO 时,它与1.8V、2.5V、3V 和5V 逻辑兼容。

AD7980 采用10 引脚MSOP 封装或10 引脚QFN (LFCSP)封装,工作温度范围为−40°C至+125°C。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

逐次逼近型AD

————————————————————————————————作者:————————————————————————————————日期:

逐次逼近型ADC

其工作原理可用天平秤重过程作比喻来说明。

若有四个砝码共重15克,每个重量分别为8、4、2、1克。

设待秤重量Wx = 13克,可以用下表步骤来秤量:

首先把待称重的重物放在托盘上,在另外一边的托盘上首先放上8克的砝码,8克砝码小于待测物体总重13克,所以保留该砝码;

第二步将4克砝码放在托盘上,砝码总重为8+4=12克,小于待测物体总重,所以也保留;

第三步将2克砝码放在托盘上,砝码总重为8+4+2=14克,大于待测物体总重,所以将2克砝码撤除;

第四步将1克砝码放在托盘上,砝码总重为13克,等于待测物体总重,所以保留;

最后得到待测物体为13克。

AD的转换过程与上述过程类似,每次加载砝码的过程受到一个时钟

脉冲CP的控制,在AD中不存在砝码,而是采用DA转换器的输出做为上面例子中砝码的重量,而比较器就是天平。

其工作流程框图如下图所示:

今以四位逐次逼近型ADC为例(设输入电压Ux=5.52 V,D/A转换器的参考电压UR=-8 V),分析其转换过程。

第一个脉冲CP到来时,使逐次逼近寄存器的最高位d3置1,其余位为0,即寄存器状态d3d2d1d0=1000,由式(9.4.1)得D/A转换器的输出电压为

因Uo<Ux,故比较器输出低电平,d3位置的1被保留。

第二个脉冲CP到来时,使逐次逼近寄存器的次高位d2置1,后两位为0,即寄存器状态d3d2d1d0=1100,此时D/A转换器的输出电压

Uo=8/16×12=6 V,因Uo>Ux,故比较器输出高电平,d2位置的1被取消变为0。

第三个脉冲CP到来时,d1置1,此时寄存器状态d3d2d1d0=1010,D/A转换器的输出电压Uo=8/16×10=5 V,因Uo<Ux,故比较器输出低电平,d1位置的1被保留。

第四个脉冲CP到来时,d0置1,此时寄存器状态d3d2d1d0=1011,D/A转换器的输出电压Uo=8/16×11=5.5 V,因Uo<Ux,故比较器输出低电平,d0位置的1被保留。

这样,经过四个脉冲就完成了一次转换,将输入的5.52 V模拟电压转换为数字量1011。

上例中转换误差为0.02 V。

误差取决于转换器的位数,位数越多,误差越小。