单片机扩展芯片8243的中文资料

STM8S103F2P6

4.10 TIM1 — 16位高级控制定时器............................................................................................11

4.11

TIM2 — 16位通用定时器...................................................................................................11

6 存储器和寄存器映像................................................................................................19

6.1

存储器映像 ........................................................................................................................19

21个高吸收电流输出 非常强健的I/O设计,对倒灌电流有非常

强的承受能力

开发支持 单线接口模块(SWIM)和调试模块(DM),

可以方便地进行在线编程和非侵入式调 试

本文档英文原文下载地址: /stonline/products/literature/ds/15441.pdf

参照2009年6月 STM8S103x 数据手册英文第3版 本译文仅供参考,如有翻译错误,请以英文原稿为准。请读者随时注意在ST网站下载更新版本

目录

STM8S103xx数据手册

目录

1 简介...........................................................................................................................4

P8242AH资料

Y

Fully Compatible with all Intel and Most Other Microprocessor Families Interchangeable ROM and OTP EPROM Versions Expandable I O Sync Mode Available Over 90 Instructions 70% Single Byte Available in EXPRESS Standard Temperature Range inteligent Programming Algorithm Fast OTP Programming Available in 40-Lead Plastic and 44Lead Plastic Leaded Chip Carrier Packages

Contact factory for current code revision available in all versions of the 8242 product lines

2

元器件交易网

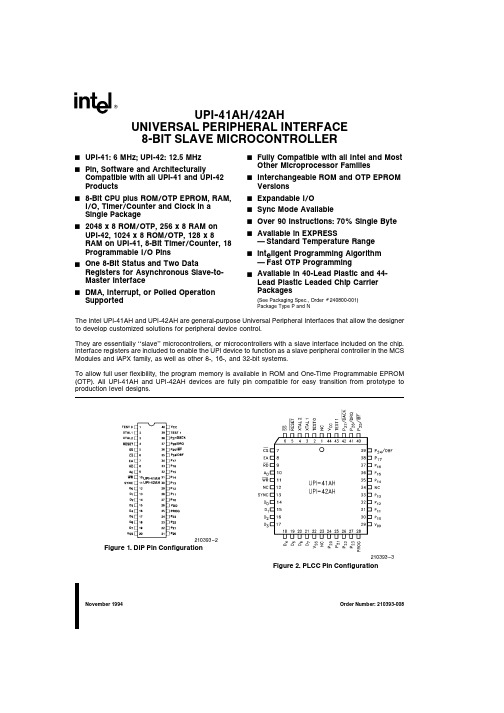

UPI-41AH 42AH

Table 1 Pin Description

210393 – 2

Figure 1 DIP Pin Configuration

210393 – 3

Figure 2 PLCC Pin Configuration

November 1994

Order Number 210393-008

元器件交易网

UPI-41AH 42AH

Symbol DIP Pin No 1 39 PLCC Pin Type No 2 43 I Name and Function

TEST 0 TEST 1

0832芯片

w

w

w

A0 ~ A9

地 port1 址 译 port2 码

f

p

.

CS

VREF

-5V

-10V

10V

XFER DGND

例2

利用上例连线图,编程输出一锯齿波.

Vo 4V

w

0V

.

f

p

g

a -

a

r m

w

w

t

21

w

start: MOV MOV next: MOV OUT MOV OUT CALL INC CMP JNZ MOV LOOP

.

2)双缓冲工作方式

f

p

g

a -

1)单缓冲工作方式

a

8

r m

一个工作于受控锁存器状态

在不要求多相D/A同时输出时,可以采用单缓冲方式,

w

w

可以提高D/A的数据吞吐量.

w

此时只需一次写操作,就开始转换,

.

f

p

g

a -

一个寄存器工作于直通状态,

a

9

r m

1)单缓冲工作方式 :

a -

a

D0 ~ D7 +5V IOW A0 ~ A9

CX, 8000H AL, 0 DX, port1 DX, AL DX, port2 DX, AL delay AL AL, 0CEH next AL, 0 next

a -

4V 0V

;锯齿谷值 ;打开第一级锁存 ;打开第二级锁存

a

Vo

;波形个数

MOV AH, 4CH INT 21H ;子程delay (略) code ENDS END start

CXP82432A资料

DescriptionThe CXP82432A/82440A is a CMOS 8-bit single chip microcomputer integrating on a single chip an A/D converter, serial interface, timer/counter, time base timer, capture timer counter, fluorescent display tube controller/driver, remote control reception circuit,CTL duty detection circuit, 14-bit PWM output and high-speed output circuit besides the basic configurations of 8-bit CPU, ROM, RAM, and I/O port.The CXP82432A/82440A also provides sleep/stop function that enables lower power consumption.Features•Wide-range instruction system (213 instructions) to cover various types of data —16-bit arithmetic/multiplication and division/boolean bit operation instructions •Minimum instruction cycle 400ns at 10MHz operation(122µs at 32kHz operation)•Incorporated ROM capacity 32K bytes (CXP82432A)40K bytes (CXP82440A)•Incorporated RAM capacity 1120 bytes (including fluorescent display area)•Peripheral functions — A/D converter 8-bit, 8-channel, successive approximation method(Conversion time of 32µs/10MHz)— Serial interface 8-bit, 8-stage FIFO incorporated(Auto transfer for 1 to 8 bytes), 1 channel 8-bit clock synchronized type, 1 channel— Timers 8-bit timer, 8-bit timer/counter, 19-bit time base timer16-bit capture timer/counter, 32kHz timer/counter— Fluorescent display tube controller/driver Maximum of 384 segments display possible1 to 16-digit dynamic display Dimmer functionHigh voltage drive output (40V)Incorporated pull-down resistor (Mask option)Hardware key scan functionMaximum of 16 x 8 key matrix compatible— Remote control reception circuit Incorporated noise elimination circuit8-bit pulse measuring counter, 6-stage FIFO— PWM output circuit 14 bits, 1 channel — CTL duty detection circuit — High-speed output circuit Precision of 800ns at 10MHz, 4 outputs •Interruption 19 factors, 15 vectors, multi-interruption possible •Standby mode SLEEP/STOP •Package 100-pin plastic QFP •Piggyback/evaluation chip CXP82400A 100-pin ceramic QFP– 1–CXP82432A/82440AE94Z15-PPCMOS 8-bit Single Chip MicrocomputerSony reserves the right to change products and specifications without prior notice. This information does not convey any license byany implication or otherwise under any patents or other right. Application circuits shown, if any, are typical examples illustrating the operation of the devices. Sony cannot assume responsibility for any problems arising out of the use of these circuits.StructureSilicon gate CMOS IC– 2–CXP82432A/82440AB l o c k D i a g r a mP E 2/I N T 2P E 3/I N T 3/N M IP A 0/A N 0 t o P A 7/A N 7A 0 t o P A 7R S TV D D V S S B 0 t o P B 6C 0 t o P C 7D 0 t o P D 7E 0 t o P E 5F 0 t o P F 7G 0 t o P G 7H 0 t o P H 7E 6 t o P E 7T E X E X T A L X T A L T X A V R E FA V S ST 0 t o T 7T 15/S 24 t o T 8/S 31P D 0/S 0 t o P I 7/S 23V F D PP E 5/C T L P E 4/R M C P B 3/S I 0P B 4/S O 0P B 6/S I 1P B 7/S O 1P B 5/S C K 1P E 0/I N T 0/E C 0P E 7/T O P B 0/C I N T P E 1/I N T 2/E C 1P B 1/C S 0P B 2/S C K 0B 7I 0 t o P I 7P G 0/R T O 0 t o P G 3/R T O 3P E 0/E C 0/I N T 0P E 1/E C 1/I N T 1P E 6/P W MP E 7/D D OP E 7/A D JCXP82432A/82440A Pin Assignment(Top View)PE1/EC1/INT1PE2/INT2 PE3/INT3/NMIPE4/RMCPE5/CTLPE6/PWM PE7/TO/DDO/ADJPB0/CINTPB1/CS0PB2/SCK0PB3/SI0PB4/SO0PB5/SCK1PB6/SI1PB7/SO1PC0/KR0PC1/KR1PC2/KR2PC3/KR3PC4/KR4PC5/KR5PC6/KR6PC7/KR7PH0PH1PH2PH3PH4PH5PH6T7T8/S31T9/S30T10/S29T11/S28T12/S27T13/S26T14/S25T15/S24PI7/S23PI6/S22PI5/S21PI4/S20PI3/S19PI2/S18PI1/S17PI0/S16PF7/S15PF6/S14PF5/S13PF4/S12PF3/S11PF2/S10PF1/S9PF0/S8PD7/S7PD6/S6PD5/S5PD4/S4PD3/S3 PH7PA/ANPA1/AN1PA2/AN2PA3/AN3PA4/AN4PA5/AN5RSTEXTALXTALVssTXTEXPA6/AN6PA7/AN7AVREFAVssPD/SPD1/S1PD2/S2 PE/EC/INTPG7PG6PG5PG4PG3/RTO3PG2/RTO2PG1/RTO1PG/RTOVssNCVDDVFDPTT1T2T3T4T5T6Note) 1.NC (Pin 90) must be connected to V DD.2.Vss (Pins 41 and 91) must be connected to GND.– 3–– 4–CXP82432A/82440APin DescriptionPin code I/OFunctionsI/O/Analog inputPA0/AN0to PA7/AN7(Port A)8-bit I/O port. I/O can be set in single bit units.(8pins)Analog inputs to A/D converter. (8 pins)I/O/InputPC0/KR0to PC7/KR7PE0/INT0/EC0PE1/INT1/EC1PE2/INT2PE3/INT3/NMI PE4/RMC PE5/CTL PE6/PWM PE7/TO/DDO/ADJ PF0/S8to PF7/S15PG0/RTO0toPG3/RTO3PG4 to PG7Input/Input/Input Input/Input/Input Input/Input Input/Input/Input Input/Input Input/Input Output/Output Output/Output/Output/OutputOutput/OutputI/O/OutputI/O(Port C)8-bit I/O port. I/O canbe set in a unit of singlebits. Capable of driving 12mA sync current.Serves as key return inputs when operatingkey scan with FDP segment signal.Output/OutputPD0/S0to PD7/S7(Port D)8-bit output port. (8 pins)FDP segment signal outputs.(Port E)8-bit port. Lower 6 bits are for inputs; upper 2 bits are for outputs.(8 pins)(Port F)8-bit output port.(8pins)(Port G)8-bit I/O port. I/O can be set in a unit of single bits. Data for the lower 4 bits are gated with thecontents of RTO or OR-gate output. (8 pins)External event inputs for timer/counter.(2 pins)Inputs for external interruption request.(4 pins)Non-maskable interruption request input.Remote control reception circuit input.Input for CTL duty direction circuit.14-bit PWM output.Output for the 16-bit timer/counter rectangular waves, CTU duty detection, and 32kHz oscillation frequency demultiplication.FDP segment signal outputs.Outputs for real-time pulse generator (RTG).Functions as high-precision, real-time pulse output port.(4 pins)I/O/Input I/O/Input I/O/I/O I/O/Input I/O/Output I/O/I/O I/O/Input Output/OutputPB0/CINT PB1/CS0PB2/SCK0PB3/SI0PB4/SO0PB5/SCK1PB6/SI1PB7/SO1(Port B)8-bit I/O port. I/O for lower 7 bits can be set in a unit of single bits.Uppermost bit (PB7) is for output only.(8 pins)Capture input to 16-bit timer/counter.Chip select input for serial interface (CH0).Serial clock I/O (CH0).Serial data input (CH0).Serial data output (CH0).Serial clock I/O (CH1).Serial data input (CH1).Serial data output (CH1).– 5–CXP82432A/82440APin code I/O FunctionsOutput/OutputPI0/S16to PI7/S23(Port I)8-bit output ports.(8 pins)FDP segment signal outputs.Output/Output T8/S31to T15/S24Outputs for FDP timing (digit) signals/segment signals.I/OPH0 to PH7(Port H)8-bit I/O port. I/O can be set in a unit of single bits.(8 pins)V FDP EXTAL XTAL TEX TX RST NC AV REF AV SS V DD V SSInput Output Input Output InputInput FDP voltage supply when incorporated resistor is set by mask option.T0 to T7FDP timing signal outputs.Crystal connectors system clock oscillation. When the clock is supplied externally, input to EXTAL; opposite phase clock should be input to XTAL.Crystal connectors for 32kHz timer/counter clock oscillation. Set 32kHz crystal oscillator between TEX and TX. For usage as event input, attach clock source to TEX, and open TX.Low-level active, system reset.NC. Under normal operation, connect to V DD .Reference voltage input for A/D converter.A/D converter GND.Vcc supply.GND.OutputCXP82432A/82440A I/O Circuit Format for Pins– 6–CXP82432A/82440A– 7–CXP82432A/82440A– 8–CXP82432A/82440A– 9–– 10–CXP82432A/82440A∗1)V IN and V OUT must not exceed V DD + 0.3V.∗2)Specifies output current of general-purpose I/O ports.∗3)The high current drive transistor is the N-CH transistor of Port C (PC).Note)Usage exceeding absolute maximum ratings may permanently impair the LSI. Normal operation should beconducted under the recommended operating conditions. Exceeding these conditions may adversely affect the reliability of the LSI.Supply voltage Input voltage Output voltage Display output voltageHigh level output currentHigh level total output currentLow level output currentLow level total output current Operating temperature Storage temperatureAllowable power dissipation V DD AVss V IN V OUT V OD I OHI ODH1I ODH2∑I OH ∑I ODH I OL I OLC∑I OL Topr TstgP D–0.3 to +7.0–0.3 to +0.3–0.3 to +7.0∗1–0.3 to +7.0∗1V DD –40 to V DD +0.3–5–15–35–40–1001520100–20 to +75–55 to +150600V V V V V mA mA mA mA mA mA mA mA °C °C mWAs P channel transistor is open drain, V DD is reference.All pins excluding outputs ∗2(value per pin)Display outputs S0 to S23 (value per pin)Display outputs T0 to T7, and T8/S31 to T15/S24 (value per pin)Total for all pins excluding display outputs Total for all display outputs Port 1High current Port 1∗3Total for all output pinsItemSymbol Rating Unit RemarksAbsolute Maximum Ratings(Vss = 0V reference)High level input voltageLow level input voltageOperating temperatureSupply voltage 5.55.55.55.5V DD V DDV DD + 0.30.3V DD 0.2V DD 0.4+75V V V V V V V V V V °CItemSymbolMin.Max.Unit Remarks4.53.52.72.50.7V DD 0.8V DDV DD – 0.400–0.3–20V IHV IHS V IHEX V ILV ILS V ILEX ToprHigh-speed modeGuaranteed operation range Low-speed modeGuaranteed operation rangeGuaranteed operation range with TEX clockGuaranteed data hold range during STOP ∗1Hysteresis input ∗2EXTAL ∗3∗1Hysteresis input ∗2EXTAL ∗3V DD∗1)Value for each pin of normal input port (PA, PB4, PC, PG, PH).∗2)Value of the following pins: RST, CINT, CS0, SCK0, SCK1, SI0, SI1, EC0/INT0, EC1/INT1, INT2,INT3/NMI, RMC, CTL.∗3)Specifies only during external clock input.Recommended Operating Conditions(Vss = 0V reference)V DD = 4.5V, I OH = –0.5mA V DD = 4.5V, I OH = –1.2mA V DD = 4.5V, I OL = 1.8mA V DD = 4.5V, I OL = 3.6mA V DD = 4.5V, I OL = 12.0mA V DD = 5.5V, V IH = 5.5V V DD = 5.5V, V IL = 0.4V V DD = 5.5V, V IH = 5.5V V DD = 5.5V V IL = 0.4VV DD = 4.5VV OH = V DD – 2.5VV DD = 5.5VV OL = V DD – 35V V FDP = V DD – 35V V DD = 5VV FDP = V DD – 35VV DD = 5.5VV I = 0, 5.5VHigh level output current Display output current4.03.50.5–0.50.1–0.1–1.5–8–2060V V V V V µA µA µA µA µA mA mAµAk ΩµAPCPA, PB,PC, PE6,PE7, PG,PH EXTAL TEX RST ∗1Item Symbol Pins ConditionsMin.S0 to S23S24/T15 to S31/T8T0 to T7S0 to S23S24/T15 to S31/T8T0 to T7S0 to S23S24/T15 to S31/T8T0 to T7PA to PCPE, PG, PH,RST ∗1I OHOpen drain output leakage current(P-CH Tr off state)I LOLPull-down resistance ∗2I/Oleakage currentR L I IZV OHV OLI IHE I ILEI IHT I ILT I ILRLow leveloutput currentInput current100Typ.0.40.61.540–4010–10–400–20270±10Max.Unit DC CharacteristicsElectrical Characteristics (Ta = –20 to +75°C, Vss = 0V reference)∗1)RST specifies the input current when pull-up resistance has been selected; leakage current when noresistance has been selected. PB7 does not specify the leakage current because it’s only for output.∗2)When incorporated pull-down resistance has been selected through mask option.∗3)When all pins are open.Item Symbol Pins ConditionsMin.Typ.Max.UnitPower supply current ∗3Input capacityV DDPins other thanS0 to S31, T0 to T7,PB7, PE6,AV REF ,AV SS , V FDP ,V DD , V SSI DD1High speed mode operation(1/2 frequency demultiplier clock)I DDS1I DDS2I DDS3I DD2V DD = 5.5V, 10MHz crystal oscillation (C 1= C 2= 15pF)V DD = 3V, 32kHz crystal oscillation (C 1= C 2= 47pF)SLEEP modeSTOP modeV DD = 5.5V, 10MHz crystal oscillation;and termination of 32kHz oscillationV DD = 5.5V, 10MHz crystal oscillation (C 1= C 2= 15pF)V DD = 3V, 32kHz crystal oscillation (C 1= C 2= 47pF)2040mA35100µA1.28mA930µA 10µAC INClock 1MHz0V for all pins excluding measured pins1020pF∗t sys indicates the three values below according to the upper two bits (CPU clock selection) of the control clock registor (address: 00FE H ).tsys (ns)=2000/fc (upper two bits="00"), 4000/fc (upper two bits="01"), 16000/fc (upper two bits="11")Crystal oscillation Ceramic oscillationExternal clock32kHz clock application condition Crystal oscillationTEX EC0EC1EH EL EF ER t THt TLt TFt TRAC Characteristics (1) Clock timingSystem clock frequency System clock input pulse width System clock input rise time,fall timeEvent count input clock pulse widthEvent count input clock rise time, fall time System clock frequency Event count input pulse widthEvent count input rise time, fall timef Ct XL t XH t CR t CF t EH t EL t ER t EFf Ct TL t TH t TR t TFXTAL EXTAL EXTAL EXTAL EC0, EC1EC0, EC1TEX TX TEX TEXMHz ns ns nsmskHzµs msItemSymbol Pin Conditions Min.Unit Fig. 1, Fig. 2Fig. 1, Fig. 2External clock drive Fig. 1, Fig. 2External clock drive Fig. 3Fig. 3V DD = 2.7 to 5.5V Fig. 2 (32kHz clock application condition)Fig. 3Fig. 3137.5t sys + 50∗10Typ.32.768Max.102002020(Ta = –20 to +75°C, V DD = 4.5 to 5.5V, Vss = 0V reference)Fig. 3. Event count clock timingChip select transfer mode (SCK0 = output mode)Chip select transfer mode (SCK0 = output mode)Chip select transfer mode Chip select transfer mode Chip select transfer mode Note 1)t sys indicates the three values below according to the upper two bits (CPU clock selection) of thecontrol clock registor (address: 00FE H ).t sys (ns)=2000/fc (upper two bits="00"), 4000/fc (upper two bits="01"), 16000/fc (upper two bits="11")Note 2)The load condition for the SCK0 output mode, SO0 output delay time is 50pF + 1TTL.(2) Serial transfer (CH0)(Ta = –20 to +75°C, V DD = 4.5 to 5.5V, Vss = 0V reference)ItemCS0 ↓ →SCK0 delay time CS0 ↑ →SCK0 float delay time CS0 ↓ →SO0 delay time CS0 ↑ →SO0 float delay time CS0 High level width SCK0 cycle time SCK0High, Low level width SI0 input set-up time (for SCK0 ↑)SI0 input hold time (for SCK0 ↑)SCK0 ↓ →SO0delay timet DCSK t DCSKF t DCSOt DCSOF t WHCS t KCY t KH t KL t SIK t KSI t KSOSCK0SCK0SO0SO0CS0SCK0SCK0SI0SI0SO0Input mode Output mode Input mode Output mode SCK0 input mode SCK0 output mode SCK0 input mode SCK0 output mode SCK0 input mode SCK0 output modens ns ns ns ns SymbolPin Min.t sys + 200t sys + 200t sys + 200t sys + 200t sys + 2002t sys + 20016000/fct sys + 1008000/fc–50100200t sys + 200100ns ns ns ns ns ns ns nsns nst sys + 200100Max.Unit ConditionFig. 4. Serial transfer CH0 timingSCK0SI0SO0Serial transfer (CH1)(Ta = –20 to +75°C, V DD = 4.5 to 5.5V, Vss = 0V reference)ItemSCK1 cycle time t KCY SCK1Input mode Ouput mode Input mode Ouput mode SCK1 input mode SCK1 ouput mode SCK1 input mode SCK1 ouput mode SCK1 input mode SCK1 ouput mode100016000/fc 4008000/fc–50100200200100200100ns ns ns ns ns ns ns ns ns nsSCK1SI1SI1SO1t KH t KL t SIK t KSI t KSOSCK1High, Low level width SI1 input set-up time (for SCK1↑)SI1 input hold time (for SCK1↑)SCK1 ↓ →SO1 delay timeSymbolPin Condition Min.Max.Unit Note)The load condition for the SCK1output mode, SO1 output delay time is 50pF + 1TTL.Fig. 5. Serial transfer CH1 timingSO1SI1Conversion time Sampling time Reference input voltage Analog input voltaget CONV t SAMPV REF V IAN V ZT ∗1V FT ∗2I REFAV REFAN0 to AN7Ta = 25°C V DD = 5.0VV SS = AV SS = 0VOperation modeSLEEP mode STOP mode32kHz operation modeLinearity error Zero transition voltageFull-scaletransition voltage Resolution AV REF currentAV REFI REFSµs µsV V V DD AV REF 1.0mA 10µA0.6160/f ADC ∗312/f ADC ∗3V DD – 0.5ItemSymbol Pin Condition Min.Typ.Max.Unit Bits (3)A/D converter characteristics(Ta = –20 to +75°C, V DD = 4.5 to 5.5V, AV REF = 4.0 to AV DD , Vss = AV SS = 0V reference)8±3LSB 70mV 5030104970–104910mV Fig. 6. Definition of A/D converter termsAnalog inputV FTV ZT00H01H FE HFF H D i g i t a l c o n v e r s i o n v a l u e∗1)V ZT :Value at which the digital transfer value changesfrom 00H to 01H and vice versa.∗2)V FT :Value at which the digital transfer value changesfrom FE H to FF H and vice versa.∗3)f ADC indicates the below values due to ADC operationclock selection (ADCS: Bit 6 of address 00F9H ).During PS2 selection, f ADC = fc/2During PS1 selection, f ADC = fcExternal interruption High, Low level width Reset input Low level widthINT0INT1INT2NMI/INT3RST132/fc µsµsItemSymbolPin ConditionMin.Max.Unit t IH t IL t RSL(4) Interruption, reset input(Ta = –20 to +75°C, V DD = 4.5 to 5.5V, Vss = 0V reference)INT0INT1INT2falling edge)Fig. 7. Interruption input timingRSTFig. 8. RST input timing(5) Others(Ta = –20 to +75°C, V DD= 4.5 to 5.5V, Vss = 0V reference)ItemCLK inputHigh, Low level widtht CTH t CTLCTLt sys = 2000/fc t sys + 200nsSymbolPin ConditionMin.Max.Unit Fig. 9. Other timingCTLAppendixFig. 10. Recommended oscillation circuit(i) Main clock(ii) Main clock(iii) Sub clockManufacturer MURATA MFGCO., LTD.RIVER ELETEC CO., LTDKINSEKI LTD.Model CSA4.19MG CSA8.00MTZCST4.19MGW ∗CST8.00MTW ∗HC-49/U03HC-49/U (-S)P3fc (MHz)4.198.0010.004.198.0010.004.198.0010.004.198.0010.00202032.768kHz50223012273012270C 1(pF)C 2(pF)Rd (Ω)Circuitexample(i)CSA10.0MTZ (ii)CST10.0MTW ∗(i)1M (iii)Those marked with an asterisk (∗) signify types with built-in ground capacitance (C 1, C 2).ItemContentReset pin pull-up resistanceNon-existent Existent Non-existentExistentMask option tableHigh voltage drive output port pull-down resistance– 21–CXP82432A/82440APackage Outline Unit: mmSONY CODE EIAJ CODE JEDEC CODEPACKAGE MATERIALLEAD TREATMENT LEAD MATERIAL PACKAGE WEIGHTEPOXY RESIN SOLDER PLATING COPPER / 42 ALLOYPACKAGE STRUCTUREQFP-100P-L01100PIN QFP (PLASTIC)+ 0.1∗QFP100-P-1420-A1.4g元器件交易网。

S-8243BAEFT资料

S-8243BADFT S-8243BAEFT S-8243BAFFT

Note. Change in the detection voltage is available in products other than listed above. Contact the SII sales office.

S-8243B series

VDD

Rev. 1.0

Battery protection

VREG

DOP,COP RVCM,RVSM control

DOP

Voltage regulator

COP

Delay Delay Delay

660 kΩ

200nA

CTL1

VREG 1.4MΩ

Delay440 k ΩFra bibliotekCTL2

S-8243AACFT S-8243AADFT

Note. Change in the detection voltage is available in products other than listed above. Contact the SII sales office.

Table.2 S-8243B Series ( 4-serial cell )

(3) (4) (5) (6) (7) (8) (9)

(10) Low current consumption

Applications

• • Lithium-ion rechargeable battery packs Lithium- polymer rechargeable battery packs

(Overdischarge release voltage n (=Overdischarge detection voltage n + Hysteresis voltage n) can be selected within the range 2.0 V to 3.4 V.) (2) Three-level overcurrent protection including protection for short-circuiting • Overcurrent detection voltage 1 0.05 V to 0.3 V (50 mV step) Accuracy ±25 mV • Overcurrent detection voltage 2 0.5 V Accuracy ±100 mV • Overcurrent detection voltage 3 Accuracy ± 15 % VDD/2 Delay times for overcharge detection, overdischarge detection and overcurrent detection 1 can be set by external capacitors. (Delay times for overcurrent detection 2 and 3 are fixed internally.) Charge/discharge operation can be controlled through the control pins. High-accuracy battery monitor amp Voltage regulator High input-voltage device Wide operating voltage range Wide operating temperature range: Operation mode Power down mode (11) Small package GAMP = VBATTERY × 0.2 ± 1.0% VOUT = 3.3 V ± 2.4% (3 mA max.) Absolute maximum rating: 26 V 6 V to 18 V −40°C to +85 °C 120 µA max. 0.1 µA max. 16-Pin TSSOP package

ADC0832CCN

±1 ±1

± 1⁄2 ±1 ± 1⁄2 ±1

Molded (N) Molded (N) SO(M) PCC (V) PCC (V) Molded (N) C0831/ADC0832/ADC0834/ADC0838

Absolute Maximum Ratings

+

15 mA 6.5V

Operating Ratings (Notes 1, 2)

Supply Voltage, VCC Temperature Range ADC0832/8CIWM ADC0834BCN, ADC0838BCV, ADC0831/2/4/8CCN, ADC0838CCV, ADC0831/2/4/8CCWM 0˚C to +70˚C 4.5 VDC to 6.3 VDC TMIN≤TA≤TMAX −40˚C to +85˚C

2)

(Notes 1,

Dual-In-Line Package (Plastic) Molded Chip Carrier Package Vapor Phase (60 sec.) Infrared (15 sec.) ESD Susceptibility (Note 5)

260˚C 215˚C 220˚C 2000V

Key Specifications

n n n n n Resolution Total Unadjusted Error Single Supply Low Power Conversion Time 8 Bits

± 1⁄2 LSB and ± 1 LSB

5 VDC 15 mW 32 µs

Features

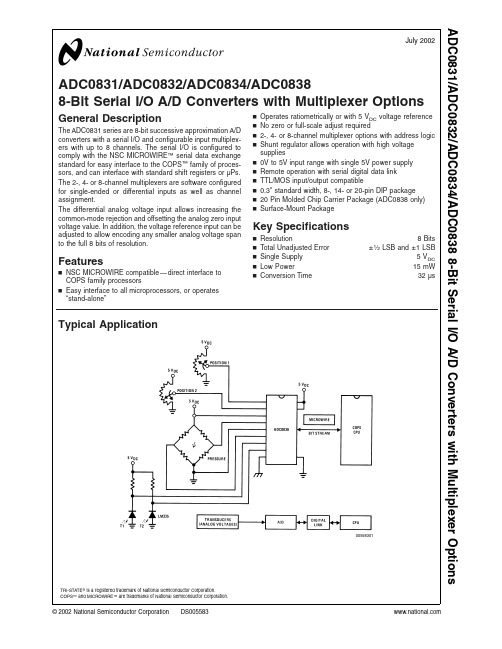

General Description

The ADC0831 series are 8-bit successive approximation A/D converters with a serial I/O and configurable input multiplexers with up to 8 channels. The serial I/O is configured to comply with the NSC MICROWIRE™ serial data exchange standard for easy interface to the COPS™ family of processors, and can interface with standard shift registers or µPs. The 2-, 4- or 8-channel multiplexers are software configured for single-ended or differential inputs as well as channel assignment. The differential analog voltage input allows increasing the common-mode rejection and offsetting the analog zero input voltage value. In addition, the voltage reference input can be adjusted to allow encoding any smaller analog voltage span to the full 8 bits of resolution. n n n n n n n n n n Operates ratiometrically or with 5 VDC voltage reference No zero or full-scale adjust required 2-, 4- or 8-channel multiplexer options with address logic Shunt regulator allows operation with high voltage supplies 0V to 5V input range with single 5V power supply Remote operation with serial digital data link TTL/MOS input/output compatible 0.3" standard width, 8-, 14- or 20-pin DIP package 20 Pin Molded Chip Carrier Package (ADC0838 only) Surface-Mount Package

FPGA可编程逻辑器件芯片EP4CE55F23C8N中文规格书

Four-Multiplier AdderIn the four-multiplier adder configuration shown in Figure 4–16, the DSP block canimplement 2 four-multiplier adders (1 four-multiplier adder per half-DSP block).These modes are useful for implementing one-dimensional and two-dimensionalfiltering applications. The four-multiplier adder is performed in two addition stages.The outputs of two of the four multipliers are initially summed in the two first-stageadder blocks. The results of these two adder blocks are then summed in thesecond-stage adder block to produce the final four-multiplier adder result, as shownin Equation 4–2 on page 4–4 and Equation 4–3 on page 4–5.Four-multiplier adder mode supports the rounding and saturation logic unit. You canuse the pipeline registers and output registers within the DSP block to pipeline themultiplier-adder result, increasing the performance of the DSP block.Figure 4–16.Four-Multiplier Adder Mode Shown for Half-DSP BlockNote to Figure 4–16:(1)Block output for accumulator overflow and saturate overflow.clock[3..0]ena[3..0]aclr[3..0]signasign bo u tp u t_ro u ndo u tp u t_sat u rateo v erflo w (1)I n p u t R e g i s t e r B a n k P i p e l i n e R e g i s t e r B a n k R o u n d /S a t u r a t e O u t p u t R e g i s t e r B a n kdataa_0[ ]data b _0[ ]dataa_1[ ]data b _1[ ]dataa_2[ ]data b _2[ ]dataa_3[ ]data b _3[ ]Half-DSP Block+++res u lt[ ]Figure4–8.12-Bit Independent Multiplier Mode Shown for Half-DSP BlockSoftware Support for Arria II Devices Software Support for Arria II DevicesAltera provides two distinct methods for implementing various modes of the DSPblock in a design: instantiation and inference. Both methods use the followingQuartus II megafunctions:■LPM_MULT ■ALTMULT_ADD ■ALTMULT_ACCUM ■ALTFP_MULTYou can instantiate the megafunctions in the Quartus II software to use the DSP block.Alternatively, with inference, you can create an HDL design and synthesize it with athird-party synthesis tool (such as LeonardoSpectrum, Synplify, or Quartus II NativeSynthesis) that infers the appropriate megafunction by recognizing multipliers,multiplier adders, multiplier accumulators, and shift functions. With either method,the Quartus II software maps the functionality to the DSP blocks during compilation.f For instructions about using the megafunctions and the MegaWizard Plug-InManager, refer to the Quartus II Software Help.f For more information, refer to Section III: Synthesis in volume 1 of the Quartus IIHandbook .shift_right shift_right = 1, shift right feature is enabled 1DSP Block Dynamic Signals per Full-DSP Blockclock0clock1clock2clock3DSP-block-wide clock signals 4ena0ena1ena2ena3Input and Pipeline Register enable signals 4aclr0aclr1aclr2aclr3DSP block-wide asynchronous clear signals (active low)4Total Count per Half- and Full-DSP Blocks 33Table 4–9.DSP Block Dynamic Signals for DSP Block in Arria II Devices (Part 2 of 2)Signal NameFunction Count。

单片机扩展芯片8243的中文资料

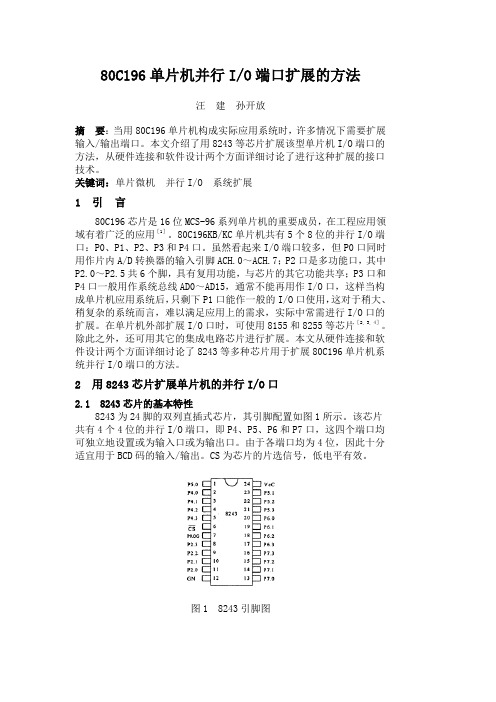

80C196单片机并行I/O端口扩展的方法汪建孙开放摘要:当用80C196单片机构成实际应用系统时,许多情况下需要扩展输入/输出端口。

本文介绍了用8243等芯片扩展该型单片机I/O端口的方法,从硬件连接和软件设计两个方面详细讨论了进行这种扩展的接口技术。

关键词:单片微机并行I/O 系统扩展1 引言80C196芯片是16位MCS-96系列单片机的重要成员,在工程应用领域有着广泛的应用[1]。

80C196KB/KC单片机共有5个8位的并行I/O端口:P0、P1、P2、P3和P4口。

虽然看起来I/O端口较多,但P0口同时用作片内A/D转换器的输入引脚ACH.0~ACH.7;P2口是多功能口,其中P2.0~P2.5共6个脚,具有复用功能,与芯片的其它功能共享;P3口和P4口一般用作系统总线AD0~AD15,通常不能再用作I/O口,这样当构成单片机应用系统后,只剩下P1口能作一般的I/O口使用,这对于稍大、稍复杂的系统而言,难以满足应用上的需求,实际中常需进行I/O口的扩展。

在单片机外部扩展I/O口时,可使用8155和8255等芯片[2, 3, 4]。

除此之外,还可用其它的集成电路芯片进行扩展。

本文从硬件连接和软件设计两个方面详细讨论了8243等多种芯片用于扩展80C196单片机系统并行I/O端口的方法。

2 用8243芯片扩展单片机的并行I/O口2.1 8243芯片的基本特性8243为24脚的双列直插式芯片,其引脚配置如图1所示。

该芯片共有4个4位的并行I/O端口,即P4、P5、P6和P7口,这四个端口均可独立地设置或为输入口或为输出口。

由于各端口均为4位,因此十分适宜用于BCD码的输入/输出。

CS为芯片的片选信号,低电平有效。

图1 8243引脚图8243芯片的P2口(P2.0~P2.3)为控制及信号端口,其有两个作用,一是传送设置芯片各端口工作方式的命令及端口地址,二是传送经芯片输入/输出的数据。

在第一种情况下,由P2.1、P2.0指定端口的地址,由P2.3、P2.2规定端口的工作方式,各位具体的定义见表1。

单片机驱动ADC0832模数转换程序

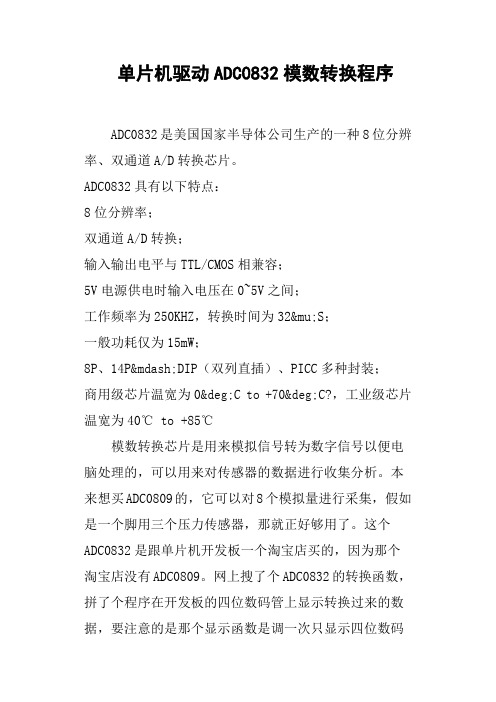

单片机驱动ADC0832模数转换程序ADC0832是美国国家半导体公司生产的一种8位分辨率、双通道A/D转换芯片。

ADC0832具有以下特点:8位分辨率;双通道A/D转换;输入输出电平与TTL/CMOS相兼容;5V电源供电时输入电压在0~5V之间;工作频率为250KHZ,转换时间为32μS;一般功耗仅为15mW;8P、14P—DIP(双列直插)、PICC多种封装;商用级芯片温宽为0°C to +70°C?,工业级芯片温宽为40℃ to +85℃模数转换芯片是用来模拟信号转为数字信号以便电脑处理的,可以用来对传感器的数据进行收集分析。

本来想买ADC0809的,它可以对8个模拟量进行采集,假如是一个脚用三个压力传感器,那就正好够用了。

这个ADC0832是跟单片机开发板一个淘宝店买的,因为那个淘宝店没有ADC0809。

网上搜了个ADC0832的转换函数,拼了个程序在开发板的四位数码管上显示转换过来的数据,要注意的是那个显示函数是调一次只显示四位数码管的一位的,所以不能转换显示转换显示这样,要转换,显示一次二次三次四次,转换,显示一次二次三次四次这样。

ADC0832引脚及代码如下:(一晚没睡,等下准备回家过清明扫墓去。

归去来兮!问西楼禁烟何处好?绿野晴天道。

马穿杨柳嘶,人倚秋千笑,探莺花总教春醉倒。

)//头文件: #include ; #include ;//变量定义:unsigned char ly_dis[4];//定义显示缓冲区code unsigned chartable[]={0xc0,0xf9,0xa4,0xb0,0x99,0x92,0x82,0xf8, 0x80,0x90};//表:共阳数码管 0-9unsigned char l_posit=0; //显示位置//引脚定义:sbit SMG_q = P3^4; //定义数码管阳级控制脚(千位)sbit SMG_b = P3^5; //定义数码管阳级控制脚(百位)sbit SMG_s = P3^7; //定义数码管阳级控制脚(十位)sbit SMG_g = P3^6; //定义数码管阳级控制脚(个位) sbit CS= P0^5;sbit Clk = P0^6;sbit DATI = P0^4;sbit DATO = P0^4;unsigned char dat = 0x00;//AD值unsigned char count = 0x00;//定时器计数unsigned char CH;//通道变量//函数声明:void display(void);//显示函数,显示缓冲区内容void delay(void);//unsigned char GetValue0832(bit Channel); unsigned char adc0832(unsigned char CH);//主函数,C语言的入口函数:void main(){unsigned int i=0;int ltemp;while(1){if(i==100){ltemp=adc0832(1);//隔时取模数转换(0~255对应0.00-5.00的电压) ly_dis[0]=ltemp/100;//显示百位值ltemp=ltemp%100;ly_dis[1]=ltemp/10; //显示十位值ltemp=ltemp%10;ly_dis[2]=ltemp/1; //显示个位值ly_dis[3]=0; //显示小数点后一位0}i++;if(i==3000)i=0;display(); //调用显示调一次只显示一位轮流显示四位delay();}}//显示函数,参数为显示内容void display(){P0=0XFF;//switch(l_posit){case 0: //选择千位数码管,关闭其它位SMG_q=0;SMG_b=1;SMG_g=1;P0=table[ly_dis[0]]; //输出显示内容 break;case 1: //选择百位数码管,关闭其它位 SMG_q=1;SMG_b=0;SMG_s=1;SMG_g=1;P0=table[ly_dis[1]];break;case 2: //选择十位数码管,关闭其它位 SMG_q=1;SMG_b=1;SMG_s=0;SMG_g=1;P0=table[ly_dis[2]]&0x7f;break;case 3: //选择个位数码管,关闭其它位 SMG_q=1;SMG_b=1;SMG_s=1;P0=table[ly_dis[3]];break;}l_posit++; //每调用一次将轮流显示一位if(l_posit>;3)l_posit=0;}//延时子函数,短暂延时void delay(void){unsigned char i=10;while(i--);}/************************************************ ****************************函数功能:AD转换子程序入口参数:CH出口参数:dat************************************************* ***************************/unsigned char adc0832(unsigned char CH) {unsigned char i,test,adval;adval = 0x00;test = 0x00;Clk = 0;//初始化DATI = 1;_nop_();CS = 0;_nop_();Clk = 1;_nop_();if ( CH == 0x00 )//通道选择{Clk = 0;DATI = 1;//通道0的第一位_nop_();Clk = 1;_nop_();Clk = 0;DATI = 0;//通道0的第二位 _nop_();Clk = 1;_nop_();}else{Clk = 0;DATI = 1;//通道1的第一位 _nop_();Clk = 1;_nop_();Clk = 0;DATI = 1;//通道1的第二位_nop_();Clk = 1;_nop_();}Clk = 0;DATI = 1;for( i = 0;i ;>;= 1; if (DATO)test |= 0x80;elsetest |= 0x00;_nop_();Clk = 1;_nop_();Clk = 0;}if (adval == test)//比较前8位与后8位的值,如果不相同舍去。

CY8C24223A资料

The PSoC Core

The PSoC Core is a powerful engine that supports a rich feature set. The core includes a CPU, memory, clocks, configurable GPIO (General Purpose IO).

ADC08234BIN资料

TL H 11015ADC08231 ADC08234 ADC08238 8-Bit2ms Serial I O A D Converters with MUX Reference and Track HoldDecember1994 ADC08231 ADC08234 ADC082388-Bit2m s Serial I OA D Converters with MUX Reference and Track Hold General DescriptionThe ADC08231 ADC08234 ADC08238are8-bit succes-sive approximation A D converters with serial I O and con-figurable input multiplexers with up to8channels The serialI O is configured to comply with the NSC MICROWIRE TMserial data exchange standard for easy interface to theCOPS TM family of controllers and can easily interface withstandard shift registers or microprocessorsDesigned for high-speed low-power applications the devic-es are capable of a fast2m s conversion when used with a4MHz clockAll three devices provide a2 5V band-gap derived referencewith guaranteed performance over temperatureA track hold function allows the analog voltage at the posi-tive input to vary during the actual A D conversionThe analog inputs can be configured to operate in variouscombinations of single-ended differential or pseudo-differ-ential modes In addition input voltage spans as small as1Vcan be accommodatedApplicationsY High-speed data acquisitionY Digitizing automotive sensorsY Process control monitoringY Remote sensing in noisy environmentsY Disk drivesY Portable instrumentationY Test systemsFeaturesY Serial digital data link requires few I O pinsY Analog input track hold functionY4-or8-channel input multiplexer options with addresslogicY On-chip2 5V band-gap reference(g2%over tempera-ture guaranteed)Y No zero or full scale adjustment requiredY TTL CMOS input output compatibleY0V to5V analog input range with single5V powersupplyY Pin compatible with Industry-Standards ADC0831 4 8Key SpecificationsY Resolution8BitsY Conversion time(f C e4MHz)2m s(Max)Y Power dissipation20mW(Max)Y Single supply5V DC(g5%)Y Total unadjusted error g LSB and g1LSBY Linearity Error(V REF e2 5V)g LSBY No missing codes(over temperature)Y On-board Reference a2 5V g1 5%(Max) ADC08238Simplified Block DiagramTL H 11015–4 TRI-STATE is a registered trademark of National Semiconductor CorporationCOPS TM microcontrollers and MICROWIRE TM are trademarks of National Semiconductor CorporationC1995National Semiconductor Corporation RRD-B30M75 Printed in U S AOrdering InformationIndustrialPackage(b40 C s T A s a85 C)ADC08231BIN ADC08231CIN N08E DIPADC08234BIN ADC08234CIN N14A DIPADC08234CIMF MTB24 TSSOPADC08238BIN ADC08238CIN N20A DIPADC08231BIWM ADC08231CIWM M14B SOADC08234BIWM ADC08234CIWM M14B SOADC08238BIWM ADC08238CIWM M20B SO Connection DiagramsADC08238SO and DIPTL H 11015–1 ADC08231DIPTL H 11015–3 ADC08231SOTL H 11015–26ADC08234SO and DIPTL H 11015–2ADC08234TSSOPTL H 11015–27 2Absolute Maximum Ratings(Notes1 3) If Military Aerospace specified devices are required please contact the National Semiconductor Sales Office Distributors for availability and specifications Supply Voltage(V CC)6 5V Voltage at Inputs and Outputs b0 3V to V CC a0 3V Input Current at Any Pin(Note4)g5mA Package Input Current(Note4)g20mA Power Dissipation at T A e25 C(Note5)800mW ESD Susceptibility(Note6)1500V Soldering InformationN Package(10sec )260 C TSSOP and SO Package(Note7)Vapor Phase(60sec )215 C Infrared(15sec )220 C Storage Temperature b65 C to a150 C Operating Ratings(Notes2 3) Temperature Range T MIN s T A s T MAX ADC08231BIN ADC08231CIN b40 C s T A s a85 C ADC08234BIN ADC08234CINADC08238BIN ADC08238CINADC08231BIWM ADC08231CIWMADC08234BIWM ADC08238BIWMADC08234CIWM ADC08238CIWMADC08234CIMFSupply Voltage(V CC)4 5V DC to6 3V DCElectrical CharacteristicsThe following specifications apply for V CC e a5V DC V REF e a2 5V DC and f CLK e4MHz R Source e50X unless otherwise specified Boldface limits apply for T A e T J e T MIN to T MAX all other limits T A e T J e25 CADC08231ADC08234andADC08238with BINUnits Symbol Parameter Conditions CIN BIWM(Limits)CIWM or CIMF SuffixesTypical Limits(Note8)(Note9)CONVERTER AND MULTIPLEXER CHARACTERISTICSLinearity Error V REF e a2 5V DCBIN BIWM g LSB(max)CIN CIMF CIWM g1LSB(max)Gain Error V REF e a2 5V DCBIN BIWM g1LSB(max)CIN CIMF CIWM g1LSB(max)Zero Error V REF e a2 5V DCBIN BIWM g1LSB(max)CIN CIMF CIWM g1LSB(max)Total Unadjusted Error V REF e a5V DCBIN BIWM(Note10)g1LSB(max)CIN CIMF CIWM g1LSB(max)Differential Linearity V REF e a2 5V DC8Bits(min) R REF Reference Input Resistance(Note11)3 5k X1 3k X(min)6 0k X(max)V IN Analog Input Voltage(Note12)(V CC a0 05)V(max)(GND b0 05)V(min)3Electrical Characteristics(Continued)The following specifications apply for V CC e a5V DC V REF e a2 5V DC and f CLK e4MHz R source e50X unless otherwise specified Boldface limits apply for T A e T J e T MIN to T MAX all other limits T A e T J e25 CADC08231ADC08234andADC08238with BINUnits Symbol Parameter Conditions CIN BIWM(Limits)CIWM or CIMF SuffixesTypical Limits(Note8)(Note9)CONVERTER AND MULTIPLEXER CHARACTERISTICS(Continued)DC Common-Mode Error V REF e a2 5V DC g LSB(max)Power Supply Sensitivity V CC e a5V g5%g LSB(max)V REF e a2 5V DCOn Channel Leakage On Channel e5V 0 2m A(max) Current(Note13)Off Channel e0V1On Channel e0V b0 2m A(max)Off Channel e5V b1Off Channel Leakage On Channel e5V b0 2m A(max) Current(Note13)Off Channel e0V b1On Channel e0V 0 2m A(max)Off Channel e5V1DYNAMIC CHARACTERISTICS(see Typical Converter Performance Characteristics)S N a D Signal-to-V REF e a5V(Noise a Distortion)Sample Rate e286kHzRatio V IN e a5V p-pf IN e10kHz48 35dBf IN e50kHz48 00dBf IN e100kHz47 40dBDIGITAL AND DC CHARACTERISTICSV IN(1)Logical‘‘1’’Input Voltage V CC e5 25V2 0V(min) V IN(0)Logical‘‘0’’Input Voltage V CC e4 75V0 8V(max)I IN(1)Logical‘‘1’’Input Current V IN e5 0V1m A(max)I IN(0)Logical‘‘0’’Input Current V IN e0V b1m A(max)V OUT(1)Logical‘‘1’’Output Voltage V CC e4 75VI OUT e b360m A2 4V(min)I OUT e b10m A4 5V(min)V OUT(0)Logical‘‘0’’Output Voltage V CC e4 75V0 4V(max)I OUT e1 6mAI OUT TRI-STATE Output Current V OUT e0V b3 0m A(max)V OUT e5V3 0m A(max)I SOURCE Output Source Current V OUT e0V b6 5mA(min)I SINK Output Sink Current V OUT e V CC8 0mA(min)I CC Supply Current CS e HIGHADC08234 ADC082383 0mA(max)ADC08231(Note16)6 0mA(max)4Electrical Characteristics (Continued)The following specifications apply for V CC e a 5V DC and f CLK e 4MHz unless otherwise specified Boldface limits apply for T A e T J e T MIN to T MAX all other limits T A e T J e 25 CADC08231 ADC08234and ADC08238with BINUnits Symbol Parameter ConditionsCIN BIWM(Limits)CIWM or CIMF Suffixes Typical Limits (Note 8)(Note 9)REFERENCE CHARACTERISTICS V REF OUTOutput VoltageBIN BIJ 2 52 5g 1 5%VBIWM g 2%CIN CIJ 2 52 5g 3 0%CIWM CMJg 3 5%D V REF D T Temperature Coefficient 40ppm CD V REF D I LLoad Regulation Sourcing% mA (max)(Note 17)(0s I L s a 4mA)ADC08234 0 0030 1ADC08238Sourcing(0s I L s a 2mA)ADC082310 0030 1Sinking(b 1s I L s 0mA)ADC08234 0 20 5ADC08238Sinking(b 1s I L s 0mA)ADC082310 20 5Line Regulation4 75V s V CC s5 25V 0 56mV (max)I SCShort Circuit CurrentV REF e 0V (max)mA ADC08234 825ADC08238V REF e 0V ADC08231825T SU Start-Up Time V CC 0V x 5V 20ms C L e 100m FD V REF D tLong Term Stability200ppm 1kHr5Electrical Characteristics(Continued)The following specifications apply for V CC e a5V DC V REF e a2 5V DC and t r e t f e20ns unless otherwise specified Boldface limits apply for T A e T J e T MIN to T MAX all other limits T A e T J e25 CSymbol Parameter Conditions Typical Limits Units (Note8)(Note9)(Limits)f CLK Clock Frequency10kHz(min)4MHz(max)Clock Duty Cycle40%(min)(Note14)60%(max)T C Conversion Time(Not Including f CLK e4MHz81 f CLK(max) MUX Addressing Time)2m s(max)t CA Acquisition Time1 1 f CLK(max)t SELECT CLK High while CS is High50nst SET-UP CS Falling Edge or Data Input25ns(min) Valid to CLK Rising Edget HOLD Data Input Valid after CLK20ns(min) Rising Edget pd1 t pd0CLK Falling Edge to Output C L e100pFData Valid(Note15)Data MSB First250ns(max)Data LSB First200ns(max)t1H t0H TRI-STATE Delay from Rising Edge C L e10pF R L e10k X50ns of CS to Data Output and SARS Hi-Z(see TRI-STATE Test Circuits)C L e100pF R L e2k X180ns(max)C IN Capacitance of Logic Inputs5pFC OUT Capacitance of Logic Outputs5pFNote1 Absolute Maximum Ratings indicate limits beyond which damage to the device may occurNote2 Operating Ratings indicate conditions for which the device is functional These ratings do not guarantee specific performance limits For guaranteed specifications and test conditions see the Electrical Characteristics The guaranteed specifications apply only for the test conditions listed Some performance characteristics may degrade when the device is not operated under the listed test conditionsNote3 All voltages are measured with respect to AGND e DGND e0V DC unless otherwise specifiedNote4 When the input voltage(V IN)at any pin exceeds the power supplies(V IN k(AGND or DGND)or V IN l AV CC )the current at that pin should be limited to 5mA The20mA maximum package input current rating limits the number of pins that can safely exceed the power supplies with an input current of5mA to four pinsNote5 The maximum power dissipation must be derated at elevated temperatures and is dictated by T JMAX i JA and the ambient temperature T A The maximumallowable power dissipation at any temperature is P D e(T JMAX b T A) i JA or the number given in the Absolute Maximum Ratings whichever is lower For deviceswith suffixes BIN CIN BIJ CIJ BIWM and CIWM T JMAX e125 C For devices with suffix CMJ T JMAXe150 C The typical thermal resistances(i JA)of theseparts when board mounted follow ADC08231with BIN and CIN suffixes120 C W ADC08234with BIN and CIN suffixes95 C W ADC08234with CIMF suffix 167 C W ADC08238with BIN and CIN suffixes80 C W ADC08231with BIWM and CIWM suffixes140 C W ADC08234with BIWM and CIWM suffixes140 C W ADC08238with BIWM and CIWM suffixes91 C WNote6 Human body model 100pF capacitor discharged through a1 5k X resistorNote7 See AN450‘‘Surface Mounting Methods and Their Effect on Product Reliability’’or Linear Data Book section‘‘Surface Mount’’for other methods of soldering surface mount devicesNote8 Typicals are at T J e25 C and represent the most likely parametric normNote9 Guaranteed to National’s AOQL(Average Outgoing Quality Level)Note10 Total unadjusted error includes zero full-scale linearity and multiplexer error Total unadjusted error with V REF e a5V only applies to the ADC08234 and ADC08238 See Note16Note11 Cannot be tested for the ADC08231Note12 For V IN(b)t V IN(a)the digital code will be00000000 Two on-chip diodes are tied to each analog input(see Block Diagram)which will forward-conduct for analog input voltages one diode drop below ground or one diode drop greater than V CC supply During testing at low V CC levels(e g 4 5V) high level analog inputs(e g 5V)can cause an input diode to conduct especially at elevated temperatures This will cause errors for analog inputs near full-scale The specification allows50mV forward bias of either diode this means that as long as the analog V IN does not exceed the supply voltage by more than50mV the output code will be correct Exceeding this range on an unselected channel will corrupt the reading of a selected channel Achievement of an absolute0V DC to5V DC input voltage range will therefore require a minimum supply voltage of4 950V DC over temperature variations initial tolerance and loadingNote13 Channel leakage current is measured after a single-ended channel is selected and the clock is turned off For off channel leakage current the following two cases are considered one with the selected channel tied high(5V DC)and the remaining off channels tied low(0V DC) total current flow through the off channels is measured two with the selected channel tied low and the off channels tied high total current flow through the off channels is again measured The two cases considered for determining on channel leakage current are the same except total current flow through the selected channel is measuredNote14 A40%to60%duty cycle range insures proper operation at all clock frequencies In the case that an available clock has a duty cycle outside of these limits the minimum time the clock is high or low must be at least120ns The maximum time the clock can be high or low is100m sNote15 Since data MSB first is the output of the comparator used in the successive approximation loop an additional delay is built in(see Block Diagram)to allow for comparator response timeNote16 For the ADC08231V REF IN is internally tied to the on chip2 5V band-gap reference output therefore the supply current is larger because it includes the reference current(700m A typical 2mA maximum)Note17 Load regulation test conditions and specifications for the ADC08231differ from those of the ADC08234and ADC08238because the ADC08231has the on-board reference as a permanent load6Typical Performance CharacteristicsReference VoltageLinearity Error vs TemperatureLinearity Error vs Clock FrequencyLinearity Error vs ADC08234)Temperature (ADC08238 Power Supply Current vs Temperature Output Current vs vs Clock FrequencyPower Supply Current Note For ADC08231add I REF (Note 16)TL H 11015–510kHz Sine Wave Input Spectral Response with 50kHz Sine Wave Input Spectral Response with 100kHz Sine Wave InputSpectral Response with Ratio vs Input FrequencySignal-to-Noise a Distortion TL H 11015–67Typical Reference Performance CharacteristicsLoad Regulation(3Typical Parts)Line Regulation (3Typical Parts)vs Temperature Output Drift vs Supply VoltageOutput Current AvailableTL H 11015–78TRI-STATE Test Circuits and Waveformst 1Ht 0HTL H 11015–8t 1Ht 0HTL H 11015–9Timing DiagramsData Input TimingTL H 11015–10To reset these devices CLK and CS must be simultaneously high for a period of t SELECT or greaterData Output TimingTL H 11015–11ADC08231Start Conversion TimingTL H 11015–129Timing Diagrams(Continued)ADC08231TimingTL H 11015–13 LSB first output not available on ADC08231LSB information is maintained for remainder of clock periods until CS goes highTo reset the ADC08231 CLK and CS must be simultaneusly high for a period of t SELECT or greater The ADC08231also has one extra clock period for sampling the analog signal(t ca) Otherwise it is compatible with the ADC0831ADC08234TimingTL H 11015–14 To reset the ADC08234 CLK and CS must be simultaneously high for a period of t SELECT or greater The ADC08234also has one extra clock period for sampling the analog signal(t ca) Otherwise it is compatible with the ADC083410Timing Diagrams (Continued)A D C 08238T i m i n gT L H 11015–15M a k e s u r e c l o c k e d g e 19c l o c k s i n t h e L S B b e f o r e S E i s t a k e n l o wT o r e s e t t h e A D C 08238 C L K a n d C S m u s t b e s i m u l t a n e o u s l y h i g h f o r a p e r i o d o f t S E L E C T o r g r e a t e r T h e A D C 08238a l s o h a s o n e e x t r a c l o c k p e r i o d f o r s a m p l i n g t h e a n a l o g s i g n a l (t c a ) O t h e r w i s e i t i s c o m p a t i b l e w i t h t h e A D C 083811ADC08238Functional Block DiagramT L H 11015–16S o m e o f t h e s e f u n c t i o n s p i n s a r e n o t a v a i l a b l e w i t h o t h e r o p t i o n sN o t e 1 F o r t h e A D C 08234 t h e ‘‘S E L 1’’F l i p -F l o p i s b y p a s s e d F o r t h e A D C 08231 V R E F O U T a n d V R E F I N a r e i n t e r n a l l y t i e d t o g e t h e r12Functional Description 1 0MULTIPLEXER ADDRESSINGThe design of these converters utilizes a comparator struc-ture with built-in sample-and-hold which provides for a dif-ferential analog input to be converted by a successive-approximation routineThe actual voltage converted is always the difference be-tween an assigned‘‘a’’input terminal and a‘‘b’’input ter-minal The polarity of each input terminal of the pair indi-cates which line the converter expects to be the most posi-tive If the assigned‘‘a’’input voltage is less than the‘‘b’’input voltage the converter responds with an all zeros out-put codeA unique input multiplexing scheme has been utilized to pro-vide multiple analog channels with software-configurable single-ended differential or pseudo-differential(which will convert the difference between the voltage at any analog input and a common terminal)operation The analog signal conditioning required in transducer-based data acquisition systems is significantly simplified with this type of input flexi-bility One converter package can now handle ground refer-enced inputs and true differential inputs as well as signals with some arbitrary reference voltageA particular input configuration is assigned during the MUX addressing sequence prior to the start of a conversion The MUX address selects which of the analog inputs are to be enabled and whether this input is single-ended or differen-tial Differential inputs are restricted to adjacent channel pairs For example channel0and channel1may be select-ed as a differential pair but channel0or1cannot act differentially with any other channel In addition to selecting differential mode the polarity may also be selected Channel 0may be selected as the positive input and channel1as the negative input or vice versa This programmability is best illustrated by the MUX addressing codes shown in the following tables for the various product optionsThe MUX address is shifted into the converter via the DI line Because the ADC08231contains only one differential input channel with a fixed polarity assignment it does not require addressingThe common input line(COM)on the ADC08238can be used as a pseudo-differential input In this mode the voltage on this pin is treated as the‘‘b’’input for any of the other input channels This voltage does not have to be analog ground it can be any reference potential which is common to all of the inputs This feature is most useful in single-sup-ply applications where the analog circuitry may be biased up to a potential other than ground and the output signals are all referred to this potentialTABLE I Multiplexer Package OptionsPart Number of Analog Channels Number of Number Single-Ended Differential Package PinsADC08231118ADC082344214ADC082388420TABLE II MUX Addressing ADC08238Single-Ended MUX ModeMUX Address Analog Single-Ended ChannelSTART SGL ODD SELECT01234567COM DIF SIGN1011000a b 11001a b 11010a b 11011a b 11100a b 11101a b 11110a b 11111a b13Functional Description(Continued)TABLE II MUX Addressing ADC08238(Continued)Differential MUX ModeMUX Address Analog Differential Channel-PairSTART SGL ODD SELECT0123DIF SIGN100123456710000a b10001a b10010a b10011a b 10100b a10101b a10110b a10111b aTABLE III MUX Addressing ADC08234Single-Ended MUX ModeMUX Address ChannelSTART SGL ODD SELECT0123 DIF SIGN11100a1101a1110a1111aCOM is internally tied to AGNDDifferential MUX ModeMUX Address ChannelSTART SGL ODD SELECT0123 DIF SIGN11000a b1001a b 1010b a1011b a14Functional Description(Continued)Since the input configuration is under software control it can be modified as required before each conversion A channel can be treated as a single-ended ground refer-enced input for one conversion then it can be reconfigured as part of a differential channel for another conversion Fig-ure1illustrates the input flexibility which can be achieved The analog input voltages for each channel can range from 50mV below ground to50mV above V CC(typically5V)with-out degrading conversion accuracy2 0THE DIGITAL INTERFACEA most important characteristic of these converters is their serial data link with the controlling processor Using a serial communication format offers two very significant system im-provements it allows many functions to be included in a small package and it can eliminate the transmission of low level analog signals by locating the converter right at the analog sensor transmitting highly noise immune digital data back to the host processor To understand the operation of these converters it is best to refer to the Timing Diagrams and Functional Block Diagram and to follow a complete conversion sequence For clarity a separate timing diagram is shown for each device1 A conversion is initiated by pulling the CS(chip select)line low This line must be held low for the entire conver-sion The converter is now waiting for a start bit and its MUX assignment word2 On each rising edge of the clock the status of the data in(DI)line is clocked into the MUX address shift register The start bit is the first logic‘‘1’’that appears on this line (all leading zeros are ignored) Following the start bit the converter expects the next2to4bits to be the MUX assignment word8Single-Ended8Pseudo-Differential4Differential Mixed ModeTL H 11015–17 FIGURE1 Analog Input Multiplexer Options for the ADC0823815Functional Description (Continued)3 When the start bit has been shifted into the start location of the MUX register the input channel has been assigned and a conversion is about to begin An interval of 1 clock periods is automatically inserted to allow for sam-pling the analog input The SARS line goes high at the end of this time to signal that a conversion is now in prog-ress and the DI line is disabled (it no longer accepts data)4 The data out (DO)line now comes out of TRI-STATE and provides a leading zero5 During the conversion the output of the SAR comparator indicates whether the analog input is greater than (high)or less than (low)a series of successive voltages gener-ated internally from a ratioed capacitor array (first 5bits)and a resistor ladder (last 3bits) After each comparison the comparator’s output is shipped to the DO line on the falling edge of CLK This data is the result of the conver-sion being shifted out (with the MSB first)and can be read by the processor immediately6 After 8clock periods the conversion is completed The SARS line returns low to indicate this clock cycle later7 The stored data in the successive approximation register is loaded into an internal shift register If the programmer prefers the data can be provided in an LSB first format this makes use of the shift enable (SE)control line On the ADC08238the SE line is brought out and if held high the value of the LSB remains valid on the DO line When SE is forced low the data is clocked out LSB first On devices which do not include the SE control line the data LSB first is automatically shifted out the DO line after the MSB first data stream The DO line then goes low and stays low until CS is returned high The ADC08231is an exception in that its data is only output in MSB first format8 All internal registers are cleared when the CS line is high and the t SELECT requirement is met See Data Input Tim-ing under Timing Diagrams If another conversion is de-sired CS must make a high to low transition followed by address informationThe DI and DO lines can be tied together and controlled through a bidirectional processor I O bit with one wireThis is possible because the DI input is only ‘‘looked-at’’during the MUX addressing interval while the DO line is still in a high impedance state 3 0REFERENCE CONSIDERATIONSThe V REF IN pin on these converters is the top of a resistor divider string and capacitor array used for the successive approximation conversion The voltage applied to this refer-ence input defines the voltage span of the analog input (the difference between V IN(MAX)and V IN(MIN)over which the 256possible output codes apply) The reference source must be capable of driving the reference input resistance which can be as low as 1 3k XFor absolute accuracy where the analog input varies be-tween specific voltage limits the reference input must be biased with a stable voltage source The ADC08234and the ADC08238provide the output of a 2 5V band-gap reference at V REF OUT This voltage does not vary appreciably with temperature supply voltage or load current (see Reference Characteristics in the Electrical Characteristics tables)and can be tied directly to V REF IN for an analog input span of 0V to 2 5V This output can also be used to bias external cir-cuits and can therefore be used as the reference in ratio-metric applications Bypassing V REF OUT with a 100m F ca-pacitor is recommendedFor the ADC08231 the output of the on-board reference is internally tied to the reference input Consequently the ana-log input span for this device is set at 0V to 2 5V The pin V REF C is provided for bypassing purposes and biasing ex-ternal circuits as suggested aboveThe maximum value of the reference is limited to the V CC supply voltage The minimum value however can be quite small (see Typical Performance Characteristics)to allow di-rect conversions of transducer outputs providing less than a 5V output span Particular care must be taken with regard to noise pickup circuit layout and system error voltage sourc-es when operating with a reduced span due to the in-creased sensitivity of the converter (1LSB equals V REF 256)TL H 11015–18a)RatiometricTL H 11015–19b)AbsoluteFIGURE 2 Reference Examples16Functional Description(Continued)4 0THE ANALOG INPUTSThe most important feature of these converters is that they can be located right at the analog signal source and through just a few wires can communicate with a controlling proces-sor with a highly noise immune serial bit stream This in itself greatly minimizes circuitry to maintain analog signal accura-cy which otherwise is most susceptible to noise pickup However a few words are in order with regard to the analog inputs should the input be noisy to begin with or possibly riding on a large common-mode voltageThe differential input of these converters actually reduces the effects of common-mode input noise a signal common to both selected‘‘a’’and‘‘b’’inputs for a conversion (60Hz is most typical) The time interval between sampling the‘‘a’’input and then the‘‘b’’input is of a clock peri-od The change in the common-mode voltage during this short time interval can cause conversion errors For a sinus-oidal common-mode signal this error isV error(max)e V PEAK(2q f CM) 0 5f CLK Jwhere f CM is the frequency of the common-mode signal V PEAK is its peak voltage valueand f CLK is the A D clock frequencyFor a60Hz common-mode signal to generate a LSB er-ror( 5mV)with the converter running at250kHz its peak value would have to be6 63V which would be larger than allowed as it exceeds the maximum analog input limits Source resistance limitation is important with regard to the DC leakage currents of the input multiplexer While operat-ing near or at maximum speed bypass capacitors should not be used if the source resistance is greater than1k X The worst-case leakage current of g1m A over temperature will create a1mV input error with a1k X source resistance An op amp RC active low pass filter can provide both im-pedance buffering and noise filtering should a high imped-ance signal source be required5 0OPTIONAL ADJUSTMENTS5 1Zero ErrorThe zero of the A D does not require adjustment If the minimum analog input voltage value V IN(MIN) is not ground a zero offset can be done The converter can be made to output00000000digital code for this minimum input voltage by biasing any V IN(b)input at this V IN(MIN)value This utilizes the differential mode operation of the A DThe zero error of the A D converter relates to the location of the first riser of the transfer function and can be mea-sured by grounding the V IN(b)input and applying a small magnitude positive voltage to the V IN(a)input Zero error is the difference between the actual DC input voltage which is necessary to just cause an output digital code transition from00000000to00000001and the ideal LSB value ( LSB e9 8mV for V REF e5 000V DC)5 2Full ScaleA full-scale adjustment can be made by applying a differen-tial input voltage which is1 LSB down from the desired analog full-scale voltage range and then adjusting the mag-nitude of the V REF IN input for a digital output code which is just changing from11111110to11111111(See figure enti-tled‘‘Span Adjust 0V s V IN s3V’’) This is possible only with the ADC08234and ADC08238 (The reference is inter-nally connected to V REF IN of the ADC08231)5 3Adjusting for an Arbitrary Analog InputVoltage RangeIf the analog zero voltage of the A D is shifted away from ground(for example to accommodate an analog input sig-nal which does not go to ground) this new zero reference should be properly adjusted first A V IN(a)voltage which equals this desired zero reference plus LSB(where the LSB is calculated for the desired analog span using1LSBe analog span 256)is applied to selected‘‘a’’input andthe zero reference voltage at the corresponding‘‘b’’input should then be adjusted to just obtain the00HEX to01HEX code transitionThe full-scale adjustment should be made with the proper V IN(b)voltage applied by forcing a voltage to the V IN(a) input which is given byV IN(a)fs adj e V MAX b1 5 (V MAX b V MIN)256( whereV MAX e the high end of the analog input rangeandV MIN e the low end(the offset zero)of the analog range(Both are ground referenced )The V REF IN(or V CC)voltage is then adjusted to provide a code change from FE HEX to FF HEX This completes the ad-justment procedure17。

汽车电子自动变速箱-TLE82453SA+三通道高低边线性电磁线圈驱动芯片应用攻略

三通道,高低边线性电磁线圈 驱动芯片 “龙”芯片TLE82453SA1 概况产品特点• 三个独立、高低边可配置的通道 • 全集成半桥功率级 • 在T j = 150 °C 时 R ON (max) = 250 m • 集成内置TCR 补偿的检测电阻• 负载电流测量范围:0mA 至1500mA (典型值) • 0.73mA 的电流设定点分辨率 • 电流控制精度小于500 mA 负载电流控制精度达+/- 5mA 大于500 mA 负载电流控制精度达+/- 1% • 免受负载电池电压变化的影响• 集成具有可编程振幅和频率的抖动发生器• 输出控制,诊断和可配置的串行外设接口(SPI ) • 每个通道独立的热关断功能PG-DSO-36• 每个通道均具有负载开路,开关被旁路,过流等故障的保护及诊断功能 • 具有可编程的摆率控制,来降低电磁干扰(EMI ) • 绿色产品(符合 RoHS 要求) • AEC 认证描述TLE82453用于自动变速箱,电子稳定控制系统和主动悬架系统的线性比例阀控制的芯片,是一款灵活且单片集成的电磁线圈驱动芯片。

三通道的设计可灵活配置高低边驱动方式。

器件由驱动晶体管,续流晶体管和电流检测电阻组成,最大限度地减少了所需外部元件的数量。

根据抖动设置和负载特性,具有0.73mA 的电流分辨率的器件可调节高达1500 mA 的负载平均电流。

三角波抖动发生器使能时,可以在被编程的电流设定点上按可编程的振幅和频率范围叠加三角波。

利用32位SPI 接口控制三个通道并监控诊断功能状态。

根据全功能SPI 接口的特点,通过复位输入低电平有效,RESN ,禁用所有通道并将所有内部寄存器复位至默认值。

通过使能引脚高电平有效,EN ,使能或禁用输出通道操作。

当EN 引脚低电平时,通道禁用。

每当检测到故障时,故障输出引脚生成一个相当于外部中断的信号发送给微控制器。

V B A TC P C 1LC P C 1HC P C 2LC P C 2HC P O U T2 功能框图VDDAREF VDDD GNDDLSUP0LSUP1LSUP2LOAD0LOAD1LOAD2GNDP2GNDP1GNDP0Block_Diagram.vsd图1 功能框图3 引脚配置3.1 引脚分配图2 引脚配置3.2 引脚定义和功能功率级接地。

单片机io扩展

单片机io扩展下面介绍两种单片机io扩展的方法!!!!用8243扩展单片机IO接口/*----------------------------------------------------------------------------------------------------------------函数名称:Config.h功能描述:8243端口配置输入参数:无输出参数:无特殊说明:在不同的单片机应用系统中,需要做相应调整//----------------------------------------------------------------------------------------------------------------*/#include ;sbitContrBit0=P1^0;sbit ContrBit1=P1^1;sbitContrBit2=P1^2;sbit ContrBit3=P1^3;sbit PROG=P1^4;sbit CS=P1^5;sfrdata_buf=0x90;/*----------------------------------------------------------------------------------------------------------------函数名称:driver8243功能描述:驱动8243输入参数:sele_P端口选择,sele_M工作模式选择,out_data输出模式下的输出数据输出参数:in_data接收模式返回接收到的数据,其它模式返回0特殊说明:在不同的单片机应用系统中,需要做相应得调整//----------------------------------------------------------------------------------------------------------------*/#include;char driver8243(char sele_P,char sele_M,char out_data) { charin_data=0;PROG=1; //置PROG为高电平//开始写控制字if((sele_P&0x01)==0) //将控制字最低位送到8243的p2.0{ContrBit0=0;}else{ ContrBit0=1; }if((sele_P&0x02)==0) //将控制字第二位送到8243的p2.1{ContrBit1=0;}else{ ContrBit1=1; //以上两位共同指定端口地址 }//写端口工作模式控制字if((sele_M&0x01)==0)//将端口工作模式控制字低位送到8243的p2.2{ContrBit2=0;}else{ ContrBit2=1; }if((sele_M&0x01)==0) //将端口工作模式控制字高位送到8243的p2.3{ContrBit3=0;}else{ ContrBit3=1; } //写控制字完成PROG=0; //在PROG上产生下降沿switch(sele_M&0x03)//判断工作模式{ case 0: break;//sele_M=B00为输入,不处理,等待上升沿 case 1: data_buf=out_data;break;//sele_M=B01为输出,直接送数据 case 2:data_buf=out_data;break;//sele_M=B10为逻辑或,直接送数据 case 3:data_buf=out_data;break;//sele_M=B11为逻辑与,直接送数据 }PROG=1;//在PROG上产生上升沿if((sele_M&0x03)==0)//sele_M=B00为输入,接收数据in_data=(data_buf&0x0F);return(in_data);//sele_M=B00,返回接收到的数据 //sele_M!=B00,返回0}void main( void){char receive_data;receive_data= driver8243(1,0,5);}单片机io扩展方法2:=======================单片机中IO口扩展IC===================================单片机中IO口数量非常有限,做一些少量的外围控制还可以,如果系统稍大一些就要加外加芯片来扩展IO数量,在应用过程中我发现PCF8574 这款芯片非常理想具有8路的输入输出的IO口同时具有锁存功能,和MCU的通讯方式为I2C,还具有中断输出功能当其中一个脚拉低时,就从中断脚输出一个低电平来通知单片机响应,这样MCU就可以按自己的方式工作当有外部触发时才读取PCF8574做为外部扩展按键等非常方便。

ADC0832 - 幸福的猫咪的日志 - 网易博客

ADC0832 - 幸福的猫咪的日志- 网易博客ADC0832硬件设计知识2008-12-27 11:10 阅读10 评论0 ADC0832 是美国国家半导体公司生产的一种8 位分辨率、双通道A/D转换芯片。

由于它体积小,兼容性强,性价比高而深受单片机爱好者及企业欢迎,其目前已经有很高的普及率。

学习并使用ADC0832 可是使我们了解A/D转换器的原理,有助于我们单片机技术水平的提高。

ADC0832 具有以下特点:· 8位分辨率;· 双通道A/D转换;· 输入输出电平与TTL/CMOS相兼容;· 5V电源供电时输入电压在0~5V之间;· 工作频率为250KHZ,转换时间为32μS;· 一般功耗仅为15mW;· 8P、14P—DIP(双列直插)、PICC 多种封装;· 商用级芯片温宽为0°C to +70°C,工业级芯片温宽为.40°C to +85°C;芯片顶视图:(图1、图2)图1 图2-DYDIYE-mail:DYDIY@ 第2 页芯片接口说明:· CS_ 片选使能,低电平芯片使能。

· CH0 模拟输入通道0,或作为IN+/-使用。

· CH1 模拟输入通道1,或作为IN+/-使用。

· GND 芯片参考0 电位(地)。

· DI 数据信号输入,选择通道控制。

· DO 数据信号输出,转换数据输出。

· CLK 芯片时钟输入。

· Vcc/REF 电源输入及参考电压输入(复用)。

ADC0832 与单片机的接口电路:图3-DYDIYE-mail:DYDIY@ 第3 页ADC0832 为8位分辨率A/D转换芯片,其最高分辨可达256级,可以适应一般的模拟量转换要求。

8249c参数

8249C是MAX7000系列CPLD器件之一,采用高密度的编程技术,在单一芯片上实现逻辑功能,有高密度、低功耗、高速、低成本、易编程、易扩展、易升级、易调试、易配置、易使用等特点。

此外,8249C的内部包含32个逻辑宏单元和64个输入/输出单元,可编程逻辑容量为2500门。

它还包含有16Kb的内部RAM和可配置逻辑模块CLB(Configurable Logic Block),用于实现复杂的组合逻辑和时序逻辑功能。

在输入/输出方面,8249C具有8个I/O口,每个I/O口可以独立编程,以适应不同的应用需求。

此外,它还具有一个时钟输入口和一个时钟输出口,用于实现时序逻辑功能。

在编程方面,8249C采用JTAG接口进行编程,支持多种编程语言,如VHDL和Verilog等。

此外,它还支持在线编程和调试功能,方便用户进行开发和调试。

在应用方面,8249C可以应用于各种数字电路设计领域,如通信、计算机、工业控制、消费电子等领域。

它可以实现复杂的组合逻辑和时序逻辑功能,如数字滤波器、数据压缩算法、密码算法等。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

单片机扩展芯片8243的中文资料单片机扩展芯片8243中文资料。

引言。

单片机扩展芯片8243是一款功能强大的芯片,它可以为单片机提供丰富的外设接口和功能扩展。

本文将介绍8243芯片的主要特性、应用领域以及使用方法,希望能为大家带来一些帮助。

一、8243芯片的主要特性。

1. 多种外设接口。

8243芯片集成了多种外设接口,包括GPIO口、SPI接口、I2C接口、UART

接口等,可以方便地与各种外部设备进行通信和控制。

2. 大容量存储器。

8243芯片内置了大容量的存储器,包括闪存和RAM,可以存储大量的程序代码和数据,满足复杂应用的需求。

3. 强大的计算能力。

8243芯片采用高性能的处理器核心,具有强大的计算能力,可以处理复杂的算法和逻辑运算。

4. 低功耗设计。

8243芯片采用先进的低功耗设计,可以在保证性能的同时降低功耗,延长电池寿命。

5. 宽工作温度范围。

8243芯片具有宽工作温度范围,可以在-40°C到85°C的环境中稳定工作,

适用于各种恶劣的工作环境。

二、8243芯片的应用领域。

1. 工业控制。

8243芯片可以应用于工业控制领域,用于控制各种机械设备和生产线,实现自动化生产。

2. 智能家居。

8243芯片可以应用于智能家居领域,用于控制家电设备、监控安防系统等,实现智能化的家居生活。

3. 汽车电子。

8243芯片可以应用于汽车电子领域,用于控制车载娱乐系统、车辆控制系统等,提升汽车的智能化水平。

4. 医疗设备。

8243芯片可以应用于医疗设备领域,用于控制医疗设备的运行和数据采集,提高医疗设备的智能化程度。

5. 物联网设备。

8243芯片可以应用于物联网设备领域,用于连接各种物联网设备,实现设备之间的互联互通。

三、8243芯片的使用方法。

1. 硬件设计。

在使用8243芯片时,首先需要进行硬件设计,包括外设接口的连接、电源电

路的设计等。

根据具体的应用需求,设计合适的硬件电路。

2. 软件开发。

接着需要进行软件开发,包括程序代码的编写、调试和优化。

根据具体的应用需求,编写相应的程序代码,实现所需的功能。

3. 系统集成。

最后需要进行系统集成,将硬件和软件进行整合,进行系统调试和测试。

确保系统能够稳定运行,满足应用需求。

结论。

8243芯片是一款功能强大的单片机扩展芯片,具有丰富的外设接口和功能扩展能力,适用于多种应用领域。

在使用8243芯片时,需要进行硬件设计、软件开发和系统集成,以实现所需的功能。

希望本文能够为大家对8243芯片有更深入的了解,为实际应用提供一些帮助。