A3977步进电机驱动芯片中文说明

A3967SLB中文资料

A3967中文资料A3967SLTB带转换器的微步进驱动芯片特点±750毫安,30 V额定输出Satlington™灌电流驱动器自动电流衰减模式检测/选择3.0 V至5.5 V逻辑电源电压范围混合,快与慢电流衰减模式内部欠压锁定(UVLO)和热关断电路交叉电流保护描述A3967SLB是一个完善的微电机驱动器内置逻辑器。

它的设计操作双极步进电机具有全步进,1/2,1/4,和1/8模式,输出驱动能力30 V和±750毫安。

A3967SLB包括一个固定关断时间的电流调节器,具有慢,快,或混合电流衰减模式的功能。

此电流衰减控制方案可以减少可听到的电流噪音,增加步进精确度,并减少功耗。

A3967SLB的驱动转换非常容易实现,通过简单的“步进”输入中输入一个脉冲电动机将产生一个步骤(全,半,四分,或八分,这取决于两个逻辑输入)。

无需相位顺序表、高频率控制线或复杂的程序。

该A3967SLB是一个理想的适合复杂的微型项目开发的接口驱动芯片。

内部电路保护包括热关机与滞后,电压锁定(UVLO)下和交叉电流保护。

不需要特别的加电排序。

A3967SLB是提供一个24-PIN SOIC封装,能够自由焊接的磨砂100%雾锡引线框架。

选项卡处于接地电位,并且不需要绝缘。

的无铅(100%雾锡引线框架)版本也已经推出。

绝对最大额定值热特性热特性表电气特性在T A = +25°C,V BB = 30 V,V CC = 3.0 V至5.5V(除非另有说明)功能说明设备操作A3967 是一个操作方便、控制线少、完整的微型步进电机驱动器,。

它可用于双极步进电机在全,半,四分和八分模式的操作。

每两个中的电流 H桥输出的调节与固定关断时间脉冲宽度调制(PWM)控制电路。

在每个步骤中的电流由一个外部的值被设置电流检测电阻(R S),一个参考电压(V REF),以及 DAC 的输出电压的输出,通过控制转换。

在上电或复位时,将根据DAC设置和相电流极性初始的内部状态设置转换(见图内部状态情况),并设定的电流调节器两相混合衰减模式。

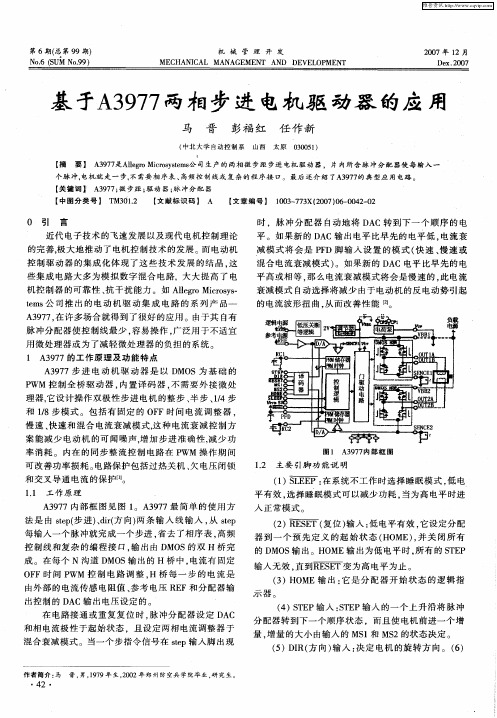

基于A3977两相步进电机驱动器的应用

的 D S输 出。HO MO ME输 出为 低电 平 时 , 有 的 S E 所 TP 输 入无 效 , 直到雨丽

示 器。

( )HO 3 ME输 出 : 是 分 配器 开 始 状 态 的逻 辑 指 它 ( )S E 4 T P输 入 :T P输 入 的一 个 上 升沿 将 脉 冲 SE 分 配器转 到下 一个 顺序 状态 ,而且使 电机 前进 一个 增 量 , 量 的大小 由输 入 的 MS 增 1和 MS 2的状 态 决定 。

( )D R( 向 ) 入 : 定 电机 的旋 转 方 向。 ( ) 5 I 方 输 决 6

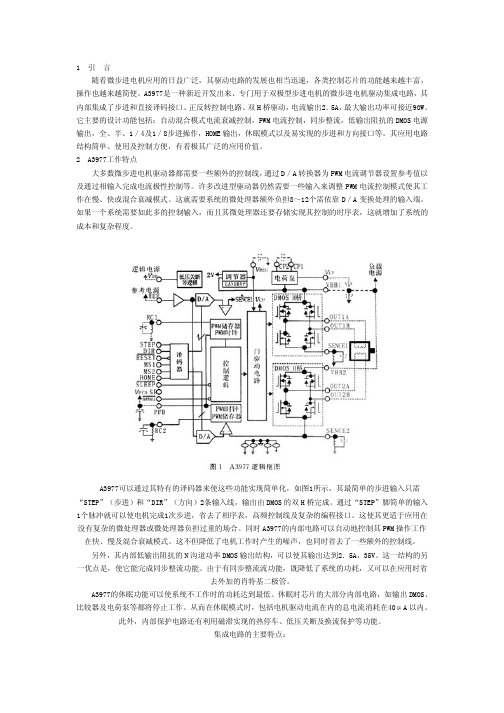

11 工 作 原 理 .

图 1 A3 7 9 7内 部 框 图

12 主 要 引脚 功 能 说 明 .

() 面 1

: 在系 统不 工 作时 选择 睡 眠模 式 , 电 低

平 有效 , 选择 睡 眠模式 可 以减少 功耗 , 当为高 电平 时进

入 正常模 式 。 () 2 雨丽 ( 复位 ) 入 : 电平有效 , 设定 分配 输 低 它

平高 或相 等 , 么 电流衰 减模 式将 会是 慢速 的 , 电流 那 此 衰减模 式 自动选 择将 减少 由于 电动 机 的反 电动 势引起

的电流 波形扭 曲 , 而改善 性能 [ 从 2 1 。

A 9 7 在许 多场 合就得 到 了很好 的应 用 。由于其 自有 37 ,

脉 冲分 配器 使控 制线 最少 , 易操作 , 泛用 于不 适宜 容 广 用 微处理 器 或为 了减 轻微 处理器 的负担 的 系统

个脉 冲, 电机 就 走 一 步 , 需要 相 序 表 、 不 高频 控 制 线 或 复 杂 的 程 序 接 I。 最后 还 介 绍 了A 9 7 典 型 应 用 电路 。 2 ' 37的

电机驱动芯片选型-步进电机和BLDC-Allegro

厂家型号描述Allegro A3901Dual Full Bridge Low Voltage Motor DriverAllegro A3916Dual DMOS Full-Bridge Motor DriverAllegro A3966Dual Full-Bridge PWM Motor DriverAllegro A3967Microstepping Driver with TranslatorAllegro A3977Microstepping DMOS Driver with TranslatorAllegro A3979Microstepping DMOS Driver with TranslatorAllegro A3981K Automotive, Programmable Stepper DriverAllegro A3982DMOS Stepper Motor Driver with TranslatorAllegro A3983DMOS Microstepping Driver with TranslatorAllegro A3984DMOS Microstepping Driver with TranslatorAllegro A3985Digitally Programmable Dual Full-Bridge MOSFET DriverAllegro A3987DMOS Microstepping Driver with TranslatorAllegro A3988Quad DMOS Full Bridge PWM Motor DriverAllegro A3989Bipolar Stepper and High Current DC Motor DriverAllegro A3992DMOS Dual Full-Bridge Microstepping PWM Motor DriverAllegro A3995DMOS Dual Full Bridge PWM Motor DriverAllegro A3998Dual DMOS Full Bridge Motor Driver With Serial Port Control and Allegro A4970Dual Full-Bridge PWM Motor DriverAllegro A4975Full-Bridge PWM Microstepping Motor DriverAllegro A4979Microstepping Programmable Stepper Motor Driver With Stall Dete Allegro A4980K Automotive, Programmable Stepper DriverAllegro A4982DMOS Microstepping Driver with Translator And Overcurrent Prote Allegro A4983DMOS Microstepping Driver with TranslatorAllegro A4984DMOS Microstepping Driver with Translator And Overcurrent Prote Allegro A4985DMOS Microstepping Driver with Translator And Overcurrent Prote Allegro A4986DMOS Dual Full-Bridge PWM Motor Driver With Overcurrent Protect Allegro A4987DMOS Dual Full-Bridge PWM Motor Driver with Overcurrent Protect Allegro A4988DMOS Microstepping Driver with Translator And Overcurrent Prote Allegro A4989Dual Full-Bridge MOSFET Driver with Microstepping Translator Allegro A4990K Automotive Dual Full Bridge DriveAllegro A4992K Automotive Stepper DriverAllegro A4993Automotive Stepper Motor DriverAllegro A5976Microstepping DMOS Driver with TranslatorAllegro A5977Microstepping DMOS Driver with TranslatorAllegro A5979Microstepping DMOS Driver with TranslatorAllegro A5984DMOS Microstepping Driver with Translator And Overcurrent Prote Allegro A5985DMOS Microstepping Driver with Translator And Overcurrent Prote Allegro A5988Bipolar Stepper and High-Current DC Motor DriverAllegro A5989Bipolar Stepper and High-Current DC Motor DriverAllegro A5990Quad DMOS Full-Bridge PWM Motor DriverAllegro AMT49701Quad DMOS Full-Bridge PWM Motor DriverAllegro AMT49702Dual DMOS Full-Bridge Motor Driver后缀“K”表示汽车级产品(通过 AEC-Q100 认证)下列器件已停产:A3986, A3972电桥数量峰值输出电流最大电源电压接口位置反馈最小电源电压Parallel External 2.5 5.50.4Full-Bridge x2 Parallel External 2.7151Full-Bridge x2 PH/EN External 4.75300.75Full-Bridge x2 Translator (Step/DIR)External 4.75300.85Full-Bridge x2 Translator (Step/DIR)External835 2.5Full-Bridge x2 Translator (Step/DIR)External835 2.5Full-Bridge x2 SPI,Translator (Step/DIR)External732 1.4Full-Bridge x2 Translator (Step/DIR)External8352Full-Bridge x2 Translator (Step/DIR)External8352Full-Bridge x2 Translator (Step/DIR)External8352Full-Bridge x2 SPI External1250Full-Bridge x2 Translator (Step/DIR)External850 1.5Full-Bridge x2 Parallel External836 1.2Full-Bridge x4 Parallel,PH/EN External836 1.2Full-Bridge x4 SPI External1550 1.5Full-Bridge x2 PH/EN External836 2.4Full-Bridge x4 SPI External950 1.5Full-Bridge x2 Parallel External7.45451Full-Bridge x2 Parallel External550 1.5Full-Bridge x1 SPI,Translator (Step/DIR)External750 1.5Full-Bridge x2 SPI,Translator (Step/DIR)External 3.332 1.4Full-Bridge x2 Translator (Step/DIR)External8352Full-Bridge x2 Translator (Step/DIR)External835 2.5Full-Bridge x2 Translator (Step/DIR)External8352Full-Bridge x2 Translator (Step/DIR)External8351Full-Bridge x2 Parallel External8352Full-Bridge x2 Parallel External8351Full-Bridge x2 Translator (Step/DIR)External8352Full-Bridge x2 Translator (Step/DIR)External1250 1.2Full-Bridge x2 Parallel External632 1.4Full-Bridge x2 SPI,Translator (Step/DIR)External 3.832 1.4Full-Bridge x2 SPI,Translator (Step/DIR)Open Loop 3.532 1.4Full-Bridge x2 Translator (Step/DIR)External840 2.8Full-Bridge x2 Translator (Step/DIR)External840 2.8Full-Bridge x2 Translator (Step/DIR)External840 2.8Full-Bridge x2 Translator (Step/DIR)External8402Full-Bridge x2 Translator (Step/DIR)External8402Full-Bridge x2 Parallel External840 1.6Full-Bridge x4 Parallel External840 1.6Full-Bridge x4 Parallel External840 1.6Full-Bridge x4 Parallel External4181Full-Bridge x4 Parallel External 3.5151Full-Bridge x2封装DFN Consumer,Industrial QFN Consumer,Industrial SOIC Consumer,Industrial SOIC Consumer,Industrial TSSOP Consumer,Industrial TSSOP Consumer,Industrial TSSOP AutomotiveSOIC Consumer,Industrial TSSOP Consumer,Industrial TSSOP Consumer,Industrial TSSOP Consumer,Industrial TSSOP Consumer,Industrial QFN,LQFP Consumer,Industrial QFN Consumer,Industrial DIP,TSSOP Consumer,Industrial QFN Consumer,Industrial QFN Consumer,Industrial SOIC Consumer,Industrial DIP,SOIC Consumer,Industrial TSSOP Consumer,Industrial TSSOP AutomotiveQFN,TSSOP Consumer,Industrial QFN Consumer,Industrial QFN,TSSOP Consumer,Industrial QFN,TSSOP Consumer,Industrial QFN,TSSOP Consumer,Industrial QFN,TSSOP Consumer,Industrial QFN Consumer,Industrial TSSOP Consumer,Industrial TSSOP AutomotiveTSSOP AutomotiveTSSOP AutomotiveTSSOP Consumer,Industrial TSSOP Consumer,Industrial TSSOP Consumer,Industrial QFN,TSSOP Consumer,Industrial QFN Consumer,Industrial QFN Consumer,Industrial QFN Consumer,Industrial QFN Consumer,Industrial,Of QFN Consumer,Industrial TSSOP AutomotiveFull, Half Step Resolution, Single Supply, Sleep ModeInternal PWM Current Control, Single Supply, OCP Protection, Fault Output, Sleep Mode, Parallel Ope Internal PWM Current Control, Full, Step Resolution, Sleep ModeInternal PWM Current Control, Full, Half, 1/4, 1/8 Step Resolution, Sleep Mode, Automatic Mixed Dec Internal PWM Current Control, Full, Half, 1/4, 1/8 Step Resolution, Sleep Mode, Automatic Mixed Dec Internal PWM Current Control, Full, Half, 1/4, 1/16 Step Resolution, Sleep Mode, Automatic Mixed De Internal PWM Current Control, Full, Half, 1/4, 1/16 Step Resolution, OCP Protection, Programable Fa Internal PWM Current Control, Full, Half Step Resolution, Sleep Mode, Automatic Mixed DecayInternal PWM Current Control, Full, Half, 1/4, 1/8 Step Resolution, Sleep Mode, Automatic Mixed Dec Internal PWM Current Control, Full, Half, 1/4, 1/16 Step Resolution, Sleep Mode, Automatic Mixed De Internal PWM Current Control, Full, Half, 1/4, 1/16 Step Resolution, Sleep Mode, Mixed Decay Internal PWM Current Control, Full, Half, 1/4, 1/16 Step Resolution, OCP Protection, Sleep Mode, Au Internal PWM Current Control, Full, Half, 1/4 Step Resolution, Automatic Mixed DecayInternal PWM Current Control, Full, Half, 1/4 Step Resolution, Automatic Mixed DecayInternal PWM Current Control, Full, Half, 1/4, 1/16 Step Resolution, OCP Protection, Sleep Mode, Mi Internal PWM Current Control, Automatic Mixed DecayInternal PWM Current Control, Full, Half, 1/4, 1/8 Step Resolution, OCP Protection, Sleep Mode, 3.3 Internal PWM Current Control, Full, Half Step Resolution, Sleep ModeInternal PWM Current Control, Full, Half, 1/4, 1/8 Step Resolution, Automatic Mixed DecayInternal PWM Current Control, Full, Half, 1/4, 1/16 Step Resolution, OCP Protection, Programable Fa Internal PWM Current Control, Full, Half, 1/4, 1/16 Step Resolution, OCP Protection, Programable Fa Internal PWM Current Control, Full, Half, 1/4, 1/16 Step Resolution, OCP Protection, Sleep Mode, Au Internal PWM Current Control, Full, Half, 1/4, 1/8, 1/16 Step Resolution, Sleep Mode, Automatic Mix Internal PWM Current Control, Full, Half, 1/4, 1/8 Step Resolution, OCP Protection, Sleep Mode, Aut Internal PWM Current Control, Full, Half, 1/4, 1/8 Step Resolution, OCP Protection, Sleep Mode, Aut Internal PWM Current Control, Full, Half, 1/4 Step Resolution, OCP Protection, Sleep Mode, Mixed De Internal PWM Current Control, Full, Half, 1/4 Step Resolution, OCP Protection, Sleep Mode, Mixed De Internal PWM Current Control, Full, Half, 1/4, 1/8, 1/16 Step Resolution, OCP Protection, Sleep Mod Internal PWM Current Control, Full, Half, 1/4, 1/16 Step Resolution, Sleep Mode, Mixed Decay Internal PWM Current Control, Full Step Resolution, Single Supply, Sleep ModeInternal PWM Current Control, Full, Half, 1/4, 1/16 Step Resolution, Single Supply, OCP Protection, Integrated Current Sense, Internal PWM Current Control, 50V Transient compatible, Full, Half, 1/4, Internal PWM Current Control, Full, Half, 1/4, 1/16 Step Resolution, OCP Protection, Fault Output, Internal PWM Current Control, Full, Half, 1/4, 1/8 Step Resolution, OCP Protection, Sleep Mode, Aut Internal PWM Current Control, Full, Half, 1/4, 1/16 Step Resolution, OCP Protection, Sleep Mode, Au Internal PWM Current Control, Full, Half, 1/4, 1/8, 1/16, 1/32 Step Resolution, Single Supply, OCP Internal PWM Current Control, Full, Half, 1/4, 1/8, 1/16, 1/32 Step Resolution, Single Supply, OCP Internal PWM Current Control, Full, Half, 1/4 Step Resolution, Single Supply, OCP Protection, Sleep Internal PWM Current Control, Full, Half, 1/4 Step Resolution, Single Supply, OCP Protection, Sleep Adaptive Percent fast decay, Adjustable off time, Internal PWM Current Control, Full, Half, 1/4 Ste Internal PWM Current Control, Full, Half, 1/4 Step Resolution, Single Supply, OCP Protection, Sleep Internal PWM Current Control, Half step resolution, Single Supply, OCP Protection, Fault Output, SlParallel OperationAutomatic Mixed DecayAutomatic Mixed Decay, Automatic Mixed Decaytion, Programable Fault Output, Sleep Mode, Advanced DiagnosticsMixed DecayAutomatic Mixed Decay, Automatic Mixed Decay, Mixed Decaytion, Sleep Mode, Automatic Mixed Decaytion, Sleep Mode, Mixed Decayion, Sleep Mode, 3.3/5.0V LDO, Mixed Decayixed Decaytion, Programable Fault Output, Sleep Mode, Advanced Diagnosticstion, Programable Fault Output, Sleep Mode, Advanced Diagnosticstion, Sleep Mode, Automatic Mixed DecayMode, Automatic Mixed Decayion, Sleep Mode, Automatic Mixed Decayion, Sleep Mode, Automatic Mixed DecaySleep Mode, Mixed DecaySleep Mode, Mixed Decayrotection, Sleep Mode, Automatic Mixed Decay, Mixed Decayply, OCP Protection, Programmable Fault Output, Sleep Mode, Mixed Decaye, Full, Half, 1/4, 1/16 Step Resolution, OCP Protection, Programable Fault Output, Sleep Mode, Advanced Dia tion, Fault Output, Sleep Mode, Automatic Mixed Decayion, Sleep Mode, Automatic Mixed Decaytion, Sleep Mode, Automatic Mixed DecaySingle Supply, OCP Protection, Fault Output, Sleep Mode, Adaptive Percent Fast DecaySingle Supply, OCP Protection, Fault Output, Sleep Mode, Adaptive Percent Fast DecayCP Protection, Sleep Mode, Mixed DecayCP Protection, Sleep Mode, Mixed DecayFull, Half, 1/4 Step Resolution, Single Supply, OCP Protection, Sleep Mode, Mixed Decay, diagnostic output CP Protection, Sleep Mode, Mixed Decayon, Fault Output, Sleep Modeep Mode, Advanced Diagnostic d Decay, diagnostic output。

A3967中文资料

A3967SLTB微步进驱动器带转换器负载电源电压,V BB ................ 30 V输出电流,I OUT连续.....................±750毫安的*峰值.................................±850毫安的逻辑电源电压,V CC ........... 7.0 V逻辑输入电压范围,V IN(T W> 30纳秒)............. -0.3 V至+7.0 V(T W <30纳秒)................ -1 V至+7.0 V检测电压,V SENSE ............... 0.68 V参考电压,V REF ................ V CC包装功耗,P D ................................. 见第8页工作温度范围,T A ............................. -20°C至+85°C结温,T J ......... +150°C存储温度范围,T S ......................... -55°C至+150°C*输出电流额定值可能是有限的,占空比,环境温度,和热下沉。

在任何条件下,不超过规定的额定电流或结温度为150℃。

A3967SLB是一个完善的微电机驱动器内置逻辑器。

它的设计操作双极步进电机全,半,季,和第八步模式,输出驱动能力30 V和±750毫安性。

A3967SLB包括一个固定关断时间的电流调节器,有能力在慢,快,或混合电流衰减模式。

此电流衰减控制方案以减少可听到的电流噪音,增加步进精确度,并减少功耗。

A3967SLB通过简单的“步进”输入中输入一个脉冲电动机将产生一个步骤(全,半,四分之一,或八分,这取决于两个逻辑输入)。

有没有相位顺序表、高频率控制线或复杂的界面。

A3977步进集成驱动

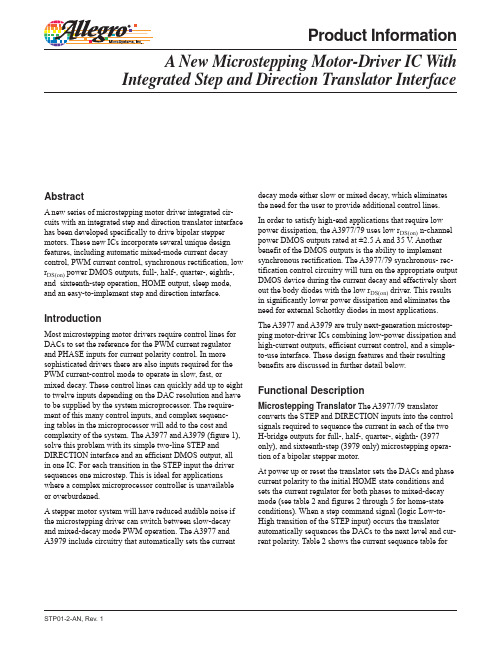

Product Information A New Microstepping Motor-Driver IC With Integrated Step and Direction Translator InterfaceAbstractA new series of microstepping motor driver integrated circuits with an integrated step and direction translator interface has been developed specifically to drive bipolar stepper motors. These new ICs incorporate several unique design features, including automatic mixed-mode current decay control, PWM current control, synchronous rectification, low rDS(on) power DMOS outputs, full-, half-, quarter-, eighth-, and sixteenth-step operation, HOME output, sleep mode, and an easy-to-implement step and direction interface.decay mode either slow or mixed decay, which eliminates the need for the user to provide additional control lines. In order to satisfy high-end applications that require low power dissipation, the A3977/79 uses low rDS(on) n-channel power DMOS outputs rated at ±2.5 A and 35 V. Another benefit of the DMOS outputs is the ability to implement synchronous rectification. The A3977/79 synchronous- rectification control circuitry will turn on the appropriate output DMOS device during the current decay and effectively short out the body diodes with the low rDS(on) driver. This results in significantly lower power dissipation and eliminates the need for external Schottky diodes in most applications. The A3977 and A3979 are truly next-generation microstepping motor-driver ICs combining low-power dissipation and high-current outputs, efficient current control, and a simpleto-use interface. These design features and their resulting benefits are discussed in further detail below.IntroductionMost microstepping motor drivers require control lines for DACs to set the reference for the PWM current regulator and PHASE inputs for current polarity control. In more sophisticated drivers there are also inputs required for the PWM current-control mode to operate in slow, fast, or mixed decay. These control lines can quickly add up to eight to twelve inputs depending on the DAC resolution and have to be supplied by the system microprocessor. The requirement of this many control inputs, and complex sequencing tables in the microprocessor will add to the cost and complexity of the system. The A3977 and A3979 (figure 1), solve this problem with its simple two-line STEP and DIRECTION interface and an efficient DMOS output, all in one IC. For each transition in the STEP input the driver sequences one microstep. This is ideal for applications where a complex microprocessor controller is unavailable or overburdened. A stepper motor system will have reduced audible noise if the microstepping driver can switch between slow-decay and mixed-decay mode PWM operation. The A3977 and A3979 include circuitry that automatically sets the currentFunctional DescriptionMicrostepping Translator The A3977/79 translator converts the STEP and DIRECTION inputs into the control signals required to sequence the current in each of the two H-bridge outputs for full-, half-, quarter-, eighth- (3977 only), and sixteenth-step (3979 only) microstepping operation of a bipolar stepper motor. At power up or reset the translator sets the DACs and phase current polarity to the initial HOME state conditions and sets the current regulator for both phases to mixed-decay mode (see table 2 and figures 2 through 5 for home-state conditions). When a step command signal (logic Low-toHigh transition of the STEP input) occurs the translator automatically sequences the DACs to the next level and current polarity. Table 2 shows the current sequence table forSTP01-2-AN, Rev. 1LOGIC SUPPLY VDD REF. SUPPLY REF DAC + RC1 PWM LATCH BLANKING 4 STEP MIXED DECAY PWM TIMER SENSE1 UVLO AND FAULT 2V REGULATOR BANDGAPVREGCP2CP1 VCP LOAD SUPPLYCHARGE PUMPVBB1 DMOS H BRIDGEVCPOUT 1A OUT1BMS 1 MS 2 HOME SLEEP VPFD SRCONTROL LOGICGATE DRIVERESETTRANSLATORDIRSENSE1DMOS H BRIDGE VBB2OUT 2A OUT2BENABLE PWM TIMER PFD RC 2 4 PWM LATCH BLANKING MIXED DECAY+ DAC-SENSE2Dwg. FP-050-2Figure 1. A3977 Functional Block DiagramTable 1 MS1 MS2L L H H HMicrostepping ResolutionFull Step (2 phase) Half Step Quarter Step Sixteenth Step (3979) Eighth Step (3977)motor operation (DIRECTION input logic Low). For the reverse operation the DIRECTION input is set to logic High and the translator reverses the sequence through table 2. The DAC outputs are used by the PWM current regulator to set the trip point of the current output of each phase. The (micro)step resolution is set by inputs MS1 and MS2 as shown in table 1.L H L H HSTP01-2-AN, Rev. 1Allegro MicroSystems, Inc. 115 Northeast Cutoff Worcester, Massachusetts 01615-0036 U.S.A. 1.508.853.5000; 2Internal PWM Current Control Each H-bridge is controlled by a fixed-off-time PWM current-control circuit that limits the load current to a desired value (ITRIP). Initially, a diagonal pair of source and sink DMOS outputs are enabled and current flows through the motor winding and the current-sense resistor (RS) as shown in figure 6. When the voltage across RS equals the DAC output voltage, the current-sense comparator resets the PWM latch, which turns off either the source drivers (slow-decay mode) or both the source and sink drivers (fast-decay or mixed-decay modes) and the current recirculates as shown in figure 6. During this recirculation the current decreases until the fixed-off time expires. The appropriate output drivers are enabled again, the motor-winding current again increases, and the PWM cycle is repeated. The maximum value of current limiting is set by the selection of RS and the voltage at the VREF input with a transconductance function approximated by: ITRIPmax = VREF / (8RS ) The DAC output reduces the VREF output to the current-sense comparator in precise steps (see table 2 for % ITRIPmax at each step). ITRIP = (% ITRIPmax / 100) × ITRIPmax The internal PWM current-control circuitry uses a one shot to control the time the driver(s) remain(s) off. The one shot off-time, toff , is determined by the selection of an external resistor (RT) and capacitor (CT) connected from the RC timing terminals to ground. The off time is approximated by: toff = RTCT In addition to the fixed-off time of the PWM control circuit, the CT component sets the comparator blanking time. This function blanks the output of the current-sense comparator when the outputs are switched by the internal current-control circuitry. The comparator output is blanked to prevent false over-current detections due to reverse-recovery currents of the clamp diodes, and / or switching transients related to the capacitance of the load. This blanking feature eliminates the low-pass filter between RS and theFigure 6. Current Pathscurrent-sense comparator that is required on most PWM-current regulators. The blank time, tBLANK , can be approximated by: tBLANK = 1900 CT Mixed-Decay Operation Automatic mixed decay is a key feature of the A3977/79. Automatic mixed-decay operation optimizes the current chopping mode in order to achieve the best sinusoidal current waveform for microstepping. Slow decay (figure 7) has the advantage of minimum current ripple. However, when microstepping at higher step rates, slowdecay chopping may fail to properly regulate current on the falling slope of the sine wave when current is decreasing. This is a result of motor BEMF overriding the voltage applied to the motor, forcing the current to increase during the decay period. Figure 8 is a scope plot of motor current that illustrates the limitations of slow-decay chopping. This distortion in the current will cause increased audible noise in the motor.STP01-2-AN, Rev. 1Allegro MicroSystems, Inc. 115 Northeast Cutoff Worcester, Massachusetts 01615-0036 U.S.A. 1.508.853.5000; 3Table 2. Step SequencingHome microstep position at Step Angle 45º; DIR = H; 360° = 4 full steps(A3977 (A3979 only) only) Phase 1 Phase 2 Full 1/2 1/4 1/8 1/16 Current Current Step Step Step Step Step Step [% Itripmax] [% Itripmax] Angle # # # # # (%) (%) (º) 1 1 1 1 100.00 0.00 0.0 2 2 2 3 4 1 2 3 5 6 4 7 8 3 5 9 10 6 11 12 2 4 7 13 14 8 15 16 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31 32 99.52 98.08 95.69 92.39 88.19 83.15 77.30 70.71 63.44 55.56 47.14 38.27 29.03 19.51 9.80 0.00 –9.80 –19.51 –29.03 –38.27 –47.14 –55.56 –63.44 –70.71 –77.30 –83.15 –88.19 –92.39 –95.69 –98.08 –99.52 9.80 19.51 29.03 38.27 47.14 55.56 63.44 70.71 77.30 83.15 88.19 92.39 95.69 98.08 99.52 100.00 99.52 98.08 95.69 92.39 88.19 83.15 77.30 70.71 63.44 55.56 47.14 38.27 29.03 19.51 9.80 5.6 11.3 16.9 22.5 28.1 33.8 39.4 45.0 50.6 56.3 61.9 67.5 73.1 78.8 84.4 90.0 95.6 101.3 106.9 112.5 118.1 123.8 129.4 135.0 140.6 146.3 151.9 157.5 163.1 168.8 174.4 32 16 31 30 4 8 15 29 28 14 27 26 7 13 25 24 12 23 22 3 6 11 21 20 10 19 18 (A3977 (A3979 only) only) Phase 1 Phase 2 Full 1/2 1/4 1/8 1/16 Current Current Step Step Step Step Step Step [% Itripmax] [% Itripmax] Angle # # # # # (%) (%) (º) 5 9 17 33 –100.00 0.00 180.0 34 35 36 37 38 39 40 41 42 43 44 45 46 47 48 49 50 51 52 53 54 55 56 57 58 59 60 61 62 63 64 –99.52 –98.08 –95.69 –92.39 –88.19 –83.15 –77.30 –70.71 –63.44 –55.56 –47.14 –38.27 –29.03 –19.51 –9.80 0.00 9.80 19.51 29.03 38.27 47.14 55.56 63.44 70.71 77.30 83.15 88.19 92.39 95.69 98.08 99.52 –9.80 –19.51 –29.03 –38.27 –47.14 –55.56 –63.44 –70.71 –77.30 –83.15 –88.19 –92.39 –95.69 –98.08 –99.52 –100.00 –99.52 –98.08 –95.69 –92.39 –88.19 –83.15 –77.30 –70.71 –63.44 –55.56 –47.14 –38.27 –29.03 –19.51 –9.80 185.6 191.3 196.9 202.5 208.1 213.8 219.4 225.0 230.6 236.3 241.9 247.5 253.1 258.8 264.4 270.0 275.6 281.3 286.9 292.5 298.1 303.8 309.4 315.0 320.6 326.3 331.9 337.5 343.1 348.8 354.4STP01-2-AN, Rev. 1Allegro MicroSystems, Inc. 115 Northeast Cutoff Worcester, Massachusetts 01615-0036 U.S.A. 1.508.853.5000; 4STEP INPUTHOME OUTPUTSLOW DECAYMIXED DECAYSLOW DECAYMIXED DECAY100% 70.7% 38.3%PHASE 1 CURRENTFigure 2. A3977 Eighth-Step (Microstepping) Operation–38.3% –70.7% –100%MS1 = MS2 = H, DIR = HMIXED DECAYSLOW DECAYMIXED DECAYSLOW DECAY100% 70.7% 38.3%PHASE 2 CURRENT–38.3% –70.7% –100%Dwg. WK-004-12STEP INPUTNOTE – Refer to table 2 for complete phase current level at each step.HOME OUTPUTSLOW DECAYMIXED DECAYSLOW DECAYMIXED DECAY100% 70.7% 38.3%PHASE 1 CURRENTFigure 3. A3977 Quarter-Step Operation–38.3% –70.7% –100%MS1 = L, MS2 = H, DIR = HMIXED DECAYSLOW DECAYMIXED DECAYSLOW DECAY100% 70.7% 38.3%PHASE 2 CURRENT–38.3% –70.7% –100%Dwg. WK-004-13STP01-2-AN, Rev. 1Allegro MicroSystems, Inc. 115 Northeast Cutoff Worcester, Massachusetts 01615-0036 U.S.A. 1.508.853.5000; 5STEP INPUTHOME OUTPUTMIXED DECAY SLOW DECAY SLOW DECAY SLOW DECAY MIXED DECAY MIXED DECAY SLOW DECAY MIXED DECAY100% 70.7%PHASE 1 CURRENTFigure 4. A3977 Half-Step OperationMS1 = H, MS2 = L, DIR = H–70.7% –100%SLOW DECAY MIXED DECAY SLOW DECAY MIXED DECAY SLOW DECAY MIXED DECAY MIXED DECAY SLOW DECAY100% 70.7%PHASE 2 CURRENT70.7% –100%Dwg. WK-004-14NOTE – Refer to table 2 for complete phase current level at each step.STEP INPUTHOME OUTPUTSLOW DECAY70.7%PHASE 1 CURRENTFigure 5. A3977 Full-Step OperationMS1 = MS2 = L, DIR = H–70.7%SLOW DECAY70.7%PHASE 2 CURRENT–70.7%Dwg. WK-004-15STP01-2-AN, Rev. 1Allegro MicroSystems, Inc. 115 Northeast Cutoff Worcester, Massachusetts 01615-0036 U.S.A. 1.508.853.5000; 6I TRIP SLOW DECAY MIXED DECAY FAST DECAY t FDt OFFDwg. WP-031-4Figure 7. Current-Decay WaveformsFast decay (figure 7) solves the current-regulation problem of slow decay. With almost the full supply across the motor winding it has the ability to quickly get the current out of the winding. The disadvantage of fast decay is the increased current ripple, which in turn causes increased motor heating. Mixed decay (figure 7) splits the fixed-off time of the PWM cycle into fast and then slow decay. When the current reaches ITRIP , the device will go into fast-decay mode until the voltage on the RC terminal decays to the voltage on the PFD terminal (VPFD ). The time that the device operates in fast decay is approximated by: tFD = RTCTln( 0.6VDD / VPFD ) After this fast-decay portion (tFD), the device will switch to slowdecay mode for the remainder of the fixed-off time period. The result is low current ripple, but with increased bandwidth to track the ideal sine wave for microstepping. Although mixed decay improves microstepping performance it will still have higher current ripple than slow decay. The best solution is to use a slow decay on the increasing slope of the sine wave and mixed decay on the falling slope of the sine wave output, which the A3977/97 does automatically. When a step-command signal occurs on the STEP input the translator automatically sequences the DACs to the next level. If the new DAC output level is lower than the previous level then the decay mode for that H-bridge will be set by the voltage level on theFigure 8. Slow-Decay Motor CurrentPFD input (fast, slow, or mixed decay). If the new DAC level is equal or higher to the previous level then the decay mode for that H-bridge will be slow decay (see figures 2 thru 5). Figure 9 is a scope plot of the A3977 motor current with slow decay on the rising slope and mixed decay on the falling slope. For comparison, included is a motor current scope plot (figure 10) of the A3977 set to 100% fast decay on the falling slope of the sine wave and slow decay on the rising slope.Figure 9. Mixed-Decay Motor CurrentSTP01-2-AN, Rev. 1Allegro MicroSystems, Inc. 115 Northeast Cutoff Worcester, Massachusetts 01615-0036 U.S.A. 1.508.853.5000; 7VBBDRIVE CURRENT RECIRCULATION (SLOW-DECAY MODE) RECIRCULATION (FAST-DECAY MODE)Dwg. EP-006-52RSFigure 10. Fast-Decay Motor CurrentFigure 11. Current Paths with Synchronous Rectification EnabledSynchronous Rectification When a PWM off cycle is triggered, by a bridge disable command or internal fixed-off time cycle, load current will recirculate according to the decay mode selected by the control logic (figure 6). The A3977/79 synchronous rectification (SR) feature will turn on the appropriate DMOS devices during the current decay and effectively short out the body diodes with the low rDS(on) driver (figure 11). In fastdecay synchronous rectification mode the voltage across RS is monitored to prevent reverse conduction. Just before the recirculation current reaches zero all of the DMOS devices are turned off and current flows through the body diodes. In a typical stepper-motor application the motor driver IC is in current-decay (recirculation) mode for a higher percentage of the PWM cycle compared to the on time. This means that most of the power dissipation is a result of the forward-voltage drop of the internal body diode of the power DMOS. This is illustrated by the first order power calculation of output power dissipation in slowdecay recirculation mode with and without synchronous rectification enabled for the A3979.Assume: I = ILOAD = 1.5 A, and rDS(on) = on resistance of the sink DMOS transistors = 0.22 ohm, and VF = forward voltage drop of the sink DMOS body diodes = 1.4 V. With synchronous rectification enabled: PD = I2 ( rDS(on) + rDS(on) ) = 1.52 (0.22 + 0.22) = 0.99 W. With synchronous rectification disabled: PD = ( IVF ) + ( I2 (rDS(on) ) = (1.5 × 1.4) + (1.52 × 0.22) = 2.595 W. The power dissipation reduction by using the A3977’s synchronous rectification feature can eliminate the need for external Schottky diodes in most stepper-motor applications thereby saving the cost and board space for these components.STP01-2-AN, Rev. 1Allegro MicroSystems, Inc. 115 Northeast Cutoff Worcester, Massachusetts 01615-0036 U.S.A. 1.508.853.5000; 8Logic Control The A3977/79 SLEEP input is used to minimize power consumption when not in use. This disables much of the internal circuitry including the output DMOS, regulator, and charge pump. Total logic plus motor supply current in sleep mode is <40 μA. Logic Low will put the device into sleep mode; logic High will allow normal operation and starts up the device in the home position. The A3977/79 sleep-mode feature is critical to new designs requiring low off-state current draw. The ENABLE and RESET inputs turn on or off all of the DMOS outputs. Translator inputs are independent of the ENABLE input state so the outputs can be disabled and then stepped to a defined microstep state and then reenabled in this position. The RESET input resets the translator to the home state. The HOME output is a logic output indicator of the initial state of the translator. At power up, the translator is reset to the home state. (See figures 2 through 5 for home state conditions). The HOME output-current level is common to all four microstepping levels in the A3977/79. It can be used as a control input to indicate that the microstepping resolution can be changed at this step without causing a current and therefore torque disturbance to the motor. Protection Circuitry An under-voltage lockout circuit protects the A3977/79 from potential shoot-through currents when the motor supply voltage is applied before the logic supply voltage. All outputs are disabled until the logic supply voltage is above 2.7 V; the control logic is then able to correctly control the state of the outputs. Thermal protection circuitry turns off all the power outputs if the junction temperature exceeds 165°C. As with most integrated thermal shutdown circuits, this is intended only to protect the A3977/79 from failure due to excessive junction temperature and will not necessarily protect the IC from output short circuits. Normal operation is resumed when the junction temperature has decreased by about 15°C.Packaging The A3977/79 is offered in two power packages, a 44-lead plastic power PLCC package (A3977SED) and a 28-lead TSSOP package with exposed thermal pad (A3977SLP and A3979SLP). The 44-lead PLCC has four copper batwing tabs for maximum heat transfer and a thermal resistance of 32°C/W. The 28-lead TSSOP measures only 9.7 mm × 4.4 mm × 0.9 mm and has a thermal resistance of 38°C/W. The TSSOP package is less than 1/4 the size of the PLCC package yet it can achieve close to the same thermal resistance. This is an important advantage in applications that have extreme space constraints.CONCLUSIONAllegro’s new microstepping motor driver ICs, A3977 and A3979, with integrated step and direction translator interface offers several features resulting in application benefits. The A3977/79 features automatic mixed-mode current-decay control, PWM current control, synchronous rectification, low rDS(on) power DMOS outputs, full-, half-, quarter-, eighth-, and sixteenth-step operation, home output, sleep mode, and an easyto-implement step and direction interface. With the A3977 and A3979, Allegro has produced high performance and cost-effective solutions for the next generation of stepper motor drivers.This paper was originally presented at the PCIM 2001 Conference, PowerSystems World, Rosemont, IL on September 10, 2001. Reprinted by permission. Insertion material regarding the A3979 added August 2010.STP01-2-AN, Rev. 1Allegro MicroSystems, Inc. 115 Northeast Cutoff Worcester, Massachusetts 01615-0036 U.S.A. 1.508.853.5000; 9。

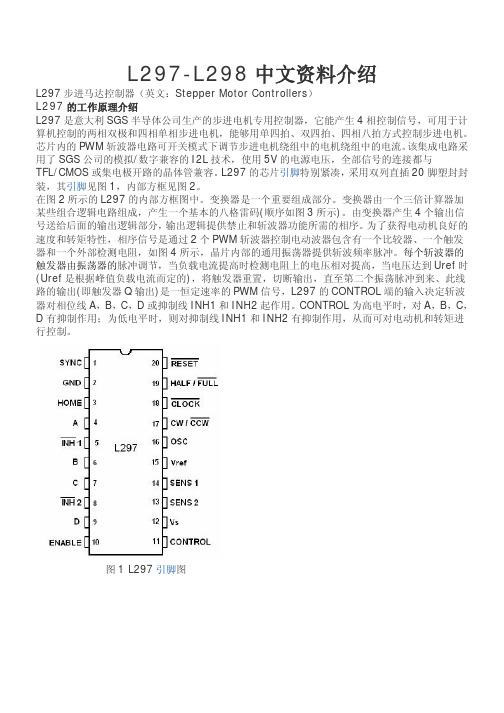

L297_L298中文资料

Unit 单位

Vs

Supply voltage 电源电压

10

V

Vi

Input signals 输入信号

7

V

Ptot

Total power dissipation 总功率耗散(Tamb = 70℃)

1

W

Tstg, Tj Storage and junction temperature 储存和结温

-40 to + 150 ℃

Ptot

Total Power Dissipation (Tcase=75℃)总功率耗散(Tcase=75℃)ຫໍສະໝຸດ 25WTop

Junction Operating Temperature 结工作温度

–25 to 130 ℃

Tstg,Tj

Storage and Junction Temperature 储存温度

图 9 L298 引脚图

图 10 L298 内部逻辑图 L298 ABSOLUTE MAXIMUM RATINGS 绝对最大额定值:

Symbol 符 号

Parameter 参数

单 Value 数值 位

VS

Power Supply 电源

50

V

VSS

Logic Supply Voltage 电源电压

7

Sense B

SEN2 分别为两个 H 桥的电流反馈脚,不用时可以直接接地

2;3 4;5

Out 1; Out 2 1Y1、1Y2 输出端

4

6

VS

功率电源电压,此引脚与地必须连接 100nF 电容器

5;7 7;9

Input

1; 1A1、1A2 输入端,TTL 电平兼容

设计报告

简易自动电阻测试仪设计报告摘要:本系统对于不同的量程分别采用恒流源测阻电路、分压法测阻电路和惠更斯桥I/V 变换测阻电路进行电阻测量,充分的发挥出不同电路不同量程的工作特点,并且在软件上进行了校准。

本自动电阻测试仪恒流源以及稳压电路由CA3140、TL431等元器件实现,由ATmega128高速单片机为主控制器,通过其内部自带10位AD 转换器的A/D 转换,对被测电阻两端电压信号进行采样,把连续信号离散化,然后通过LCD 液晶显示屏显示电阻的大小。

该自动测试仪能够较精确的测量1Ω—10M Ω范围内的电阻,其测量误差为±1%,是一个简单易用的电阻测试仪方案。

该系统有,能够自动换档,筛选电阻,并且绘制电阻变化曲线。

实现了测量准确度为±(1%读数+2 字)的三位有效数字显示的简易自动电阻测试仪。

通过偏置电源的改进提高了精度,又通过软件算法的改进再次提高了精度,对22个范围在0~10M 电阻的反复测试,证明了该系统测量精度的明显改善(见表3)。

关键词:A Tmega128 稳压源 恒流源 继电器 电阻分压原理1、系统方案:1、1方案描述 被测电阻 4.7半周克条电阻步进马达模拟放大电路数据采集系统电源图1 系统硬件图简易自动电阻测试仪由5大部分构成:(如图1)1、电源向检测电路提供+-12V ,+5V 模拟电源和+5V 数字电源,模拟地与数字地被光耦隔离。

2、模拟放大电路有三部分构成,第一部分是100Ω档的恒流源测阻电路,第二部分是1K Ω,10K Ω分压法测阻电路,第三部分是1M Ω.档的惠更斯桥I/V 变换测阻电路。

3、步进马达采用信农200步,每步1.8度。

驱动器采用A3977八细分驱动电路。

4、数据采集系统采用ATMEGA128L 单片机。

5、LCD240641、2比较与选择对于电阻的测试方法,一般可以从以下几个方面入手:1、四线测电阻法:为减少接触电阻对测量结果的影响,用一对线通电流(接触电阻对电流的测量无影响),用另一对线测电位(通过的电流很少,接触电阻对电位的影响可忽略)。

A3977

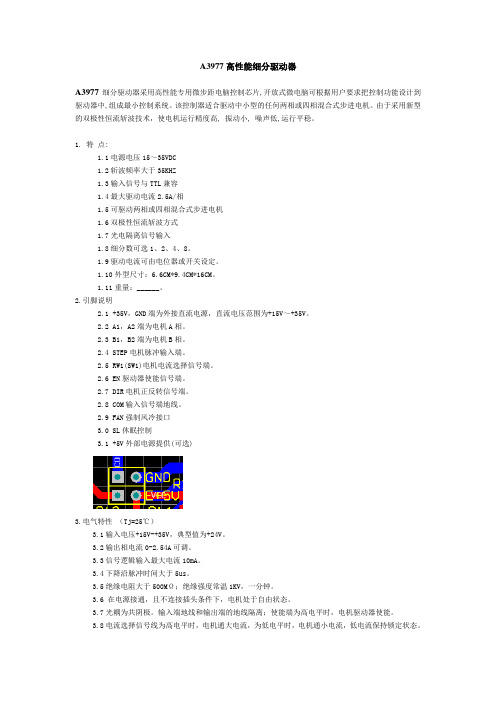

A3977高性能细分驱动器A3977细分驱动器采用高性能专用微步距电脑控制芯片,开放式微电脑可根据用户要求把控制功能设计到驱动器中,组成最小控制系统。

该控制器适合驱动中小型的任何两相或四相混合式步进电机。

由于采用新型的双极性恒流斩波技术,使电机运行精度高, 振动小, 噪声低,运行平稳。

1. 特点:1.1电源电压15~35VDC1.2斩波频率大于35KHZ1.3输入信号与TTL兼容1.4最大驱动电流2.5A/相1.5可驱动两相或四相混合式步进电机1.6双极性恒流斩波方式1.7光电隔离信号输入1.8细分数可选1、2、4、8。

1.9驱动电流可由电位器或开关设定。

1.10外型尺寸:6.6CM*9.4CM*16CM。

1.11重量:______。

2.引脚说明2.1 +35V,GND端为外接直流电源,直流电压范围为+15V~+35V。

2.2 A1,A2端为电机A相。

2.3 B1,B2端为电机B相。

2.4 STEP电机脉冲输入端。

2.5 RW1(SW1)电机电流选择信号端。

2.6 EN驱动器使能信号端。

2.7 DIR电机正反转信号端。

2.8 COM输入信号端地线。

2.9 FAN强制风冷接口3.0 SL休眠控制3.1 +5V外部电源提供(可选)3.电气特性(Tj=25℃)3.1输入电压+15V-+35V,典型值为+24V。

3.2输出相电流0-2.54A可调。

3.3信号逻辑输入最大电流10mA。

3.4下降沿脉冲时间大于5us。

3.5绝缘电阻大于500MΩ;绝缘强度常温1KV,一分钟。

3.6 在电源接通,且不连接插头条件下,电机处于自由状态。

3.7光耦为共阴极。

输入端地线和输出端的地线隔离;使能端为高电平时,电机驱动器使能。

3.8电流选择信号线为高电平时,电机通大电流,为低电平时,电机通小电流,低电流保持锁定状态。

3.9当驱动器长时间以高于2A的电流工作时,建议更换大一点的散热片或安装风扇。

3.10 为可靠起见,电机连线最好使用直径0.75以上的电缆。

全自动贴片机电动飞达电控模块研制

全自动贴片机电动飞达电控模块研制作者:何善印来源:《科技与创新》2017年第11期摘要:简要阐述了电动飞达在贴片机上的应用优势,介绍了电动飞达的机构,重点论述了飞达电控模块方案,对比采用AVR单片机和ARM7控制方案,分析了2种方案的优缺点及其具体应用注意事项,以期为日后的相关工作提供参考。

关键词:电动飞达;AVR单片机;ARM7;电控模块中图分类号:TM910.6 文献标识码:A DOI:10.15913/ki.kjycx.2017.11.112随着电子工业的飞速发展,贴片设备已被广泛应用于大规模电子产品组装生产上,分为自动和手动2种,而全自动贴片机是电子组装行业的发展方向。

供料器FEEDER(飞达)是贴片机的一个重要部件,目前,供料器基本采用的是气动工作方式,就是行业所说的气动飞达。

随着电子产品的发展,要求贴片机向速度更快、精度更高和柔性连接模块化发展。

气动飞达是纯机械结构,各型号间不能替换,速度和精度都不能满足全自动贴片机发展的要求,而电动飞达就是替代气动飞达的产品。

目前,进口高端贴片机使用电动飞达。

1 电动飞达的优点1.1 提高产能电子马达可以微调进给料距离,解决机械飞达使用中不同步贴装的问题,节约了大量的换料和调机时间。

1.2 节约成本使用机械飞达,容易因磁化、气缸不良等原因引发工作误差。

而电动飞达精度高,能够有效解决贴片机贴片零件翻件、侧立、送料不到位、抛料等问题。

1.3 通用性电动飞达用单片机控制,可以通过调整工作参数用于不同型号的贴片机上。

1.4 高安全性机械飞达加装保护装置,结构复杂、难实现,而电动飞达是电气控制的,容易加装保护装置,能够避免因外部问题而造成的设备维修损失。

1.5 人机对话电动飞达可以实时监控每支飞达的贴装数量,可作为设备数据库分析使用。

2 电动飞达的结构2.1 飞达的主要结构飞达包括变速皮带、马达、齿轮、卷取齿轮、加块和控制电路板等部分。

2.2 飞达端口说明飞达采用14Pin易插式插头与机台连接,端口通讯协议如下:引脚1为(24 V)外部供电24 V;引脚2为(NC)空脚;引脚3为(GND)外部供电0 V;引脚4为(NC)空脚;引脚5为(CHECK)飞达状态指示,上电默认低电平,当自动吐料几个后至为高电平;引脚6为(WRITE)写飞达数据控制,高电平有效,与PLUS同时为高电平时,可修改飞达内部数据;引脚7为(PLUS)进给脉冲,高电平有效;引脚8为(RUN)运行指示,飞达运转中输出低电平,待机时高电平;引脚9为(ALM)故障输出,飞达有故障时输出低电平;引脚10为(CONT)飞达插入确认,连接飞达插入保护开关,插入后与GND短接;引脚11为(GND)外部供电0 V;引脚12为(TXD)串口数据发送,TTL电平,逻辑反向;引脚13为(RXD)串口数据接收,TTL电平,逻辑反向;引脚14为(FG)地线,连接外壳。

A3977SED-T中文资料

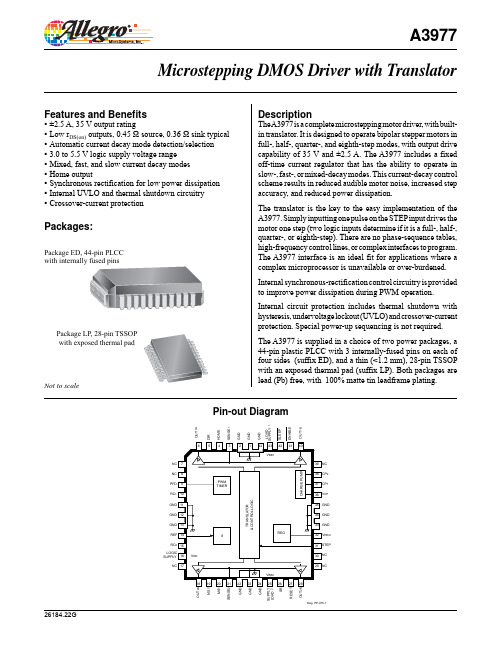

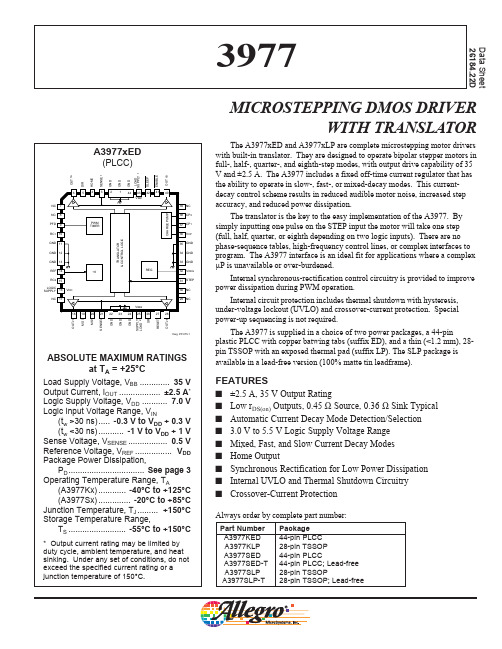

A3977

Microstepping DMOS Driver with Translator

Features and Benefits

▪ ±2.5 A, 35 V output rating ▪ Low rDS(on) outputs, 0.45 Ω source, 0.36 Ω sink typical ▪ Automatic current decay mode detection/selection ▪ 3.0 to 5.5 V logic supply voltage range ▪ Mixed, fast, and slow current decay modes ▪ Home output ▪ Synchronous rectification for low power dissipation ▪ Internal UVLO and thermal shutdown circuitry ▪ Crossover-current protection

Output current rating may be limited by duty cycle, ambient temperature, and heat sinking. Under any set of conditions, do not exceed the specified current rating or a junction temperature of 150°C. Range K Range S

MIXED DECAY

4

PWM TIMER

DMOS H BRIDGE

PWM TIMER

4

PWM LATCH

BLANKING

MIXED DECAY

两相混合式步进电机及其驱动技术

▪ 一般称单四拍和双四拍工作方式为整步距方式; 单、双八拍工作方式为半步距方式。

▪ 步进电机中定子磁场和转子磁场旳相互作用产生 转矩:

▪ 定子磁势IW(安匝),I为相电流,W为绕组匝 数。

▪ 转子磁势是由转子磁钢产生旳,它是一种常数。 ▪ 所以当定子线圈匝数、转子磁钢磁性能及定、

ia

AB

BA AB BA

t

ib

t 图6-8

▪ 整步运营时,绕组电流每90°电角度转过一种整步距。

▪ 四细分时电流电角度为 90/4=22.5 °。 以22.5°旳角

度递增从0°到360°共有16个电角度;所相应旳cos和

sin值求出并整量化后作成数据表放在存储器中。

31

32

D/A转换器

T1

T2

D1 D2

A0

u D0

B

A1

u D1

A

A2 A3

u D2

B

u D3

A

A4

A4接地时,可选通00H~0FH之 间旳十六个地址。该 地址空间存

储了循环旳单、双八拍运动方式 旳数据表 A4接5V时,可选通10H~1FH 之间旳十六个地址。该地址空间 存储了循环旳双四拍运营方式2旳3 数据表。

3)功率放大—单电压驱动方式

T1

Us

T2

D1

D2

电流放大

ia A BAB

t

uA

T3

A

A

T4

uA

ib

D3

D4

t

Vi -

Vg

+

单稳

图6-6

a

b

c

i

d

雕刻机使用说明

3040雕刻机使用说明2,本机是针对旋转轴比速1:6首先装好MACH3软件,根据以下说明设好参数,然后装上电气箱插上电源.数据线和USB,如果软件装对,打开软件主轴不转,为正确.因为数据受控制,如果打开软件主轴会转说明参数没设对或软件未装好.请客户认真仔细看以下说明.首先要看一下光盘的雕刻机接线图,步进电机从上往下最上是Z轴,中间是X轴,最下是Y轴(在这里特别要说明,长期使用要经常检验,步进电机线不能短路,控制板电源线不要接反,或路板。

机床发货时线都接好的,所以客户只要插上就可以用了,要6孔对6针,插对插正)新手使用时特注意:1.收到雕刻机后先看光盘资料。

2.然后需要一台25针的台式电脑,25针直接从主板上出来的台式机,先装MACH3软件,注意装时有360或杀毒软件的,先把360或杀毒软件的删了,再装MACH3,MACH3具体安装看下面说明。

3.装好后电脑重起,开机过程,先开电脑,后开软件,最后开电气箱,关机刚好相反。

先关电气箱后关软件,最后关电脑。

4.参数全部设好后,新手试机,看是否装对,能手动控制XYZ和主轴,说明装对了,先要学会手动操作,然后学会自动操,手动操作时注意这二处是绿灯才可进行5.平时加工时主轴开到最高速8000转加工,别低速加工。

6,特别注意点,电气箱通电后不要拔插步进电机接头,只有关机后才可以7.习惯,晚上不加工产品睡前把电气箱关了,哈哈,这是我自已的习惯8,XYZ的步进电机都是可以改变方向的,下面参数中有说到,这里我说一下,电机输出那里,674523后面的钩和叉就是改变方向的,很多软件编程出来的Z轴方向刚好相反,客户在用时首先要确认Z轴方向正确了在进行,然后雕刻字时比如阴阳字雕刻也是改变步进电机方向得到的。

注意事项:1.机器使用前应该在滑道光轴和丝杠上滴一些机油,减少磨损延长磨损件的使用寿命。

2.由于该机器是电脑控制机械设备,电机都具有一定的力矩,具有伤害性。

使用时注意安全,刀具要夹紧。

基于AISG2

基于AISG2.0协议的电调天线远程控制单元的设计实现放大器放大器放大器放大器等和射频信号相关的ALD设备。

本系统中的AISG通信接口电路。

由于天线一般都分布在相对较高而且空旷的地带,因而RCU通信接口的防雷功能必不可少。

本通信接口电路的防雷部分包括气体放电管、PTC和TVS三部分。

气体放电管构成第一道防雷保护,PTC和TVS作为第二道防线,进一步保证了通信接口的防雷性能。

考虑到所有的RET控制器都是挂在空中,最后通过基站单点接到大地,不存在大地电位差,因而采用了非隔离的方案。

2.2 电机控制模块电机控制驱动模块的核心是Allegro公司的步进电机驱动芯片A3977。

该芯片具有1/2、1/4及1/8等微步模式。

本系统中通过软件配置使MS1为高电平、MS2为低电平,电机工作在半步模式,MCU每发400个脉冲电机转动一圈。

A3977输出驱动器容量为35 V、2.5 A,内部包括一个固定停机时间电流稳压器,该稳压器可在低、快或混合衰减模式下工作,从而可以有效降低电机噪音,增加步进精确度并减少功率耗散。

2.3 存储模块存储模块主要包括天线相关的参数存储和RCU固件存储。

天线参数存储采用铁电存储器FM24LC16,其中包括产品序列号、天线参数、天线配置数据和移相器配置数据等。

选用铁电存储器的主要原因是:AISG协议中规定,RCU收到基站的命令后,必须在10 ms之内发出回应帧,否则就认为通信超时,这就要求向存储器中写入天线参数的命令必须在10 ms内完成;考虑到执行程序的时间消耗,在天线数据较多的情况下,普通的EEPROM无法满足要求;铁电存储器相比于EEPROM写入速度快,写入过程无需等待,可以满足这一要求。

RCU固件存储则采用了μPSD单片机的内部Flash。

利用μPSD单片机内部特有的Flash结构,将正在执行的固件和更新的固件都存储在单片机的片内Flash中,从而省去了外部存储器,既节省了BOM成本,又提高了产品的可靠性和安全性。

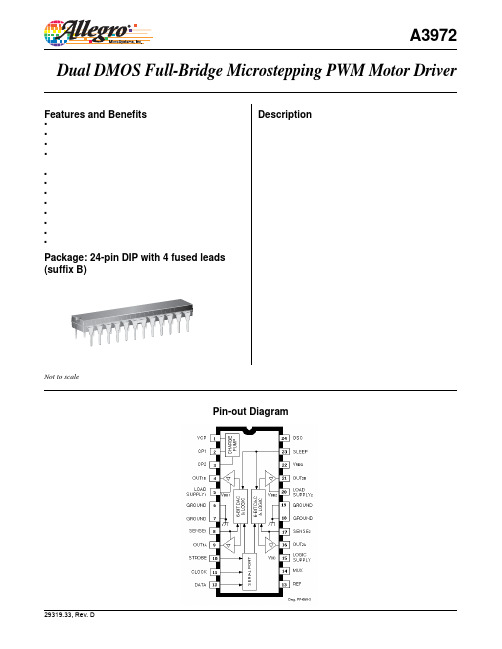

A3972微步电机驱动器说明书

A3972Selection GuidePart Number PackingA3972SB-T15 pieces/tubeAbsolute Maximum RatingsCharacteristic Symbol Notes Rating Units Load Supply Voltage V BB50V Output Current*I OUT±1.5A Logic Supply Voltage V DD7.0V Logic Input Voltage Range V IN–0.3 to V DD + 0.3V Reference Voltage V REF3V Sense Voltage (DC)V S500mV Package Power Dissipation P D 3.1W Operating Ambient Temperature T A Range S–20 to 85ºC Junction Temperature T J150ºC Storage Temperature T stg–55 to 150ºC *Output current rating may be limited by duty cycle, ambient temperature, and heat sinking. Under any set of conditions, do not exceed the specifi ed current rating or a junction temperature of 150°C.FUNCTIONAL BLOCK DIAGRAMELECTRICAL CHARACTERISTICS at T A = +25°C, V BB = 50 V, V DD = 5.0 V, V S = 0.5 V,f PWM < 50 kHz (unless otherwise noted).LimitsMax.Typ.UnitsConditions Min.Characteristic SymbolTestLoad Supply Voltage Range V BB Operating 15 — 50 VDuring sleep mode 0 — 50 VLogic Supply Voltage Range V DD Operating 4.5 5.0 5.5 VLoad Supply Current I BB f PWM < 50 kHz — — 8.0 mAOperating, outputs disabled — — 6.0 mASleep or idle mode — — 20 μALogic Supply Current I DD f PWM < 50 kHz — — 12 mA10—mA—OutputsoffIdle mode (D0 = 1, D18 = 0) — — 1.5 mASleep mode — — 100 μAOutput DriversμAOutput Leakage Current I DSS V OUT = V BB —50<1.0V OUT = 0 V — <-1.0 -50 μAOutput On Resistance r DS(on)Source driver, I OUT = –1.5 A — 0.5 0.55 ΩSink driver, I OUT = 1.5 A — 0.315 0.35 ΩBody Diode Forward Voltage V F Source diode, I F = 1.5 A — — 1.2 VSink diode, I F = 1.5 A — — 1.2 VControl LogicLogic Input Voltage V IN(1) 2.0 — — VV IN(0)— — 0.8 VLogic Input Current I IN(1)V IN = 2.0 V — <1.0 20 μAI IN(0)V IN = 0.8 V — <-2.0 -20 μAOSC Input Frequency Range f OSC Divide by one 2.5 — 6.0 MHz(D0 =1, D13 = 0, D14 = 1)OSC Input Duty Cycle — 40 — 60 %Input Hysterisis ΔV IN0.20 — 0.40 Vcontinued next page ...ELECTRICAL CHARACTERISTICS at T A = +25°C, V BB = 50 V, V DD = 5.0 V, V S = 0.5 V,f PWM < 50 kHz (unless otherwise noted).LimitsMax.Typ.UnitsTestConditions Min.Characteristics SymbolControl Logic (continued)Internal Oscillator f OSC OSC shorted to ground 3.0 4.0 5.0 MHzR OSC = 51 kΩ 3.4 4.0 4.6 MHzDAC Accuracy (total error) E T Relative to DAC reference buffer — ±1/2 — LSBoutput, D0 = 0, D17 = 0Reference Input Voltage Range V REF(EXT) 0.5 — 2.6 V—mV±10 Reference Buffer Offset V OS —Reference Divider Ratio V REF/V S D0 = 0, D18 = 0 — 8.0 — —D0 = 0, D18 = 1 — 4.0 — —Reference Input Current I REF V REF = 2.0 V — — ±0.5 μAInternal Reference Voltage V REF(INT) 1.94 2.0 2.06 VGain (G m) Error (note 3) E G D0 = 0, D17 = 0,D18 = 0, DAC = 63 — 0 ±6 %D18 = 0, DAC = 31 — 0 ±9 %D18 = 1, DAC = 63 — 0 ±6 %D18 = 1, DAC = 15 — 0 ±10 %Comparator Input Offset Voltage V IO V REF = 0 V — ±5.0 — mVPropagation Delay Times t pd50% to 90%:PWM change to source on 500 800 1200 nsPWM change to source off 50 150 350 nsPWM change to sink on 500 800 1200 nsPWM change to sink off 50 150 350 nsCrossover Dead Time t dt300 700 900 nsThermal Shutdown Temperature T J— 165 — °CThermal Shutdown Hysteresis ΔT J— 15 — °C4.2V4.45UVLO Enable Threshold V UVLO IncreasingV DD 3.9UVLO Hysteresis ΔV UVLO0.05 0.10 — VNOTES: 1. Typical Data is for design information only.2. Negative current is defi ned as coming out of (sourcing) the specifi ed device terminal.3. E G = [(V REF/Range) – V S]/(V REF/Range).Serial Interface. The A3972SB is controlled via a 3-wire (clock, data, strobe) serial port. The programmable functions allow maximum fl exibility in con fi guring the PWM to the motor drive requirements. The serial data is written as two19-bit words: 1 bit to select the word and 18 bits of data. The serial data is clocked in starting with D18.Word 0 Bit AssignmentsBit Function D0 Word select = 0 D1 Bridge 1, DAC, LSB D2 Bridge 1, DAC, bit 2 D3 Bridge 1, DAC, bit 3 D4 Bridge 1, DAC, bit 4 D5 Bridge 1, DAC, bit 5 D6 Bridge 1, DAC, MSB D7 Bridge 2, DAC, LSB D8 Bridge 2, DAC, bit 2 D9 Bridge 2, DAC, bit 3 D10 Bridge 2, DAC, bit 4 D11 Bridge 2, DAC, bit 5 D12 Bridge 2, DAC, MSB D13 Bridge 1 phase D14 Bridge 2 phase D15 Bridge 1 mode D16 Bridge 2 mode D17 REF select D18 Range selectD1 – D6 Bridge 1 Linear DAC. Six-bit word sets desired current level for Bridge 1. Setting all six bits to zero disables Bridge 1, with all drivers off (See current regulation section of functional description).D7 – D12 Bridge 2 Linear DAC. Six-bit word sets desired current level for Bridge 2. Setting all six bits to zero disables Bridge 2, with all drivers off (See current regulation section of functional description).FUNCTIONAL DESCRIPTIONcontinued next page ...D13 Bridge 1 Phase. This bit controls the direction of output current for Load 1.D13 OUT 1A OUT 1B0 L H 1 H LD14 Bridge 2 Phase. This bit controls the direction of output current for Load 2.D14 OUT 2A OUT 2B 0 L H1 H L D15 Bridge 1 Mode.D15 Mode 0 Mixed-decay 1 Slow-decay D16 Bridge 2 Mode.D16 Mode 0 Mixed-decay 1 Slow-decayD17 REF Select. This bit determines the reference input for the 6-bit linear DACs. D17 Reference Voltage 0 Internal 2 V1External (3 V max)D18 G m Range Select. This bit determines the scaling factor (4 or 8) used.D18 Divider Load Current 0 1/8 I TRIP = V DAC /8R S 1 1/4 I TRIP = V DAC /4R SFor example, with a master oscillator frequency of 4 MHz, the fi xed off-time will be adjustable from 1.75 μs to 63.75 μs in increments of 2 μs.D8 – D11 Fast Decay Time. These four bits set the fast-decay portion of fi xed off-time for the internal PWM control circuitry. The fast-decay portion is de fi ned by:t fd = [(1 + N) x 8/f OSC ] - 1/f OSC where N = 0 (15)For example, with an oscillator frequency of 4 MHz, the fast-decay time will be adjustable from 1.75 μs to 31.75 μs in incre-ments of 2 μs. For t fd > t off , the device will effectively operate in fast-decay mode.D12 – D13 Oscillator Control. A 4 MHz internal oscillator is used for the timing functions and charge-pump clock. If more precise control is required, an external oscillator can be input to the OSC terminal. To accommodate a wider range of system clocks, an internal divider is provided to generate the desired MO frequency according to the following table: D13 D12 OSC 0 0 4 MHz internal clock 0 1 External clock 1 0 External clock/2 1 1 External clock/4D14 – D15 Synchronous Recti fi cation.D15 D14 Synchronous Recti fi er 0 0 Active 0 1 Disabled 1 0 Passive 1 1 Low side only The different modes of operation are in the synchronous recti fi -cation section of the functional description.D16, D17. These bits are reserved for testing and should be programmed to zero during normal operation.D18 Idle Mode. The device can be placed in a low power “idle” mode by writing a “0” to D18. The outputs will be dis-abled, the charge pump will be turned off, and the device will draw a lower load supply currrent. The undervoltage monitor circuit will remain active. D18 should be programmed high for 1 ms before attempting to enable any output driver.Word 1 Bit AssignmentsBit Function D0 Word select = 1D1 Blank-time LSBD2 Blank-time MSB D3 Off-time LSB D4 Off-time bit 1 D5 Off-time bit 2 D6 Off-time bit 3D7 Off-time MSB D8 Fast-decay time LSB D9 Fast-decay time bit 1 D10 Fast-decay time bit 2 D11 Fast-decay time MSB D12 C0 oscillator control D13 C1 oscillator control D14 SR control bit 1 D15 SR control bit 2 D16 Reserved for testing D17 Reserved for testing D18 Idle modeD1 – D2 Blank Time. These two bits set the blank time for the current-sense comparator. When a source driver turns on, a current spike occurs due to the reverse-recovery currents of the clamp diodes and/or switching transients related to distributed capacitance in the load. To prevent this current spike from er-roneously resetting the source-enable latch, the sense comparator is blanked. The blank timer runs after the off-time counter to provide the programmable blanking function. The blank timer is reset when PHASE is changed. D2 D1 Time 0 0 4/f OSC 0 1 6/f OSC 1 0 8/f OSC 1 1 12/f OSCD3 – D7 Fixed Off Time. These fi ve bits set the fi xed off-time for the internal PWM control circuitry. Fixed off-time is de fi ned by:t off = [(1 + N) x 8/f OSC ] - 1/f OSCwhere N = 0 (31)FUNCTIONAL DESCRIPTION (continued)continued next page ...V REG. This internally generated supply voltage is used to run the sink-side DMOS outputs. V REG is internally monitored and in the case of a fault condition, the outputs of the device are disabled. The V REG pin should be decoupled with a 0.22 μF capacitor to ground.Current Regulation. The reference voltage can be set by ana-log input to the REF terminal, or via the internal 2 V precision reference. The choice of reference voltage and sense resistor set the maximum trip current.I TRIPMAX = V REF/(Range x R S) Microstepping current levels are set according to the following equations:I TRIP = V DAC/(Range x R S)V DAC = [(1 + DAC) x V REF]/64where DAC input code equals 1 to 63 and Range is 4 or 8 as selected by Word 0, D18. Programming the DAC input code to zero disables the bridge, and results in minimum load current. PWM Timer Function. The PWM timer is programmable via the serial port to provide fi xed off-time PWM signals to the con-trol block. In mixed-decay mode, the fi rst portion of the off time operates in fast decay, until the fast-decay time count is reached, followed by slow decay for the rest of the fi xed off-time period. If the fast-decay time is set longer than the off-time, the device effectively operates in fast-decay mode.Oscillator. The PWM timer is based on an oscillator input, typically 4 MHz. The A3972SB can be confi gured to select ei-ther a 4 MHz internal oscillator or, if more precision is required, an external clock can be connected to the OSC terminal. If an external clock is used, three internal divider choices are select-able via the serial port to allow fl exibility in choosing f OSC, based on available system clocks. If the internal oscillator op-tion is used, the absolute accuracy is dependent on the process variation of resistance and capacitance. A precision resistor can be connected from the OSC terminal to V DD to further improve the tolerance. The frequency will be:f OSC = 204 x 109/R OSCIf the internal oscillator is used without the external resistor, the OSC terminal should be connected to ground.Sleep Mode. The input terminal SLEEP is dedicated to putting the device into a minimum current draw mode. When pulled low, the serial port will be reset to all zeros and all circuits will be disabled.Shutdown. In the event of a fault due to excessive junction temperature, or low voltage on V CP or V REG, the outputs of the device are disabled until the fault condition is removed. At power up, or in the event of low V DD, the UVLO circuit disables the drivers and resets the data in the serial port to zeros. Synchronous Rectifi cation. When a PWM off-cycle is triggered, either by a bridge disable command or internal fi xed off-time cycle, the load current will recirculate according tothe decay mode selected by the control logic. The A3972SB synchronous rectifi cation feature will turn on the appropriate MOSFET(s) during the current decay and effectively short out the body diodes with the low r DS(on) driver. This will lower power dissipation signifi cantly and can eliminate the need for external Schottky diodes for most applications.Four distinct modes of operation can be confi gured with the two serial port control bits:1. Active Mode. Prevents reversal of load current by turningoff synchronous rectifi cation when a zero current level isdetected.2. Passive Mode. Allows reversal of current but will turnoff the synchronous rectifi er circuit if the load current inver-sion ramps up to the current limit.3. Disabled. MOSFET switching will not occur during loadrecirculation. This setting would only be used with fourexternal clamp diodes per bridge.4. Low Side Only. The low-side MOSFETs will switch onduring the off time to short out the current path throughthe MOSFET body diode. With this setting, the high-sideMOSFETs will not synchronously rectify so four externaldiodes from output to supply are recommended. This mode is intended for use with high-power applications where itis desired to save the expense of two external diodes perbridge. In this mode, the sink-side MOSFETs are chopped during the PWM off time. In all other cases, the source-side MOSFETs are chopped in response to a PWM off com-mand.continued next page ...FUNCTIONAL DESCRIPTION (continued)Current Sensing.To minimize inaccuracies in sensing the IPEAKcurrent level caused by ground-trace IR drops, the senseresistor should have an independent ground return to the ground terminal of the device. For low-value sense resistors, the IR drops in the sense resistor’s PCB traces can be signi fi cant and should be taken into account. The use of sockets should beavoided as they can introduce variation in R S due to their contact resistance.Thermal Protection. Circuitry turns off all drivers when the junction temperature reaches 165°C typically. It is intended only to protect the device from failures due to excessive junction temperature and should not imply that output short circuits are permitted. Thermal shutdown has a hysteresis of approximately 15°C.Serial Port Write Timing Operation. Data is clocked into a shift register on the rising edge of CLOCK signal. Normally, STROBE will be held high, and only will be brought low to initiate a write cycle. The data is written MSB fi rst, followed by the word-select bit. Refer to serial port diagram for timing requirements.APPLICATIONS INFORMATIONA. Minimum Data Setup Time .......................................15 nsB. Minimum Data Hold Time ........................................10 nsC. Minimum Setup Strobe to Clock Rising Edge ........150 nsD. Minimum Clock High Pulse Width ...........................40 nsE. Minimum Clock Low Pulse Width ............................40 nsF. Minimum Setup Clock Rising Edge to Strobe ...........50 ns G . Minimum Strobe Pulse Width .................................150 ns H. Minimum Setup Sleep to Strobe Falling ...................50 μsLayout. The printed wiring board should use a heavy ground plane. For optimum electrical and thermal performance, the driver should be soldered directly onto the board. The ground side of R S should have an individual path to the ground pin(s) of the driver. This path should be as short as physically possible and should not have any other components connected to it. The load supply pin, V BB , should be decoupled with an electrolytic capacitor (>47 μF is recommended) placed as close to the driveras is possible.Dwg. WP-038-1B Package, 24-Pin DIPCopyright ©2000-2007, Allegro MicroSystems, Inc.The products described here are manufactured under one or more U.S. patents or U.S. patents pending.Allegro MicroSystems, Inc. reserves the right to make, from time to time, such de p ar t ures from the detail spec i f i c a t ions as may be required to per-mit improvements in the per f or m ance, reliability, or manufacturability of its products. Before placing an order, the user is cautioned to verify that the information being relied upon is current.Allegro’s products are not to be used in life support devices or systems, if a failure of an Allegro product can reasonably be expected to cause the failure of that life support device or system, or to affect the safety or effectiveness of that device or system.The in f or m a t ion in c lud e d herein is believed to be ac c u r ate and reliable. How e v e r, Allegro MicroSystems, Inc. assumes no re s pon s i b il i t y for its use; nor for any in f ringe m ent of patents or other rights of third parties which may result from its use.For the latest version of this document, visit our website:。

基于A3977--步进电机驱动电路设计

摘要随着微步进电机应用的日益广泛,其驱动电路的发展也相当迅速,各类控制芯片的功能越来越丰富,操作也越来越简便。

A3977 是一种新近开发出来、专门用于双极型步进电机的微步进电机驱动集成电路。

本文的主要内容是以A3977SED芯片为核心,设计一块步进电机驱动电路,利用protel软件设计出原理图及PCB板,最后制作成实物。

关键词:步进电机驱动 A3977 DMOS 转换目录摘要 (1)目录 (2)第一章概述 (3)1.1 步进电机概述 (3)1.2 步进电机驱动技术概述 (3)第二章驱动电路设计 (5)2.1 总体电路 (5)2.2芯片概述 (5)2.2.1 芯片特点 (6)2.2.2外形结构 (6)2.2.3方框图 (7)2.2.4引脚定义及说明 (7)第3章电路图设计 (12)3.1 原理图设计 (12)3.2 PCB板设计 (13)3.3 实验结果 (14)第4章总结+展望 (16)第一章概述1.1 步进电机概述步进电机又称脉冲电机或阶跃电机,国外一般称为Stepper motor、Stepping motor或Stepper 等。

它是一种用电脉冲信号进行控制,并将电脉冲信号转化成相应的角位移或线位移的控制电机。

它可以看作是一种特殊运行方式的同步电动机,由专用电源供给电脉冲,每输入一个脉冲,步进电机就移动一步。

这种电动机的运动形式与普通迅速旋转的电动机有一定的差别,它是步进式运动的,所以称为步进电动机。

又因其绕组上所加的电源式脉冲电压,有时也称它为脉冲电动机。

步进电机受脉冲信号控制,它的直线位移量或角位移量与电脉冲数成正比,所以电机的线速度或转速也与脉冲频率成正比,通过改变脉冲频率的高低就可以在很大的范围内调节电机的转速,并能快速起动、制动和反转。

所以,电机步距角和转速大小都不受电压波动和负载变化的影响,也不受环境条件如温度、气压、冲击和振动等影响。

它每转一周都有固定的步数,在不丢步的情况下运行,其步距误差不会长期积累。

自动窗帘说明

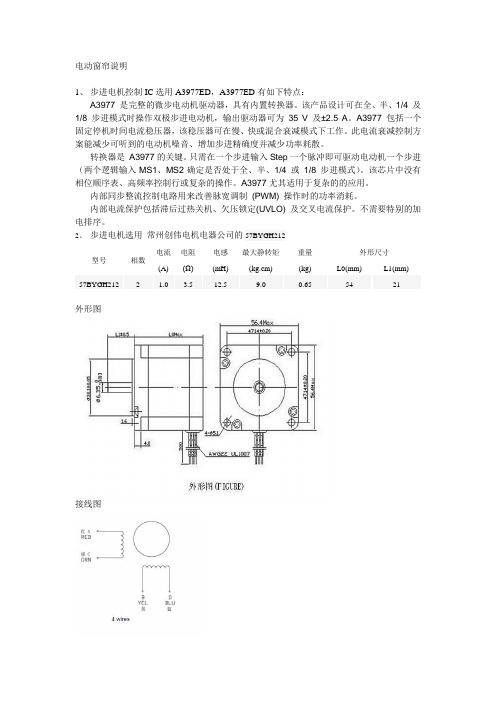

电动窗帘说明1、步进电机控制IC选用A3977ED,A3977ED有如下特点:A3977 是完整的微步电动机驱动器,具有内置转换器。

该产品设计可在全、半、1/4 及1/8 步进模式时操作双极步进电动机,输出驱动器可为35 V 及±2.5 A。

A3977 包括一个固定停机时间电流稳压器,该稳压器可在慢、快或混合衰减模式下工作。

此电流衰减控制方案能减少可听到的电动机噪音、增加步进精确度并减少功率耗散。

转换器是A3977的关键。

只需在一个步进输入Step一个脉冲即可驱动电动机一个步进(两个逻辑输入MS1、MS2确定是否处于全、半、1/4 或1/8 步进模式)。

该芯片中没有相位顺序表、高频率控制行或复杂的操作。

A3977尤其适用于复杂的的应用。

内部同步整流控制电路用来改善脉宽调制(PWM) 操作时的功率消耗。

内部电流保护包括滞后过热关机、欠压锁定(UVLO) 及交叉电流保护。

不需要特别的加电排序。

外形图接线图3、光敏电阻光敏电阻又称光导管,常用的制作材料为硫化镉,另外还有硒、硫化铝、硫化铅和硫化铋等材料。

这些制作材料具有在特定波长的光照射下,其阻值迅速减小的特性。

这是由于光照产生的载流子都参与导电,在外加电场的作用下作漂移运动,电子奔向电源的正极,空穴奔向电源的负极,从而使光敏电阻器的阻值迅速下降。

电路中选用深圳龙信达科技生产的CdS光敏电阻系列中的LXD25549光敏电阻外形尺寸4、干簧管开关选择干簧管是一种磁敏的特殊开关。

它通常由两个或三个既导磁又导电材料做成的簧片触点,被封装在充有惰性气体(如氮、氦等)或真空的玻璃管里,玻璃管内管内平行封装的簧片端部重叠,并留有一定间隙或相互接触以构成开关的常开或常闭接点。

当永久磁铁靠近干簧管时,或者由绕在干簧管上面的线圈通电后形成磁场使簧片磁化时,簧片的接点就会感应出极性相反的磁极。

由于磁极极性相反而相互吸引,当吸引的磁力超过簧片的抗力时,分开的接点便会吸合;当磁力减小到一定值时,在簧片抗力的作用下接点又恢复到初始状态。

A3977SLP中文资料