EDA技术及应用朱正伟三四五章部分课后题答案

EDA技术与应用课后习题答案

EDA技术与应用课后习题答案EDA技术与应用课后习题答案第一章1-1 EDA技术与ASIC设计和FPGA开发有什么关系? P3~4答:利用EDA技术进行电子系统设计的最后目标是完成专用集成电路ASIC 的设计和实现;FPGA和CPLD是实现这一途径的主流器件。

FPGA和CPLD通常也被称为可编程专用IC,或可编程ASIC。

FPGA和CPLD的应用是EDA技术有机融合软硬件电子设计技术、SoC(片上系统)和ASIC设计,以及对自动设计与自动实现最典型的诠释。

1-2与软件描述语言相比,VHDL有什么特点? P6答:编译器将软件程序翻译成基于某种特定CPU的机器代码,这种代码仅限于这种CPU而不能移植,并且机器代码不代表硬件结构,更不能改变CPU的硬件结构,只能被动地为其特定的硬件电路结构所利用。

综合器将VHDL程序转化的目标是底层的电路结构网表文件,这种满足VHDL设计程序功能描述的电路结构,不依赖于任何特定硬件环境;具有相对独立性。

综合器在将VHDL(硬件描述语言)表达的电路功能转化成具体的电路结构网表过程中,具有明显的能动性和创造性,它不是机械的一一对应式的“翻译”,而是根据设计库、工艺库以及预先设置的各类约束条件,选择最优的方式完成电路结构的设计。

l-3什么是综合?有哪些类型?综合在电子设计自动化中的地位是什么? P5 什么是综合? 答:在电子设计领域中综合的概念可以表示为:将用行为和功能层次表达的电子系统转换为低层次的便于具体实现的模块组合装配的过程。

有哪些类型? 答:(1)从自然语言转换到VHDL语言算法表示,即自然语言综合。

(2)从算法表示转换到寄存器传输级(RegisterTransport Level,RTL),即从行为域到结构域的综合,即行为综合。

(3)从RTL级表示转换到逻辑门(包括触发器)的表示,即逻辑综合。

(4)从逻辑门表示转换到版图表示(ASIC设计),或转换到FPGA的配置网表文件,可称为版图综合或结构综合。

EDA技术及应用习题参考答案

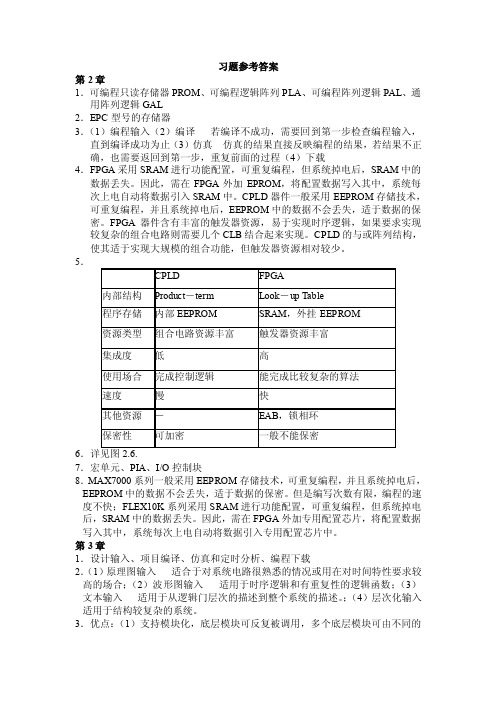

习题参考答案第2章1.可编程只读存储器PROM、可编程逻辑阵列PLA、可编程阵列逻辑PAL、通用阵列逻辑GAL2.EPC型号的存储器3.(1)编程输入(2)编译若编译不成功,需要回到第一步检查编程输入,直到编译成功为止(3)仿真仿真的结果直接反映编程的结果,若结果不正确,也需要返回到第一步,重复前面的过程(4)下载4.FPGA采用SRAM进行功能配置,可重复编程,但系统掉电后,SRAM中的数据丢失。

因此,需在FPGA外加EPROM,将配置数据写入其中,系统每次上电自动将数据引入SRAM中。

CPLD器件一般采用EEPROM存储技术,可重复编程,并且系统掉电后,EEPROM中的数据不会丢失,适于数据的保密。

FPGA器件含有丰富的触发器资源,易于实现时序逻辑,如果要求实现较复杂的组合电路则需要几个CLB结合起来实现。

CPLD的与或阵列结构,使其适于实现大规模的组合功能,但触发器资源相对较少。

5.67.宏单元、PIA、I/O控制块8.MAX7000系列一般采用EEPROM存储技术,可重复编程,并且系统掉电后,EEPROM中的数据不会丢失,适于数据的保密。

但是编写次数有限,编程的速度不快;FLEX10K系列采用SRAM进行功能配置,可重复编程,但系统掉电后,SRAM中的数据丢失。

因此,需在FPGA外加专用配置芯片,将配置数据写入其中,系统每次上电自动将数据引入专用配置芯片中。

第3章1.设计输入、项目编译、仿真和定时分析、编程下载2.(1)原理图输入适合于对系统电路很熟悉的情况或用在对时间特性要求较高的场合;(2)波形图输入适用于时序逻辑和有重复性的逻辑函数;(3)文本输入适用于从逻辑门层次的描述到整个系统的描述。

;(4)层次化输入适用于结构较复杂的系统。

3.优点:(1)支持模块化,底层模块可反复被调用,多个底层模块可由不同的设计者同时使用,提高了设计效率;(2)设计方法比较自由;(3)团队之间的合作方便灵活。

EDA技术与应用课后习题答案(6)

EDA技术与应⽤课后习题答案(6)EDA技术与应⽤课后习题答案 CLK: IN STD_LOGIC; --状态机⼯作时钟 EOC: IN STD_LOGIC; --转换状态指⽰,低电平表⽰正在转换 ALE:OUT STD_LOGIC; --8个模拟信号通道地址锁存信号 START:OUT STD_LOGIC; --转换开始信号 OE:OUT STD_LOGIC; --数据输出三态控制信号 ADDA:OUT STD_LOGIC; --信号通道最低位控制信号 LOCK0:OUT STD_LOGIC; --观察数据锁存时钟 Q:OUT STD_LOGIC_VECTOR(7 DOWNTO 0)); --8位数据输出 END ADCINT; ARCHITECTURE behav OF ADCINT IS TYPE states IS(st0,st1,St2,st3,st4); --定义各状态⼦类型 SIGNAL current_state,next_state: states:=st0; SIGNAL REGL: STD_LOGIC_VECTOR(7 DOWNTO 0); SIGNAL LOCK: STD_LOGIC;--转换后数据输出锁存时钟信号 BEGIN ADDA<='1';--当ADDA<='0',模拟信号进⼊通道IN0;当ADDA<='1',则进⼊通道INI Q<=REGL;LOCK0<=LOCK; COM: PROCESS(current_state,EOC) BEGIN --规定各状态转换⽅式 CASE current_state IS WHEN st0=> ALE<='0';START<='0';LOCK<='0';OE<='0'; next_state<=st1; --0809初始化 WHEN st1=> ALE<='1';START<='1';LOCK<='0';OE<='0'; next_state<=st2 ;--启动采样 WHEN st2=> ALE<='0';START<='0';LOCK<='0'; OE<='0'; IF(EOC='1') THEN next_state<=st3;--EOC=1表明转换结束 ELSE next_state<=st2; END IF; --转换未结束,继续等待 WHEN st3=> ALE<='0';START<='0';LOCK<='0';OE<='1'; next_state<=st4;--开启OE,输出转换好的数据 WHEN st4=> ALE<='0';START<='0';LOCK<='1';OE<='1';next_state<=st0; WHEN OTHERS=>next_state<=st0; END CASE; END PROCESS COM; REG:PROCESS(CLK) BEGIN IF(CLK'EVENT AND CLK='1') THEN current_state<=next_state; END IF; END PROCESS REG; --由信号current_state将当前状态值带出此进程:REG LATCH1: PROCESS(LOCK) --此进程中,在LOCK的上升沿,将转换好的数据锁⼊ BEGIN IF LOCK='1' AND LOCK'EVENT THEN REGL<=D; END IF; END PROCESS LATCH1; END behav; 8-5在不改变原代码功能的条件下⽤两种⽅法改写例8-2,使其输出的控制信号(ALE、START、OE、LOCK)没有⽑刺。

EDA课后答案(适用于《EDA技术及应用》)

1.1、设计集成计数器74161,设计要求如下:4-BIT BINARY UP COUNTER WITH SYNCHRONOUS LOAD AND ASYNCHRONOUS CLEAR NOTEINPUTS: CLK LDN CLRN D C B AOUTPUTS:QD QC QB QA RCO*RCO = QD & QC & QB & QALIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;USE IEEE.STD_LOGIC_UNSIGNED.ALL;ENTITY CNT4 ISPORT(CLK,LDN,CLRN : IN STD_LOGIC;D,C,B,A : IN STD_LOGIC;CARRY : OUT STD_LOGIC;QD,QC,QB,QA : OUT STD_LOGIC);END;ARCHITECTURE A OF CNT4 ISSIGNAL DATA_IN: STD_LOGIC_VECTOR(3 DOWNTO 0);BEGINDATA_IN<=D&C&B&A;PROCESS(DATA_IN,CLK,LDN,CLRN)VARIABLE CNT:STD_LOGIC_VECTOR(3 DOWNTO 0);BEGINIF CLRN='0' THENCNT:=(OTHERS=>'0');ELSIF CLK'EVENT AND CLK='1' THENIF LDN='0' THENCNT:=DATA_IN;ELSECNT:=CNT+1;END IF;END IF;CASE CNT ISWHEN "1111"=> CARRY<='1';WHEN OTHERS=> CARRY<='0';END CASE;QA<=CNT(0);QB<=CNT(1);QC<=CNT(2);QD<=CNT(3);END PROCESS;END A;1.2、设计一个通用双向数据缓冲器,要求缓冲器的输入和输出端口的位数可以由参数决定。

eda技术及应用课后习题答案

eda 技术及应用课后习题答案【篇一:eda 技术实用教程(第四版)》习题答案】ss=txt>1 习题1- 1 eda 技术与asic 设计和fpga 开发有什么关系?fpga 在asic 设计中有什么用途?p3~41- 2 与软件描述语言相比,vhdl 有什么特点? p6l- 3 什么是综合?有哪些类型? 综合在电子设计自动化中的地位是什么? p51- 4 在eda 技术中,自顶向下的设计方法的重要意义是什么? p7~101- 5 ip 在eda 技术的应用和发展中的意义是什么? p22~141- 6 叙述eda 的fpga/cpld 设计流程,以及涉及的eda 工具及其在整个流程中的作用。

(p11~13)2 习题2- 1 olmc (输出逻辑宏单元)有何功能? 说明gal 是怎样实现可编程组合电路与时序电路的。

p34~362- 2 什么是基于乘积项的可编程逻辑结构? p33~34 ,40 什么是基于查找表的可编程逻辑结构? p40~412- 3 fpga 系列器件中的lab 有何作用? p43~452- 5 解释编程与配置这两个概念。

p582- 6 请参阅相关资料,并回答问题:按本章给出的归类方式,将基于乘积项的可编程逻辑结构的pld 器件归类为cpld ;将基于查找表的可编程逻辑结构的pld 器什归类为fpga ,那么,apex 系列属于什么类型pld 器件? max ii 系列又属于什么类型的pld 器件?为什么? p54~563 习题3- 1 画出与以下实体描述对应的原理图符号元件: entity buf3s is -- 实体1: 三态缓冲器port(input:in std_logic; -- 输入端enable:in std_logic; -- 使能端output:out std_logic); -- 输出端end buf3s ;entity mux21 is -- 实体2: 2 选1 多路选择器port(in0, in1,sel: in std_logic; output:out std_logic);3- 2 图3-16 所示的是4 选1 多路选择器,试分别用if_then 语句和case 语句的表达方式写出此电路的vhdl 程序,选择控制信号s1 和s0 的数据类型为std_logic_vector; 当s1='0',s0=;'s01'='0',s0= ;'1' s1 =' 1' ,s0=和Sf='1' ,s0=时,分别执行y=a、y=b、y=c、y=d。

EDA课后题答案

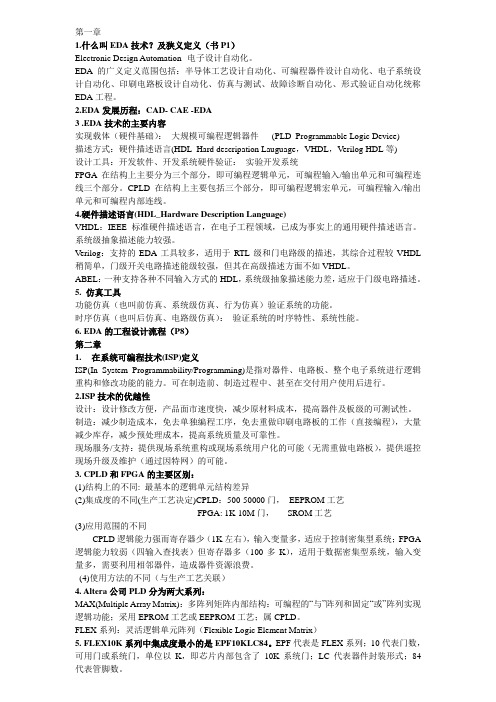

第一章1.什么叫EDA技术?及狭义定义(书P1)Electronic Design Automation--电子设计自动化。

EDA的广义定义范围包括:半导体工艺设计自动化、可编程器件设计自动化、电子系统设计自动化、印刷电路板设计自动化、仿真与测试、故障诊断自动化、形式验证自动化统称EDA工程。

2.EDA发展历程:CAD- CAE -EDA3 .EDA技术的主要内容实现载体(硬件基础):大规模可编程逻辑器件(PLD_Programmable Logic Device)描述方式:硬件描述语言(HDL_Hard descripation Lauguage,VHDL,Verilog HDL等)设计工具:开发软件、开发系统硬件验证:实验开发系统FPGA 在结构上主要分为三个部分,即可编程逻辑单元,可编程输入/输出单元和可编程连线三个部分。

CPLD在结构上主要包括三个部分,即可编程逻辑宏单元,可编程输入/输出单元和可编程内部连线。

4.硬件描述语言(HDL_Hardware Description Language)VHDL:IEEE标准硬件描述语言,在电子工程领域,已成为事实上的通用硬件描述语言。

系统级抽象描述能力较强。

Verilog:支持的EDA工具较多,适用于RTL级和门电路级的描述,其综合过程较VHDL 稍简单,门级开关电路描述能级较强,但其在高级描述方面不如VHDL。

ABEL:一种支持各种不同输入方式的HDL,系统级抽象描述能力差,适应于门级电路描述。

5. 仿真工具功能仿真(也叫前仿真、系统级仿真、行为仿真)验证系统的功能。

时序仿真(也叫后仿真、电路级仿真):验证系统的时序特性、系统性能。

6. EDA的工程设计流程(P8)第二章1.在系统可编程技术(ISP)定义ISP(In_System Programmability/Programming)是指对器件、电路板、整个电子系统进行逻辑重构和修改功能的能力。

数字电路逻辑设计朱正伟课后答案

A

B

C

F1

F2

0

0

0

0

0

0

0

1

1

0

0

1

0

1

0

0

1

1

0

1

1

0

0

1

0

1

0

1

0

1

1

1

0

0

1

1

1

1

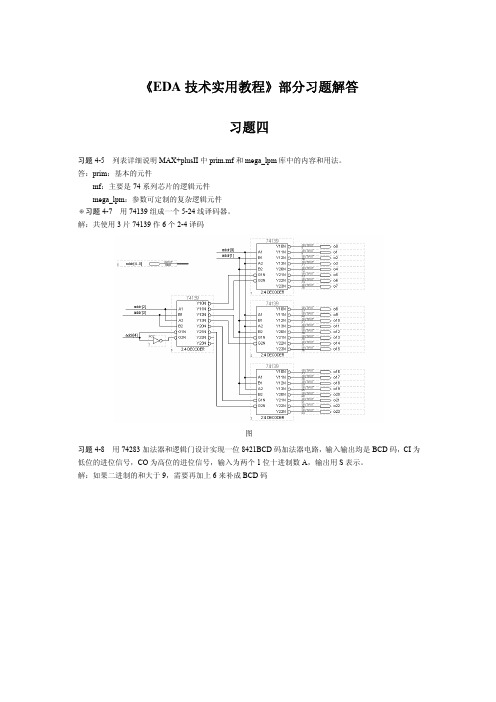

《EDA技术实用教程》习题解答

习题 5-6 根据图 5-23,写出顶层文件 MX3256.VHD 的 VHDL 设计文件。

第 1 章 概述

9

图 5-21 习题 5-4 图

解: VHDL 设计文件内容如下:

library ieee; use ieee.std_logic_1164.all;

entity exen is

port ( cl

: in std_logic;

clk0 : in std_logic;

out1 );

: out std_logic

out1 <= not tmp; end hdlarch; ⊕习题 5-5 给出 1 位全减器的 VHDL 描述。要求: (1) 首先设计 1 位半减器,然后用例化语句将它们连接起来,图 5-22 中 h_suber 是半减器,diffr 是输出差, s_out 是借位输出,sub_in 是借位输入。

解:

图 5-19 4 选 1 多路选择器

图 5-20 双 2 选 1 多路选择器

architecture hdlarch of MUXK is

signal tmp : std_logic;

begin

process(s0,a2,a3) begin

if s0 = '0' then

tmp <= a2;

else

解:用同步计数器来实现。(事实上要求设计的是一个袼雷码计数器)

考虑不同状态时,对应的 DFF 输入端的值:

EDA技术习题集及答案

第一章 EDA概述一、填空题1.2000年推出的Pentium 4微处理器芯片的集成度达——万只晶体管。

2.一般把EDA技术的发展分为——、——和——三个阶段。

3.在EDA发展的——阶段,人们只能借助计算机对电路进行模拟、预测,以及辅助进行集成电路版图编辑、印刷电路板(PcB)布局布线等工作。

4.在EDA发展的——阶段,人们可以将计算机作为单点设计工具,并建立各种单元库,开始用计算机将许多单点工具集成在一起使用。

5.EDA设计流程包括——、——、——和——四个步骤。

6.EDA的设计验证包括——、——和——三个过程。

7.EDA的设计输入主要包括——、——和———。

8.文本输入是指采用——进行电路设计的方式。

9.功能仿真是在设计输入完成之后,选择具体器件进行编译之前进行的逻辑功能验证,因此又称为——。

10.时序仿真是在选择了具体器件并完成布局、布线之后进行的时序关系仿真,因此又称为——或——。

11.当前最流行的并成为1EEE标准的硬件描述语言包括————和——。

12.采用PLD进行的数字系统设计,是基于芯片的设计或称之为——的设计。

13.硬件描述语言HDL给PLD和数字系统的设计带来了更新的设计方法和理念,产生了目前最常用的并称之为——的设计法。

14.EDA工具大致可以分为——、——、———、———和——等五个模块。

15.将硬件描述语吉转化为硬件电路的重要工具软件称为——————。

二、单项选择题1.将设计的系统或电路按照EDA开发软件要求的某种形式表示出来,并送入计算机的过程称为( )。

①设计输入②设计输出③仿真④综合2.一般把EDA技术的发展分为( )几个阶段。

①2 ②3 ③4 ④53.AHDL属于( )描述语言。

①普通硬件②行为③高级④低级4.vHDL属于( )描述语言。

①普通硬件②行为③高级④低级5.包括设计编译和检查、逻辑优化和综合、适配和分割、布局和布线,生成编程数据文件等操作的过程称为( )。

智慧树知道网课《EDA技术》课后章节测试满分答案

智慧树知道网课《EDA技术》课后章节测试满分答案绪论单元测试1【多选题】(10分)学习EDA技术这门课程的具体要求是()A.初步掌握基于FPGA的VLSI系统设计与实现的方法和技术,具备分析、解决实际问题的能力,具有较强的专业实践能力和创新能力。

B.较好地掌握应用EDA技术进行系统设计开发的方法,具备应用EDA技术进行综合性数字系统设计的初步能力,经过后续的综合应用实践,能够从事FPGA的设计与开发、SOPC的设计与开发以及ASIC 的前端设计等工作。

C.掌握EDA技术的基本概念、基础知识;了解FPGA/CPLD的结构、工作原理、性能指标及应用选择;熟练掌握硬件描述语言VHDL的编程;熟练掌握EDA技术的开发软件及EDA实验开发系统的使用。

2【多选题】(10分)学习EDA技术这门课程,我们希望达到的学习目标是()A.基本掌握ASIC的后端设计与开发B.基本掌握ASIC的前端设计与开发C.掌握一种硬件描述语言VHDLD.基本掌握SOC的设计与开发方法E.基本掌握SOPC的设计与开发方法F.熟悉FPGA的设计与开发3【多选题】(10分)EDA技术课程的学习要点是()A.以课题为中心,以研究式教学为主要形式B.抓住一个重点(硬件描述语言编程)C.掌握两个工具(FPGA/CPLD开发软件、EDA实验开发系统的使用)D.运用四种手段(案例分析、应用设计、线上学习、上机实践)E.采用五个结合(边学边用相结合、边用边学相结合、理论与实践相结合、线上与线下相结合、课内与课外相结合)第一章测试1【单选题】(10分)EDA的中文含义是()A.计算机辅助工程设计B.计算机辅助设计C.电子设计自动化2【判断题】(10分)狭义的EDA技术,就是指以大规模可编程逻辑器件为设计载体,以硬件描述语言为系统逻辑描述的主要表达方式,以计算机、大规模可编程逻辑器件的开发软件及实验开发系统为设计工具,通过有关的开发软件,自动完成用软件方式设计的电子系统到硬件系统的逻辑编译、逻辑化简、逻辑分割、逻辑综合及优化、逻辑布局布线、逻辑仿真,直至对于特定目标芯片的适配编译、逻辑映射、编程下载等工作,最终形成集成电子系统或专用集成芯片的一门新技术,或称为IES/ASIC自动设计技术。

EDA课后习题答案

图1-14 寄存器输出结构

1-7 什么是基于乘积项的可编程逻辑结构?什么是基于查找表的可编程逻辑 结构? 答:基于乘积项的可编程结构,即由可编程的“与”阵列和固定的“或”阵 列组成。 可编程的查找表(Look Up Table,LUT)结构,LUT是可编程的最小逻 辑构成单元。大部分FPGA采用基于SRAM(静态随机存储器)的查找表逻 辑形成结构,即用SRAM来构成逻辑函数发生器。一个N输入LUT可以实现N 个输入变量的任何逻辑功能,如N输入“与”、N输入“异或”等。 1-8 就逻辑宏单元而言,GAL中的OLMC、CPLD中的LC、FPGA中的LUT 和LE的含义和结构特点是什么?它们都有何异同点? 答:输出逻辑宏单元(Output Logic Macro Cell,OLMC),此结构使得 PLD器件在组合逻辑和时序逻辑中的可编程或可重构性能都成为可能。 MAX7000S系列器件包含32~256个逻辑宏单元(Logic Cell,LC),其单个 逻辑宏单元结构如图1-15所示。 LUT即可编程的查找表(Look Up Table,LUT)结构,是可编程的最小逻辑 构成单元。大部分FPGA采用基于SRAM(静态随机存储器)的查找表逻辑 形成结构,即用SRAM来构成逻辑函数发生器。一个N输入LUT可以实现N个 输入变量的任何逻辑功能,如N输入“与”、N输入“异或”等。 LE是Cyclone III FPGA器件的最基本的可编程单元,LE主要由一个4输入的 查找表LUT、进位链逻辑、寄存器链逻辑和一个可编程的寄存器构成。

《EDA技术及应用》朱正伟-三,四,五章部分课后题答案

第三章3-5设计一个4选1多路选择器,当选择输入信号分别取“00”、“01”、“10”和“11”时,输出信号分别与一路输入信号相连。

LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;ENTITY MAX4_1 ISPORT(A,B,C,D,S1,S2 : IN STD_LOGIC;Y : OUT STD_LOGIC);END ENTITY MAX4_1;ARCHITECTURE HF1 OF MAX4_1 ISSIGNAL SS : STD_LOGIC_VECTOR (0 TO 1);BEGINSS<=S2&S1;PROCESS(SS)BEGINCASE SS ISWHEN "00" => Y<=A;WHEN "01" => Y<=B;WHEN "10" => Y<=C;WHEN "11" => Y<=D;WHEN OTHERS => NULL;END CASE;END PROCESS;END HF1;3-6设计一个7人表决电路,参加表决者7人,同意为1,不同意为0,同意者过半则表决通过,绿指示灯亮;表决不通过则红指示灯亮。

设计思路:根据7人表决电路设计要求,7人中至少有4个通过才可以表决通过,故可以在程序中设置一个变量TEMP,使其在表决电路中遇1则加1,遇0则加0(设计中1表示通过,0表示不通过)。

当TEMP>=4时,表示表决通过,当TEMP<4时表决不通过。

LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;USE IEEE.STD_LOGIC_UNSIGNED.ALL;ENTITY VOTE7 ISPORT (MEN:IN STD_LOGIC_VECTOR(6 DOWNTO 0);OUTPUT: OUT BIT);END VOTE7;ARCHITECTURE BEHA VE OF VOTE7 ISBEGINPROCESS(MEN)V ARIABLE TEMP: INTEGER RANGE 0 TO 7;BEGINTEMP:=0;FOR I IN 0 TO 6 LOOPIF(MEN(I)='1')THENTEMP:=TEMP+1;ELSETEMP:=TEMP;END IF;END LOOP;CASE TEMP ISWHEN 0 TO 3 =>OUTPUT<='0';WHEN 4 TO 7 =>OUTPUT<='1';END CASE ;END PROCESS;END BEHA VE;第四章4-6试写出4选1多路选择器VHDL描述。

EDA课后习题答案

定义为Net型的变量常被综合为硬件电路中的物理连接,其特点是输出的值 紧跟输入值的变化而变化,因此常被用来表示以assign关键词引导的组合电路描 述。

形成结构,即用SRAM来构成逻辑函数发生器。一个N输入LUT可以实现N个

输1-入8 变就量逻的辑任宏何单逻元辑而功言能,,G如ALN中输的入O“LM与C”、、CNP输LD入中“的异LC或、”F等PG。A中的LUT和

LE的含义和结构特点是什么?它们都有何异同点?

答:输出逻辑宏单元(Output Logic Macro Cell,OLMC),此结构使得

综合器就是能够将一种设计表述形式自动向另一种设计表述形式转换的 计算机程序,或协助进行手工转换的程序。它可以将高层次的表述转化为低 层次的表述,可以将行为域转化为结构域,可以将高一级抽象的电路描述 (如算法级)转化为低一级的电路描述(如门级),并可以用某种特定的 “技术”(如CMOS)实现。

精选ppt课件

1-10 标志FPGA/CPLD逻辑资源的逻辑宏单元包含哪些结构? 答: CPLD( MAX7000S)系列中的 逻辑宏单元由3个功能块组成:逻辑阵列、 乘积项选择矩阵和可编程寄存器,它们可以被单独地配置为时序逻辑和组合逻 辑工作方式。其中逻辑阵列实现组合逻辑,可以给每个逻辑宏单元提供5个乘 积项。“乘积项选择矩阵”分配这些乘积项作为到“或门”和“异或门”的主 要逻辑输入,以实现组合逻辑函数;或者把这些乘积项作为宏单元中寄存器的 辅助输入:清零(Clear)、置位(Preset)、时钟(Clock)和时钟使能控制 (Clock Enable)。 FPGA(Cyclone III)器件的可编程资源主要来自逻辑阵列块LAB,而每个LAB都 由多个逻辑宏单元(Logic Element,LE)构成。LE是Cyclone III FPGA器件 的最基本的可编程单元,LE主要由一个4输入的查找表LUT、进位链逻辑、寄 存器链逻辑和一个可编程的寄存器构成。

EDA技术与应用课后习题答案(2)

EDA技术与应用课后习题答案(2)END IF;END PROCESS;PR02:PROCESS(s1)BEGINIF s1=”0” THEN outy<=a1;ELSE outy<=tmp;END IF;END PROCESS;END ARCHITECTURE ONE;END CASE;4-4.下图是一个含有上升沿触发的D触发器的时序电路,试写出此电路的VHDL设计文件。

4-4.答案LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;ENTITY MULTI ISPORT(CL:IN STD_LOGIC; --输入选择信号CLK0:IN STD_LOGIC; --输入信号OUT1:OUT STD_LOGIC);--输出端END ENTITY;ARCHITECTURE ONE OF MULTI ISSIGNAL Q : STD_LOGIC;BEGINPR01: PROCESS(CLK0)BEGINIF CLK ‘EVENT AND CLK=’1’THEN Q<=NOT(CL OR Q);ELSEEND IF;END PROCESS;PR02: PROCESS(CLK0)BEGINOUT1<=Q;END PROCESS;END ARCHITECTURE ONE;END PROCESS;4-5.给出1位全减器的VHDL描述。

要求:(1) 首先设计1位半减器,然后用例化语句将它们连接起来,图3-32中h_suber是半减器,diff是输出差,s_out是借位输出,sub_in 是借位输入。

(2) 以1位全减器为基本硬件,构成串行借位的8位减法器,要求用例化语句来完成此项设计(减法运算是 x – y - sun_in = diffr) 4-5.答案底层文件1:or2a.VHD实现或门操作LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;USE IEEE.STD_LOGIC_UNSIGNED.ALL;ENTITY or2a ISPORT(a,b:IN STD_LOGIC;c:OUT STD_LOGIC);END ENTITY or2a;ARCHITECTURE one OF or2a ISBEGINc <= a OR b;END ARCHITECTURE one;底层文件2:h_subber.VHD实现一位半减器LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;USE IEEE.STD_LOGIC_UNSIGNED.ALL;ENTITY h_subber ISPORT(x,y:IN STD_LOGIC;diff,s_out::OUT STD_LOGIC);END ENTITY h_subber;ARCHITECTURE ONE OF h_subber ISSIGNAL xyz: STD_LOGIC_VECTOR(1 DOWNTO 0); BEGINxyz <= x & y;PROCESS(xyz)BEGINCASE xyz ISWHEN "00" => diff<='0';s_out<='0';WHEN "01" => diff<='1';s_out<='1';WHEN "10" => diff<='1';s_out<='0';WHEN "11" => diff<='0';s_out<='0';WHEN OTHERS => NULL;END CASE;END PROCESS;END ARCHITECTURE ONE;顶层文件:f_subber.VHD实现一位全减器LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;USE IEEE.STD_LOGIC_UNSIGNED.ALL;ENTITY f_subber ISPORT(x,y,sub_in:IN STD_LOGIC;diffr,sub_out:OUT STD_LOGIC);END ENTITY f_subber;ARCHITECTURE ONE OF f_subber IS COMPONENT h_subberPORT(x,y:IN STD_LOGIC;diff,S_out:OUT STD_LOGIC);END COMPONENT;COMPONENT or2aPORT(a,b:IN STD_LOGIC;c:OUT STD_LOGIC);END COMPONENT;SIGNAL d,e,f: STD_LOGIC;BEGINu1: h_subber PORT MAP(x=>x,y=>y,diff=>d,s_out=>e);u2: h_subber PORT MAP(x=>d,y=>sub_in,diff=>diffr,s_out=>f);u3: or2a PORT MAP(a=>f,b=>e,c=>sub_out);END ARCHITECTURE ONE;END ARCHITECTURE ART;4-6.根据下图,写出顶层文件MX3256.VHD的VHDL设计文件。

EDA技术及应用(第2版)朱正伟复习资料

EDA技术及应用(第2版)朱正伟复习资料第一章1、EDA的定义:以计算机为工作平台,以EDA软件工具为开发环境,以硬件描述语言为设计语言,以ASIC为实现载体的电子产品自动化设计过程。

2、EDA的三大特征:硬件描述语言、系统级仿真、综合技术3、EDA的设计方法:自上而下4、EDA的核心:利用计算机完成电路设计的全程自动化5、常用的EDA工具及其作用:设计编辑器:一般支持图形输入,HDL文本输入,波形图输入等仿真器:完成行为模型的表达、电子系统的建模、逻辑电路的验证以及门级系统的测试HDL综合器:将软件描述与给定的硬件结构用某种网表文件的方式对应起来,成为相互的映射关系。

6、EDA的设计流程:设计输入(将设计的系统或电路按照EDA开发软件要求的文本方式或图形方式表示出来,并送入计算机的过程。

)第二章1、PLD的基本结构:输入缓冲器、与阵列、或阵列、输出缓冲器;电路的核心是由门电路构成的与阵列、或阵列,逻辑函数靠它们实现。

与阵列产生乘积项,或阵列产生乘积项之和。

2、PLD的分类:简单PLD:PROM:与门阵列固定,或门阵列可编程。

优点:价格低、易编程性能可预测。

不足:规模大、速度低、功耗高。

PLA:与阵列和或阵列均可编程。

特点使用灵活,运行速度慢,价格高,缺少高质量的支持软件,使用不广泛。

PAL:与阵列可编程,或阵列固定,即乘积项可若干,数目固定。

特点:性能速度较高。

有几种固定的输出结构,不同结构对应不同的型号。

GAL;即通用阵列逻辑器件,与阵列和PAL的类似,或阵列及输出寄存器则采用OLMC输出逻辑宏单元OLMC最多有8个或项,每个或项最多有32个与项。

复杂PLD:(1)CPLD-----复杂可编程逻辑器件(2)FPGA-----现场可编程门阵列(3)ISP-----在系统可编程逻辑器件3、PLD的互联结构:(1)确定型:除FPGA外的PLD器件布线每次相同。

(2)统计型:FPGA每次布线模式不同,设计者提出约束模式。

EDA课后题答案

EDA课后题答案第⼀章1.什么叫EDA技术?及狭义定义(书P1)Electronic Design Automation--电⼦设计⾃动化。

EDA的⼴义定义范围包括:半导体⼯艺设计⾃动化、可编程器件设计⾃动化、电⼦系统设计⾃动化、印刷电路板设计⾃动化、仿真与测试、故障诊断⾃动化、形式验证⾃动化统称EDA⼯程。

2.EDA发展历程:CAD- CAE -EDA3 .EDA技术的主要内容实现载体(硬件基础):⼤规模可编程逻辑器件(PLD_Programmable Logic Device)描述⽅式:硬件描述语⾔(HDL_Hard descripation Lauguage,VHDL,Verilog HDL等)设计⼯具:开发软件、开发系统硬件验证:实验开发系统FPGA 在结构上主要分为三个部分,即可编程逻辑单元,可编程输⼊/输出单元和可编程连线三个部分。

CPLD在结构上主要包括三个部分,即可编程逻辑宏单元,可编程输⼊/输出单元和可编程内部连线。

4.硬件描述语⾔(HDL_Hardware Description Language)VHDL:IEEE标准硬件描述语⾔,在电⼦⼯程领域,已成为事实上的通⽤硬件描述语⾔。

系统级抽象描述能⼒较强。

Verilog:⽀持的EDA⼯具较多,适⽤于RTL级和门电路级的描述,其综合过程较VHDL 稍简单,门级开关电路描述能级较强,但其在⾼级描述⽅⾯不如VHDL。

ABEL:⼀种⽀持各种不同输⼊⽅式的HDL,系统级抽象描述能⼒差,适应于门级电路描述。

5. 仿真⼯具功能仿真(也叫前仿真、系统级仿真、⾏为仿真)验证系统的功能。

时序仿真(也叫后仿真、电路级仿真):验证系统的时序特性、系统性能。

6. EDA的⼯程设计流程(P8)第⼆章1.在系统可编程技术(ISP)定义ISP(In_System Programmability/Programming)是指对器件、电路板、整个电⼦系统进⾏逻辑重构和修改功能的能⼒。

《EDA技术及应用》课后题解

单元一EDA技术概述1.什么是EDA技术?EDA技术的基本特征是什么?答:EDA(Electronic Design Automation,电子设计自动化)技术是电子设计工程师在计算机上完成电路的功能设计、逻辑设计、性能分析、时序测试直至PCB(印制电路板)的自动设计等。

EDA技术的基本特征是采用高级语言描述,具有系统级仿真和综合能力。

2.可编程逻辑器件有什么特点?有哪些可编程资源?答:可编程逻辑器件的主要特点1.缩短研制周期2.降低设计成本3.提高设计灵活性3.写出Altera器件中的下列英文缩写的中文含义。

LE LAB PIA EAB答:LE:逻辑单元LAB:逻辑阵列块PIA:可编程连线阵列EAB:嵌入式阵列块4.简述可编程逻辑器件的发展趋势。

答:可编程逻辑器件未来的发展将呈现以下几个方面的趋势:1)向高密度、大规模的方向发展2)向系统内可重构的方向发展3)向低电压、低功耗的方向发展4)向高速可预测延时器件的方向发展5)向混合可编程技术方向发展单元二可编程逻辑器件的设计与开发1.简述可编程逻辑器件的一般设计过程。

答:CPLD/FPGA器件的设计流程一般分为设计输入、设计实现、设计校验和编程下载4个步骤。

2.试比较可编程逻辑器件设计的常用输入方式。

答:1)原理图输入原理图是图形化的表达方式,它是利用软件中所提供的元件符号和连线来描述设计。

其特点是比较直观,便于进行接口设计和引脚锁定,容易实现仿真,便于信号的观察和电路的调整,系统运行速率较高,但当描述复杂电路时则比较烦琐。

2)硬件描述语言输入硬件描述语言输入是采用文本方式描述设计,这种方式的描述范围较宽,从简单的门电路到复杂的数字系统均可描述。

特别是在描述复杂设计时,非常简洁。

但这种描述方式不适合描述接口和连接关系,并且该输入方式必须依赖综合器,只有好的综合器才能把语言综合成优化的电路。

3.列举常用的EDA工具软件,并比较各有什么特点。

答:1)Synplify该软件是由Synplicity公司专为FPGA和CPLD开发设计的逻辑综合工具。

第EDA技术使用教程课后答案5章

KX

康芯科技

5.4 原理图输入设计方法

5. 将设计项目设置成工程和时序仿真

图5-46 加入本工程所有文件

KX

康芯科技

5.4 原理图输入设计方法

5. 将设计项目设置成工程和时序仿真

全加器工程f_adder的仿真波形 图5-47 全加器工程 的仿真波形

KX

康芯科技

5.4 原理图输入设计方法

5.4.2 应用宏模块的原理图设计 1. 计数器设计

KX

康芯科技

5.3 嵌入式逻辑分析仪使用方法

5.编译下载 启动SignalTap II进行采样与分析 6.启动SignalTap II进行采样与分析

下载cnt10.sof并准备启动 并准备启动SignalTap II 图5-39 下载 并准备启动

康芯科技

KX

5.3 嵌入式逻辑分析仪使用方法

启动SignalTap II进行采样与分析 6.启动SignalTap II进行采样与分析

图5-40 SignalTap II采样已被启动 采样已被启动

KX

康芯科技

5.3 嵌入式逻辑分析仪使用方法

II的其他设置和控制方法 7.SignalTap II的其他设置和控制方法

图5-41 SignalTap II数据窗设置后的信号波形 数据窗设置后的信号波形

KX

康芯科技

5.4 原理图输入设计方法

KX

康芯科技

5.2 引脚设置和下载

5.2.3 AS模式编程配置器件 模式编程配置器件

接口AS模式编程窗口 图5-29 ByteBlaster II接口 模式编程窗口 接口

KX

康芯科技

5.2 引脚设置和下载

5.2.4 JTAG间接模式编程配置器件 间接模式编程配置器件

EDA课后答案(适用于朱正伟《EDA技术及应用》)

1.1、设计集成计数器74161,设计要求如下:4-BIT BINARY UP COUNTER WITH SYNCHRONOUS LOAD AND ASYNCHRONOUS CLEAR NOTEINPUTS: CLK LDN CLRN D C B AOUTPUTS:QD QC QB QA RCO*RCO = QD & QC & QB & QALIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;USE IEEE.STD_LOGIC_UNSIGNED.ALL;ENTITY CNT4 ISPORT(CLK,LDN,CLRN : IN STD_LOGIC;D,C,B,A : IN STD_LOGIC;CARRY : OUT STD_LOGIC;QD,QC,QB,QA : OUT STD_LOGIC);END;ARCHITECTURE A OF CNT4 ISSIGNAL DATA_IN: STD_LOGIC_VECTOR(3 DOWNTO 0);BEGINDATA_IN<=D&C&B&A;PROCESS(DATA_IN,CLK,LDN,CLRN)V ARIABLE CNT:STD_LOGIC_VECTOR(3 DOWNTO 0);BEGINIF CLRN='0' THENCNT:=(OTHERS=>'0');ELSIF CLK'EVENT AND CLK='1' THENIF LDN='0' THENCNT:=DATA_IN;ELSECNT:=CNT+1;END IF;END IF;CASE CNT ISWHEN "1111"=> CARRY<='1';WHEN OTHERS=> CARRY<='0';END CASE;QA<=CNT(0);QB<=CNT(1);QC<=CNT(2);QD<=CNT(3);END PROCESS;END A;1.2、设计一个通用双向数据缓冲器,要求缓冲器的输入和输出端口的位数可以由参数决定。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

第三章3-5设计一个4选1多路选择器,当选择输入信号分别取“00”、“01”、“10”和“11”时,输出信号分别与一路输入信号相连。

LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;ENTITY MAX4_1 ISPORT(A,B,C,D,S1,S2 : IN STD_LOGIC;Y : OUT STD_LOGIC);END ENTITY MAX4_1;ARCHITECTURE HF1 OF MAX4_1 ISSIGNAL SS : STD_LOGIC_VECTOR (0 TO 1);BEGINSS<=S2&S1;PROCESS(SS)BEGINCASE SS ISWHEN "00" => Y<=A;WHEN "01" => Y<=B;WHEN "10" => Y<=C;WHEN "11" => Y<=D;WHEN OTHERS => NULL;END CASE;END PROCESS;END HF1;3-6设计一个7人表决电路,参加表决者7人,同意为1,不同意为0,同意者过半则表决通过,绿指示灯亮;表决不通过则红指示灯亮。

设计思路:根据7人表决电路设计要求,7人中至少有4个通过才可以表决通过,故可以在程序中设置一个变量TEMP,使其在表决电路中遇1则加1,遇0则加0(设计中1表示通过,0表示不通过)。

当TEMP>=4时,表示表决通过,当TEMP<4时表决不通过。

LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;USE IEEE.STD_LOGIC_UNSIGNED.ALL;ENTITY VOTE7 ISPORT (MEN:IN STD_LOGIC_VECTOR(6 DOWNTO 0);OUTPUT: OUT BIT);END VOTE7;ARCHITECTURE BEHA VE OF VOTE7 ISBEGINPROCESS(MEN)V ARIABLE TEMP: INTEGERRANGE 0 TO 7;BEGINTEMP:=0;FOR I IN 0 TO 6 LOOPIF(MEN(I)='1')THENTEMP:=TEMP+1;ELSETEMP:=TEMP;END IF;END LOOP;CASE TEMP ISWHEN 0 TO 3 =>OUTPUT<='0';WHEN 4 TO 7 =>OUTPUT<='1';END CASE ;END PROCESS;END BEHA VE;第四章4-6试写出4选1多路选择器VHDL描述。

选择控制信号为S1和S0,输入信号为A,B,C,D,输出信号为Y。

LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;ENTITY MUX41A ISPORT (A,B,C,D,S0,S1:IN STD_LOGIC; --输入信号Y:OUT STD_LOGIC); --输出信号END ENTITY MUX41A;ARCHITECTURE ONE OF MUX41A ISSIGNAL S:STD_LOGIC_VECTOR(1 DOWNTO 0);BEGINS<=S0&S1; --并置操作,获得二维矢量数据类型PROCESS(S0,S1,A,B,C,D) --敏感信号BEGINCASE S ISWHEN"00"=> Y<=A;WHEN"01"=> Y<=B;WHEN"10"=> Y<=C;WHEN"11"=> Y<=D;WHEN OTHERS=>NULL; --其它情况为空值END CASE; --CASE语句结束END PROCESS; --PROCESS进程语句结束END ARCHITECTURE ONE;4-7使给出1位全减器的VHDL描述,要求:首先设计1位半减器,然后用例化语句将它们连接起来。

设X为被减数,Y为减数,SUB_IN是借位输入,DIFF是输出差,SUB_OUT是借位输出。

(1.1):实现1位半减器H_SUBER(DIFF=X-Y;S_OUT=1,X<Y)LIBRARY IEEE; --半减器描述(1):布尔方程描述方法USE IEEE.STD_LOGIC_1164.ALL;ENTITY H_SUBER ISPORT( X,Y: IN STD_LOGIC;DIFF,S_OUT: OUT STD_LOGIC);END ENTITY H_SUBER;ARCHITECTURE HS1 OF H_SUBER ISBEGINDIFF <= X XOR (NOT Y);S_OUT <= (NOT X) AND Y;END ARCHITECTURE HS1;--解(1.2):采用例化实现图4-20的1位全减器LIBRARY IEEE; --1位二进制全减器顺层设计描述USE IEEE.STD_LOGIC_1164.ALL;ENTITY F_SUBER ISPORT(XIN,YIN,SUB_IN: IN STD_LOGIC;SUB_OUT,DIFF_OUT: OUT STD_LOGIC);END ENTITY F_SUBER;ARCHITECTURE FS1 OF F_SUBER ISCOMPONENT H_SUBER --调用半减器声明语句PORT(X, Y: IN STD_LOGIC;DIFF,S_OUT: OUT STD_LOGIC);END COMPONENT;SIGNAL A,B,C: STD_LOGIC; --定义1个信号作为内部的连接线。

BEGINU1:H_SUBERPORT MAP(X=>XIN,Y=>YIN, DIFF=>A, S_OUT=>B); U2:H_SUBERPORT MAP(X=>A, Y=>SUB_IN, DIFF=>DIFF_OUT,S_OUT=>C);SUB_OUT <= C OR B;END ARCHITECTURE FS1;二进制全加器,元件声明与元件例化(COMPONENT,PORT MAP)//或门LIBRARY IEEE; ;USE IEEE.STD_LOGIC_1164.ALL;ENTITY OR2A ISPORT(A,B : IN STD_LOGIC;C : OUT STD_LOGIC);END OR2A;ARCHITECTURE ART1 OF OR2A ISBEGINC<=A OR B;END ART1;//半加器;LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;ENTITY H_ADDER ISPORT(A,B : IN STD_LOGIC;CO,SO: OUT STD_LOGIC);END H_ADDER;ARCHITECTURE ART2 OF H_ADDER ISBEGINSO <= A XOR B;CO <= A AND B;END ART2;1位二进制全加器顶层设计:LIBRARY IEEE;USE IEEE.STD_LOGIC_1164。

ALL;ENTITY F_ADDER ISPORT(AIN,BIN,CIN : IN STD_LOGIC;COUT,SUM : OUT STD_LOGIC);END F_ADDER;ARCHITECTURE ART3 OF F_ADDER ISCOMPONENT H_ADDER //元件声明;PORT(A,B : IN STD_LOGIC;CO,SO: OUT STD_LOGIC);END COMPONENT;COMPONENT OR2APORT(A,B : IN STD_LOGIC;C : OUT STD_LOGIC);END COMPONENT;SIGNAL D,E,F : STD_LOGIC;BEGINU1:H_ADDER PORT MAP(AIN,BIN,D,E); //元件例化;U2:H_ADDER PORT MAP(A=>E,B=>CIN,CO=>F,SO=>SUM);U3:OR2A PORT MAP(D,F,COUT);END ART3;第五章5-1.试说明实体端口模式BUFFER和INOUT的不同之处?答: BUFFER端口:缓冲模式,具有读功能的输出模式,即信号输出到实体外部,但同时也在内部反馈使用,不允许作为双向端口使用。

而INOUT端口:双向模式,即信号的流通是双向的,既可以对此端口赋值,也可以通过此端口读入数据。

5-2.VHDL的数据对象有哪几种?它们之间有什么不同?答:VHDL的数据对象有三种:信号、变量、常量。

它们之间的的区别如下:信号赋值至少有Δ延时,而变量和常量没有;信号除当前值外,有许多相关信息,变量只有当前值,常量的值在设计实体中始终不变;进程对信号敏感而对变量及常量不敏感;信号可以是多个进程的全局信号,变量只在定义它们的顺序域可见,而常量的使用范围取决于它被定义的位置;信号是硬件连线的抽象描述信号赋值,赋值符号 <= 而变量和常量的赋值符号 :=。

5-3.说明下列各定义的意义:SIGNAL a , b , c : BIT : =’0’;CONSTANT TIME1,TIME2 : TIME : 20ns ;VARIABLE x , y , z : STD_LOGIC :=’x’;答:○1定义3个位数据类型的信号A、B、C,它们取值为0;○2定义2个时间数据类型的常量TIME1、TIME2,它们值为20NS;○3定义3个标准逻辑位 STD_LOGIC数据类型的变量X、Y、Z,它们的值是强未知的。

5-4.什么是重载函数?重载运算符有何用处?如何调用重载运算符函数?答:为了方便各种不同数据类型间的运算,VHDL允许用户对原有的基本操作符重新定义,赋予新的含义和功能,从而建立一种新的操作符,这就是重载操作符,定义这种操作符的函数成为重载函数。

重载运算符的作用是为了方便各种不同的数据类型间的运算。

要调用重载运算符函数,先要在程序包中进行函数体的定义,调用的格式如下:X <=函数名(参数1,参数2,····)参数个数和类型与所定义的函数要保持一致。