时钟树

STM32F4时钟树概述

STM32F4时钟树概述STM32F4 相对于 STM32F1 来说,时钟部分复杂了很多, STM32F4 的时钟配置,我们提供两个函数: Sys_Clock_Set 和Stm32_Clock_Init。

其中 Sys_Clock_Set 是核⼼的系统时钟配置函数,由 Stm32_Clock_Init 调⽤,实现对系统时钟的配置。

外部程序,⼀般调⽤ Stm32_Clock_Init函数来配置时钟。

sys⽂件夹中在 STM32F4 中,有 5 个最重要的时钟源,为 HSI、 HSE、 LSI、 LSE、 PLL。

其中 PLL 实际是分为两个时钟源,分别为主 PLL 和专⽤PLL。

从时钟频率来分可以分为⾼速时钟源和低速时钟源,在这 5 个中 HSI, HSE 以及 PLL 是⾼速时钟, LSI 和 LSE 是低速时钟。

从来源可分为外部时钟源和内部时钟源,外部时钟源就是从外部通过接晶振的⽅式获取时钟源,其中 HSE 和LSE 是外部时钟源,其他的是内部时钟源。

①、 LSI 是低速内部时钟, RC 振荡器,频率为 32kHz 左右。

供独⽴看门狗和⾃动唤醒单元使⽤。

②、 LSE 是低速外部时钟,接频率为 32.768kHz 的⽯英晶体。

这个主要是 RTC 的时钟源。

③、 HSE 是⾼速外部时钟,可接⽯英/陶瓷谐振器,或者接外部时钟源,频率范围为 4MHz~26MHz。

我们的开发板接的是 8M 的晶振。

HSE 也可以直接做为系统时钟或者 PLL 输⼊。

④、 HSI 是⾼速内部时钟, RC 振荡器,频率为 16MHz。

可以直接作为系统时钟或者⽤作 PLL输⼊。

⑤、 PLL 为锁相环倍频输出。

STM32F4 有两个 PLL:1)主 PLL(PLL)由 HSE 或者 HSI 提供时钟信号,并具有两个不同的输出时钟。

第⼀个输出 PLLP ⽤于⽣成⾼速的系统时钟(最⾼ 168MHz)第⼆个输出 PLLQ ⽤于⽣成 USB OTG FS 的时钟(48MHz),随机数发⽣器的时钟和 SDIO时钟。

复杂时钟树的sdc约束

复杂时钟树的sdc约束1.引言1.1 概述在本文中,我们将讨论复杂时钟树的SDC约束。

时钟树是现代集成电路系统中至关重要的部分,它负责将时钟信号从时钟源传播到整个芯片。

然而,随着芯片设计的复杂性的增加,时钟树也变得更加复杂。

复杂时钟树的问题主要包括时钟偏斜、时钟抖动、时钟峰值电流等。

这些问题可能会导致芯片的时序失效,甚至影响整个系统的性能。

因此,为了保证芯片的正常工作,需要对复杂时钟树进行有效的SDC约束。

本文的目的是探讨如何针对复杂时钟树提供适当的SDC约束。

我们将首先介绍复杂时钟树的概念,包括其结构和功能。

接着,我们将深入探讨复杂时钟树可能面临的问题,并分析其原因和影响。

在结论部分,我们将总结复杂时钟树的挑战,并提出解决这些问题的方法。

我们将探讨如何优化时钟树布线、降低时钟抖动、设计合适的时钟电路等方面的技术和方法。

本文的结构如下:引言部分将对文章进行概述,并明确文章的目的。

正文部分将详细介绍复杂时钟树的概念和问题。

结论部分将总结文章的主要内容,并提出解决复杂时钟树问题的建议。

通过阅读本文,读者将能够深入了解复杂时钟树的挑战,并学习如何制定适当的SDC约束来解决这些问题。

最终,我们希望本文能对芯片设计工程师和研究人员提供有价值的参考和指导。

文章结构部分的内容可以写成以下形式:1.2 文章结构本文将主要分为以下几个部分进行讨论:第一部分是引言部分,在引言中将对复杂时钟树的概念进行介绍,并概述本文的目的和结构。

第二部分是正文部分,将详细探讨复杂时钟树的概念、存在的问题以及挑战。

其中,复杂时钟树的概念将对其定义进行解释,而问题部分将探讨在实际设计过程中可能会遇到的困扰和难题。

第三部分是结论部分,将对复杂时钟树的挑战进行总结,并探讨解决这些问题的方法。

这部分将讨论目前存在的一些解决方案,以及可能的进一步研究方向。

通过以上结构安排,希望能够达到全面、系统地介绍复杂时钟树的问题和解决方法的目的。

读者可以根据自身需求和兴趣,选择性阅读相关章节以获得更具体和深入的内容。

数字电路设计中的时钟树设计原理

数字电路设计中的时钟树设计原理

时钟树设计原理在数字电路设计中起着至关重要的作用,它主要用于在整个芯

片中分配和传递时钟信号,保证整个系统的同步性和稳定性。

时钟信号在数字电路中被广泛应用,它决定了数据的采样时间、触发时间和稳定性,是整个系统中最重要的信号之一。

时钟树设计的主要目的是传送时钟信号到整个芯片的各个部分,并确保各个部

分同时受到相同的时钟信号,避免出现时序偏差和时序冲突。

时钟树设计需要考虑到时钟信号的频率、延迟、功耗、噪声等多方面因素,以确保整个系统的性能和稳定性。

在时钟树设计中,一般会采用层次式的结构,将时钟信号从芯片的输入端传输

到各个功能模块,并通过缓存器、分频器、中继器等组件来进行时钟信号的分配和缓存,最终保证整个系统内部各个部分的同步。

时钟树设计中需要考虑的一个重要因素是时钟分配网络的拓扑结构,不同的拓

扑结构会对时钟信号的传输速度、功耗和稳定性等方面产生影响。

常见的拓扑结构包括二叉树结构、星型结构、环状结构等,根据具体的设计需求和性能指标选择合适的拓扑结构进行时钟树设计。

此外,时钟树设计中还需要考虑时钟信号的布线与布局,以减小时钟信号在传

输过程中的延迟和功耗,提高整个系统的性能。

合理的布线和布局可以降低时钟信号的传输损耗和噪声干扰,确保时钟信号能够准确、稳定地传输到各个功能模块。

总的来说,时钟树设计原理是数字电路设计中至关重要的一环,它直接影响到

整个系统的性能和稳定性。

通过合理的时钟树设计,可以确保系统内部各个功能模块的同步运行,提高系统的可靠性和性能,是数字电路设计中不可或缺的关键步骤。

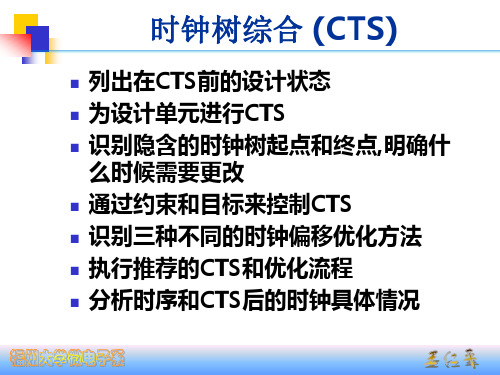

时钟树综合(1)

时钟树综合(1)时钟树综合学习背景时钟信号是数据传输的基准,他对于同步数字系统的功能、性能、稳定性起决定性作⽤。

时钟信号通常是整个芯⽚中有最⼤扇出、通过最长距离、以最⾼速度运⾏的信号。

时钟信号必须要保证在最差的条件下,关键的时序要求能够满⾜,否则对时钟信号的任何不当的控制都可能导致紊乱情况,将错误的数据信号索存到寄存器,从⽽导致系统功能的错误。

时钟信号怎么产⽣的时钟信号源⼀般是从晶体(⽯英晶体、陶瓷晶体)产⽣的。

IC设计时通常会使⽤晶体振荡器来提供时钟源信号。

⼀般会使⽤PLL加上晶体振荡器来给芯⽚内部电路提供倍频或相位的时钟信号。

时钟信号特征时钟的周期(频率)、时钟延迟、时钟信号的不确定性是时钟的三个主要特征要素。

时钟信号延迟时钟信号延迟(latency)⼜称为插⼊延迟(insertion delay), 包括时钟源插⼊延迟和时钟⽹络插⼊延迟。

时钟源插⼊延迟是来⾃系统到当前芯⽚(当前模块)时钟根节点(clock root pin)之间的延迟,时钟⽹络插⼊延迟是时钟树的延迟。

时钟信号不确定性时钟信号的不确定性主要是有时钟信号抖动引起的,时钟抖动是先天存在的,所以在时钟树综合的时候只能考虑起影响,⽆法消除。

时钟抖动是信号实际时间与理想时间的偏差,抖动中含有确定抖动成分和随机抖动的成分【】。

时钟信号偏差时钟信号偏差是指同⼀时钟达到该时钟域内的不同寄存器之间的时间偏差,也即是skew=max(|t i−t j|)产⽣时钟偏差的原因有多种:时钟源到各个时钟端点的路径长度不同、各个端点负载不同、在时钟⽹中插⼊的缓冲器不同等。

在什么时候做时钟树综合:如下图所⽰,通常在物理设计布局完成之后布线之前进⾏时钟树综合。

在此之前所有的寄存器时钟信号是由同⼀个时钟pin驱动的,具有相同的延时的理想时钟。

已经⽣成了gatelevel 的netlist已经有⼀个初步的版图规划,每个逻辑门包括时序器件都有⼀个具体的位置。

已经基于理想时钟完成了时序优化设计。

cubemx时钟树自动配置计算公式

cubemx时钟树自动配置计算公式

在CubeMX中,时钟树的自动配置是通过计算公式来确定各个时钟源、分频器和外设时钟的配置参数。

具体的计算公式可以根据不同的微控制器芯片和时钟模块而有所不同。

以下是一个示例计算公式,用于说明CubeMX中时钟树自动配置的计算原理:

1. 假设存在一个主时钟源(如HSI、HSE等)以及一些分频器和外设模块,需要配置它们的时钟频率。

2. CubeMX会基于芯片规格和用户选择的配置信息来计算每个时钟源和分频器的频率设置。

3. 假设主时钟源频率为Fclk_source。

4. 对于每个分频器,假设分频因子为N_div。

5. 对于每个外设模块,假设需要的时钟频率为F_peripheral。

6. 根据需要配置的时钟源和外设模块数量,在时钟树上设置连接关系,确定每个模块的时钟源和分频器等参数。

7. 基于这些参数,CubeMX将计算出每个分频器的具体分频因子N_div,并将每个外设模块的时钟频率配置为F_peripheral。

这只是一个示例计算公式,实际的计算公式和配置细节会根据具体的芯片和时钟模块而有所不同。

在使用CubeMX配置时钟树时,应根据具体的芯片手册和CubeMX软件的说明文档来了解更详细的配置方法和计算原理。

高性能芯片设计中的时钟树优化技术

高性能芯片设计中的时钟树优化技术时钟树是芯片设计中至关重要的一个组成部分,它负责传输时钟信号以保证芯片的正常工作。

在高性能芯片设计中,时钟树的优化技术尤为重要,可以提高芯片的稳定性、降低功耗,并保证芯片的高性能工作。

本文将介绍高性能芯片设计中的时钟树优化技术,并探讨其在芯片设计中的应用。

一、时钟树设计的重要性时钟信号是芯片工作的基准,它控制着各个功能模块的操作时序,因此时钟树设计的合理性直接影响着芯片的性能和功耗。

在高性能芯片设计中,要实现较高的工作频率和低功耗,时钟树的设计至关重要。

一个优秀的时钟树设计应具备以下几个方面的特点:1. 低时钟抖动:时钟抖动会导致芯片工作不稳定,降低性能。

通过合理的时钟树设计,可以减少时钟抖动,提高芯片的工作稳定性和可靠性。

2. 低功耗:时钟信号在芯片中的传输需要消耗功耗,较长的时钟路径和不优化的时钟树设计将导致大量的功耗浪费。

通过优化时钟树设计,可以降低功耗,提高芯片的能效。

3. 均衡和分布平衡:时钟信号在传输过程中,应该保持均衡和分布平衡,避免信号传输的不平衡导致时钟抖动和延迟问题。

二、时钟树优化的目标在高性能芯片设计中,时钟树优化的目标是实现如下几个方面的优化:1. 降低时钟路径的长度:时钟路径越短,芯片的工作频率越高,性能越好。

2. 降低时钟路径的延时:通过合理的时钟树设计,可以降低时钟路径的延时,提高芯片的工作速度。

3. 降低时钟树的功耗:优化时钟树设计,可以减少时钟信号传输过程中的功耗损耗,提高芯片的能效。

三、时钟树优化技术1. 时钟树综合:时钟树综合是时钟树优化的一项重要技术,通过对时钟信号的分析和综合,优化时钟树的结构,减少时钟路径的长度和延时。

时钟树综合工具可以根据设计需求自动完成时钟树的综合工作,生成一个最优的时钟树结构,提高芯片的性能和功耗。

2. 缓冲器插入:在时钟路径过长或者时钟分布不均衡时,可以通过插入合适的缓冲器来优化时钟树设计。

缓冲器可以提升时钟信号的驱动能力,减少时钟路径的延时和功耗。

fpga时钟树设计原则

fpga时钟树设计原则FPGA时钟树设计原则随着科技的不断发展,FPGA(Field Programmable Gate Array)在数字电路设计中的应用越来越广泛。

而时钟树作为FPGA中最重要的组成部分之一,对于整个系统的性能和稳定性起着至关重要的作用。

本文将介绍FPGA时钟树设计的原则,以帮助读者更好地理解和应用这一关键技术。

1. 时钟树的稳定性时钟信号的稳定性对于FPGA的性能至关重要。

在时钟树设计中,应采取以下措施来确保时钟信号的稳定传递:(1)降低时钟信号的抖动:抖动是指时钟信号在传输过程中产生的不稳定性。

为了降低抖动,可以采用低抖动的时钟源,并合理布局时钟信号线路,避免与其他高干扰信号线路相交。

(2)降低时钟信号的噪声:噪声是指时钟信号中的不期望的干扰成分。

为了降低噪声,可以采用低噪声的时钟源,并在布局过程中避免与高噪声信号线路相近。

2. 时钟树的延时平衡时钟树的延时平衡对于保证时序一致性和减小时序偏差至关重要。

在时钟树设计中,应采取以下措施来保持时钟信号的延时平衡:(1)合理选择时钟树拓扑结构:时钟树的拓扑结构直接影响到时钟信号的传播延时。

一般来说,采用层次化的拓扑结构可以有效减小时钟信号传播的延时差。

(2)采用缓冲器和驱动器:缓冲器和驱动器可以用来调整时钟信号的驱动能力和传播延时,从而实现时钟信号的延时平衡。

3. 时钟树的功耗优化时钟树的功耗优化对于提高系统的能效至关重要。

在时钟树设计中,应采取以下措施来降低功耗:(1)合理选择时钟树的频率:时钟树的频率直接影响到功耗的消耗。

一般来说,较低频率的时钟信号可以降低功耗,但也会影响系统的性能。

(2)采用时钟门控技术:时钟门控技术可以根据需要对时钟信号进行开关控制,从而降低时钟信号的功耗。

4. 时钟树的布局与布线时钟树的布局与布线对于保证时钟信号的稳定传递和延时平衡至关重要。

在时钟树设计中,应采取以下措施来优化布局与布线:(1)合理布局时钟信号线路:时钟信号线路应尽量短且对称,避免与其他信号线路相交,减小互相干扰。

图文详解stm32时钟树

对于广大初次接触STM32的读者朋友(甚至是初次接触ARM器件的读者朋友)来说,在熟悉了开发环境的使用之后,往往“栽倒”在同一个问题上。

这问题有个关键字叫:时钟树。

众所周知,微控制器(处理器)的运行必须要依赖周期性的时钟脉冲来驱动——往往由一个外部晶体振荡器提供时钟输入为始,最终转换为多个外部设备的周期性运作为末,这种时钟“能量”扩散流动的路径,犹如大树的养分通过主干流向各个分支,因此常称之为“时钟树”。

在一些传统的低端8位单片机诸如51,AVR,PIC等单片机,其也具备自身的一个时钟树系统,但其中的绝大部分是不受用户控制的,亦即在单片机上电后,时钟树就固定在某种不可更改的状态(假设单片机处于正常工作的状态)。

比如51单片机使用典型的12MHz晶振作为时钟源,则外设如IO口、定时器、串口等设备的驱动时钟速率便已经是固定的,用户无法将此时钟速率更改,除非更换晶振。

而STM32微控制器的时钟树则是可配置的,其时钟输入源与最终达到外设处的时钟速率不再有固定的关系,本文将来详细解析STM32微控制器的时钟树。

图1是STM32微控制器的时钟树,表1是图中各个标号所表示的部件。

标号图1标号释义1 内部低速振荡器(LSI,40Khz)2 外部低速振荡器(LSE,32.768Khz)3 外部高速振荡器(HSE,3-25MHz)4 内部高速振荡器(HIS,8MHz)5 PLL输入选择位6 RTC时钟选择位7 PLL1分频数寄存器8 PLL1倍频寄存器9 系统时钟选择位10 USB分频寄存器11 AHB分频寄存器12 APB1分频寄存器13 AHB总线14 APB1外设总线15 APB2分频寄存器16 APB2外设总线17 ADC预分频寄存器18 ADC外设19 PLL2分频数寄存器20 PLL2倍频寄存器21 PLL时钟源选择寄存器22 独立看门狗设备23 RTC设备图1 STM32的时钟树在认识这颗时钟树之前,首先要明确“主干”和最终的“分支”。

时钟树总结

时钟树总结引言在现代集成电路设计中,时钟树是非常重要的组成部分。

时钟信号被用于同步电路中的各个部分,确保各个部件在正确的时间进行操作。

时钟树的设计和优化对于电路的性能和功耗具有重要的影响。

本文将总结时钟树的基本概念、设计和优化方法。

时钟树基本概念时钟树是由时钟发生器、时钟网络和时钟接收器组成的,用于传输时钟信号到整个电路的各个部分。

时钟发生器产生基准时钟信号,时钟网络将信号传输到各个时钟接收器。

时钟树的主要目标是提供一个稳定的时钟信号,使整个电路以正确定时进行操作。

时钟信号的稳定性可以通过降低时钟树的延迟、抖动和功耗来实现。

时钟树设计方法时钟树设计需要考虑以下几个因素:1. 时钟频率时钟频率是指每秒内时钟信号的周期数。

它决定了系统的工作速度和性能。

时钟频率越高,系统的运行速度越快,但也会带来更大的功耗和噪声。

2. 时钟网络拓扑时钟网络拓扑决定了时钟信号的传输路径和延迟。

常见的时钟网络拓扑包括树状结构、网状结构和环形结构。

不同的拓扑结构会对时钟信号的传输速度和功耗产生影响,选择合适的拓扑结构是时钟树设计的关键。

3. 时钟缓冲器的布局和参数选择时钟缓冲器用于放大、增强和传输时钟信号。

时钟缓冲器的布局和参数选择会直接影响时钟信号的稳定性和功耗。

合理选择时钟缓冲器的位置和参数是时钟树设计的重要一环。

4. 时钟树的功耗和抖动优化时钟树的功耗和抖动是设计过程中需要优化的指标。

功耗优化可以通过选择合适的缓冲器和优化时钟网络的结构来实现。

抖动优化可以通过减小时钟信号的传输路径和优化时钟缓冲器的参数来实现。

时钟树优化方法时钟树的优化方法主要包括以下几个方面:1. 延迟优化通过减小时钟信号的传输路径和优化时钟缓冲器的参数,可以减小时钟树的延迟。

延迟优化可以提高时钟信号的稳定性和电路的工作速度。

2. 抖动优化抖动是时钟信号波形的不稳定程度,影响时钟信号的精确性。

通过减小时钟信号的传输路径和优化时钟缓冲器的参数,可以减小时钟树的抖动。

Clock tree

Clock tree一、简介时钟树,是个由许多缓冲单元(buffer cell)平衡搭建的网状结构,它有一个源点,一般是时钟输入端(clock input port),也有可能是design内部某一个单元输出脚(cell output pin),然后就是由一级一级的缓冲单元搭建而成,具体的多少级,根据你的设置以及所使用的单元而定,目的就是使所用终点的clock skew(一般最关心这个)、insertion delay以及transtion 了,满足设计要求。

1在传统的集成电路设计中,只须考虑门本身的延迟,互连引起的延迟可忽略。

深亚微米芯片的设计不能沿用传统的设计流程,因为随着器件尺寸的不断减小和电路规模的扩大,门的延时越来越小,限制电路性能提高的主要因素是互连延迟。

因此,精确地计算互连延迟在芯片设计中具有十分重要的意义。

表1是线延时在不同工艺下占总延时的比例关系。

可以清楚的看到:随着工艺的发展,线延时逐渐占据了主导地位。

对集成电路设计的要求也日益提高,尤其是同步数字集成电路的时序问题更备受关注.在同步数字集成电路中,时钟信号为系统中的数据传送提供时间基准,通常是整个芯片中扇出最大、通过距离最长、以最高速度运行的信号,它对于同步系统的运行至关重要。

时钟树必须保证在最差条件下关键的时序要求能得到满足,对时钟信号任何不当的控制都可能导致情况紊乱,将错误的数据信号锁存到寄存器中。

2二、同步数字集成电路系统大部分的同步数字系统由级联的时序寄存器组和每组寄存器之间的组合电路组成.每个数据信号都锁存在一个双稳态寄存器中,该寄存器的使能时钟信号一到达,数据信号就离开双稳态寄存器,穿过组合电路网络进入下一个寄存器,并完全锁存在该寄存器直到下一个时钟信号到达.一个常用数字同步系统的延时单元由以下三个子系统组成[1]:1)记忆存储元件;2)组合逻辑元件; 3)时钟产生电路和其分配网络(clocktree).这三个子系统的相互关系对电路能否获得最好的性能和可靠性起着关键作用.对任意的有序寄存器对R1、R2,其关系可能为以下两种情况之一[1]:1) R1输出不能仅通过一系列组合逻辑元件传输到R2的输入端;2)存在一组组合逻辑元件直接连接R1的输出端和R2的输入端.在第一种情况下, R1输出端的信号变化不影响同一周期内R2的输入.第二种情况下(用R1yR2表示), R1输出端的信号转变将传到R2的输入端,该情况下R1、R2被称为时序相邻的寄存器对,它们组成了一条本地数据路径.如图1[1]所示, Ri和Rf为一对时序相邻寄存器对,它们分别为本地数据路径的起始和目标寄存器, Ci、Cf分别为驱动Ri和Rf的时钟信号,这两个时钟信号都由同一个时钟信号源通过时钟树产生.该时钟树用以产生同步于每个寄存器的特定时钟信号.从理论上来说,同步事件在同一时刻发生于所有寄存器上.在这个整体时钟策略的基础上,时钟信号到每个寄存器的时间都基于一个全局时间基准来定义.图1 本地数据路径选择时钟周期使得由起始寄存器产生的最迟信号在激活起始寄存器的时钟沿的下一个时钟沿到来时被锁存到目标寄存器中,故时序数据路径中的任意时序相邻寄存器对所允许的最小时钟周期TCP(min)和最大时钟频率fmax可由以下公式算出:1fmax= TCP(min)= tPD(max)+ tskewif+ tsetup.其中tskewif=tCi-tCf,tCi、tCf分别为从时钟源到Ri和Rf的时钟延迟,故tskewif可以为正或者为负(即Ci超前或滞后Cf);tPD(max)为数据路径的总路径延时,可由以下公式计算出:tPD(max)=tC-Q+tL+tInt,其中tC-Q为Ci到达后数据离开起始寄存器所需要的最大时间,tL+tInt为穿过组合逻辑块L和连线所需要的时间;tsetup为寄存器的建立时间.为了保证数据成功锁存进目标寄存器,必须满足两个条件:1)在使能时钟沿到达之前的一段时间内数据必须为有效和稳定的,这段时间称为建立时间,即tsetup.2)在使能时钟沿到达之后的一段时间内数据必须保持稳定,这段时间称为保持时间,即thold.三、时钟偏移1、时钟偏移的定义在整个同步数字系统中,时钟偏移是指时钟信号到达所有寄存器的最大时钟延迟和最小时钟延时之差[1~3],可以由如下公式表示:tskew=tmax-tmin,tmax和tmin分别为时钟源到接收端的最大和最小延时.如果所有时钟同时到达相应寄存器,则时钟偏移为零.2、时钟偏移对时序限制的影响时钟偏移的大小和极性会对系统的性能和可靠性产生好的或差的影响.tskewif相对任意两个时序相邻寄存器对而言,可正可负,而且由于时钟颤动的影响,会出现一定的不确定性,所以在时序分析中均采用最差情况.分析建立时间时采用tskewif为正的情况,分析保持时间时采用tskewif为负的情况.下面将就时钟偏移对同步数字电路的时序限制的影响进行详细分析.1)最大延时数据路径和时钟偏移的关系如果Ci超前Cf,即tskewif=tCi-tCf>0,则称时钟偏移为正时钟偏移.这种情况下主要考虑的是最大延时数据路径的建立时间问题,定义ts为要求信号最迟到达寄存器的时间treq max 和实际到达寄存器的时间tarr的差,TCP为时钟周期.要满足建立时间问题,必须使:ts=treq max-tarr=(TCP-tsetup-tskewif)-tPD(max)=(TCP-tsetup-tskewif)-(tC-Q+tL+tInt)>0 (1)由式(1)可知,正的时钟偏移使得ts减小,系统可达到的最大工作频率减小.2)最小延时数据路径和时钟偏移的关系如果Ci滞后Cf,即tskewif=tCi-tCf<0,则称时钟偏移为负时钟偏移.负时钟偏移可用于提高同步数字系统的最大工作频率,但是可能会导致最小延时路径的保持时间问题.定义th为要求信号实际到达寄存器的时间tarr与最早到达寄存器的时间treq min的差.要满足保持时间问题,必须使: th=tarr-treq min=(tC-Q+tL+tInt)-(thold+tskewif)>0 (2)由式(2)可知,tskewif为负时,th减小,当th<0时,可能导致紊乱情况,将错误的数据信号锁存到寄存器中.四、时钟树的经验结构及设计流程一种有效的方法是缓冲器插入。

时钟树优化与有用时钟延迟简介

时钟树优化与有用时钟延迟简介

时钟树优化与有用时钟延迟在后端时序修正基本思路提到了时序优化的基本步骤。

其中,最关键的阶段就是时钟树建立。

基本的优化都优先在数据路径上进行,并且希望路径尽量的短,最好在一个时钟周期之内。

当然,如果考虑输入、输出延迟,收敛悲观因素,库的建立时间,与时钟不确定性,以及不同时钟沿触发等因素,这个要求还要进一步的压缩,这些将在以后陆续进行讨论。

通常,我们希望时钟树偏差(clock tree skew) 越小越好,目标为零。

所以,在

建立时钟树(CTS)之前,我们首先将时钟设定为理想时钟。

这样的好处是,优

化数据路径时,不会对时钟路径有额外的修改。

而且,因为排除了时钟的影响,可以看到最终优化的结果,是否能够满足时序的要求。

如果不满足,最要考虑的就是数据路径组合逻辑是否太多,导致延迟过长。

其他,可以估计一下RC

延迟所占的比例,比如15%左右,过长时,检查是否路径逻辑单元之间是否间

隔的太长等等。

不过,本文重点要讨论的是,路径过长时,如何通过增加有用时钟延迟(useful skew) 来达到时序的满足。

IC compiler 有这样的命令skew_opt ,还有其两次流程(two pass)可供参

考。

阅读过本文后,我相信大家可以大致了解其工作的基本思路。

如果流程不正确,skew_opt 可能花费过长的运行时间,而且,不能达到预期

的效果。

如果我们清楚其中的原理,就可以更好,更自由的运用与发挥。

在不要考虑过多的情况下,如图,在理想时钟前提下,时序无法满足,即slack 0 。

原本我们可以做:。

时钟树的名词解释

时钟树的名词解释时钟树是指在数字电路中用于同步各个时序元件的一组时钟信号的分布网络。

在现代的高性能芯片或电路中,时钟同步至关重要,因为它在各个时序元件之间提供了稳定的时间基准。

时钟树的设计和优化对芯片的性能、功耗和可靠性都有着重要影响。

时钟树由时钟源、连接线和时钟树网络组成。

时钟源是输入时钟信号的来源,可以是外部时钟源或来自其他模块的输出时钟信号。

连接线是将时钟信号传输到时钟树网络中各个节点的物理线路。

时钟树网络则是一个复杂的分布网络,将输入时钟信号从源头传递到各个时序元件,如寄存器、触发器或时钟门等。

时钟树的设计目标是保证时钟信号的准确性、稳定性和低功耗。

为了达到这些目标,时钟树需要考虑以下几个方面。

首先,时钟树的拓扑结构需要合理设计。

常见的时钟树结构有线性结构、树状结构、网状结构等。

不同的结构对时钟信号的传输延迟、抖动和功耗有不同的影响。

合理选择拓扑结构可以减小时钟信号的传输延迟和抖动,提高系统的稳定性和可靠性。

其次,时钟树的布线需要考虑信号的传输延迟和功耗。

布线过程决定了时钟信号在连接线和时钟树网络中的传输速度和功耗消耗。

优化布线可以减小时钟信号的传输延迟和功耗,提高系统的性能和能效。

此外,时钟树还需要考虑时钟信号的脆弱性和噪声对系统性能的影响。

时钟信号容易受到环境噪声、温度变化和电源噪声的干扰,导致时钟信号的抖动、偏移或失真。

为了减小这些干扰对系统的影响,时钟树需要采取抑制噪声和干扰的措施,如噪声滤波器、抑制器和电源抗干扰电路等。

最后,时钟树的优化还需要考虑功耗和能效。

时钟树的设计和布线会产生一定的功耗损耗。

为了降低功耗,需要采取一些优化措施,如降低时钟频率、减小时钟驱动电流、优化布线路径等。

通过优化功耗,可以提高系统的能效,延长电池寿命或减少电能消耗。

总的来说,时钟树作为数字电路中重要的时序管理技术,对系统的性能、功耗和可靠性都有着重要影响。

通过合理的设计和优化,可以实现准确、稳定和低功耗的时钟信号分布,提高系统的性能和能效。

时钟树综合算法

时钟树综合算法时钟树综合算法是在集成电路设计中非常重要的一项技术。

它的作用是将时钟信号传输到整个电路中的各个部分,确保电路的稳定运行。

在现代集成电路中,时钟信号被用来同步各个模块之间的操作。

因为电路中的不同模块需要按照一定的顺序进行操作,所以时钟信号的传输是非常关键的。

时钟信号不仅要准确地传输到每个模块,还需要满足一些设计约束,比如时延、功耗等方面的要求。

时钟树综合算法的目标是在满足设计约束的前提下,最小化时钟信号路径的时延和功耗。

为了实现这个目标,时钟树综合算法通常包括以下几个步骤:1. 时钟树构建:首先,根据设计规格和约束,确定时钟树的拓扑结构和时钟信号的传输路径。

这个步骤中需要考虑信号的时延、功耗以及电磁干扰等因素。

2. 时钟树优化:在确定了时钟树的拓扑结构后,需要对时钟信号路径进行优化。

优化的目标是使得时钟信号的时延最小化,从而提高电路的工作频率和性能。

常用的优化技术包括缩短时钟信号路径、减少时钟缓冲器的数量等。

3. 时钟树布线:优化后的时钟树需要进行布线,将时钟信号传输到各个模块。

布线的目标是使得时钟信号的功耗尽可能小,并且满足电磁兼容性和电磁互容性的要求。

为了达到这个目标,布线时需要考虑时钟线的走向、间距、层间距、抗干扰措施等因素。

4. 时钟树验证:最后,根据设计规格和约束进行时钟树的验证。

验证的目标是确保时钟信号能够准确地传输到每个模块,并满足时延和功耗等设计要求。

验证过程需要使用专门的工具进行模拟和分析,以确保时钟树的正确性。

时钟树综合算法在集成电路设计中起着重要的作用。

它可以帮助设计工程师在设计过程中更好地管理和优化时钟信号,从而提高电路的性能和稳定性。

通过合理的时钟树设计和优化可以降低时延和功耗,提高电路的工作频率和可靠性。

同时,时钟树综合算法也需要与其他的电路设计工具和算法进行配合,共同完成电路的设计和验证。

总之,时钟树综合算法是一项非常重要的电路设计技术,它对电路的性能和稳定性具有重要影响。

芯片中时钟树综合质量评价指标

芯片中时钟树综合质量评价指标芯片中的时钟树综合质量评价指标时钟树综合质量在芯片设计中起着至关重要的作用,它直接影响着整个芯片的性能和稳定性。

时钟树综合质量评价指标是评判时钟树设计是否合理、性能是否优越的重要标准。

在芯片设计过程中,工程师需要充分了解时钟树综合质量评价指标的相关知识,才能设计出高质量的时钟树,确保芯片性能的稳定和可靠。

一、时钟树综合质量评价指标的重要性时钟树综合质量评价指标是评判时钟树设计优劣的重要标准,它直接影响着芯片的工作稳定性、功耗和时序性能。

一个良好的时钟树设计能够减小时钟树网络的延迟、功耗和时钟偏移,提高时钟树的稳定性和可靠性,从而提升整个芯片的性能和功耗表现。

二、时钟树综合质量评价指标的内容时钟树综合质量评价指标主要包括时钟树的布线长度、时钟树的网络拓扑结构、时钟树的功耗和时钟偏移等指标。

其中,时钟树的布线长度直接影响着时钟信号传输的延迟和功耗,时钟树的网络拓扑结构则直接决定了时钟信号的传输效率和时序一致性,时钟树的功耗和时钟偏移则是评价时钟树稳定性和可靠性的重要指标。

三、时钟树综合质量评价指标的影响因素时钟树综合质量评价指标受到多种因素的影响,包括芯片的工作频率、布局结构、设计规则和工艺制程等。

不同的工艺制程和设计规则会对时钟树的布线长度和功耗产生影响,布局结构的不同也会影响时钟树网络的拓扑结构和时钟偏移。

工作频率对时钟树的设计要求也是不容忽视的因素,高频率下的时钟树设计需要更高的稳定性和可靠性。

四、时钟树综合质量评价指标的优化方法针对时钟树综合质量评价指标的影响因素,工程师可以采取一系列优化方法来改善时钟树的设计质量。

在布局设计阶段,可以采用合理的布局规则和工艺制程,来减小时钟树的布线长度和功耗;在时钟树综合阶段,可以优化时钟树的拓扑结构和时钟网络,来提高时钟信号传输效率和时序一致性;在时钟树布线阶段,可以采用时钟树缓冲技术和时钟树匹配技术,来降低时钟树的功耗和时钟偏移。

时钟树综合解读

同步Pins和忽略Pins

同步Pins: CTS优化达到 buffer约束(最大传 输时间/电容)和时 钟树目标(偏移,插 入延时等)) 忽略Pins: CTS加入一个小的 buffer去隔离所有 的Pins 忽略buffer约束 (最大传输时间/电 容和时钟树目标)

默认的Skew Optimization

带有SDC不确定的传播时钟

如果SDC不确定值包括抖动和时间裕量,Astro仍 能计算实际的时钟网络延时,同时模仿这些效应 调整SDC中set_clock_uncertainty 的值 通过估计偏移值减少这个值 执行相同的命令 sdc “set_propagated_clock [all_clocks]” 调节下面的时序设置项 Unset “Ignore Clock Uncertainty ” Unset “Ignore Propagated Clock ”

符合buffer约束(不符合该约束会报违规) 最大传输时间延迟 最大负载电容 最大扇出 最大buffer级数 符合时钟树目标(不会报违规) 最大偏移 根据Min/Max delay插入延迟

CTS流程

布局完成 设置时钟公共选项 综合时钟树 重新连接扫描链 使能传播时钟 Post-CTS布局优化 优化时钟偏移(CTO) 优化时序(Useful Skew CTO) 布线

时钟树综合结果

时钟buffer增加 阻塞可能会增加 非时钟树单元可能 会被移动到不理想 的位置 可能会引起新的时 序和最大tran/cap 违规

Post-CTS布局优化

Post-CTS布局优化能 优化时序和减少阻塞 执行逻辑和布局优化 去修复可能的时序 (建立时间和保持时 间)、最大电容和最 大过渡时间违规 保持时间推荐在这 里进行首次修复 Congestion Removal 能通过移动不必要的 非时钟树buffer减少 阻塞

时钟树的作用

时钟树的作⽤

加buffer之后带负载的能⼒增强。

钟树的作⽤是平衡skew,但最重要的三个指标重要性排序:transition > insertion delay > skew。

(1)因为每个主时钟带的负载数量很⼤(high fanout),会违反drv(max transition/ max cap / max fanout),因此需要将巨⼤的负载通过⼏级buffer分担,为了不违反drv,每个buffer都不会带太多数量的负载,就形成了树状的buffer tree。

(2)buffer在时钟树中的作⽤既可以增⼤延时,也可以减⼩延时。

的确,buffer本⾝也有延时,你可以通过加减每个sink前的buffer来控制skew。

但对于没有做CTS前的时钟树延时太⼤,是由于时钟线长度和巨⼤时钟⽹本⾝的电容导致的。

互连线delay与长度成平⽅关系,如果太长就会很⼤,⽤buffer做个中继,可以降低延时,起码与长度成线性关系。

另外,加⼊buffer可以减⼩主时钟及以后各级buffer的fanout,这样可以让每段时钟线得到更⼤的驱动能⼒。

总之,互连延时和input transition 和本⾝负载⼤⼩有关。

简单描述时钟树工作原理

简单描述时钟树工作原理

时钟树是计算机硬件中一个重要的部分,作用是为系统中的各个部件提供精确的时钟信号以同步其工作。

其工作原理可以简单描述如下:

1. 时钟源:时钟树的起点是一个稳定的时钟源,通常是一个晶体振荡器或其他可靠的时钟发生器。

该时钟源产生一个固定频率的时钟信号。

2. 时钟传输:时钟信号通过时钟传输线路向系统中的各个部件传输。

为了保证信号传输的稳定性和减少时钟抖动,通常采用差分信号传输,并使用特殊的时钟线路设计。

3. 时钟分频:时钟树中的分频器会根据需要将时钟信号分频为更低的频率。

这是因为不同的部件可能需要不同的工作频率,例如CPU和内存可能需要不同的频率。

4. 时钟分配:时钟信号通过时钟分配网络被分配到各个部件。

这通常涉及到使用缓冲器来延长时钟信号的传输距离,并确保各个部件能够准确接收到时钟信号。

5. 时钟延迟管理:时钟延迟是时钟传输过程中的一个关键问题,因为时钟信号在传输过程中会有一定的延迟。

时钟树设计中通常会通过延迟控制电路来管理时钟延迟,以保证各个部件在同一时刻接收到时钟信号。

6. 时钟校准:时钟树的最后一步是进行时钟校准,以确保各个

部件接收到的时钟信号是准确且稳定的。

这包括时钟相位校准和时钟频率校准,以保证整个系统能够在正确的时钟节拍下工作。

综上所述,时钟树通过将高频的时钟信号进行分频、传输、分配和校准,为计算机系统中的各个部件提供准确的时钟信号,以确保它们能够在同一时刻同步工作。

芯片中时钟树综合质量评价指标

芯片中时钟树综合质量评价指标介绍时钟树是芯片设计中非常重要的一部分,它负责为芯片内的各个功能模块提供稳定的时钟信号。

时钟树的设计质量直接影响芯片的性能和功耗。

因此,对时钟树的综合质量进行评价是芯片设计过程中的重要任务。

时钟树的综合质量评价指标时钟树的综合质量评价指标主要包括以下几个方面:1. 时钟树延迟时钟树的延迟是指时钟信号从源端到达目的端所需的时间。

时钟树延迟的大小直接影响芯片的工作频率和时序要求。

因此,评价时钟树的综合质量时,需要考虑时钟树延迟是否满足设计要求。

2. 时钟树功耗时钟树的功耗是指时钟信号在时钟树中传输过程中所消耗的能量。

时钟树功耗的大小与时钟树的拓扑结构、电压和频率等因素有关。

评价时钟树的综合质量时,需要考虑时钟树功耗是否在可接受范围内。

3. 时钟树抖动时钟树的抖动是指时钟信号的相位或频率在传输过程中发生的变化。

时钟树抖动会导致芯片的时序偏差和时钟信号的不稳定性。

因此,评价时钟树的综合质量时,需要考虑时钟树抖动是否满足设计要求。

4. 时钟树噪声时钟树的噪声是指时钟信号中的不良成分,包括时钟信号的谐波、杂散等。

时钟树噪声会对芯片的功能模块产生干扰,影响芯片的性能和可靠性。

因此,评价时钟树的综合质量时,需要考虑时钟树噪声是否在可接受范围内。

评价指标的权重不同的芯片设计对时钟树的要求不同,因此,在评价时钟树的综合质量时,需要为不同的评价指标分配不同的权重。

一般来说,时钟树延迟和功耗是两个比较重要的指标,因为它们直接关系到芯片的性能和功耗。

而时钟树抖动和噪声相对来说可以适当放宽要求。

评价方法和工具评价时钟树的综合质量可以采用静态分析和动态仿真的方法。

静态分析是指通过对时钟树的结构和参数进行分析,预测时钟树的性能指标。

动态仿真是指通过模拟时钟信号在时钟树中的传输过程,评估时钟树的实际性能。

评价时钟树的综合质量还可以借助一些专门的工具,如PrimeTime、HSPICE等。

这些工具可以对时钟树进行详细的分析和仿真,提供时钟树的延迟、功耗、抖动和噪声等性能指标。

时钟树功耗开题报告

时钟树功耗开题报告时钟树功耗开题报告一、引言时钟树是现代集成电路中非常重要的组成部分,它用于分配和传输时钟信号,确保电路中各个部分的同步工作。

然而,时钟树的设计和优化对功耗和性能具有重要影响。

本报告旨在探讨时钟树功耗的问题,并提出一种可能的解决方案。

二、时钟树功耗的问题时钟树功耗主要包括开关功耗和导线功耗。

开关功耗是由时钟树中的开关电路引起的,而导线功耗则是由时钟信号在导线上的传输引起的。

这两种功耗都会对整个集成电路的功耗产生显著影响。

1. 开关功耗开关功耗是由时钟树中的时钟驱动器和时钟缓冲器引起的。

时钟驱动器负责驱动时钟信号,而时钟缓冲器则用于放大和缓冲时钟信号。

这些电路在切换时会产生瞬态功耗,并且随着时钟频率的增加而增加。

因此,减少时钟驱动器和时钟缓冲器的功耗是降低开关功耗的关键。

2. 导线功耗导线功耗是由时钟信号在时钟树的导线上传输时引起的。

导线的电阻和电容会导致功耗的损耗。

此外,时钟信号在长距离传输时还会受到噪声和时钟抖动的影响,进一步增加功耗。

因此,减少导线的电阻和电容以及优化时钟信号传输路径是降低导线功耗的关键。

三、解决方案为了降低时钟树功耗,可以采取以下几种解决方案:1. 优化时钟驱动器和时钟缓冲器通过改进时钟驱动器和时钟缓冲器的设计,可以降低开关功耗。

一种可能的方法是采用低功耗的开关电路和缓冲电路,并优化其电源电压和电流。

此外,还可以采用时钟门控技术,只在需要时才开启时钟驱动器和时钟缓冲器,从而降低功耗。

2. 优化时钟树的布局和布线通过优化时钟树的布局和布线,可以降低导线功耗。

一种可能的方法是采用层次化布局,将时钟树分为多个层次,每个层次使用不同的导线材料和尺寸。

此外,还可以采用差分传输线技术,减少时钟信号的传输损耗和噪声干扰。

3. 时钟树功耗的建模和仿真为了更好地理解和优化时钟树功耗,可以采用建模和仿真的方法。

通过建立时钟树功耗的数学模型,并使用仿真工具进行验证和分析,可以帮助设计人员更好地理解时钟树功耗的来源和影响因素,从而提出更有效的优化方案。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

芯片设计中具有十分重要的意义。 图。

因为 L → 0, 故 N →∞,于是得到 τ

表1是线延时在不同工艺下占总延

其中 R和 C分别代表单位长度 =R*C*l*l/2。可以看出,线的延时

时的比例关系。可以清楚的看到: 的电阻和电容,l代表总的线长。经 与线长的平方成正比,减小线的长

度可以大大降低延时,同时延时与

2 庄镇泉,胡庆生. 电子设计自 动化. 科学出版社. 2000

3 L.T.Pillage and R.A.Rohrer. Asymptotic Waveform Evaluation for Timing Analysis. IEEE Trans.CAD,1990,9(9)

4 F.Y.Chang. Transient Simulation of Nonuniform Coupled Lossy Transmission Lines Characterized with Frequency- Dependent Parameters,Part Ⅱ: Discrete Time Analysis. IEEE Trans.on CAS. 1992

5 Jan M.Rabaey. 数字集成电路 设计透视. 清华大学出版社

6 洪先龙,严晓浪,乔长阁. 超 大规模集成电路布图理论与算法 . 科学出版社. 1998

(收修改稿日期:2003-06-23)

结语 对于时钟频率要求很高的电 路,或者说以追求高速为目的的设 计,如 CPU设计,广泛采用全定制

参考文献 1 秦晓凌,潘中平 .“ASIC/SOC 后端设计作业流程剖析”. 中国集成 电路. 2002

3 8 2003.10 电子设计应用 www.eaw.com.cn

时钟偏差和时钟树综合

载不同;在时钟网中插入的缓冲器 不同等等。

时钟偏差过大会引起同步电路 功能混乱,一般要求时钟偏差不能 超过时钟周期的10%。

综合。在算法中,这个问题可描述

为:给定时钟源点C ,给定平面内时 0

钟端点的集合 C={C ,C ,C …C },

12

i

n

那么就是连接各个C ,使得以下两 i

网表以及写出时序限制

文件,送给apollo做布局

布线,采用的基本流程

如图 2所示。

时钟树在布线前

做,说明时钟信号优先

级是高于一般信号的。

做时钟树会碰到以下几

项必要的指标:树的根

结点、时钟周期、树的最

大延迟、树的最小延迟、

图3 平衡的时钟树综合

传递时间和缓冲器的种 类等等,要按其特点设

定一组特别的参数。这

max t(C0,Ci), i∈{1,2…n} max|t(C0,Ci)-t(C0,Cj) | i,j∈ {1,2…n}

实例 在ASIC后端设计中,基于时序 的布局布线就是为了解决连线时延 而产生的。对高速电路后端设计采

用自动布局布线。由

design compiler综合生成

通信与计算机

数。 电路板的板材选用 Nelco 的

N4000-2,在 1GHz实际测量的介电 常数是4.1,正切损耗角是0.004,板 才厚度是 0.8mm。图 2 是对 LNA 进 行实际测试的增益。平均值是 46dB,图形的产生:先用安捷伦的 频谱分析仪(E4440A)进行测量,然 后用生成的 datafile在 Microwave Office里用散射参量生成图形。由 于没有专用仪器,所以没法测量噪 声系数,但是在接收 -130dBm的输

式都达到最小化:

高速电路使得所有时序的容差

由于时钟偏差的存在,所以时

都非常小,也对精确定位电路各部 分的延迟模型提出了更高的要求。 理想的时钟是:时钟同时到达各个 同步单元。但是实际上这是不可能 的。我们把到达各个同步单元的最 大时间差叫做时钟偏差。产生时钟 偏差的原因有:时钟源到各个时钟

钟周期公式应为 T=Tco+Tdelay+Tsetup + Tskew(其中Tco是同步元件的内部 延时;Tdelay是组合逻辑部分延时; Tsetup是触发器的建立时间)。随着工 艺的发展,Tco、Tdelay和 Tsetup都有明 显的降低,所以降低Tskew成为提高 电路速度的关键。在ASIC后端设计

是一种需要多实践,多

摸索的经验。采用台积

电的0.25µm库做了高速 电路的时序驱动布局布

线,在时钟布线时选择

平衡时钟树(见图3)。

在时滞时间满足要

求的前提下,注意分析

图 2 ASIC布局布线流程

图4 高速电路的各个时钟树节点(4 levels)

了时钟树综合前后的一 些数据信息。这 38

www.eaw.com.cn 电子设计应用 2003.10 1 9

表1 不同工艺下线延时占总延时的比例

RC 成正比,故应该采用 RC较小的 金属进行长线传输。一种有效的方

法是缓冲器插入。加入缓冲器后,

缓冲器本身会带来延时,但是由于

它减小了线长,大大降低了线延

时,所以总的延时还是减小了。如

果在长l的线中点加一个缓冲器,那

么我们可以计算:

图1 互连线的分布式模型

τtotal = τ1+τbuf+τ2=R*C*l*l/ 8+τbuf+R*C*l*l/8=R*C*l*l/4+τbuf

3 Randall W. Rhea. HF Filter Design and Computer Simulation

4 Ulrich L. Rohde, David P. Newkirk. RF/Microwave Circuit Design for wireless application

5 Guillermo Gonzalez, Ph.D. Microwave Transistor Amplifiers Analysis and Design

入功率时,效果非常好。

结语 本设计实现的 LNA 和国内其 他厂家生产的 LNA比较起来,具有 在L波段的噪声系数小,增益大,频 带宽等优点。是一种比较理想的 LNA 方案。■

参考文献 1 傅君眉. 微波无源和有源电路原 理. 西安:西安交通大学出版社. 1988

2 Jeremy Everard. Fundamentals of RF Circuit Design

不能沿用传统的设计流程,因为随 把互连线建模为单个电阻R和单个

x是线上任一点到信号源点的

着器件尺寸的不断减小和电路规模 电容 C 的模型,计算它们的 RC 延 距离,而 V是该点的电势。这个方

的扩大,门的延时越来越小,限制 时,对于较长的互连线就不太适用 程没有闭解,一般采用近似解。输

电路性能提高的主要因素是互连延 了。对于较长的互连线,分布式模 出 点 的 时 间 常 数 为 : τ = 迟。因此,精确地计算互连延迟在 型是比较精确的,图1是它的示意 R*C*L*L*(N(N+钟 网络,一般搭成网格状的,这需要 经验丰富的工程师来完成。这种网 络使得时钟偏差减小,大大提高了 设计的性能。

对于自动布局布线,有些好的 算法时钟偏差最小化过程要在延迟 优化以后进行。由于时钟树的延迟 已经最小化,因此,时钟偏差最小化 只需对各时钟汇点的延迟进行合理 的再分配即可,而不会破坏延迟最 小化的结果。Synopsys 公司的Astro 是用来做百万门以上设计的布局布 线工具,适合于0.18µm及其以下的 工艺, Astro CTS的主要特征是:为 了有更好的预测能力,布局和CTS 同时进行;局部skew分析和优化;增 加的时钟树优化,以解决最后一分 钟的 ECO。在百万门级以上的设计 中,采用Astro做时序驱动布局布线 将带来极好的时序收敛效果。

(收稿日期:2003-06-26)

19 些数据如下:

从前后数据比较可以看出,虽 然最长和最短延时时间比时钟树综 合前都要增大,但是它们的差值— —总体时钟偏差大大减小了。通过 做时序驱动的布局布线,对高速电 路进行了优化,使其性能得到了最 佳,最后的时钟频率可达200M。时 钟树节点(4 levels)如图4所示。

其中τbuf是缓冲器的延时。由于

1 8 2003.10 电子设计应用 www.eaw.com.cn

I C 设计

工艺的发展以及缓冲器设计的要 端点的路径长度不同;各个端点负 中,解决这个问题的方法是时钟树

求,现在的缓冲器延时τbuf是相当小 的,比较前后的延时,可以知道总 的延时是可以大大减小的。

I C 设计

■ 同济大学信息与控制工程系 唐振宇

A S I C 后端设计中的时序偏差 以及时钟树综合

摘 要:同步设计中,由于时钟网络延时决定了芯片的最大工作速度,所以时钟树需要高精度进行 布线。一种重要的时钟网络设计是缓冲器插入。在超大规模集成电路的设计中,为了最小化 时钟延时和时钟偏差,缓冲器插入是一种有效的方法。在布局布线流程中,时钟树布线在“时 钟树综合”时由工具自动完成“ 。时钟树综合”在apollo里是在布局完成后布线之前做的。

关键词:缓冲器插入;时钟偏差;时钟树综合

引言

随着工艺的发展,线延时逐渐占据 过列写节点 KCL方程,并且使单位

在传统的集成电路设计中,只 了主导地位。

长度L→0,经过一系列数学推导可

须考虑门本身的延迟,互连引起的

对于线的延时,已经提出了不 以得出下面的微分方程:

延迟可忽略。深亚微米芯片的设计 少模型。较早的有lumped model,它