锁相环地相位噪声杂散抑制锁相时间

锁相环电路的设计及相位噪声分析

和响应速度之间折衷考虑,相位裕度越大,系统越稳定,但是响应速度变慢。

这里取相位裕度为60度。

同样的,这两个环路参数是估计出来的,在实际电路中仍然需要多次考虑。

最后根据上面的两个环路参数,利用第二章第六节的公式2-22到2-24可以计算出低通滤波器的电阻和电容的值大约为:R2=12K,C2=138PF,CI=1IPF。

根据以上估算的参数可以将锁相环系统的幅频和相频特性曲线画出,如图4.2所示。

图4-2PLL的幅频与相频特性曲线4.3锁相环系统级模型4.3.1Matlab构造数学模型Mauab是MathWorks公司开发的具有强大科学运算功能的数学工具,其中的软件包--Simulink是专门用于数学建模的工具。

通过建立锁相环系统的线性模型,如图4—3所示,分别建立环路中每个模块的传输函数,然后设置输入输出点。

该线性模型不仅可以分析系统的冲击响应和阶跃响应,还可以分析零极点与波特图。

冲击响应和阶越响应的模拟结果如图4-4所示,此模型可以很方便的修改参数,仿真速度非常快,模拟结果也非常直观,对于理解二阶系统的特性非常有帮助。

t№啦*血瞻呻目删e,ra口aap蝌m鼬rtrartim'哥缸眦h恤啪蚓of恤VCO图4-3Matlab建立PLL的线性模型图4—4PLL的阶跃响应与冲击响应4.3.2VerilogA构造行为级模型VerilogA语言是Verilog硬件描述语言的扩展,主要用来描述模拟系统的结构和行为,包括电子,机械,流体力学和热力学系统等㈣。

下面给出VerilogA描述锁相环的行为级模型,并应用Mica进行仿真。

首先,以电阻的行为级模型为例,简单的说明一下VerilogA语言的特点和应用。

、include“disciplines.”’’include“constants.h,’moduleres(a,b);inouta,b;electricala,b;parameterrealR21.O:analogbeginI(a,b)<+V(a,b)/R;//Altemative:V(a,b)<+I(a,b)4R;第五章锁相环电路设计及模拟第五章锁相环电路设计及模拟5.1整体设计本章主要是关于锁相环的晶体管级电路的设计,不但详细的分析了电路的结构,而且给出了模拟结构及相关的解释。

简述锁相环电路的关键指标

简述锁相环电路的关键指标锁相环(PLL)是一种电路系统,它以某个外部参考信号为基准,通过比较输出信号和输入信号的相位差,实现信号的同步和跟踪。

锁相环电路广泛应用于通信、计算机、控制系统等领域,其关键指标对于性能和稳定性具有重要意义。

锁相环电路的关键指标有以下几个方面:1. 频率稳定性:频率稳定性是指锁相环输出信号的频率与参考信号的频率之间的稳定性。

一般情况下,频率稳定性可以用频率偏差和频率漂移来描述。

频率偏差是指锁相环输出信号的实际频率与参考信号频率之间的偏离程度,频率漂移是指锁相环输出信号的频率随时间的变化趋势。

在实际应用中,频率稳定性通常是评价锁相环电路性能的重要指标,特别是在无线通信系统中,频率稳定性的好坏直接影响到系统的性能和覆盖范围。

2. 锁定时间:锁定时间是指锁相环从失锁状态到稳定锁定状态所需的时间。

在实际应用中,锁定时间也是锁相环性能的重要指标之一。

一般情况下,锁相环的锁定时间越短越好,因为锁定时间短意味着锁相环能够更快地跟踪和同步输入信号。

在快速变化的环境中,锁定时间短可以使锁相环更好地适应信号的变化,保持稳定的工作状态。

3. 相位噪声:相位噪声是指锁相环输出信号的相位随机扰动的程度。

通常情况下,相位噪声可以通过相位噪声密度来描述。

相位噪声对于一些高精度的应用来说是非常重要的,比如雷达、卫星导航等系统,因为相位噪声的存在会影响到系统的精度和测量精度。

4. 抑制比:抑制比是指锁相环输出信号与输入信号的比较结果的信噪比。

在实际应用中,抑制比是评价锁相环抑制噪声和干扰的重要指标之一。

抑制比越大,意味着锁相环对输入信号的跟踪能力和抗干扰能力越强。

除了以上几个关键指标之外,锁相环的带宽、稳定性、幅度恢复时间、输出电平等指标也是需要考虑的重要因素。

带宽是指锁相环对输入信号的跟踪范围,通常用于描述锁相环的跟踪速度和跟踪能力。

在很多应用中,锁相环的带宽需要根据具体的要求来调整,以满足不同的跟踪和同步要求。

锁相环(PLL)原理及其应用中的七大常见问题

当 VCO/VCXO 的控制电压超出了 Vp,或者非常接近 Vp 的时候,就需要用有源滤波器。在对 环路误差信号进行滤波的同时,也提供一定的增益,从而调整 VCO/VCXO 控制电压到合适的 范围。 问:PLL 对于 VCO 有什么要求?以及如何设计 VCO 输出功率分配器? 答:选择 VCO 时,尽量选择 VCO 的输出频率对应的控制电压在可用调谐电压范围的中点。 选用低控制电压的 VCO 可以简化 PLL 设计。 问:如何设置电荷泵的极性? 答:在下列情况下,电荷泵的极性为正。 环路滤波器为无源滤波器,VCO 的控制灵敏度为正(即,随着控制电压的升高,输出频率增 大)。 在下列情况下,电荷泵的极性为负。环路滤波器为有源滤波器,并且放大环节为反相放大; VCO 的控制灵敏度为正。环路滤波器为无源滤波器,VCO 的控制灵敏度为负;PLL 分频应用, 滤波器为无源型。即参考信号直接 RF 反馈分频输入端,VCO 反馈到参考输入的情况。 问:为何我的锁相环在做高低温试验的时候,出现频率失锁? 答:高低温试验失败,可以从器件的选择上考虑,锁相环是一个闭环系统,任何一个环节上 的器件高低温失效都有可能导致锁相环失锁。先从 PLL 频率合成器的外围电路逐个找出原 因,如参考源(TCXO,)是否在高低温试验的范围之内? 问:非跳频(单频)应用中,最高的鉴相频率有什么限制? 答:如果是单频应用,工程师都希望工作在很高的鉴相频率上,以获得最佳的相位噪声。数 据手册都提供了最高鉴相频率的值,另外,只要寄存器中 B > A,并且 B > 2,就可能是环 路锁定。通常最高频率的限制是:这里 P 为预分频计数器的数值。

问:环路滤波器采用有源滤波器还是无源滤波器? 答:有源滤波器因为采用放大器而引入噪声,所以采用有源滤波器的 PLL 产生的频率的相 位噪声性能会比采用无源滤波器的 PLL 输出差。因此在设计中我们尽量选用无源滤波器。 其中三阶无源滤波器是最常用的一种结构。 PLL 频率合成器的电荷泵电压 Vp 一般取 5V 或者稍高,电荷泵电流通过环路滤波器积分后 的最大控制电压低于 Vp 或者接近 Vp。如果 VCO/VCXO 的控制电压在此范围之内,无源滤波 器完全能够胜任。

锁相环的相位噪声分析

锁相环路相位噪声分析张文军 电信0802【摘要】本文对锁相电路的相位噪声进行了论述,并对其中各组成部件的相位噪声也做了较为详细的分析。

文中最后提出了改进锁相环相位噪声的办法。

【关键词】锁相环;相位噪声;分析 引言相位噪声是一项非常重要的性能指标,它对电子设备和电子系统的影响很大,从频域看它分布的载波信号两旁按幂律谱分布。

用这种信号无论做发射激励信号,还是接收机本振信号以及各种频率基准,这些信号在解调过程中都会和信号一样出现在解调终端,引起基带信噪比下降。

在通信系统中使环路信噪比下将,误码率增加;在雷达系统中影响目标的分辨能力,即改善因子。

接收机本振的相位噪声遇到强干扰信号时,会产生“倒混频”,使接收机有效噪声系数增加。

随着电子技术的发展,对频率源的信号噪声要求越来越严格,因此低相位噪声在物理、天文、无线电通信、雷达、航空、航天以及精密计量、仪器仪表等各种领域里都受到重视。

1 相位噪声概述相位噪声 ,就是指在系统内各种噪声作用下所表现的相位随机起伏,相位的随机起伏起必然引起频率随机起伏,这种起伏速度较快,所以又称之为短期频率稳定度。

理想情况下,合成器的输出信号在频域中为根单一的谱线,而实际上任何信号的频谱都不可能绝对纯净,总会受到噪声的调制产生调制边带。

由于相位噪声的存在,使波形发生畸变。

在频域中其输出信号的谱线就不再是一条单根的谱线,而是以调制边带的形式连续地分布在载波的两边,在主谱两边出现了一些附加的频谱,从而导致频谱的扩展,相位噪声的边带是双边的,是以0f 为中心对称的,但为了研究方便,一般只取一个边带。

其定义为偏离载频1Hz带宽内单边带相位噪声的功率与载频信号功率之比,它是偏离 载频的复氏频率m f 的函数 ,记为()m f ζ,单位为d B c / Hz ,即()010lg[/](1)m SSB f P P ζ=式中SSB P 为偏离载频m f 处,1Hz 带宽内单边带噪声功率;0P 为载波信号功率。

(高频电子线路)第七章锁相环

测试原理及步骤说明

3. 调整信号发生器的频率和幅度,观察锁相环电 路的输出变化。

4. 使用频率计测量输入信号和输出信号的频率, 记录数据。

5. 使用电压表测量输入信号、输出信号以及误差 信号的电压幅度,记录数据。

数据处理与结果分析

数据处理:根据实验记录的数据,计算 输入信号和输出信号的频率差、相位差 以及误差信号的电压幅度等指标。

VS

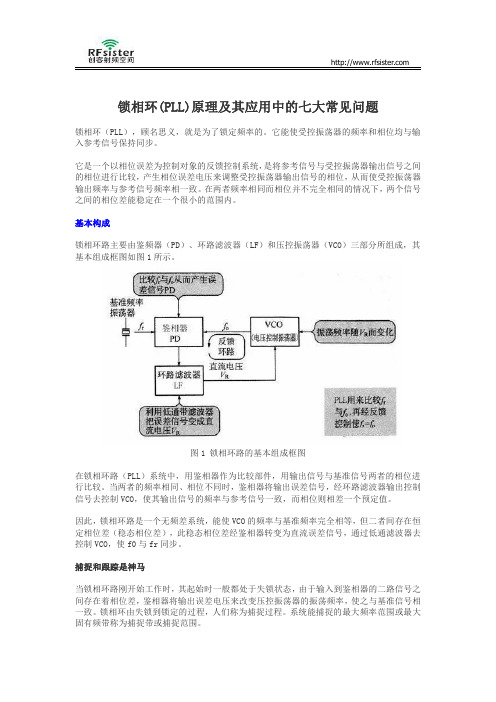

组成结构

锁相环主要由鉴相器(PD)、环路滤波器 (LF)和压控振荡器(VCO)三个基本部 分组成。其中,鉴相器用于检测输入信号 与本地振荡器输出信号的相位差;环路滤 波器用于滤除误差信号中的高频噪声,保 证环路稳定性;压控振荡器则根据误差信 号调整本地振荡器的频率和相位。

性能指标及分类方法

性能指标

滤波特性

滤除鉴相器输出电压中的高频成分,保证环路稳定性。

电路设计要点

根据锁相环的带宽和稳定性要求,选择合适的滤波器类型和参数, 优化滤波器的幅频特性和相频特性。

压控振荡器设计

振荡器类型

LC振荡器、晶体振荡器等。

振荡特性

描述振荡器输出频率与输入控制电压之间的关系。

电路设计要点

选择合适的振荡器类型,确定振荡器的频率范围和稳定性要求,优化 振荡器的线性范围和灵敏度,以及减小相位噪声和杂散。

集成化趋势

集成化是锁相环发展的另一个重要趋 势。通过高度集成化设计,可以减小 锁相环的体积和重量,降低成本,提 高可靠性和稳定性。

面临的技术挑战和解决方案

技术挑战

锁相环在发展过程中面临着一些技术挑战,如相位噪声、杂散抑制、快速锁定 等。这些挑战限制了锁相环的性能和应用范围。

锁相环相噪计算公式

锁相环相噪计算公式锁相环相噪计算公式1. 引言锁相环是一种常见的电路技术,用于对输入信号进行频率、相位或时延的调整。

在锁相环中,相噪是一个重要的性能指标,用来描述输出信号中的相位噪声。

2. 相噪计算公式•公式1:相噪指数(ENOB) = 20log10(2pi f3dB T)–其中,f3dB表示锁相环的3dB截止频率,T表示锁相环的环路延迟时间。

•公式2:相噪功率密度(PN) = 20log10(Kv f)–其中,Kv表示锁相环的控制增益,f表示锁相环的偏置频率。

3. 解释与示例相噪指数(ENOB)相噪指数(ENOB)是一种常用的相噪度量单位,表示为dBc,表示输出信号中相位噪声相对于理想信号的衰减程度。

具体计算方法如下:ENOB = 20log10(2pi f3dB T)例如,一个锁相环的3dB截止频率为10 kHz,环路延迟时间为2 ns,则根据公式1计算其相噪指数为:ENOB = 20log10(2pi10^4 2*10^-9) = - dBc这意味着锁相环输出信号中的相位噪声相对于理想信号衰减了 dB。

相噪功率密度(PN)相噪功率密度(PN)是另一种常用的相噪度量单位,表示为dBc/Hz,表示单位频带中的相位噪声功率。

具体计算方法如下:PN = 20log10(Kv f)例如,一个锁相环的控制增益为30 dB/V,偏置频率为1 MHz,则根据公式2计算其相噪功率密度为:PN = 20log10(10^3 10^6) = 140 dBc/Hz这意味着在1 Hz的频带内,锁相环输出信号的相位噪声功率为-140 dBc/Hz。

4. 总结本文介绍了锁相环相噪计算公式和其含义,包括相噪指数(ENOB)和相噪功率密度(PN)的计算公式,并通过示例进行了说明。

相噪是衡量锁相环性能的重要指标之一,在设计和应用中需要对相噪进行合理估算和控制。

5. 其他相关公式和注意事项•公式3:锁定时间(Tlock) = 1/(2pi f3dB)–锁定时间表示锁相环从失锁状态到锁定状态所需的时间。

锁相环输出信号相位噪声噪声及杂散特性分析应用实践

锁相环输出信号相位噪声噪声及杂散特性分析应用实践【摘要】本文详细地介绍了锁相环的鉴频鉴相器、分频器和输入参考信号的相位噪声对锁相环合成输出信号的近端相位噪声的具体贡献值。

并以CDMA 1X基站系统中800MHz的FS 单板的锁相环输出信号相位噪声指标进行理论计算。

为广大锁相环设计者提供理论计算方法的参考和实践设计的参考依据。

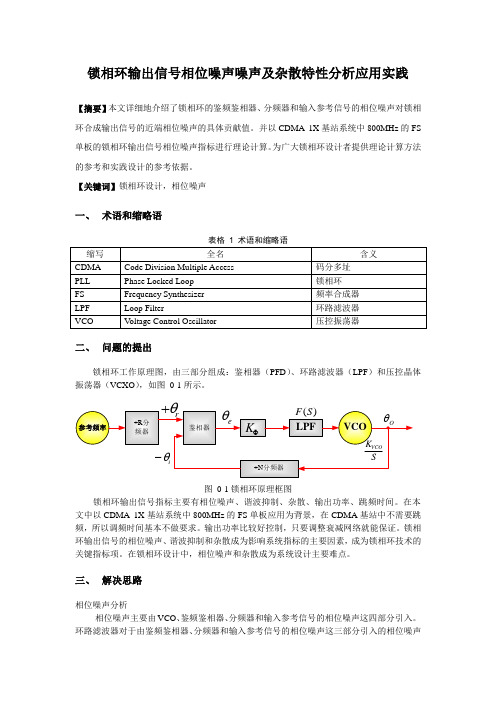

【关键词】锁相环设计,相位噪声一、术语和缩略语表格 1 术语和缩略语二、问题的提出锁相环工作原理图,由三部分组成:鉴相器(PFD)、环路滤波器(LPF)和压控晶体振荡器(VCXO),如图0-1所示。

图0-1锁相环原理框图锁相环输出信号指标主要有相位噪声、谐波抑制、杂散、输出功率、跳频时间。

在本文中以CDMA 1X基站系统中800MHz的FS单板应用为背景,在CDMA基站中不需要跳频,所以调频时间基本不做要求。

输出功率比较好控制,只要调整衰减网络就能保证。

锁相环输出信号的相位噪声、谐波抑制和杂散成为影响系统指标的主要因素,成为锁相环技术的关键指标项。

在锁相环设计中,相位噪声和杂散成为系统设计主要难点。

三、解决思路相位噪声分析相位噪声主要由VCO、鉴频鉴相器、分频器和输入参考信号的相位噪声这四部分引入。

环路滤波器对于由鉴频鉴相器、分频器和输入参考信号的相位噪声这三部分引入的相位噪声具有低通特性,对于VCO产生的相位噪声具有高通特性。

一般来说环路带宽内的相位噪声主要决定于由鉴频鉴相器、分频器和输入参考信号,环路带宽以外的相位噪声主要决定于VCO,在环路带宽周围,这四部分的噪声影响相当。

所以为了尽量降低输出信号的相位噪声环路滤波器的环路带宽的最佳点是由鉴频鉴相器、分频器和输入参考信号的相位噪声这三部分引入的相位噪声总和与VCO引入的相位噪声相同时的频率。

在实际运用中还礼滤波器的设计是非常重要的。

对于远端相位噪声如100KHz和1MHz处的一般远远高于环路带宽,其相位噪声主要决定于VCO,要保证其指标主要是选择良好的VCO。

改善锁相环相位噪声的方法

改善锁相环相位噪声的方法锁相环(Phase-Locked Loop, PLL)是一种常用的频率合成器和时钟恢复方法。

然而,在某些应用中,锁相环的相位噪声成为限制系统性能的因素。

因此,改善锁相环相位噪声是一个重要的课题。

下面将介绍几种改善锁相环相位噪声的方法。

首先,一个容易实施的方法是优化锁相环的环路滤波器。

环路滤波器的设计直接影响锁相环的带宽和噪声性能。

通过增加滤波器的阻尼比,可以提高锁相环的稳定性和减小相位噪声。

另外,合理选择滤波器的带宽,可以平衡相位追踪性能和噪声抑制能力,从而改善锁相环的相位噪声。

其次,采用抖动降低技术可以有效减小锁相环的相位噪声。

抖动降低技术基于频率抖动和相位抖动之间的关系,通过控制频率抖动来减小相位噪声。

常用的抖动降低技术包括相位锁定环(Phase-Locked Loop, PPL)、时钟周期抖动降低技术等。

这些技术通过引入额外的控制环路或采用特殊的抖动降低算法,可以显著改善锁相环的相位噪声性能。

第三,优化参考信号源也是改善锁相环相位噪声的有效方法。

参考信号源的噪声特性直接传递到锁相环的输出。

因此,选择低噪声的参考信号源对于改善锁相环的相位噪声非常重要。

常见的低噪声参考信号源包括晶体振荡器(Crystal Oscillator, XO)或原子钟等。

通过使用低噪声的参考信号源,可以有效降低锁相环的相位噪声。

总结起来,改善锁相环相位噪声的方法包括优化环路滤波器、采用抖动降低技术和选择低噪声的参考信号源。

通过合理应用这些方法,可以显著提升锁相环的相位噪声性能,从而满足不同应用对于相位噪声的要求。

锁相环的关键指标

锁相环的关键指标一、引言锁相环(Phase-Locked Loop,简称PLL)是一种常用的电子控制系统,用于在输入信号和参考信号之间建立相位关系。

它在通信、数据转换和时钟同步等领域有着广泛的应用。

在设计和评估锁相环时,需要考虑一些关键指标,以确保其性能和稳定性。

本文将就锁相环的关键指标展开讨论。

二、锁相环的基本原理在了解锁相环的关键指标之前,我们先来简要了解一下锁相环的基本原理。

锁相环由相位比较器、低通滤波器、电压控制振荡器和分频器等组成。

其工作原理是通过不断调整电压控制振荡器的频率,使得相位比较器输出的误差信号趋近于零。

这样,输入信号和参考信号之间就能够建立起稳定的相位关系。

三、锁相环的关键指标锁相环的性能和稳定性受多个指标的影响。

下面将分别介绍这些指标。

3.1 带宽锁相环的带宽是指其输出相位响应的频率范围。

带宽越宽,锁相环对频率变化的响应越快。

通常情况下,带宽越宽,锁相环的性能越好。

但同时也需要考虑到带宽过宽可能导致噪声增加和稳定性下降的问题。

3.2 相位噪声相位噪声是指锁相环输出信号的相位随时间变化的不稳定性。

相位噪声越小,锁相环的性能越好。

相位噪声可以通过频域分析来评估,常用的评估指标包括相位噪声密度和积分相位噪声。

3.3 锁定时间锁定时间是指锁相环从初始状态到稳定状态所需的时间。

锁定时间越短,锁相环的性能越好。

锁定时间受到带宽和相位噪声等因素的影响。

3.4 抖动抖动是指锁相环输出信号的瞬时频率偏离其平均频率的程度。

抖动越小,锁相环的性能越好。

抖动可以通过时域分析来评估,常用的评估指标包括峰峰值抖动和均方根抖动。

3.5 稳定性锁相环的稳定性是指其输出信号在长时间内保持稳定的能力。

稳定性受到带宽、相位噪声和抖动等因素的影响。

稳定性可以通过频域和时域分析来评估。

四、评估锁相环的关键指标为了评估锁相环的关键指标,可以采取以下步骤:1.设计合适的测试电路,包括输入信号源和参考信号源。

2.使用合适的测量设备,如频谱分析仪、示波器和时钟分析仪等,对锁相环的输出信号进行测量。

锁相环频率合成器的相位噪声分析

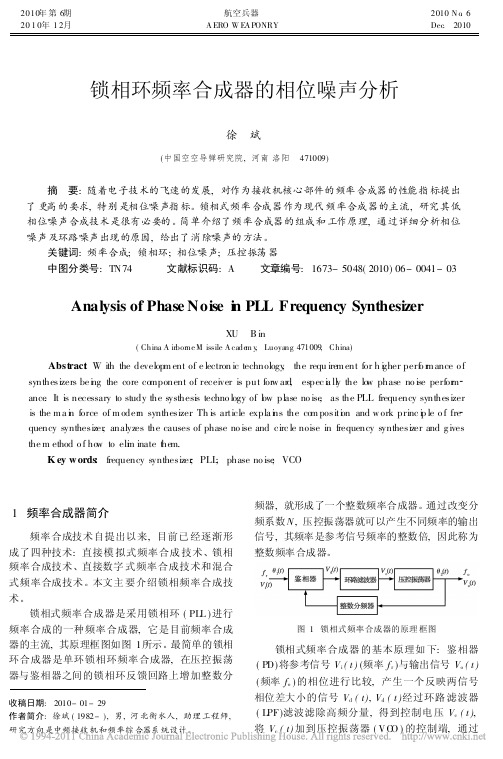

图 1 锁相式频率合成器的原理 框图

锁相式频率合成器 的基本原理如 下: 鉴相器 ( PD) 将参考信号 V i ( t ) (频率 f r )与输出信号 Vo ( t ) ( 频率 fo ) 的相位进行比较, 产生一个反映两信号 相位差大小的信号 Vd ( t) , Vd ( t ) 经过环路 滤波器 ( LPF )滤波滤除高频分量 , 得到控制电 压 Vc ( t ), 将 Vc ( t) 加到压控振荡器 ( VCO ) 的控制端, 通过

42

航空兵器

2010 年第 6 期

VCO 使得输出频率 fo 向 f r 靠拢 , 直到消除相差使 环路锁定。

令

pd

2 锁相环路中的相位噪声

锁相环频率合成器主要由倍频器、放大器、分 频器、混频器、鉴相器、 压控振荡器 ( VCO) 等基本 电路组成, 有的还包括辅助捕获电路、跳频控制电 路和电子开关等, 它们都不同程度地将噪声引入 频率合成器中, 因此对频率合成器各组成部件噪 声的研究就很有必要。 2 . 1 鉴相器对环路噪声的影响 鉴相器是 PLL 的关键部件之一, 它有许多不 同的类型和电路形式。目前较常用的鉴相器基本 上可分为两大类: 乘法器 ( 或逻辑组合 ) 电路和时 序电路。 这里主要讨论乘法器类鉴相器。 乘法器类 鉴相器将输 入信号波 形与本地 振荡器波 形相乘 , 并把乘积的平均值作为其有用的直流输出, 一个 设计正确的乘法器鉴相器可以对淹没在极大噪声 中的输入信号进行处理。 这里假设 PLL 环路是线性的, 鉴相器是理想 的。鉴相器引入的噪声用一个外加的等效干扰噪 声电压 vpd ( s) 代替 , 如图 2 所示。

1 频率合成器简介

频率合成技术自提出以来 , 目前已 经逐渐形 成了四种技术 : 直接模 拟式频率合成 技术、锁相 频率合成技术、直接数字 式频率合成技术和混合 式频率合成技术。本文主 要介绍锁相频率合成技 术。 锁相式频率合成器是采用锁相环 ( PLL ) 进行 频率合成的一种频率合成器, 它是目前频率合成 器的主流, 其原理框图如图 1 所示。 最简单的锁相 环合成器是单环锁相环频率合成器, 在压控振荡 器与鉴相器之间的锁相环反馈回路上增加整数分

锁相环输出信号相位噪声噪声及杂散特性分析应用实践

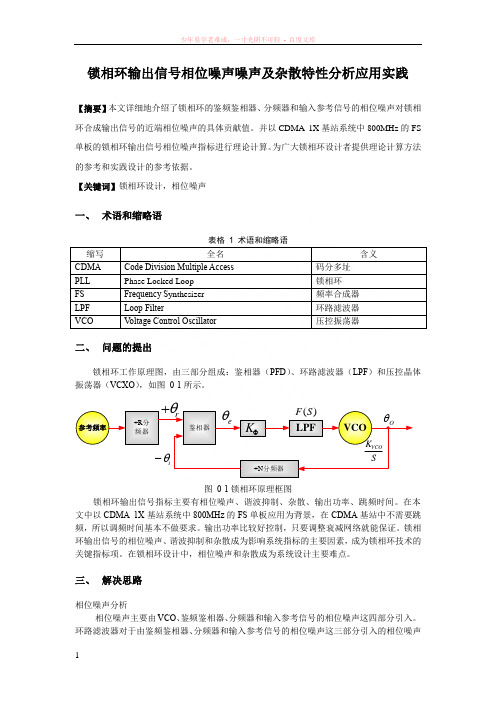

锁相环输出信号相位噪声噪声及杂散特性分析应用实践【摘要】本文详细地介绍了锁相环的鉴频鉴相器、分频器和输入参考信号的相位噪声对锁相环合成输出信号的近端相位噪声的具体贡献值。

并以CDMA 1X 基站系统中800MHz 的FS 单板的锁相环输出信号相位噪声指标进行理论计算。

为广大锁相环设计者提供理论计算方法的参考和实践设计的参考依据。

【关键词】锁相环设计,相位噪声一、 术语和缩略语表格 1 术语和缩略语 缩写全名 含义 CDMACode Division Multiple Access 码分多址 PLLPhase Locked Loop 锁相环 FSFrequency S ynthesizer 频率合成器 LPFLoop Filter 环路滤波器 VCO Voltage Control Oscillator压控振荡器 二、 问题的提出锁相环工作原理图,由三部分组成:鉴相器(PFD )、环路滤波器(LPF )和压控晶体振荡器(VCXO ),如图 0-1所示。

÷R 分频器VCO 参考频率鉴相器÷N 分频器LPF ΦK O θS K VCO )(S F rθ+iθ-e θ图 0-1锁相环原理框图锁相环输出信号指标主要有相位噪声、谐波抑制、杂散、输出功率、跳频时间。

在本文中以CDMA 1X 基站系统中800MHz 的FS 单板应用为背景,在CDMA 基站中不需要跳频,所以调频时间基本不做要求。

输出功率比较好控制,只要调整衰减网络就能保证。

锁相环输出信号的相位噪声、谐波抑制和杂散成为影响系统指标的主要因素,成为锁相环技术的关键指标项。

在锁相环设计中,相位噪声和杂散成为系统设计主要难点。

三、 解决思路相位噪声分析相位噪声主要由VCO 、鉴频鉴相器、分频器和输入参考信号的相位噪声这四部分引入。

环路滤波器对于由鉴频鉴相器、分频器和输入参考信号的相位噪声这三部分引入的相位噪声具有低通特性,对于VCO产生的相位噪声具有高通特性。

锁相环 相位噪声

锁相环相位噪声锁相环是一种常用的电路技术,用于抑制信号中的相位噪声。

相位噪声是指信号中的相位变化不稳定性,它可以导致信号的频偏和抖动,影响系统的性能和稳定性。

锁相环通过比较输入信号和参考信号的相位差,然后通过反馈调节输入信号的相位,以达到消除相位噪声的目的。

在现代通信系统中,相位噪声是一个非常重要的问题。

相位噪声的存在会导致信号的频谱扩展,降低系统的信噪比,影响通信质量。

因此,研究和解决相位噪声问题对于提高通信系统的性能至关重要。

锁相环通过利用负反馈原理来消除相位噪声。

它由相位检测器、低通滤波器、电压控制振荡器和除相器等组成。

首先,相位检测器将输入信号和参考信号进行比较,产生相位误差信号。

然后,低通滤波器对相位误差信号进行滤波,得到控制电压。

接下来,电压控制振荡器根据控制电压来调节输出信号的相位。

最后,除相器将输出信号和参考信号进行比较,得到反馈信号,闭环控制系统实现了相位的稳定。

锁相环的关键是相位检测器。

常用的相位检测器有边沿检测器、比较器和混频器等。

边沿检测器通过检测信号的边沿来获得相位信息,适用于高频信号。

比较器通过比较两个信号的幅值来获得相位信息,适用于低频信号。

混频器通过将信号与参考信号相乘,然后滤波得到直流分量来获得相位信息,适用于宽频带信号。

除了相位检测器,滤波器也是锁相环中的重要组成部分。

低通滤波器的作用是滤除高频噪声,使得控制电压变化平稳。

滤波器的带宽决定了锁相环对相位噪声的抑制能力。

带宽越宽,抑制能力越强,但相应的噪声增益也会增加。

因此,在选择滤波器带宽时需要进行权衡。

锁相环的另一个关键参数是环路带宽。

环路带宽决定了锁相环的跟踪能力和响应速度。

带宽越高,跟踪能力越好,但相应的稳定性也会降低。

因此,在设计锁相环时需要根据具体应用需求来选择合适的环路带宽。

除了上述基本结构,锁相环还可以通过添加频率鉴频器、倍频器和除频器等模块来实现更复杂的功能。

例如,可以利用频率鉴频器来实现频率锁定,将输入信号的频率锁定到参考信号的频率上。

锁相环指标 -回复

锁相环指标-回复什么是锁相环指标?锁相环指标是指用来衡量锁相环(Phase-Locked Loop,PLL)性能的各种参数和指标。

PLL是一种电路系统,通过对输入信号的相位进行比较,并根据比较结果调整本身输出信号的相位,从而使输出信号保持与输入信号的相位同步。

在各种通信、控制和测量领域,PLL已经广泛应用。

而锁相环指标则是评估PLL工作性能和稳定度的重要依据。

有哪些常见的锁相环指标?实际上,锁相环的指标非常多,并且根据具体应用的不同可能略有差异。

下面列举几个常见的锁相环指标:1. 锁定时间(Lock time):指PLL从失锁状态转变为锁定状态所需要的时间。

锁定时间短是衡量PLL性能和适用性的重要指标之一。

2. 锁定范围(Lock range):指PLL在输入信号频率范围内能够保持稳定锁定的能力。

通常用频率范围或相位范围来表示。

3. 噪声性能(Noise performance):指PLL对输入信号中的噪声和扰动的抵抗能力。

好的锁相环应该能够在抑制噪声的同时保持输出信号的稳定性。

4. 抖动(Jitter):指信号在时间上的不稳定性,可以通过锁相环来降低抖动。

抖动越小,表明锁相环性能越好。

5. 相位噪声(Phase noise):指锁相环输出信号相位随时间的变化情况。

相位噪声小的锁相环输出信号更加稳定。

6. 频率稳定度(Frequency stability):指锁相环输出信号频率的变化程度。

频率稳定度好的锁相环输出信号与输入信号的频率差距很小。

以上仅为锁相环指标中的几个常见要素,根据不同应用的需求,可能还会有其他更具体的指标。

锁相环指标如何优化?优化锁相环指标是实际应用中非常重要的任务,因为合理的指标设计和优化可以提高PLL的性能,提高系统的可靠性和稳定性。

1. 设计合适的环路带宽:适当选择环路带宽可以平衡相位噪声和锁定时间的要求。

过高的带宽容易引入噪声,过低的带宽又会增加锁定时间。

2. 添加滤波器:通过添加滤波器来抑制输入信号中的噪声和频率扰动,从而提高锁相环的噪声性能和稳定性。

利用双压控晶振降低锁相环中的相位噪声赵晨

of PLL. Using double VCXO will decrease phase noise of PLL, improve the performances of whole system.

Key words: VCXO; PLL; Phase Noise

中图分类号:TP73

文献标识码:B

PLL 的实施方案可以采用全数字方式、全模拟或混合电路, 目前混合电路方案居多。

图 1 接收机方案框图

20 世纪 50 年代,伴随着电视机进入实用化进程,PLL 开始得 以广泛使用,最为代表性的为电视机中的 AFC(自动频率控制) 电路。20 世纪 70 年代民用无线电收发报机中的本振(LO)开始 广泛使用 PLL 电路,并由此开发了多种 PLL 集成电路。随着计 算机技术的进步和 PLL 电路集成化程度进一步提高,PLL 电路的 应用前景日趋广泛。例如目前 PLL 已成为现代通讯系统的基本 构建模块,为无线电接收机和发射极提供稳定可靠的 LO;也可 由于时钟信号分配和降噪;以及高速率采样模式转换(A/D)的时 钟源。

的影响,进而提升系统的性能。

关键词:VCXO;PLL;相位噪声

Abstract: Pll is a important part of modern electronic system. It’s a guarantee of whole system that improved performance

3 压控晶振的基本特性 3.1 压控晶振简介

利用调节直流电压改变主振级变容二极管的电容,从而改 变晶振输出的频率,这样的晶振称作压控晶振。晶振是目前获 得最好相位噪声的技术方案。晶振利用晶体的压电效应与振荡 电路产生谐振获得振荡电信号,经放大输出即可获得标准频率 信号。晶振的等效电路如图 3 所示,图中 R1为等效电阻,C1为动 态电容,L1 为等效电感,C0 为静态电容,Re 为晶体阻抗的电阻部 分,Jx 为晶体阻抗的电抗部分。从晶体的等效电路可知,晶体有 一个串联谐振频率 fs和并联谐振频率 fp。

数字锁相环的相位噪声分析

电气传动2021年第51卷第11期摘要:随着信息化社会的发展,数字锁相环越发受研发人员的重视。

而相位噪声是衡量数字锁相环性能的关键技术,更是研究的重点。

介绍数字锁相环的组成结构和工作原理,建立环路各个模块的相位噪声模型,从闪烁噪声和白噪声的特性入手,定性分析相位噪声的影响因素,并针对电荷泵增益和环路滤波器阻抗对锁相环电路相位噪声的影响进行了仿真,进一步验证了分析结果,为设计高性能的数字锁相环提供理论基础。

关键词:数字锁相环;相位噪声;振荡器;电荷泵;环路滤波器中图分类号:TM28文献标识码:ADOI :10.19457/j.1001-2095.dqcd21463Analysis of Phase Noise in Digital Phase -locked Loop ZHANG Zhanrong 1,WANG Yunfei 2,QU Meixia 2,ZHAO Li 3(1.Department of Mechanical and Electrical Engineering ,Ordos Vocational College ofEco-environment ,Ordos 017010,Nei Moggol ,China ;2.Basic Department ,Ordos Vocational College of Eco-environment ,Ordos 017010,Nei Moggol ,China ;3.School of Software ,Shanxi University ,Taiyuan 030013,Shanxi ,China )Abstract:With the development of information society ,digital phase-locked loop (DPLL )attracts more and more attention of researchers.As the key technology to evaluate the performance of DPLL ,phase noise becomes the key point of the study.The structure and work principle of DPLL were introduced ,the phase noise model of each module of the loop was established.Starting from the characteristics of flicker noise and white noise ,the influence factors of phase noise were analyzed qualitatively ,and the influence of charge pump gain and loop filter impedance on phase noise of PLL circuit was simulated to further verify the analysis results.The theoretical basis was provided for improving the phase noise performance of DPLL.Key words:digital phase-locked loop (DPLL );phase noise ;oscillator ;charge pump ;loop filter基金项目:山西省科技厅基础研究计划项目—青年科技研究基金(2014021039-6)作者简介:张占荣(1969—),男,本科,副教授,Email :131****************数字锁相环的相位噪声分析张占荣1,王云飞2,屈美霞2,赵丽3(1.鄂尔多斯生态环境职业学院机电工程系,内蒙古鄂尔多斯017010;2.鄂尔多斯生态环境职业学院基础部,内蒙古鄂尔多斯017010;3.山西大学软件学院,山西太原030013)现代频率源一般是由直接频率合成、间接频率合成和直接数字频率合成这三种合成技术实现的[1]。

关于相位噪声分析

关于相位噪声的分析大家都知道,相位噪声是频率域的概念,这里我们就先讲一下时域分析和频域分析:频域是描述信号在频率方面特性时用到的一种坐标系。

对任何一个事物的描述都需要从多个方面进行,每一方面的描述仅为我们认识这个事物提供部分的信息。

对于一个信号来说,它也有很多方面的特性,如信号强度随时间的变化规律(时域特性),信号是由哪些单一频率的信号合成的(频域特性)。

时域分析与频域分析是对模拟信号的两个观察面。

时域分析是以时间轴为坐标表示动态信号的关系;频域分析是把信号变为以频率轴为坐标表示出来。

一般来说,时域的表示较为形象与直观,频域分析则更为简练,剖析问题更为深刻和方便。

目前,信号分析的趋势是从时域向频域发展。

然而,它们是互相联系,缺一不可,相辅相成的。

抖动测量一直被称为示波器测试测量的最高境界。

传统最直观的抖动测量方法是利用余辉来查看波形的变化。

后来演变为高等数学概率统计上的艰深问题,抖动测量结果准还是不准的问题就于是变得更加复杂。

时钟的特性可以用频率计测量频率的稳定度,用频谱仪测量相噪,用示波器测量TIE抖动、周期抖动、cycle-cycle抖动。

关于相位噪声分析仪的更多信息请和小安联系,QQ894 959 252;联系电话: 189 **** ****但是更深层次的时域测量方法和频域测量方法的原理, TIE抖动和相噪抖动之间关系的推导推导,我们在网上搜集为大家提供一篇高人提供的文档,希望对仍然纠结在这些问题迷雾中的朋友们有所启发:抖动是衡量时钟性能的重要指标,抖动一般定义为信号在某特定时刻相对于其理想位置的短期偏移。

这个短期偏移在时域的表现形式为抖动(这里的抖动专指时域抖动),在频域的表现形式为相噪。

本文主要探讨下时钟抖动和相噪以及其测量方法,以及两者之间的关系。

1、抖动介绍抖动是对时域信号的测量结果,反映了信号边沿相对其理想位置偏离了多少。

抖动有两种主要成分:确定性抖动和随机抖动。

确定性抖动是可以重复和预测的,其峰峰值是有界的,通常意义上的DJ是指其pk-pk值;随机抖动是不能预测的定时噪声,分析时一般使用高斯分布来近似表征,理论上可以偏离中间值无限大,所以随机抖动是没有峰到峰边界的,通常意义上的RJ指标是指其RMS 值,可以根据其RMS值推算其在一定误码率时的值。

锁相环近端相位噪声

锁相环近端相位噪声锁相环近端相位噪声是现代通信和信号处理领域中一个重要的概念。

在本文中,我们将深入研究锁相环近端相位噪声的定义、原因,以及其对系统性能的影响。

通过从简到繁的方式,逐步展开论述,希望能给读者带来全面、深刻和灵活的理解。

1. 什么是锁相环近端相位噪声锁相环近端相位噪声是指在锁相环内部产生的相位抖动。

在锁相环中,相位噪声是由多种因素产生的,如参考源、振荡器、放大器等。

近端相位噪声可以通过衡量锁相环输出信号的相位变化来评估,通常以分贝(dBc)为单位表示。

2. 锁相环近端相位噪声的原因锁相环近端相位噪声的主要原因可以归结为以下几点:- 振荡器的噪声:振荡器是锁相环中最重要的组成部分之一,其本身的噪声会对系统性能产生较大影响。

振荡器的噪声主要由两方面因素决定,即抖动和频率噪声。

- 参考源的不稳定性:锁相环的性能主要取决于参考源的稳定性。

如果参考源的相位不稳定,将会导致锁相环输出的相位抖动。

- 放大器的噪声:放大器在信号处理过程中发挥着重要的作用,然而放大器本身也会引入噪声,这些噪声会增加锁相环近端相位噪声的水平。

3. 锁相环近端相位噪声对系统性能的影响锁相环近端相位噪声对于系统的性能有着重要的影响。

它会显著降低系统的信号质量、容易引发震荡,同时还会增加系统的位错误率。

锁相环近端相位噪声还可能导致时钟抖动、时钟漂移等问题,特别是在高精度的通信和信号处理系统中,这种影响更为显著。

4. 个人观点和理解在我看来,锁相环近端相位噪声是一个令人头疼的问题。

虽然锁相环本身是一种非常强大的技术,可以用来抑制相位噪声和频率噪声,提高系统性能,但近端相位噪声的存在限制了其应用范围。

研究如何减小锁相环近端相位噪声,提高系统稳定性和性能是非常重要的。

为了应对锁相环近端相位噪声带来的挑战,我认为我们应该采取以下几个方面的策略:- 加强振荡器的设计和优化,提高其抗噪声能力和稳定性;- 优化参考源的设计,减小相位抖动;- 采用低噪声放大器,降低放大器引入的噪声水平;- 引入噪声补偿技术,抵消近端相位噪声的影响;- 进一步研究和开发新的锁相环结构和算法,以提高系统的稳定性和性能。

[原创]在单片机中锁相环功能

![[原创]在单片机中锁相环功能](https://img.taocdn.com/s3/m/5907d3015e0e7cd184254b35eefdc8d376ee147c.png)

在单片机中锁相环功能锁相环是指一种电路或者模块,它用于在通信的接收机中,其作用是对接收到的信号进行处理,并从其中提取某个时钟的相位信息。

或者说,对于接收到的信号,仿制一个时钟信号,使得这两个信号从某种角度来看是同步的(或者说,相干的)。

由于锁定情形下(即完成捕捉后),该仿制的时钟信号相对于接收到的信号中的时钟信号具有一定的相差,所以很形象地称其为锁相器。

而一般情形下,这种锁相环的三个组成部分和相应的运作机理是:1 鉴相器:用于判断锁相器所输出的时钟信号和接收信号中的时钟的相差的幅度;2 可调相/调频的时钟发生器器:用于根据鉴相器所输出的信号来适当的调节锁相器内部的时钟输出信号的频率或者相位,使得锁相器完成上述的固定相差功能;3 环路滤波器:用于对鉴相器的输出信号进行滤波和平滑,大多数情形下是一个低通滤波器,用于滤除由于数据的变化和其他不稳定因素对整个模块的影响。

从上可以看出,大致有如下框图:┌—————┐ ┌—————┐ ┌———————┐→—┤ 鉴相器├—→—┤环路滤波器├—→—┤受控时钟发生器├→┬—→└——┬——┘ └—————┘ └———————┘ │ ↑ ↓└——————————————————————————┘可见,是一个负反馈环路结构,所以一般称为锁相环(PLL: Phase Locking Loop)锁相环有很多种类,可以是数字的也可以是模拟的也可以是混合的,可以用于恢复载波也可以用于恢复基带信号时钟锁相环锁相环:为无线电发射中使频率较为稳定的一种方法,主要有VCO(压控振荡器)和PLL IC ,压控振荡器给出一个信号,一部分作为输出,另一部分通过分频与PLL IC所产生的本振信号作相位比较,为了保持频率不变,就要求相位差不发生改变,如果有相位差的变化,则PLL IC的电压输出端的电压发生变化,去控制VCO,直到相位差恢复!达到锁频的目的!!能使受控振荡器的频率和相位均与输入信号保持确定关系的闭环电子电路。

减小锁相环锁定时间的措施

减小锁相环锁定时间的措施

减小锁相环锁定时间的措施有以下几种:

1. 增加锁相环的带宽:通过增加锁相环的带宽,可以提高锁相环系统的频率响应。

这可以通过增加锁相环环路滤波器的带宽或增加放大器的带宽来实现。

2. 使用自适应滤波器:自适应滤波器可以根据输入信号的频率变化自动调整锁相环的带宽。

这可以有效地减小锁相环的锁定时间。

3. 使用预测性滤波器:预测性滤波器可以根据过去的输入信号数据预测未来的输入信号数据,并据此调整锁相环的带宽。

这可以提前适应输入信号的频率变化,进而减小锁定时间。

4. 优化锁相环参数:锁相环的参数设置对于锁定时间很关键。

通过优化锁相环的参数,例如增益、相位裕度等,可以显著减小锁定时间。

5. 使用锁相环的预估模型:锁相环的预估模型可以用于估计输入信号的频率变化,并据此调整锁相环的带宽。

这可以提前适应输入信号的频率变化,从而减小锁定时间。

总的来说,通过增加锁相环的带宽、使用自适应滤波器、使用预测性滤波器、优化锁相环参数、使用锁相环的预估模型等措施,可以有效地减小锁相环的锁定时间。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

相位噪声对一个给定载波功率的输出频率来说,相位噪声是载波功率相对于给定的频率偏移处(频率合成器通常定义1kHz频率偏移)1-Hz的带宽上的功率,单位为dBc/Hz@offset frequency。

锁相环频率合成器的带内相位噪声主要取决于频率合成器,VCO的贡献很小。

相位噪声的测量需要频谱分析仪。

注意一点,普通频谱分析仪读出的数据需要考虑分辨带宽的影响。

即,频谱分析仪的读数减掉10log(RBW)才是正确的相位噪声数值。

高端的频谱分析仪往往可以直接给出单边带相位噪声。

相位噪声是信号在频域的度量。

在时域,与之对应的是时钟抖动(jitter),它是相位噪声在时间域里的反映,大的时钟抖动在高速ADC应用中会严重恶化采样数据的信噪比,尤其是当ADC模拟前端信号的频率较高时,更是要求低抖动的时钟。

图1形象地描述了时钟抖动。

图表 1 相位噪声和时钟抖动时钟抖动可以通过相位噪声积分得到,具体实现如下如下:计算从给定的起始频率偏移处到结束频率(通常定义为两倍输出频率)偏移处的相位噪声和A,单位为dBc;对A进行取对数操作;求相位抖动均方值(rms phase jitter),单位为弧度;将弧度值转换成时间单位,秒或者皮秒。

图表 2. 时钟抖动与相位噪声和白噪声之间的关系参考杂散锁相环中最常见的杂散信号就是参考杂散。

这些杂散信号会由于电荷泵源电流与汇电流的失配,电荷泵漏电流,以及电源退耦不够而增大。

在接收机设计中,杂散信号与其他干扰信号相混频有可能产生有用信号频率从而降低接收机的灵敏度。

锁相环处于锁定状态时,电荷泵会周期性的(频率等于鉴相频率)产生交替变换(正负)脉冲电流给环路滤波器。

环路滤波器对其进行积分产生稳定的控制电压。

图表 3 环路锁定时,PLL电荷泵电流输出波形当鉴相频率较低时,由电荷泵的漏电流引起的杂散占主要地位。

当鉴相频率较高时,由电荷泵的交替电流(源电流I和汇电流I)引起的杂散占主要地位。

sourcesink二者频率的界定。

一般地,若电荷泵漏电流为1nA,电荷泵电流为1mA,电荷泵电流的失配在4%时,交界频率大约为100k~200kHz。

当电荷泵处于三态的时候(绝大部分时间是如此),电荷泵的漏电流是杂散的主要来源。

电荷泵漏电流经过环路滤波器形成控制电压,以调谐VCO,这样就相当于对VCO进行调频(FM),反映在VCO的输出,就会出现杂散信号。

电荷泵漏电流越大,鉴相频率越低,这种参考杂散越大。

在鉴相频率相等的条件下,电荷泵的漏电流与电荷泵电流的比值越大,由电荷泵漏电流引起的参考杂散会越大。

ADI的PLL产品漏电流大部分在1nA左右的水平上。

为了对电荷泵漏电流引起的杂散有个清楚地认识,这里给出一些仿真波形。

仿真条件如下:ADF4106,输出频率1GHz,鉴相频率25kHz,三阶无源滤波器,带宽2.5Hz,相位裕度45度,VCO 模型为Sirenza VCO190-1000T。

参考晶振模型10MHz。

电荷泵漏电流1nA。

当环路滤波器变窄到1kHz后可以看到对这种杂散的衰减效果如下。

当电荷泵工作时,电荷泵的交替脉冲电流是杂散的主要来源。

定义电荷泵源电流(Source current)与汇电流(Sink current)的失配程度。

杂散增益的定义,锁定时间锁相环从一个指定频率跳变到另一个指定频率(在给定的频率误差范围内)所用的时间就是锁定时间。

频率跳变的步长取决于PLL频率合成器工作在限定的系统频带上所能达到的最大的频率跳变能力。

例如,GSM-900,频率步长最大为45MHz,而GSM-1800为95MHz。

容许的频率误差分别为90Hz和180Hz。

PLL频率合成器必须在小于1.5个时隙(GSM的一个时隙是577us)内达到锁定。

锁定时间还需要另外一个指标来度量,即PLL频率合成器输出达到给定相位误差范围所用的时间。

图3是ADI提供的一种测量相位锁定的方法,该方法利用ADI的增益/相位联合检波器AD8302实现。

图表 4. 相位锁定时间测量的一种方法参考晶振有哪些要求?我该如何选择参考源?波形:可以使正弦波,也可以为方波。

功率:满足参考输入灵敏度的要求。

稳定性:通常用TCXO,稳定性要求< 2 ppm。

这里给出几种参考的稳定性指标和相位噪声指标。

频率范围:ADI提供的PLL产品也可以工作在低于最小的参考输入频率下,条件是输入信号的转换速率要满足给定的要求。

例如,ADF4106的数据手册要求的最小参考输入信号REFIN为20MHz,功率最小为-5dBm,这相当于转换速率(slew rate)为22.6V/us,峰峰值为360mV的正弦波。

具体计算如下:对正弦波Vp*sin(2*pi*f*t)而言,转换速率Slew Rate=dv/dt|max=2*pi*f*Vp。

那么我们来考察功率为-5dBm(50欧姆系统)(Vp=180mV)的信号,其峰峰值为360mV,其转换速率为Slew Rate=dv/dt|max=2*pi*f*Vp=22.6V/us所以,只要REFIN功率满足要求,并且输入信号的转换速率高于22.6V/us ,REFIN可以工作在低于20MHz的条件下。

具体实现是,一个转换时间为146ns的3.3V CMOS输入可以很容易的满足该项要求。

总的来说,用功率较大的方波信号作为参考可以使REFIN工作在低于数据手册上给出的最低频率限制。

请详细解释一下控制时序,电平及要求。

ADI的所有锁相环产品控制接口均为三线串行控制接口。

如图4所示。

图表 5 PLL频率合成器的串行控制接口(3 Wire Serial Interface)PLL频率合成器的串行控制接口(3 Wire Serial Interface)控制接口由时钟CLOCK,数据DATA,加载使能LE构成。

加载使能LE的下降沿提供起始串行数据的同步。

串行数据先移位到PLL频率合成器的移位寄存器中,然后在LE的上升沿更新内部相应寄存器。

SPI控制接口为3V/3.3V CMOS电平。

控制信号的产生,可以用MCU,DSP,或者FPGA。

产生的时钟和数据一定要干净,过冲小。

当用FPGA 产生时,要避免竞争和冒险现象,防止产生毛刺。

如果毛刺无法避免,可以在数据线和时钟线上并联一个10~47pF的电容,来吸收这些毛刺。

请简要介绍一下环路滤波器参数的设置ADISimPLL V3.0使应用工程师从繁杂的数学计算中解脱出来。

我们只要输入设置环路滤波器的几个关键参数,ADISimPLL就可以自动计算出我们所需要的滤波器元器件的数值。

这些参数包括,鉴相频率PFD,电荷泵电流Icp,环路带宽BW,相位裕度,VCO控制灵敏度Kv,滤波器的形式(有源还是无源,阶数)。

计算出的结果往往不是我们在市面上能够买到的元器件数值,只要选择一个最接近元器件的就可以。

通常环路的带宽设置为鉴相频率的1/10或者1/20。

相位裕度设置为45度。

滤波器优先选择无源滤波器。

滤波器开环增益和闭环增益以及相位噪声图之间的关系。

闭环增益的转折频率就是环路带宽。

相位噪声图上,该点对应于相位噪声曲线的转折频率。

如果设计的锁相环噪声太大,就会出现频谱分析仪上看到的转折频率大于所设定的环路带宽。

环路滤波器采用有源滤波器还是无源滤波器?有源滤波器因为采用放大器而引入噪声,所以采用有源滤波器的PLL产生的频率的相位噪声性能会比采用无源滤波器的PLL输出差。

因此在设计中我们尽量选用无源滤波器。

其中三阶无源滤波器是最常用的一种结构。

PLL频率合成器的电荷泵电压Vp一般取5V或者稍高,电荷泵电流通过环路滤波器积分后的最大控制电压低于Vp或者接近Vp。

如果VCO/VCXO的控制电压在此范围之内,无源滤波器完全能够胜任。

当VCO/VCXO的控制电压超出了Vp,或者非常接近Vp的时候,就需要用有源滤波器。

在对环路误差信号进行滤波的同时,也提供一定的增益,从而调整VCO/VCXO控制电压到合适的范围。

那么如何选择有源滤波器的放大器呢?这类应用主要关心一下的技术指标:低失调电压(Low Offset Voltage)[通常小于500uV]低偏流(Low Bias Current)[通常小于50pA]如果是单电源供电,需要考虑使用轨到轨(Rail-to-Rail)输出型放大器。

这里提供几种常见的PLL滤波器应用放大器的型号。

AD711/2, AD797, AD820/2, AD8510/2, AD8605/6, AD8610/20, AD8651/2, OP162/262, OP184/284, OP249, OP27,PLL对于VCO有什么要求?以及如何设计VCO输出功率分配器?选择VCO时,尽量选择VCO的输出频率对应的控制电压在可用调谐电压范围的中点。

选用低控制电压的VCO可以简化PLL设计。

VCO的输出通过一个简单的电阻分配网络来完成功率分配。

从VCO的输出看到电阻网络的阻抗为18+(18+50)//(18+50)=52ohm。

形成与VCO的输出阻抗匹配。

下图中ABC三点功率关系。

B,C点的功率比A点小6dB。

如何设置电荷泵的极性?在下列情况下,电荷泵的极性为正。

环路滤波器为无源滤波器,VCO的控制灵敏度为正(即,随着控制电压的升高,输出频率增大)。

在下列情况下,电荷泵的极性为负。

环路滤波器为有源滤波器,并且放大环节为反相放大;VCO的控制灵敏度为正。

环路滤波器为无源滤波器,VCO的控制灵敏度为负。

PLL分频应用,滤波器为无源型。

即参考信号直接RF反馈分频输入端,VCO反馈到参考输入的情况锁定指示电路如何设计?PLL锁定指示分为模拟锁定指示和数字锁定指示两种图表 6 鉴相器和电荷泵原理图数字锁定指示:当PFD的输入端连续检测到相位误差小于15ns的次数为3(5)次,那么PLL就会给出数字锁定指示数字锁定指示的工作频率范围:通常为5kHz~50MHz。

在更低的PFD频率上,漏电流会触发锁定指示电路;在更高的频率上,15ns的时间裕度不再适合。

在数字锁定指示的工作频段范围之外,推荐使用模拟锁定指示。

模拟锁定指示对电荷泵输入端的Up脉冲和Down脉冲进行异或处理后得出的脉冲串。

所以当锁定时,锁定指示电路的输出为带窄负脉冲串的高电平信号。

图为一个典型的模拟锁定指示输出(MUXOUT输出端单独加上拉电阻的情况)。

图表7模拟锁定指示的输出级为N沟道开漏结构,需要外接上拉电阻,通常为10KOhm~160kohm。

我们可以通过一个积分电路(低通滤波器)得到一个平坦的高电平输出,如图所是的蓝色框电路。

误锁定的一个条件:参考信号REFIN信号丢失。

当REFIN信号与PLL频合器断开连接时,PLL显然会失锁;然而,ADF41xx 系列的PLL,其数字锁定指示用REFIN时钟来检查是否锁定,如果PLL先前已经锁定,REFIN时钟突然丢失,PLL会继续显示锁定状态。