allegro SI 信号完整性仿真介绍

在Allegro 中进行SI 仿真

第一章在Allegro 中准备好进行SI 仿真的PCB 板图1)在Cadence 中进行SI 分析可以通过几种方式得到结果:* Allegro 的PCB 画板界面,通过处理可以直接得到结果,或者直接以*.brd 存盘。

* 使用Specctre Quest 打开*.brd,进行必要设置,通过处理直接得到结果。

这实际与上述方式类似,只不过是两个独立的模块,真正的仿真软件是下面的SigXplore 程序。

* 直接打开SigXplore 建立拓扑进行仿真。

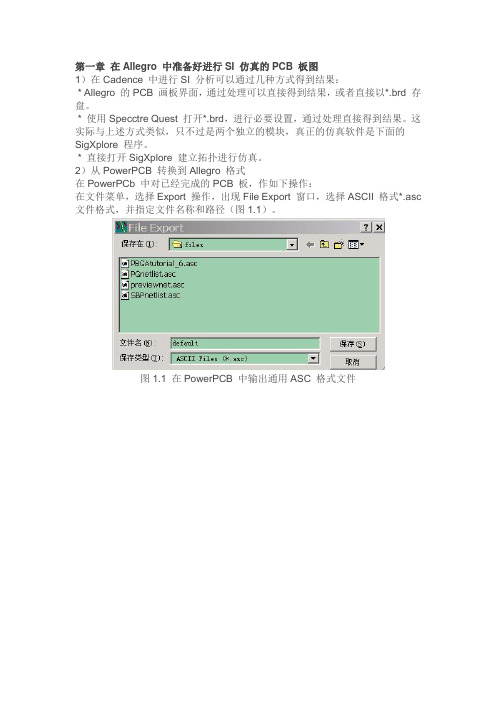

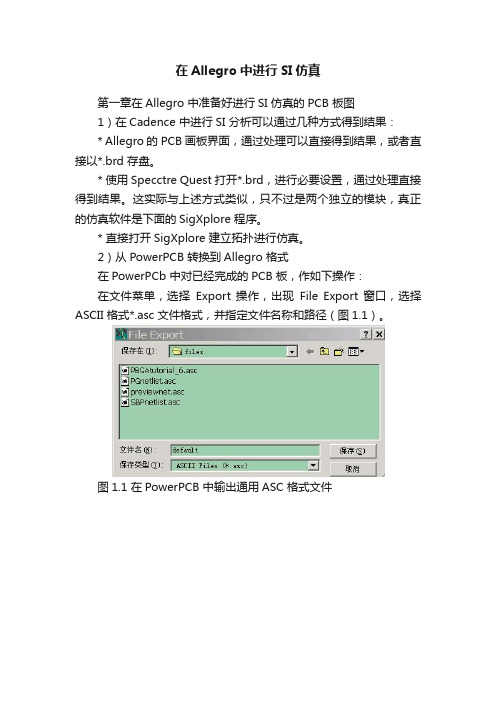

2)从PowerPCB 转换到Allegro 格式在PowerPCb 中对已经完成的PCB 板,作如下操作:在文件菜单,选择Export 操作,出现File Export 窗口,选择ASCII 格式*.asc 文件格式,并指定文件名称和路径(图1.1)。

图1.1 在PowerPCB 中输出通用ASC 格式文件图1.2 PowerPCB 导出格式设置窗口点击图1.1 的保存按钮后出现图1.2 ASCII 输出定制窗口,在该窗口中,点击“Select All”项、在Expand Attributes 中选中Parts 和Nets 两项,尤其注意在Format 窗口只能选择PowerPCB V3.0 以下版本格式,否则Allegro 不能正确导入。

3)在Allegro 中导入*.ascPCB 板图在文件菜单,选择Import 操作,出现一个下拉菜单,在下拉菜单中选择PADS 项,出现PADS IN 设置窗口(图1.3),在该窗口中需要设置3 个必要参数:图1.3 转换阿三次文件参数设置窗口i. 在的一栏那填入源asc 文件的目录ii. 在第二栏指定转换必须的pads_in.ini 文件所在目录(也可将此文件拷入工作目录中,此例)iii. 指定转换后的文件存放目录然后运行“Run”,将在指定的目录中生成转换成功的.brd 文件。

注:pads_in.ini 所在目录路:.Psd_14.2ToolsPCBbin 中。

利用Cadence Allegro PCB SI进行SI仿真分析

利用Cadence Allegro PCB SI进行SI仿真分析摘要本文主要针对高速电路中的信号完整性分析,利用Cadence Allegro PCB SI 工具进行信号完整性(SI)分析。

说明:本手册中的实例均采用Cadence SPB 16_2操作实现。

目录一、高速数字电路的基本知识 (3)1.1高速电路的定义 (3)1.2高速PCB的设计方法 (3)1.3微带线与带状线 (4)1.4常见的高速数字电路 (5)1.4.1 ECL(Emitter Coupled Logic)射级耦合电路 (5)1.4.2 CML(Current Mode Logic)电流模式电路 (6)1.4.3 GTL(Gunning Transceiver Logic)电路 (6)1.4.4 TTL(Transistor Transistor Logic)电路 (7)1.4.5 BTL(BackPlane Transceiver Logic)电路 (7)1.5信号完整性 (8)1.4.1 反射(Reflection) (8)1.4.2 串扰(Crosstalk) (8)1.4.3 过冲(Overshoot)与下冲(Undershoot) (9)1.4.4 振铃(Ringring) (9)1.4.5 信号延迟(Delay) (9)二、信号完整性分析和仿真流程 (11)2.1 SpecctraQuest interconnect Designer的性能简介 (11)2.2 SpectraQuest(PCB SI)仿真流程 (11)三、仿真前的准备 (13)3.1 IBIS模型 (13)3.1.1 IBIS模型介绍 (13)3.1.2 IBIS模型的获取方法 (14)3.1.2 验证IBIS模型 (14)3.2 预布局 (20)3.3 电路板设置要求(Setup Advisor) (23)3.3.1 叠层设置(Edit Cross-section) (24)3.3.2 设置DC电压值(Identify DC Nets) (25)3.3.3 器件设置(Device Setup) (26)3.3.4 SI模型分配(SI Model Assignment) (27)四、约束驱动布局 (35)4.1 预布局提取和仿真 (35)4.1.2 预布局拓扑提取分析 (37)4.1.3 执行反射仿真 (40)4.1.4 反射仿真测量 (42)4.2 设置和添加约束 (43)4.2.1 运行参数扫描 (43)4.2.2 为拓扑添加约束 (47)4.2.3 分析拓扑约束 (52)五、布线后仿真 (53)5.1 后仿真 (53)5.2反射仿真 (53)5.2.1 设置参数 (53)5.2.2指定要仿真的网络 (53)5.2.3 执行仿真 (55)5.3综合仿真 (57)5.4 串扰仿真 (57)5.5 Simultaneous Switching Noisie仿真 (57)5.6 多析仿真 (57)六、参考文献 (57)说明:本手册中的实例均采用Cadence SPB 16_2操作实现。

Cadence Allegro Sigrity介绍

Cadence Allegro Sigrity介绍高科技企业开发复杂的芯片,封装和单板努力克服由于飞速增长的IC速度和数据传输速率联合引起的供电电压的降低,更高密度,越来越小型化的结构引起的电源完整性和信号完整性问题。

同时,更高的I/O数目,多堆叠的芯片和封装以及更高的电气性能约束都使得IC 封装物理设计更加复杂。

Cadence具有突破型进展的解决方案,基于Sigrity专利技术,解决这些设计挑战。

该解决方案致力于完整的电源供电系统分析跨越了芯片,封装和单板;系统级的信号完整性(SI)分析,包含高速信号传输同步反转噪声和单个和多个芯片封装,最先进的3D封装以及系统级封装(SiPs)的高级物理设计。

Power Integrity电源完整性Cadence 电源完整性(PI)解决方案,基于Sigrity技术,提供signoff 级别精度的PCB和IC封装的AC和DC电源分析。

每个工具都能与Cadence Allegro® PCB 和IC封装物理设计解决方案无缝集成。

Sigrity PowerSIIC封装和PCB设计快速准确的全波电磁场分析作为专业的频域分析工具,为当前高速电路设计中面临的各种信号完整性(SI)、电源完整性(PI)和电磁兼容(EMI/EMC)分析提供快速准确的全波电磁场分析,并提供宽带S参数提取以及频域仿真。

Sigrity™ PowerSI®可以为IC封装和PCB设计提供快速准确的全波电磁场分析,从而解决高速电路设计中日益突出的各种PI和SI问题:如同步切换噪声(SSN)问题,电磁耦合问题,信号回流路径不连续问题,电源谐振问题,去耦电容放置不当问题以及电压超标等问题,从而帮助用户发现或改善潜在的设计风险。

PowerSI可以方便的提取封装和PCB的各种网络参数(S/Y/Z),并对复杂的空间电磁谐振问题产生可视化的输出。

PowerSI能与当前主流的物理设计数据库如PCB, IC封装和系统级封装(SiP)进行无缝连接。

基于Allegro PCB SI 的DSP最小系统板信号完整性仿真分析

I T 技术科技创新导报 Science and Technology Innovation Herald70随着现代科技的飞速发展,许多系统的工作频率很高,达到数百M H z甚至G H z,并且信号沿越来越陡,已经达到n s级别甚至更小。

如此高速的信号的切换对于P C B 设计者而言需要考虑到低频电路所不需要考虑的信号完整性问题,如延时,串扰,反射,地弹等。

本文拟借助传输线理论对D S P 最小系统板进行信号完整性仿真。

1 DSP最小系统介绍D S P 最小系统主要由D S P芯片,电源电路,复位电路,时钟电路,JATG 接口电路和外部存储器等部分构成,其结构框图如下:本文仿真分析的最小系统板采用型为T M S 320C 6713的D S P 芯片,外接存储器部分由F L A S H 芯片和S D R A M 存储器芯片共同组成。

其中D S P 芯片的最高主频可达300M H z,并且与外接存储器芯片进行高速数据传输。

所以必须对最小系统板进行信号完整性分析。

2 基于传输线理论的高速PCB布线分析P C B上的印制导线如果作为传输线设计的不够合理,根据不同的传输线模型在电路上可能会出现信号反射,延时,串扰,地弹等传输线效应。

根据传输线理论,通过综合分析各种传输线效应产生原理,可得出相应的布线方法规避传输线效应。

2.1 减少反射的布线方法当信号传输路径上特征阻抗不连续时,就会有信号反射发生。

反射会造成诸如过冲,下冲,振铃等信号失真的现象,从而引起信号完整性的问题。

由于反射产生的根本原因是传输路径上阻抗不连续,我们一般采取端接阻抗的方法达减少信号的反射。

其中常见的端接阻抗方法有串联端接和并联端接。

串联端接是在靠近输出端位置串接一个电阻,端接的电阻和输出端的阻抗总和应该与传输线的特征阻抗Z 0相等。

该方案消除了驱动端的二次反射,且不受接收端负载变化的影响。

但是由于端接电阻的分压,线路上传输的电压仅仅为驱动电压的一半,不能驱动分布式负载。

Allegro_SI仿真流程简介

上海市共进通信技术有限公司

仿真步骤

开始 指定仿真信号线 准备好要仿真的PCB图 生成仿真报告

转换库模式并加载 给器件加载模型 定义电源和地线

提取拓扑结构

更改电路条件重复仿真

根据阻抗要求调整叠层 结果分析 仿真参数设置 结束

上海市共进通信技术有限公司

仿真Байду номын сангаас数设置

• Allegro菜单中Analyze\SI/EMI Smi\ Preference

上海市共进通信技术有限公司

指定仿真信号线

• Allegro菜单中Analyze\SI/EMI Smi\ Probe

上海市共进通信技术有限公司

仿真结果

• Driver端增加电阻

加电阻

上海市共进通信技术有限公司

Crosstalk

• Crosstalk Waveform

上海市共进通信技术有限公司

仿真结果参数

SIM ID(模拟的次数) Diver(驱动端) Receiver(接收端) Cycle(仿真的周期) FTS MODE(仿真模式) Monotonic(单调性) Noise Margin(噪声裕量) Overshoothigh(上过冲) Overshootlow(下过冲) PropDelay(传输延迟,驱动端到接收端)

IBIS库转换DML

• Allegro菜单中Analyze\SI/EMI Smi\ Library

上海市共进通信技术有限公司

加载DML库

• Allegro菜单中Analyze\SI/EMI Smi\ Library

上海市共进通信技术有限公司

生成仿真报告

• Reflection

Cadence SI信号完整性仿真技术

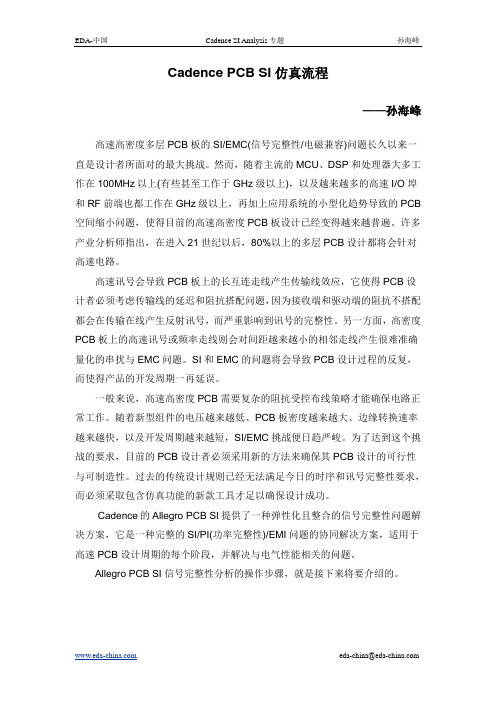

Cadence PCB SI仿真流程——孙海峰高速高密度多层PCB板的SI/EMC(信号完整性/电磁兼容)问题长久以来一直是设计者所面对的最大挑战。

然而,随着主流的MCU、DSP和处理器大多工作在100MHz以上(有些甚至工作于GHz级以上),以及越来越多的高速I/O埠和RF前端也都工作在GHz级以上,再加上应用系统的小型化趋势导致的PCB 空间缩小问题,使得目前的高速高密度PCB板设计已经变得越来越普遍。

许多产业分析师指出,在进入21世纪以后,80%以上的多层PCB设计都将会针对高速电路。

高速讯号会导致PCB板上的长互连走线产生传输线效应,它使得PCB设计者必须考虑传输线的延迟和阻抗搭配问题,因为接收端和驱动端的阻抗不搭配都会在传输在线产生反射讯号,而严重影响到讯号的完整性。

另一方面,高密度PCB板上的高速讯号或频率走线则会对间距越来越小的相邻走线产生很难准确量化的串扰与EMC问题。

SI和EMC的问题将会导致PCB设计过程的反复,而使得产品的开发周期一再延误。

一般来说,高速高密度PCB需要复杂的阻抗受控布线策略才能确保电路正常工作。

随着新型组件的电压越来越低、PCB板密度越来越大、边缘转换速率越来越快,以及开发周期越来越短,SI/EMC挑战便日趋严峻。

为了达到这个挑战的要求,目前的PCB设计者必须采用新的方法来确保其PCB设计的可行性与可制造性。

过去的传统设计规则已经无法满足今日的时序和讯号完整性要求,而必须采取包含仿真功能的新款工具才足以确保设计成功。

Cadence的Allegro PCB SI提供了一种弹性化且整合的信号完整性问题解决方案,它是一种完整的SI/PI(功率完整性)/EMI问题的协同解决方案,适用于高速PCB设计周期的每个阶段,并解决与电气性能相关的问题。

Allegro PCB SI信号完整性分析的操作步骤,就是接下来将要介绍的。

一、Allegro PCB SI分析前准备:1、准备需要分析的PCB,如下图;2、SI分析前的相关设置,执行T ools/Setup Advisor,进入Database Setup Advisor 对话框,进行SI分析前的设置;(1)设置PCB叠层的材料、阻抗等,点击Edit Cross section,进入叠层阻抗等设置界面。

在Allegro中进行SI仿真

在Allegro中进行SI仿真第一章在Allegro 中准备好进行SI 仿真的PCB 板图1)在Cadence 中进行SI 分析可以通过几种方式得到结果:* Allegro 的PCB 画板界面,通过处理可以直接得到结果,或者直接以*.brd 存盘。

* 使用Specctre Quest 打开*.brd,进行必要设置,通过处理直接得到结果。

这实际与上述方式类似,只不过是两个独立的模块,真正的仿真软件是下面的SigXplore 程序。

* 直接打开SigXplore 建立拓扑进行仿真。

2)从PowerPCB 转换到Allegro 格式在PowerPCb 中对已经完成的PCB 板,作如下操作:在文件菜单,选择Export 操作,出现File Export 窗口,选择ASCII 格式*.asc 文件格式,并指定文件名称和路径(图1.1)。

图1.1 在PowerPCB 中输出通用ASC 格式文件图1.2 PowerPCB 导出格式设置窗口点击图1.1 的保存按钮后出现图1.2 ASCII 输出定制窗口,在该窗口中,点击“Select All”项、在Expand Attributes 中选中Parts 和Nets 两项,尤其注意在Format 窗口只能选择PowerPCB V3.0 以下版本格式,否则Allegro 不能正确导入。

3)在Allegro 中导入*.ascPCB 板图在文件菜单,选择Import 操作,出现一个下拉菜单,在下拉菜单中选择PADS 项,出现PADS IN 设置窗口(图1.3),在该窗口中需要设置3 个必要参数:图1.3 转换阿三次文件参数设置窗口i. 在的一栏那填入源asc 文件的目录ii. 在第二栏指定转换必须的pads_in.ini 文件所在目录(也可将此文件拷入工作目录中,此例)iii. 指定转换后的文件存放目录然后运行“Run”,将在指定的目录中生成转换成功的.brd 文件。

注:pads_in.ini 所在目录路:.Psd_14.2ToolsPCBbin 中。

Allegro_PCB_SI 一步一步学会前仿真

Allegro PCB SI:一步一步学会前仿真Learn Allegro PCB SI Pre-simulation Step by StepDoc Scope : Cadence 16.5Doc Number : SFTEC12007Author : Daniel ZhongCreate Date : 2012-04-10Rev : 1.00目录1Cadence Allegro PCB SI简介 (7)1.1高速PCB设计流程 (7)2Allegro PCB SI的前仿真 (8)2.1准备仿真模型和其他需求 (8)2.1.1获取所使用元器件的仿真模型 (9)2.1.2获取所使用连接器的仿真模型 (10)2.1.3获取所使用元器件和连接器的器件手册和用户指南等相关资料 (10)2.1.4获取所需的规范文档 (10)2.1.5了解相关电路和接口工作原理 (10)2.1.6提取与信号完整性相关的要求 (10)2.1.7预先创建拓扑样本 (11)2.1.8预先创建相对于不同阈值电压的眼图模板 (11)2.1.9预先创建自定义测量 (12)2.2仿真前的规划 (12)2.3关键器件预布局 (13)2.4模型加载和仿真配置 (13)2.4.1模型的转化 (14)2.4.2使用SI Design Setup配置 (15)2.4.3选择需要配置的信号线 (16)2.4.4设置仿真库 (18)2.4.5设置电源和地网络 (20)2.4.6设置叠层 (24)2.4.7设置元器件类别 (27)2.4.8为元器件分配和创建模型 (28)2.4.9设置差分对 (37)2.4.10设置仿真参数 (42)2.4.11SI Design Audit相关 (50)2.4.12提取拓扑 (52)2.4.13在SigXP中设置仿真库和仿真参数 (54)2.4.14在SigXP中绘制拓扑 (58)2.5方案空间分析 (68)2.5.1输出驱动力扫描分析 (71)2.5.2Stub长度扫描分析 (73)2.5.3线宽线间距扫描分析 (74)2.6方案到约束规则的转化 (76)2.6.1传输线延迟规则的设置 (77)2.6.2拓扑结构等传输线特性规则的设置 (80)2.6.3传输线耦合规则的设置 (80)2.6.4拓扑规则在约束管理器中的应用 (81)3Allegro PCB SI的后仿真 (84)表格表格 1:Routed Interconnect Models参数 (45)表格 2:Simulation栏眉仿真参数 (47)表格 3:IO Cell Stimulus Edit窗口中的选项 (68)图图 1:传统的PCB设计流程图 (7)图 2:Allegro PCB SI高速PCB设计流程图 (8)图 3:眼图模式下的眼图模板 (11)图 4:地址、命令和控制信号传输线拓扑 (12)图 5:RDIMM的布局示意图 (13)图 6:Model Integrity界面 (14)图 7:使用Model Integrity将IBIS文件转换至DML格式 (15)图 8:Cadence Product Choices产品选择器窗口 (16)图 9:Allegro PCB SI GXL界面 (17)图 10:Setup Category Selection窗口 (17)图 11:Setup Xnet Selection窗口 (17)图 12:Allegro PCB SI GXL关于网络设置的提醒框 (18)图 13:Setup Library Search Directories窗口 (19)图 14:Setup Library File Extensions窗口 (19)图 15:Setup Working Libraries窗口 (19)图 16:Setup Power and Ground Nets窗口 (20)图 17:Allegro PCB SI GXL电压赋值窗口 (21)图 18:选择“Edit Voltage On Any Net In Design” (21)图 19:Identify DC Nets窗口。

五款信号完整性仿真工具介绍

现在的高速电路设计已经达到GHz的水平,高速PCB设计要求从三维设计理论出发对过孔、封装和布线进行综合设计来解决信号完整性问题。

高速PCB设计要求中国工程师必须具备电磁场的理论基础,必须懂得利用麦克斯韦尔方程来分析PCB设计过程中遇到的电磁场问题。

目前,Ansoft公司的仿真工具能够从三维场求解的角度出发,对PCB设计的信号完整性问题进行动态仿真。

(一)Ansoft公司的仿真工具现在的高速电路设计已经达到GHz的水平,高速PCB设计要求从三维设计理论出发对过孔、封装和布线进行综合设计来解决信号完整性问题。

高速PCB设计要求中国工程师必须具备电磁场的理论基础,必须懂得利用麦克斯韦尔方程来分析PCB设计过程中遇到的电磁场问题。

目前,Ansoft公司的仿真工具能够从三维场求解的角度出发,对PCB设计的信号完整性问题进行动态仿真。

Ansoft的信号完整性工具采用一个仿真可解决全部设计问题:SIwave是一种创新的工具,它尤其适于解决现在高速PCB和复杂IC封装中普遍存在的电源输送和信号完整性问题。

该工具采用基于混合、全波及有限元技术的新颖方法,它允许工程师们特性化同步开关噪声、电源散射和地散射、谐振、反射以及引线条和电源/地平面之间的耦合。

该工具采用一个仿真方案解决整个设计问题,缩短了设计时间。

它可分析复杂的线路设计,该设计由多重、任意形状的电源和接地层,以及任何数量的过孔和信号引线条构成。

仿真结果采用先进的3D图形方式显示,它还可产生等效电路模型,使商业用户能够长期采用全波技术,而不必一定使用专有仿真器。

(二)SPECCTRAQuestCadence的工具采用Sun的电源层分析模块:Cadence Design Systems的SpecctraQuest PCB信号完整性套件中的电源完整性模块据称能让工程师在高速PCB设计中更好地控制电源层分析和共模EMI。

该产品是由一份与Sun Microsystems公司签署的开发协议而来的,Sun最初研制该项技术是为了解决母板上的电源问题。

Allegro16.5 中进行SI 仿真

在仿真之前,需要相应的IBIS模型文件,并把它转换为Cadence需要的DML文件,现在已经下载了一个IBIS 文件,它是Altera公司的cyclone3的IBIS文件:cyclone3.ibs。

为了把它转化,我们首先需要打开Model Integrity打开Model Integrity后,选择File Open 打开需要转化的IBIS文件打开后如下图:点击cyclon3,然后点右键,选择IBIS to DML,来实现IBIS到DML的转化在转化时报错:查看LOG File有如下说明:这个时候实际上是出了很多报错,报错的说明如下:WARNING: CYCLONE3_sstl18c1_cio_d10s Ramp value for maximum of Fall is significantly different with that computed from the corresponding TV curve - fixedERROR: TVCurve start time of CYCLONE3_ttl18_rdio_d8s RisingWaveform rise_1 at line 483255 is not same as CYCLONE3_ttl18_rdio_d8s FallingWaveform fall_1 at line 482667ERROR: TVCurve start time of CYCLONE3_ttl18_rdio_d8s RisingWaveform rise_2 at line 483368 is not same as CYCLONE3_ttl18_rdio_d8s FallingWaveform fall_2 at line 482778WARNING: CYCLONE3_sstl2c1_cio_d12s Ramp value for typical of Fall is significantly different with that computed from the corresponding TV curve - fixedWARNING: CYCLONE3_sstl2c1_rio_d12s Ramp value for typical of Fall is significantly different with that computed from the corresponding TV curve - fixedWARNING: CYCLONE3_ttl18_rdio_d10s Ramp value for maximum of Rise is significantly different with that computed from the corresponding TV curve - fixedTranslation failed due to DMLCHECK errors.Output saved as D:\yanshi\2\cyclone3.dml.txt.Run ibis2signoise -d, a DML will be generated.Examine it with line numbers from the log message.对于这个错误,说明是在DOS环境下运行ibis2signoise -d,可以了,那么就在DOS下运行运行结束后,在运行目录下可以看到已经生成了文件:cyclone3.ibs.dml,修改它为cyclone3.dmlDML文件已经生成,关闭Model Integrity下一步就是要进行仿真了,首先打开PCB SI然后在弹出的菜单中选择红线框住的部分进入PCB SI GXL后打开要仿真的BRD文件。

SI仿真深入讲解

Allegro SI 仿真讲解

Myron He 2010.03.02 Myron_He@

Index

► 仿真前准备 ► 电路板设置 ► 拓扑提取与仿真

► 前时序仿真

► 后时序仿真

► 差分对设计与仿真

Allegro PCB SI仿真

仿真前准备

► 仿真前准备文件

Allegro PCB文件.brd 仿真信号器件IBIS模型 PCB叠层结构详细参数

VCC A VCC Pow低电平的上下拉U/I曲线

R_pkg L_pkg 2 1 2 O utput

1

2

3

1

3

2

B

C_pkg

2

C_comp

1

2

G ND_Clamp

Allegro PCB SI仿真

1

1

B:包含了上升沿和下降沿的摆率

仿真前准备

2

C_comp

2

C_pkg

1

IBIS模型数据的准确性直接影响仿真的效果,同时模型数据的获得比较困难, IC供应商为目前IBIS模型数据的最有效来源. IC供应商在这方面的投资会比较大,RD需要不断Push,推动IC厂商来提供模 型数据.

Allegro PCB SI仿真

1

仿真前准备

► IBIS模型输出结构

► 1.添加工作库

Allegro PCB SI仿真

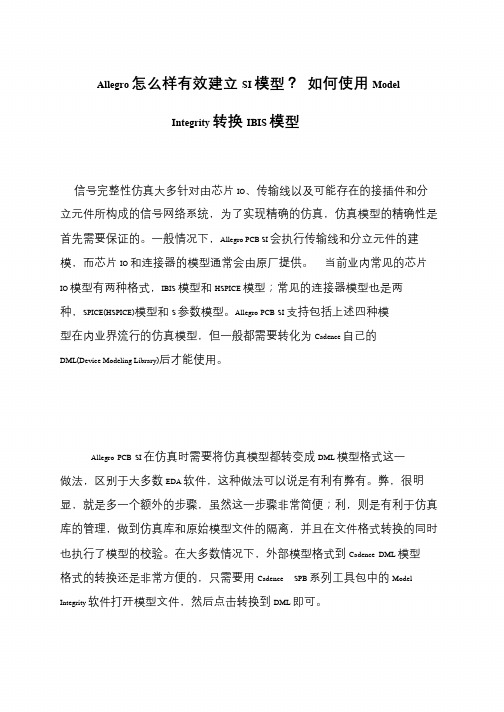

Allegro怎么样有效建立SI模型? 如何使用Model Integrity转换IBIS模型

Allegro 怎么样有效建立SI 模型?如何使用Model

Integrity 转换IBIS 模型

信号完整性仿真大多针对由芯片IO、传输线以及可能存在的接插件和分

立元件所构成的信号网络系统,为了实现精确的仿真,仿真模型的精确性是

首先需要保证的。

一般情况下,Allegro PCB SI 会执行传输线和分立元件的建模,而芯片IO 和连接器的模型通常会由原厂提供。

当前业内常见的芯片

IO 模型有两种格式,IBIS 模型和HSPICE 模型;常见的连接器模型也是两种,SPICE(HSPICE)模型和S 参数模型。

Allegro PCB SI 支持包括上述四种模型在内业界流行的仿真模型,但一般都需要转化为Cadence 自己的

DML(Device Modeling Library)后才能使用。

Allegro PCB SI 在仿真时需要将仿真模型都转变成DML 模型格式这一做法,区别于大多数EDA 软件,这种做法可以说是有利有弊有。

弊,很明

显,就是多一个额外的步骤,虽然这一步骤非常简便;利,则是有利于仿真

库的管理,做到仿真库和原始模型文件的隔离,并且在文件格式转换的同时

也执行了模型的校验。

在大多数情况下,外部模型格式到Cadence DML 模型格式的转换还是非常方便的,只需要用Cadence SPB 系列工具包中的Model Integrity 软件打开模型文件,然后点击转换到DML 即可。

基于Cadence_Allegro的高速PCB设计信号完整性分析与仿真

,采用端接电阻后数据波形质量明显提升,端接能有效解决阻抗不匹配所引起的反射问题。

3 结语 Cadence_Allegro软件中的Specctraquest和Sigxp组件工具,为高速PCB的设计与仿真提供了强有力的支撑,包括仿真模型验证、拓扑分析、布线前与布线后仿真、约束条件的设置、PCB布局布线等硬件环节,通过仿真结果可促使设计者较好地把握信号完整性问题,优化设计,提高高速PCB设计的一次成功率,较好地应对高速设计所面临的挑战。

,源端端接主要采用串行端接,远(负载)端主要采用并行端接、戴维南端接、RC端接。由于并行端接的电流消耗大,戴维南端接的直流功耗大,RC端接的开关速度低等缺点,最为广泛使用的是源端串联电阻端接的方式,实际设计中需根据情况选择使用。

1.3 串扰 串扰发生在两个相邻的网络之间,若一个网络发生动态变化,将会通过场的作用将噪声耦合到与其相邻的静态网络上,从而影响其信号质量。信号传播时的信号路径与返回路径存在边缘场,会产生容性耦合与感性耦合,称为互容和互感。当一个网络发生动态变化时,通过边缘场的作用,容性、感性耦合电流对相邻网络造成影响。开关噪声、地弹都是由串扰引起的。串扰分为近端串扰(NEXT)与远端串扰(FEXT),近端接近源端而远端远离源端。NEXT与FEXT幅值分别如式(2),式(3): 式中:Vb静态线后向噪声电压;Va1为动态线上信号电压;kb为后向串扰系数;Vf为静态线远端电压;Va2为信号线电压;k1为远端耦合系数;为两条线耦合区的长度;RT为上升时间;CmL,CL,LmL,LL分别为单位长度互容、电容、互感、电感。由式(2),式(3)可知,减小NEXT的主要方法是减小CmL,LmL,通过加大网络间的距离可以做到这一点。减小FEXT的主要方法是增加RT,减小L,加大网络间的距离。减小串扰会增加系统成本,需要折中才能在保证信号完整性的基础上实现成本最节省化。1.4 定时 集成电路只能按规定的时序接收数据,过长的信号延迟可能导致时序违背和功能混乱。当系统时钟很高时,信号在器件间的传输时间以及同步准备时间都缩短了,驱动过载、走线过长都会引起延时。高速电路要求在很短的时间内满足各种门延时,包括建立时间、保持时间、线延时等,而且在高速PCB中,传输线上的分布电容、分布电感都会对信号的数字切换产生延时,影响数字电路的建立和保持时间,延时过长可能会导致集成电路无法正确判断数据。常见的时序系统分为普通时序系统和源同步时序系统2类,本文主要介绍普通时序系统的时序问题。所谓普通时序系统(公共时钟时序系统)就是指驱动端和接收端的同步时钟信号都是由一个系统时钟发生器提供的,其主要限制条件如式(4),式(5): 式中:Ts,t,Th,t分别为建立时间与保持时间;Ts,m与Th.m分别为建立时间裕量与保持时间裕量;Tc为时钟周期;Tp,s为2根CLOCK走线之间的时钟偏移;Tc.s为时钟驱动器(PLL)的2个时钟输出之间的偏移;Tj为前后两个时钟周期之间的误差;Tc,d为驱动器内部的延时;Tf,d为驱动器到接收端之间的数据线飞行时间。对于任何普通时钟控制系统,如果能保证正常工作,就必须使建立时间裕量和保持时间裕量都至少大于零,即Ts,m>T0,Th,m>0。2 基于Cadence_Allegro的仿真结果及分析2.1 高速14位ADC/DAC应用系统简介 ,该应用系统可做ADC/DAC芯片验证,基于Cyclone2系列的FPGA,可实现DDC,DDS功能。实际应用中待测ADC选用Linear公司14位105 MS/s的芯片LTC2284,DAC芯片采用AD公司14位、210 MSPS的芯片AD9783,系统PCB设计。

Allegro PCB SI PCB信号完整性分析系统

Allegro PCB SI -XL为高速数字PCB板和系统的电气设计工程师提供的一个集成的设计和分析环境,它可以探索和解决在设计各个环节中存在的与电气性能相关的问题。

通过对时序、信噪、串扰、电源地构造和电磁兼容等多方面因素进行探索和折中,设计工程师可以在将设计递交到生产之前充分优化设计的电气性能和可靠性。

它既可以对单个板进行,又可以对多块PCB板构成的系统进行。

它可以直接读、写Cadence的Allegro PCB格式的Brd文件,与Allegro PCB 设计流程完全集成。

设计工程师可以在设计的各个阶段进行高速性能的分析,如在PCB板部分布局或完全布局的情况下,在PCB 板部分布线或完全布线的情况下,甚至在没有网表或PCB数据的情况下均可进行分析。

Allegro PCB SI -XL 不需数据转换,直接对PCB数据操作的特点,以及它能够产生约束条件来驱动布局,布线功能,可以确保高速PCB设计中电气性能的约束能快速、精确地实现。

Allegro PCB SI 共包括五个主要的组成部分:. Floorplanner/editor——布局规划编辑器. SigXplorer ——SigXplorer拓扑结构研发环境. SigNoise——SigNoise信噪分析子系统. SPECCTRA Autorouter——SPECCTRA 专家级自动布线器. EMControl ——电磁兼容设计规则检查工具以下详述这五个组成部分的功能:a) Floorplanner/editor 布局规划编辑器Allegro PCB SI Floorplanner/editor 布局规划编辑器以图形化方式显示PCB板数据,方便用户阅读、分析和修改PCB数据。

设计者可以快速、方便地评判不同的布局策略对设计性能的影响。

设计工程师可以按计划好的电气约束去试布线,以便在将这些约束规则传递给PCB布局布线工程师之前,能保证这些高速PCB 设计规则的执行状态。

Allegro SI 高速信号完整性仿真

信号完整性是指信号在信号线上的质量。

信号具有良好的信号完整性是指当在需要的时候,具有所必需达到的电压电平数值。

差的信号完整性不是由某一因素导致的,而是由板级设计中多种因素共同引起的。

特别是在高速电路中,所使用的芯片的切换速度过快、端接元件布设不合理、电路的互联不合理等都会引起信号的完整性问题。

具体主要包括串扰、反射、过冲与下冲、振荡、信号延迟等。

信号完整性问题由多种因素引起,归结起来有反射、串扰、过冲和下冲、振铃、信号延迟等,其中反射和串扰是引发信号完整性问题的两大主要因素。

反射和我们所熟悉的光经过不连续的介质时都会有部分能量反射回来一样,就是信号在传输线上的回波现象。

此时信号功率没有全部传输到负载处,有一部分被反射回来了。

在高速的PCB中导线必须等效为传输线,按照传输线理论,如果源端与负载端具有相同的阻抗,反射就不会发生了。

如果二者阻抗不匹配就会引起反射,负载会将一部分电压反射回源端。

根据负载阻抗和源阻抗的关系大小不同,反射电压可能为正,也可能为负。

如果反射信号很强,叠加在原信号上,很可能改变逻辑状态,导致接收数据错误。

如果在时钟信号上可能引起时钟沿不单调,进而引起误触发。

一般布线的几何形状、不正确的线端接、经过连接器的传输及电源平面的不连续等因素均会导致此类反射。

另外常有一个输出多个接收,这时不同的布线策略产生的反射对每个接收端的影响也不相同,所以布线策略也是影响反射的一个不可忽视的因素。

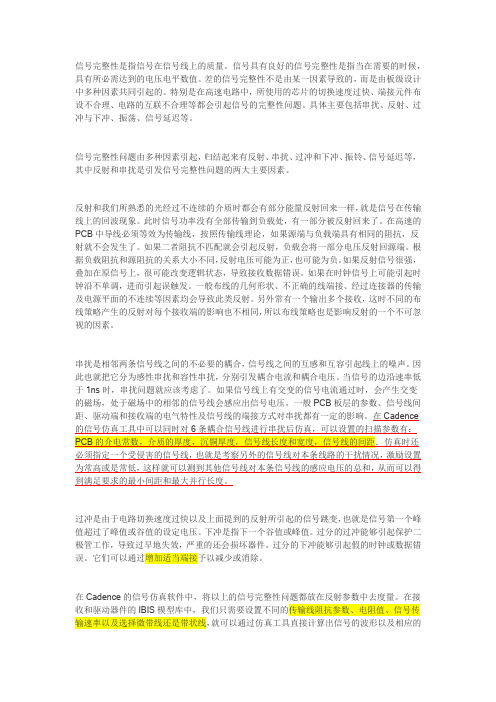

串扰是相邻两条信号线之间的不必要的耦合,信号线之间的互感和互容引起线上的噪声。

因此也就把它分为感性串扰和容性串扰,分别引发耦合电流和耦合电压。

当信号的边沿速率低于1ns时,串扰问题就应该考虑了。

如果信号线上有交变的信号电流通过时,会产生交变的磁场,处于磁场中的相邻的信号线会感应出信号电压。

一般PCB板层的参数、信号线间距、驱动端和接收端的电气特性及信号线的端接方式对串扰都有一定的影响。

在Cadence 的信号仿真工具中可以同时对6条耦合信号线进行串扰后仿真,可以设置的扫描参数有:PCB的介电常数,介质的厚度,沉铜厚度,信号线长度和宽度,信号线的间距.仿真时还必须指定一个受侵害的信号线,也就是考察另外的信号线对本条线路的干扰情况,激励设置为常高或是常低,这样就可以测到其他信号线对本条信号线的感应电压的总和,从而可以得到满足要求的最小间距和最大并行长度。

AllegroSI信号完整性仿真激励源设置

DDR信号完整性仿真频率的确定——孙海峰仿真过程中,我们必须了解如何来确定各类总线的仿真激励源,即Memory Contoller-DIMM之间的各类总线信号工作中的实际频率及其时序特性等,或者认为是DDR-DIMM工作中的外部输入激励信号——因为仿真过程中,必须设置DIMM的模拟激励源,即CPU驱动端的信号,才能仿真DIMM接收端信号SI/窜扰等状况。

实际工作中,DDR各类信号工作频率特征如下图所示:在此基础上,我们如何确定DDR最佳的仿真激励源,如何确定最佳SI仿真频率呢?接下来,将做出详细的阐述。

1、确定DDR核心频率DDR核心频率,即DDR上DRAM颗粒的工作频率,它与DDR数据传输位数有关,由于:DDR等效数据传输频率=DRAM核心频率×DDR读取位数,那么我们即可了解DRAM核心频率=数据等效传输频率/读取位数。

对于不同类型的DDR,数据读取位数为:DDR1(DDR SDRAM):2 bit pre-fetch,同时读取(预取)2n的数据——数据读取位数2;DDR2:4 bit pre-fetch,同时读取(预取)4n的数据——数据读取位数4;DDR3:8 bit pre-fetch,同时读取(预取)8n的数据——数据读取位数8;结论:我们可以从数据传输频率,结合DDR类型,计算出核心频率。

2、确定DDR Controller(CPU)-DDR差分时钟仿真激励源——CK+/CK-差分时钟总线根据DDR时序图,我们可以知道,无论DDR1,DDR2,还是DDR3,DDRx 数据的最大实际传输频率均等于时钟频率,则DDRx最大数据等效工作频率(常说的DDRx能跑多少频率为等效值)为实际频率的2倍(周期为时钟周期1/2),如下图所示:结论:DDRx时钟总线仿真频率等于等效数据传输频率的1/2。

3、确定DDR Controller(CPU)-DDR地址/命令信号线仿真激励源——A*地址总线/BA*Bank地址选择信号/CAS(Column)列命令信号/RAS(Row)行命令信号/WE(Write)写命令使能端对于地址/命令信号仿真激励源的确定,即实际工作频率及其时序特性的确定,我们首先必须认识1-T/2-T这两种DDR常用时序工作模式。

allegro_PCB_SI仿真

allegro_PCB_SI仿真IntroductionAllegro PCB SI仿真可以帮助人们在设计PCB 电路板时进行信号完整性仿真,以验证电路设计的有效性和稳定性。

这个工具是Cadence 公司的Allegro 系列产品中的一个,它可以让我们对PCB 电路板进行模拟分析,发现布线中的信号完整性问题,并接下来进行优化,从而得到更好的结果。

下面我们来详细讲解一下Allegro PCB SI仿真的使用。

功能与特点Allegro PCB SI仿真工具主要有以下功能和特点:1. 电路适配性:根据实际电路接口,自动生成仿真模型,无须手工绘制,可节省大量时间和精力。

2. 建模精度:采用仿真模型进行仿真分析,模型的建立过程和仿真数据的处理过程均达到高精度的要求。

3. 可视化展示:提供直观、易于理解的仿真结果图像,用户可对仿真结果进行直观的分析和判断。

4. 高效优化:在分析结果的基础上,提供了一系列可行性方案,以便优化布局和电路设计,提高设计质量和效率。

5. 多维度仿真:支持多种仿真方式,可以分析不同工作频率、物理层、仿真类型等多种因素的影响。

6. 构建模块化:支持多种最新技术,如DDR、PCIe等,可实现模块化的仿真分析。

使用步骤Allegro PCB SI仿真的使用步骤如下:1. 在Allegro 设计工具中添加SI 仿真属性:在Allegro 中进行PCB 设计工作的人员首先需要添加SI 仿真属性。

这时需要使用Allegro constraint manager 工具,在其中添加SI 属性和控制器约束等信息。

Allegro SI 分析扫描过程会依据这些信息实现电路仿真。

2. 运行Allegro SI 分析:电路设计人员在完成电路布线后,需要使用Allegro SI 分析来分析信号完整性情况,以发现和解决可能存在的电路问题。

执行步骤为:首先选择si_analysis 工具,在其菜单中选择指定布线仿真设置;然后在仿真window 中选择仿真起点、仿真长度等参数,然后点击Run。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

基于Cadence Allegro SI 16.3的信号完整性仿真信号完整性是指信号在信号线上的质量。

信号具有良好的信号完整性是指当在需要的时候,具有所必需达到的电压电平数值。

差的信号完整性不是由某一因素导致的,而是由板级设计中多种因素共同引起的。

特别是在高速电路中,所使用的芯片的切换速度过快、端接元件布设不合理、电路的互联不合理等都会引起信号的完整性问题。

具体主要包括串扰、反射、过冲与下冲、振荡、信号延迟等。

信号完整性问题由多种因素引起,归结起来有反射、串扰、过冲和下冲、振铃、信号延迟等,其中反射和串扰是引发信号完整性问题的两大主要因素。

反射和我们所熟悉的光经过不连续的介质时都会有部分能量反射回来一样,就是信号在传输线上的回波现象。

此时信号功率没有全部传输到负载处,有一部分被反射回来了。

在高速的PCB中导线必须等效为传输线,按照传输线理论,如果源端与负载端具有相同的阻抗,反射就不会发生了。

如果二者阻抗不匹配就会引起反射,负载会将一部分电压反射回源端。

根据负载阻抗和源阻抗的关系大小不同,反射电压可能为正,也可能为负。

如果反射信号很强,叠加在原信号上,很可能改变逻辑状态,导致接收数据错误。

如果在时钟信号上可能引起时钟沿不单调,进而引起误触发。

一般布线的几何形状、不正确的线端接、经过连接器的传输及电源平面的不连续等因素均会导致此类反射。

另外常有一个输出多个接收,这时不同的布线策略产生的反射对每个接收端的影响也不相同,所以布线策略也是影响反射的一个不可忽视的因素。

串扰是相邻两条信号线之间的不必要的耦合,信号线之间的互感和互容引起线上的噪声。

因此也就把它分为感性串扰和容性串扰,分别引发耦合电流和耦合电压。

当信号的边沿速率低于1ns时,串扰问题就应该考虑了。

如果信号线上有交变的信号电流通过时,会产生交变的磁场,处于磁场中的相邻的信号线会感应出信号电压。

一般PCB板层的参数、信号线间距、驱动端和接收端的电气特性及信号线的端接方式对串扰都有一定的影响。

在Cadence 的信号仿真工具中可以同时对6条耦合信号线进行串扰后仿真,可以设置的扫描参数有:PCB 的介电常数,介质的厚度,沉铜厚度,信号线长度和宽度,信号线的间距.仿真时还必须指定一个受侵害的信号线,也就是考察另外的信号线对本条线路的干扰情况,激励设置为常高或是常低,这样就可以测到其他信号线对本条信号线的感应电压的总和,从而可以得到满足要求的最小间距和最大并行长度。

过冲是由于电路切换速度过快以及上面提到的反射所引起的信号跳变,也就是信号第一个峰值超过了峰值或谷值的设定电压。

下冲是指下一个谷值或峰值。

过分的过冲能够引起保护二极管工作,导致过早地失效,严重的还会损坏器件。

过分的下冲能够引起假的时钟或数据错误。

它们可以通过增加适当端接予以减少或消除。

在Cadence的信号仿真软件中,将以上的信号完整性问题都放在反射参数中去度量。

在接收和驱动器件的IBIS模型库中,我们只需要设置不同的传输线阻抗参数、电阻值、信号传输速率以及选择微带线还是带状线,就可以通过仿真工具直接计算出信号的波形以及相应的数据,这样就可以找出匹配的传输线阻抗值、电阻值、信号传输速率,在对应的PCB软件Allegro中,就可以根据相对应的传输线阻抗值和信号传输速率得到各层中相对应信号线的宽度(需提前设好叠层的顺序和各参数)。

选择电阻匹配的方式也有多种,包括源端端接和并行端接等,根据不同的电路选择不同的方式。

在布线策略上也可以选择不同的方式:菊花型、星型、自定义型,每种方式都有其优缺点,可以根据不同的电路仿真结果来确定具体的选择方式。

信号延迟是电路中只能按照规定的时序接收数据,过长的信号延迟可能导致时序和功能的混乱,在低速的系统中不会有问题,但是信号边缘速率加快,时钟速率提高,信号在器件之间的传输时间以及同步时间就会缩短。

驱动过载、走线过长都会引起延时。

必须在越来越短的时间预算中要满足所有门延时,包括建立时间,保持时间,线延迟和偏斜。

由于传输线上的等效电容和电感都会对信号的数字切换产生延迟,加上反射引起的振荡回绕,使得数据信号不能满足接收端器件正确接收所需要的时间,从而导致接收错误。

在Cadence的信号仿真软件中,将信号的延迟也放在反射的子参数中度量,有Settledelay、Switchdelay、Propdelay。

其中前两个与IBIS模型库中的测试负载有关,这两个参数可以通过驱动器件和接收器件的用户手册参数得到,可以将它们与仿真后的Settledelay、Switchdelay加以比较,如果在Slow模式下得到的Switchdelay都小于计算得到的值,并且在Fast的模式下得到的Switchdelay的值都大于计算得到的值,就可以得出我们真正需要的两个器件之间的时延范围Propdelay。

在具体器件布放的时候,如果器件的位置不合适,在对应的时延表中那部分会显示红色,当把其位置调整合适后将会变成蓝色,表示信号在器件之间的延时已经满足Propdelay规定的范围了。

PCB 仿真设计的一般流程:原理图设计阶段:编制元件表、建立连线网表、建立元器件封装库、确定电路逻辑符号与物理器件的映射(指定元器件封装)PCB 前仿真:高速PCB 的前仿真包括以下几个方面:信号完整性(SI)仿真,时序(TIMING)仿真,电磁兼容性(EMI)仿真。

PCB 布局布线:模板设计、确定PCB 尺寸、形状、层数及层结构、元件放置、输入网表、设计PCB 布线规则、PCB 交互布局、PCB 走线、PCB 光绘文件生成、钻孔数据文件。

PCB 后仿真:高速PCB 的后仿真:信号完整性(SI)后仿真,电源完整性(PI)后仿真,电磁兼容性(EMI)后仿真。

功能、性能、EMI 测试:单板调试、性能测试、设计验证、温度试验、EMI 测试等。

Cadence 高速设计流程中的仿真条件及实施:以下将逐个介绍如何在Cadence的高速设计流程中实现这些仿真条件,通过仿真分析,得到高速设计的约束条件和实施设计约束。

一、获取模型1、/ibis/home/models/models.htm2、到器件厂商的官方网站下载二、模型验证和管理用Cadence集成工具Model Integrity打开模型,此工具将自动检查验证模型。

如果没有错误,将模型转换成DML格式。

注意:DML是Cadence专用的模型语言,在Cadence的高速设计环节中所有的器件模型都以DML格式存储并使用。

不管用户使用的是什么文件,在仿真之前都要转换成DML 格式的文件才能被Cadence的仿真引擎所识别并使用。

三、仿真库的建立和设置上一步得到了经过验证的DML模型库,下面将把这个模型库加入到设计中使用。

在PCB SI菜单中,选择Analyze---SI/EMI sim---Model Browser,出现如下模型库管理界面:选择Set Search Path,出现以下界面,可以通过选择Add Directory指向我们之前保存的模型库文件夹。

四、仿真分析条件设置通过菜单Tools=》Setup Advisor命令打开Database Setup Advisor 窗口,打开的窗口如下图所示:Cross-section:定义在Layout中使用的叠层和材料参数;DC Nets:定义直流电压值,也即系统静态工作点;Device:指定器件的类型和Pinuse属性;SI Module:为器件的指定电气模型;SI Audit:对前面的设置进行检查以确保能够进行正常地进行抽取和仿真。

点击Next,选择Edit Cross-section,出现PCB叠层参数设置界面:在此对话框中,可以添加或者删除叠层,也可以改变每一层的类型、材料、厚度、电导率、介电常数、线宽和特征阻抗等参数。

做完并关闭叠层参数的设计之后,回到Database Setup Advisor界面,点击Next,进入直流电源网络的设置界面,如下:选择左侧列表框中的待选网络,在右侧的文本框中可以指定该网络直流电压值。

设置好直流电压后,回到Database Setup Advisor界面,点击Next,出现以下界面:点击Device Setup,进入器件类型设置界面:在此界面中,用户可以指定以特定字符开始的器件标号属于某一类器件。

对于Default Value,原理图中标明的是多大就标多大。

设置好后继续Next,进入模型分配界面:Devices目录显示了所有网表中导入的元器件,要指定模型,先选中,然后点Find Model,弹出模型分配对话框:在Model Name Pattern中输入“*”,按“Tab”键,库目录中所有的模型将列出来,选择合适的,点击Assign,模型就被分配好了。

当以上所有的仿真条件及参数设置完成之后,在Database Setup的最后一步我们可以用SI Audit进行一下验证,以确保我们所关心的网络上所有和仿真相关的因素都已经处理好了。

如果Audit的结果出错,对照结果的提示,找到出错的原因,重复前面的某些步骤,对仿真条件进行修改和完善,如果没有问题就可以进入下一步的高速信号仿真了。

以上对仿真的各项条件进行了详细讲解,下面将结合具体例子来说明如何来仿真。

如图所示一个预布局好的PCB,以下将对PCB中一对差分信号进行仿真,首先必须进行阻抗控制,器件模型分配,前面已经讲过具体的操作过程,这里不再赘述,接下来我们需要对差分对进行拓扑提取。

1、设置互联模型参数从Allegro PCB SI GXL窗口选择Analyze---SI/EMI Sim---Preference命令,弹出Analyze Preferences窗口,选择“Interconnect Models”如下图:在“Unrouted Interconnect Models”部分,设置“Percent Manhattan”为100,“Default Diff-Impedance”为100ohm,在“Topology Extraction”部分确保选择“Differential Extraction Mode”,如果没有选择,差分对拓扑将仅使用理想传输线模型。

为了使用理想的耦合传输线模型,必须选择“Differential Extraction Mode”。

2、提取拓扑在“Allegro Constraint Manager”窗口选择“Net”---“Routing”---“Differential Pair”如下图:选择“DP_LOOPIN”差分对(差分对可以在原理图或者导入PCB之后设置),单击右键,选择“SigXplorer”命令,弹出“SigXplorer PCB SI GXL”窗口,显示了提取的有理想耦合的传输线模型的差分对拓扑,如下图所示:的“time”改为“length”。