基于Encounter的自动布局布线

《自动布局布线》课件

探索自动布局布线的奇妙世界,帮助你提高电路板或芯片的性能,节省时间, 减少错误。

什么是自动布局布线?

自动布局布线是一种方法,用于自动为电路板或芯片设计最佳电线布局。

为什么需要自动布局布线?

手动布线耗时且容易出错,而自动布局布线可以节省时间、减少错误,并提 高电路板或芯片的性能。

2 准确性

避免人为错误,提高电路板或芯片的性能。

4 高效

节省时间,快速完成布线任务。

自动布局布线的挑战

算法复杂度高

处理大规模网络布线的算法复杂度较高。

异常情况处理

对输入异常情况的处理较困难,需要更精细的算法设计。

CPU处理限制

处理大规模网络布线时,仅依靠CPU很难满足要求。

结论

自动布局布线能够帮助我们节省时间、减少错误,并提高电路板或芯片的性 能。

自动布局布线的流程,为后续布线准备。

2

网络构建

将电路元件在网格中建立连接,形成网络。

3

优化网络

对网络进行优化,使其满足性能要求。

4

生成布线

根据优化后的网络,生成最佳的电线布局。

自动布局布线的优势

1 自动化

提高效率,减少人工工作量。

3 可重复性

保持一致的布线质量。

尽管自动布局布线还面临一些挑战,但随着技术发展,我们可以期待它在未 来发挥更大的作用。

SOC_encounter使用说明

上述设置如下图所示:

具体的电源条 参数值需根据 设计特点如功 耗值,设计面 积等信息进行 设定。

设置完成后,8条垂直电源条如下分布:

上述若发现存在Stripes未连接上,则点击菜单栏Route Special Route, 只选择‘Stripes(unconnected)‟选项,如下 图:

2011.01.09

概要

在本篇ppt中,主要以一个32位的流水线加法 器设计为例,介绍SOC Encounter V7.1版本 自动布局布线工具的主要使用方法及步骤。

目录

以加法器为例,将综合后的结果导入SOC Encounter, 生成 GDSII版图分为以下几个步骤:

根据设计特点不同,这些选 项可灵活调整。

• 点击‘Attribute‟键,设置一些Net的属性,如下:

选中‘Net Type‟,选择‘Clock Nets‟, 即对时钟Nets的布线作一些 特殊设置。

Skip Antenna: 选择FALSE; Skip Rouing: 选择FALSE; Avoid Detour: 选择TRUE; SI Prevention: 选择TRUE; SI Post Route Fix: 选择 TRUE; Weight: 10; Spacing: 1。设置如下,然后点击‘OK‟。

(5)给’Advanced‘中SI Analysis项填入如下噪声库.cdB文件:

上述各项填好后,点‟save‟将此次的设置保存成.conf文件,然后 点击’OK„键即可导入设计,如下图:

Floorplan

点击菜单栏Floorplan Specify Floorplan,如下:

• 指定Core/Die的面积或者Core的利用率,如本例中指定了Die的 宽高分别为3200,3200um。具体的大小值可通过预估,试验几 次等方法进行估算。 • 指定Core到IO/Die边界的距离,以给电源环留下足够的空间,本 例中设定Core到IO边界上下左右的距离都为100um。如下图:

自动布局布线软件

浙大微电子

11/74

工具界面

命令输入 例如:help “insertPad” 查看insertPad 命令使用方法

浙大微电子

6/74

Astro自动布局布线流程

参考库 门级网表

时序约束文件 数据输入

IO管脚排列文件

工艺文件

布局规划

布线

布局

静态时序分析,后仿真

时钟综合

DRC、LVS

流片

浙大微电子

7/74

数据输入

工艺库文件--是Foundry或IP提供商提供的各 种库(标准单元库、IO库、SRAM库和IP库) 和工艺文件 --网站下载

dbCreateCellInst (geGetEditCell) "" "PCORNERRN" "CORNER3" "0" "No" '(0 0) "fsk0323"

dbCreateCellInst (geGetEditCell) "" "PCORNERRN4;0" "No" '(0 0) "fsk0323"

设计文件—网表文件(.sv文件)和时序约束 文件(.sdc文件)--都是DC综合得到

管脚排列文件(.tdf文件)--手动编写,保存成 XXX.tdf到任意你能找到目录里。

课件中是在软件启动目录下创建了一个data目录来 保存tdf文件

浙大微电子

8/74

IO管脚排列文件

IO顺序 插入一些特殊的IO单元:

pad "en_block" "bottom" 1

自动布局布线(SiliconEnsemble)

Timing Library Format (TLF)

General Constraints Format (GCF) file Standard Delay Format (SDF) Constraints File

Library Requirements

LEF

• • LEF库是一个文本文件,描述目标工艺库中宏单元的局部的物 理信息。其描述必须符合LEF规定结构及语法。 LEF库描述标准单元库的工艺特性及单元(cell)数据 • • • • 描述用于宏单元互连的各布线层的详细信息 布线器要用的via单元 core和pad的位置定义

使用 Abstract Generator产生LEF库

• 可以使用Abstract Generator或 AutoABgen产生Abstract和LEF

View of a NAND Gate

TLF

• • • TLF文件描述单元库的时序信息 进行时序驱动布局布线及产生时钟树所必需 描述的元件与其它库一致,包括: • • • • LEF库所有单元,并有一致的单元信号引脚,除电源、地 引脚次序与Verilog库一致

LEF库可以有一个或多个 LEF库可以由Envisia™ Abstract Generator产生 注意LEF的版本。对于SEDSM, LEF版本要高于5.1。 用Import LEF命令读入LEF文件来建立设计数据库。

LEF — 工艺说明

• 不需要说明IC设计所需要的所有层的信息,如扩散层,就不需 要在LEF文件中描述,除非有在扩散层的pin

•

System support tools:导 入/导出数据、验证设计数据并可以手工进行 布局布线。

SE 特点

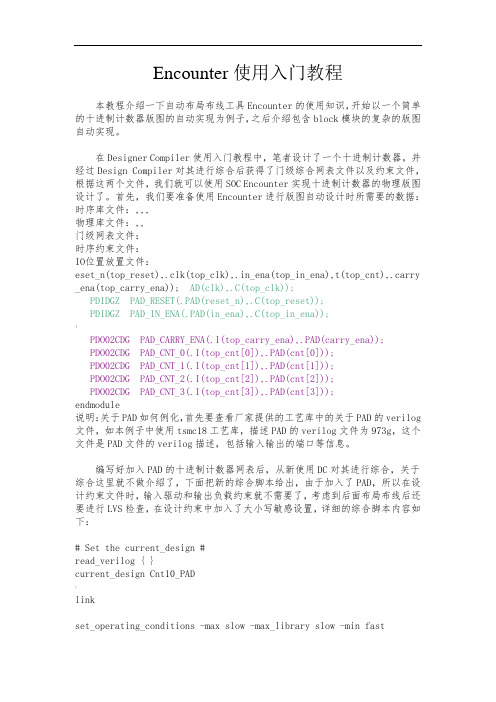

Encounter使用入门教程

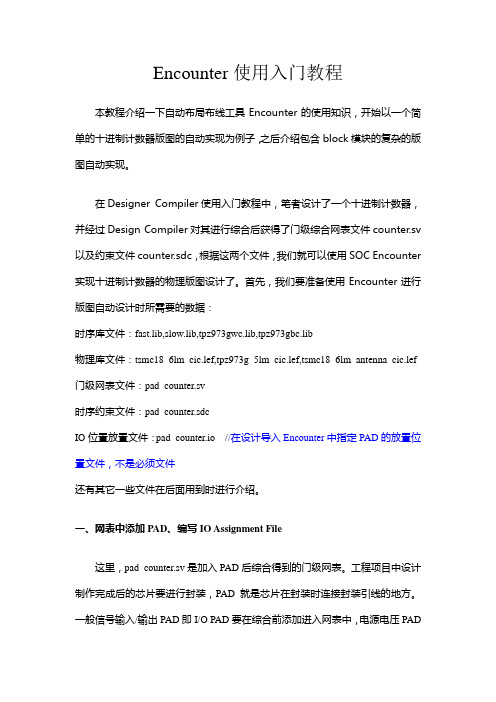

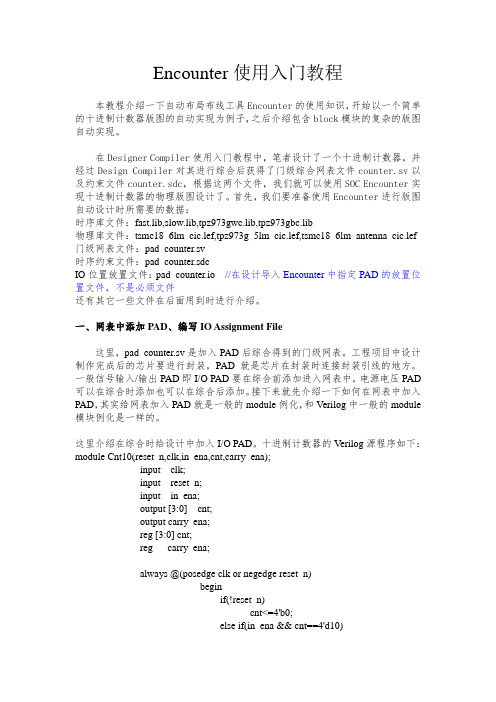

Encounter使用入门教程本教程介绍一下自动布局布线工具Encounter的使用知识,开始以一个简单的十进制计数器版图的自动实现为例子,之后介绍包含block模块的复杂的版图自动实现。

在Designer Compiler使用入门教程中,笔者设计了一个十进制计数器,并经过Design Compiler对其进行综合后获得了门级综合网表文件counter.sv 以及约束文件counter.sdc,根据这两个文件,我们就可以使用SOC Encounter 实现十进制计数器的物理版图设计了。

首先,我们要准备使用Encounter进行版图自动设计时所需要的数据:时序库文件:fast.lib,slow.lib,tpz973gwc.lib,tpz973gbc.lib物理库文件:tsmc18_6lm_cic.lef,tpz973g_5lm_cic.lef,tsmc18_6lm_antenna_cic.lef 门级网表文件:pad_counter.sv时序约束文件:pad_counter.sdcIO位置放置文件:pad_counter.io //在设计导入Encounter中指定PAD的放置位置文件,不是必须文件还有其它一些文件在后面用到时进行介绍。

一、网表中添加PAD、编写IO Assignment File这里,pad_counter.sv是加入PAD后综合得到的门级网表。

工程项目中设计制作完成后的芯片要进行封装,PAD就是芯片在封装时连接封装引线的地方。

一般信号输入/输出PAD即I/O PAD要在综合前添加进入网表中,电源电压PAD可以在综合时添加也可以在综合后添加。

接下来就先介绍一下如何在网表中加入PAD,其实给网表加入PAD就是一般的module例化,和Verilog中一般的module 模块例化是一样的。

这里介绍在综合时给设计中加入I/O PAD。

十进制计数器的Verilog源程序如下:module Cnt10(reset_n,clk,in_ena,cnt,carry_ena);input clk;input reset_n;input in_ena;output [3:0] cnt;output carry_ena;reg [3:0] cnt;reg carry_ena;always @(posedge clk or negedge reset_n)beginif(!reset_n)cnt<=4'b0;else if(in_ena && cnt==4'd10)cnt<=4'b0;else if(in_ena && cnt<4'd10)cnt<=cnt+1'b1;endalways @(posedge clk or negedge reset_n)beginif(!reset_n)carry_ena<=1'b0;else if(in_ena && cnt==4'd10)carry_ena<=1'b1;elsecarry_ena<=1'b0;endendmodule加入PAD后的十进制计数器Verilog网表如下:module Cnt10_PAD(reset_n,clk,in_ena,cnt,carry_ena); //顶层模块input reset_n;input clk;input in_ena;output [3:0] cnt;output carry_ena;wire top_clk,top_reset,top_in_ena;wire top_carry_ena;wire [3:0] top_cnt;Cnt10CNT10(.reset_n(top_reset),.clk(top_clk),.in_ena(top_in_ena),.cnt(top_cnt),.carry_ena (top_carry_ena)); //这里是对Cnt10 module的例化//下面是I/O PAD module的例化PDIDGZ PAD_CLK(.PAD(clk),.C(top_clk));PDIDGZ PAD_RESET(.PAD(reset_n),.C(top_reset));PDIDGZ PAD_IN_ENA(.PAD(in_ena),.C(top_in_ena));PDO02CDG PAD_CARRY_ENA(.I(top_carry_ena),.PAD(carry_ena));PDO02CDG PAD_CNT_0(.I(top_cnt[0]),.PAD(cnt[0]));PDO02CDG PAD_CNT_1(.I(top_cnt[1]),.PAD(cnt[1]));PDO02CDG PAD_CNT_2(.I(top_cnt[2]),.PAD(cnt[2]));PDO02CDG PAD_CNT_3(.I(top_cnt[3]),.PAD(cnt[3]));endmodule说明:关于PAD如何例化,首先要查看厂家提供的工艺库中的关于PAD的verilog 文件,如本例子中使用tsmc18工艺库,描述PAD的verilog文件为tpz973g.v,这个文件是PAD文件的verilog描述,包括输入输出的端口等信息。

Encounter使用方法

Encounter使用入门教程本教程介绍一下自动布局布线工具Encounter的使用知识,开始以一个简单的十进制计数器版图的自动实现为例子,之后介绍包含block模块的复杂的版图自动实现。

在Designer Compiler使用入门教程中,笔者设计了一个十进制计数器,并经过Design Compiler对其进行综合后获得了门级综合网表文件counter.sv以及约束文件counter.sdc,根据这两个文件,我们就可以使用SOC Encounter实现十进制计数器的物理版图设计了。

首先,我们要准备使用Encounter进行版图自动设计时所需要的数据:时序库文件:fast.lib,slow.lib,tpz973gwc.lib,tpz973gbc.lib物理库文件:tsmc18_6lm_cic.lef,tpz973g_5lm_cic.lef,tsmc18_6lm_antenna_cic.lef 门级网表文件:pad_counter.sv时序约束文件:pad_counter.sdcIO位置放置文件:pad_counter.io //在设计导入Encounter中指定PAD的放置位置文件,不是必须文件还有其它一些文件在后面用到时进行介绍。

一、网表中添加PAD、编写IO Assignment File这里,pad_counter.sv是加入PAD后综合得到的门级网表。

工程项目中设计制作完成后的芯片要进行封装,PAD就是芯片在封装时连接封装引线的地方。

一般信号输入/输出PAD即I/O PAD要在综合前添加进入网表中,电源电压PAD 可以在综合时添加也可以在综合后添加。

接下来就先介绍一下如何在网表中加入PAD,其实给网表加入PAD就是一般的module例化,和Verilog中一般的module 模块例化是一样的。

这里介绍在综合时给设计中加入I/O PAD。

十进制计数器的Verilog源程序如下:module Cnt10(reset_n,clk,in_ena,cnt,carry_ena);input clk;input reset_n;input in_ena;output [3:0] cnt;output carry_ena;reg [3:0] cnt;reg carry_ena;always @(posedge clk or negedge reset_n)beginif(!reset_n)cnt<=4'b0;else if(in_ena && cnt==4'd10)cnt<=4'b0;else if(in_ena && cnt<4'd10)cnt<=cnt+1'b1;endalways @(posedge clk or negedge reset_n)beginif(!reset_n)carry_ena<=1'b0;else if(in_ena && cnt==4'd10)carry_ena<=1'b1;elsecarry_ena<=1'b0;endendmodule加入PAD后的十进制计数器Verilog网表如下:module Cnt10_PAD(reset_n,clk,in_ena,cnt,carry_ena); //顶层模块input reset_n;input clk;input in_ena;output [3:0] cnt;output carry_ena;wire top_clk,top_reset,top_in_ena;wire top_carry_ena;wire [3:0] top_cnt;Cnt10CNT10(.reset_n(top_reset),.clk(top_clk),.in_ena(top_in_ena),.cnt(top_cnt),.carry_ena (top_carry_ena)); //这里是对Cnt10 module的例化//下面是I/O PAD module的例化PDIDGZ PAD_CLK(.PAD(clk),.C(top_clk));PDIDGZ PAD_RESET(.PAD(reset_n),.C(top_reset));PDIDGZ PAD_IN_ENA(.PAD(in_ena),.C(top_in_ena));PDO02CDG PAD_CARRY_ENA(.I(top_carry_ena),.PAD(carry_ena));PDO02CDG PAD_CNT_0(.I(top_cnt[0]),.PAD(cnt[0]));PDO02CDG PAD_CNT_1(.I(top_cnt[1]),.PAD(cnt[1]));PDO02CDG PAD_CNT_2(.I(top_cnt[2]),.PAD(cnt[2]));PDO02CDG PAD_CNT_3(.I(top_cnt[3]),.PAD(cnt[3]));endmodule说明:关于PAD如何例化,首先要查看厂家提供的工艺库中的关于PAD的verilog 文件,如本例子中使用tsmc18工艺库,描述PAD的verilog文件为tpz973g.v,这个文件是PAD文件的verilog描述,包括输入输出的端口等信息。

CADENCEPCB设计布局与布线

CADENCEPCB设计布局与布线CADENCEPCB设计工具是电子工程师在进行PCB电路板设计时经常使用的软件。

其强大的功能使得设计师可以进行布局和布线,确保电路板的性能和可靠性。

下面将详细介绍CADENCEPCB设计的布局和布线过程。

首先是布局过程。

布局是指在PCB上放置电子元器件和确定它们之间的物理布置。

布局的目标是优化电路板的性能、减小电磁干扰并提供良好的散热。

以下是CADENCEPCB设计中的布局步骤:1.确定布局约束:首先,设计师需要根据电路的要求和特定的应用环境,确定布局的约束条件,如电源分配、信号完整性、热管理等。

这些约束条件将指导接下来的布局和布线过程。

2.放置电子元器件:根据电路图和设计要求,将电子元器件在PCB上进行合理的放置。

重要的因素包括元器件之间的物理距离,信号和电源线的长度和走向,以及避免冲突和干扰的布局。

3.优化布局:在放置元器件之后,设计师需要优化布局,以确保信号完整性。

这包括优化电源和地平面的布置,减小信号线的长度和交叉,并提供良好的散热条件等。

4.电源和地平面设计:在布局过程中,需要合理设计电源和地平面,以提供足够的电源稳定性和地电流供应。

这需要将电源和地线走线得当,并采用合适的电容和电感等元件进行滤波和终端处理。

接下来是布线过程。

布线是指设计师将电子元器件之间的连线进行优化和优化,以确保信号的完整性、最小化电磁干扰并满足设计约束条件。

以下是CADENCEPCB设计中的布线步骤:1.设计路由规则:在进行布线之前,设计师需要制定一个路由规则,包括最小线宽和线间距、阻抗控制、信号类型和电源线与地线的关系等。

这些规则将指导后续的布线过程。

2.自动布线:CADENCEPCB设计工具提供了自动布线工具,可以根据预先设定的规则和优化目标,自动生成布线方案。

设计师可以根据需要进行调整和优化。

3.手动布线:对于一些复杂的板线、高速信号或特殊需求,手动布线是必要的。

对于这些情况,设计师需要手动布线,根据设计约束和优化目标,确定线路的走向和走线方式,并避免冲突和干扰。

自动布局布线

//插入Corner

dbCreateCellInst (geGetEditCell) "" "PCORNERW" "CORNER1" "0" "No" '(0 0) "design_in"

AND2HDLX U1 ( .A(A[0]), .B(B[0]), .Z(carry_1_) ); XOR2HDLX U2 ( .A(B[0]), .B(A[0]), .Z(SUM[0]) );

2020/5/22

共83页

7

2020/5/22

共83页

8

自动布局布线工具—Astro介绍

Astro是Synopsys公司开发的一种基于标准单 元的版图自动生成工具,通过调用标准单元库中 的门单元进行自动布局布线完成版图设计,其前 身是Avanti公司(2002年被Synopsys公司收购) 的Apollo。 2007年以后软件叫ICC 。

翻译

映射

2020/5/22

共83页

4

setup/hold

建立(setup)时间是指触发器的时钟信号上 升沿到来以前,数据稳定不变的时间。

保持(hold)时间是指触发器的时钟信号上升 沿到来以后,数据稳定不变的时间。

裕度(slack):是时序要求与实际时序之间 的差值,反映了时序是否满足要求。裕度为正, 满足要求dat;a 反之不满足。 裕度=clk要求的时间-实际的时间

使用Encounter进行电路布局布线

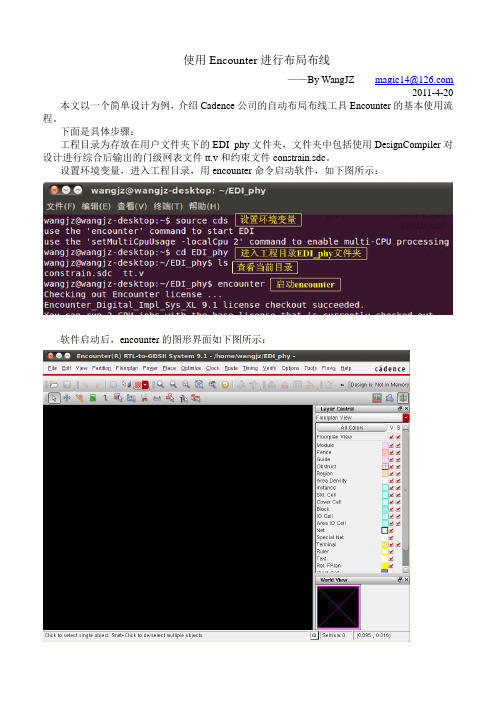

使用Encounter进行布局布线——By WangJZ magic14@2011-4-20 本文以一个简单设计为例,介绍Cadence公司的自动布局布线工具Encounter的基本使用流程。

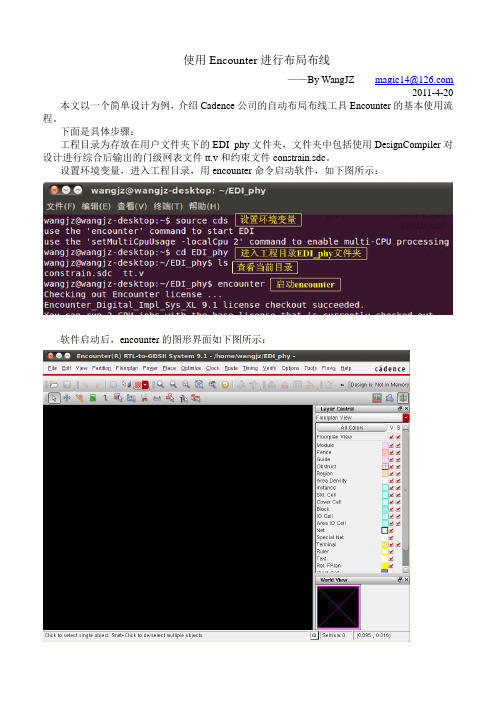

下面是具体步骤:工程目录为存放在用户文件夹下的EDI_phy文件夹,文件夹中包括使用DesignCompiler对设计进行综合后输出的门级网表文件tt.v和约束文件constrain.sdc。

设置环境变量,进入工程目录,用encounter命令启动软件,如下图所示:软件启动后,encounter的图形界面如下图所示:导入设计文件,如下所示。

其他选项可暂时不填,保持默认设置,点击确认按钮。

成功导入设计文件后,Encounter视图如下所示:定义设计的尺寸、长宽比等信息,如下所示:完成后如下图所示,Core区和IO边缘有10um的距离。

添加全局连线,此处主要是电源和地的全局连线,分别把VDD的pin、net和高电平连接到全局连线VDD,把VSS的pin、net和低电平连接到全局连线VSS,如下所示:添加电源环,如下所示:填入电源环的宽度、距离、使用的金属层等信息,点击确认后,电源环添加到Core区和IO 边缘之间的空间,如下所示:添加core区中标准单元的电源连线,如下所示:添加电源连线后,视图如下所示:放置标准单元,然后切换到版图视图,可看到标准单元放置后的效果,如下所示:接着进行时钟树综合,可使用手动编写的时钟树配置文件或者用软件自动生配置文件进行时钟树综合。

此处采用软件自动生成配置文件的方式,如下所示:时钟树综合的同时会进行版图的初始布线。

完成时钟树综合后,进行版图的详细布线,如下所示:详细布线采用默认设置即可,完成详细布线后效果图如下:如果只是进行Encounter的学习,到此处即可保存并输出结果。

如果是要进行实际的流片生产,还需对各层进行填充,包括标准单元填充和各个金属层的填充,以保证满足生产所需的密度。

基于Encounter软件的布局布线_

导出GDSⅡ

共44页 44

谢谢大家!

共44页

45

共44页

7

Design Import对话框中Design栏

共44页 8

Core Spec Defaults栏

在Core Spec Defaults栏目中: Spect Ratio为芯片的高度和宽度之比; Core Utilization是芯片的利用率; Core to left:芯片到左边I/O边缘的距离; Core to right:芯片到右边I/O边缘的距离; Core to top:芯片到上边边I/O边缘的距离; Core to bottom:芯片到下边I/O边缘的距离; 设置Core到I/O边缘的距离大于零是为了给后面布电源和地线留出空间来。

共44页 10

Power栏

Power/Ground Nets/Power Nets中填入设计需要的电源名称; Power/Ground Nets/Ground Nets中填入设计需要的地线名称; 在后面布电源线和地线的时候会用到;如果设计中有多组电源和地, 比如电源有VDDC、 VDDO、VDDH和地VSSC,、VSSO、VSSH,就分别都填上去,中 间用一个空格隔开。

共44页 18

添加了横竖STRIPES后的版图

共44页 19

SROUTE

布好CORE 的电源和地 线后,就可 以给标准单 元布电源和 地线,通过 Route / SRoute设置

共44页 20

Basic / Net (s) 中填入给标准 单元供电的电 源地线。 Route一栏选 择要连接该组 电源地线的选 项。 Layer Change Control中Top layer和Bottom layer分别填入 用到的库的最 高金属层次和 最低金属层次。 Sroute对话框

Cadence后端实验系列15布局布线SoCEncouter

5、creat power ring

在power里选择power planing→add rings会弹出add ring对话框

将值设为1

选上选项,将number of bits设 为3

6、placement

• place→standard cells

里面的参数我们用默认值,1

然后place→place Flip I/O

Outline

• SOC Encounter 简介 • SOC Encounter 布局/布线 流程 • 布局布线中的参数设置 • 演示

SOC Encounter 简介

SOC Encounter是cadence数字集成电路设计平台的 一个集成的后端工具,功能相当强大,可以从综合,一 直做到生成GDSII文件!当然里面集成了很多的工具,如 RC,Nanoroute,FIRE&ICE QXC等。支持超过5000万门 180纳米以下工艺的层次化设计。

7、Route route→nanoroute

选上timing driven和 SI driven

选择attribute,修改参数

选上ture,意思是 route as short as possible

Weight, spacing都 设为1

得到最后的布线图

参考文献

➢ SOC encounter user guide ➢ 台湾经典培训教材-SOC Encounter

SOC Encounter 布局/布线 流程

IO,电源和地的布置

指定平面布置图 平面布置图

电源的规划

电源布线

布线

输入文件

• 逻辑和时序库:TLF或.lib • 物理库:库交换格式(.LEF) • 门级网表:*.v • 时序约束:*.sdc • IO assignment file:*.io

Encounter_数字版图设计流程

28 后仿真 ........................................................................................................................................... 35 版图体会 ............................................................................................................................................... 36

by:Zhu Qiuling

1

1 目录

基于 hejian18 工艺的 SOC Ecounter 数字版图设计流程 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 25 26 27 目录 .............................................................................................................................................. 2 文件准备 ...................................................................................................................................... 3 运行软件 ...................................................................................................................................... 7 DESIGN_IMPORT ...................................................................................................................... 8 LOAD DEF 文件和 IO FILE 文件 ......................................................................................... 10 GLOBAL NET CONNECTION............................................................................................... 11 FLOORPLAN ............................................................................................................................ 12 ADD POWER RINGS .............................................................................................................. 13 ADD STRIPES .......................................................................................................................... 14 PLACEMENT BLOCKAGE .................................................................................................... 14 PLACEMENT............................................................................................................................ 15 SPECIAL ROUTE (SROUTE) ................................................................................................. 16 CREAT CLOCK TREE SPEC ................................................................................................. 17 CLOCK TREE SYNTHESIS.................................................................................................... 18 POST–CTS OPTIMIZATION .................................................................................................. 19 TRAIL ROUTING ..................................................................................................................... 20 NANO ROUTING ..................................................................................................................... 20 IO FILLING ............................................................................................................................... 21 ADD FILLING .......................................................................................................................... 22 POST – ROUTE OPTIMIZATION .......................................................................................... 23 生成 SDF 时序文件 .................................................................................................................. 23 VERIFY CONNECTIVITY...................................................................................................... 24 VERIFY GEOMETRY .............................................................................................................. 25 EXPORT FILES......................................................................................................................... 26 版图验证——导入 ICFB ......................................................................................................... 28 DRC ............................................................................................................................................ 30 LVS ............................................................................................................................................. 32

集成电路设计中的自动布局布线方法研究

集成电路设计中的自动布局布线方法研究在集成电路的设计过程中,自动布局布线是必不可少的一步。

它的目标是将电路中的各个组件合理地布局在芯片的表面,并通过导线将它们连接起来,以实现电路的功能。

自动布局布线方法的研究可以提高电路的性能、减小面积、降低功耗,对于集成电路的设计具有重要的意义。

自动布局布线方法的研究主要包括两个方面,即自动布局和自动布线。

自动布局是指在给定的芯片面积内,将电路中的各个组件按照一定的规则自动布置在芯片上,使得它们之间的距离适当,并且不产生电路冲突。

自动布线是指根据布局结果,自动地在芯片的表面上生成导线网络,使得电路中的各个组件之间能够正确地互连。

在自动布局的研究中,通常采用的方法是通过建立电路的等效模型,将布局问题转化为数学优化问题。

具体来说,可以使用基于禁忌搜索、模拟退火等启发式算法来求解布局问题。

另外,还可以利用迁移学习、强化学习等机器学习方法,通过训练模型来优化布局结果。

在自动布线的研究中,常常使用的方法是通过建立网络流模型,将布线问题转化为最小费用流、最大流等经典问题。

然后,可以采用广度优先搜索、深度优先搜索等算法来求解布线问题。

此外,还可以使用并行计算、多目标优化等技术,提高布线的效率和质量。

自动布局布线方法的研究不仅需要考虑电路的性能,还需满足芯片的制造工艺要求。

因此,在布局布线的过程中,需要考虑到电路的延迟、功耗、面积等指标,并且要遵守芯片制造的规则。

例如,可以利用线性规划等数学方法来求解布局布线问题中的多目标优化问题,以平衡不同指标的要求。

自动布局布线方法的研究还要考虑到不同工艺、不同电路结构之间的差异性。

因此,对于不同类型的电路,需要采用不同的布局布线方法。

例如,对于数字电路,可以采用网格化布局方法,将电路中的组件和导线都放置在网格交叉点上。

而对于模拟电路,可以采用层次化布局方法,将电路中的组件和导线分别放置在不同的层次上。

总的来说,自动布局布线方法的研究对于集成电路的设计具有重要的意义。

印制电路板的自动布局与自动布线

印制电路板的构造

基板

作为电路板的承载体, 通常由绝缘材料制成,

如FR4、CEM-1等。

铜箔

元件

附着在基板上,形成导 电路径,具有导电性能。

安装在电路板上的电子 元件,如电阻、电容、

电感等。

焊盘

连接元件引脚和导电路径 的金属片,通过焊接实现 元件与电路板的连接。

印制电路板的设计流程

原理图设计

使用EDA(Electronic Design Automation)软件 绘制电路原理图,描述电路 的功能和连接关系。

PART 05

自动布局与自动布线的挑 战与解决方案

REPORTING

WENKU DESIGN

布局的挑战与解决方案

组件密度高

随着电子设备的小型化和集成化 ,印制电路板上的组件密度越来 越高,布局难度增大。

信号完整性要求高

为了确保高速信号的完整性,需 要精确控制元件之间的距离和角 度。

布局的挑战与解决方案

对于大型和复杂电路板,规则 难以制定,且难以保证最优布

局。

基于优化算法的布局

优化目标

通过数学模型和优化算法,寻 找最优的电路元件布局方案。

常用算法

遗传算法、模拟退火算法、蚁 群算法等。

优点

能够处理大型和复杂电路板, 寻求最优解。

缺点

计算量大,时间长,需要较高 的计算资源。

混合布局算法

结合方式

结合基于规则的布局算法和基于优化算法的 布局,以获得更好的布局效果。

点连接起来。该算法简单明了,但可能无法处理复杂的布线需求。

பைடு நூலகம்

02 03

网格布线算法

该算法将电路板上的布线区域划分为一系列的网格,然后根据起点和终 点的位置以及网格的大小来决定布线的路径。该算法能够处理复杂的布 线需求,但计算量较大。

Encounter使用入门教程

Encounter使用入门教程本教程介绍一下自动布局布线工具Encounter的使用知识,开始以一个简单的十进制计数器版图的自动实现为例子,之后介绍包含block模块的复杂的版图自动实现。

在Designer Compiler使用入门教程中,笔者设计了一个十进制计数器,并经过Design Compiler对其进行综合后获得了门级综合网表文件以及约束文件,根据这两个文件,我们就可以使用SOC Encounter实现十进制计数器的物理版图设计了。

首先,我们要准备使用Encounter进行版图自动设计时所需要的数据:时序库文件:,,,物理库文件:,,门级网表文件:时序约束文件:IO位置放置文件:eset_n(top_reset),.clk(top_clk),.in_ena(top_in_ena),t(top_cnt),.carry _ena(top_carry_ena)); AD(clk),.C(top_clk));PDIDGZ PAD_RESET(.PAD(reset_n),.C(top_reset));PDIDGZ PAD_IN_ENA(.PAD(in_ena),.C(top_in_ena));(PDO02CDG PAD_CARRY_ENA(.I(top_carry_ena),.PAD(carry_ena));PDO02CDG PAD_CNT_0(.I(top_cnt[0]),.PAD(cnt[0]));PDO02CDG PAD_CNT_1(.I(top_cnt[1]),.PAD(cnt[1]));PDO02CDG PAD_CNT_2(.I(top_cnt[2]),.PAD(cnt[2]));PDO02CDG PAD_CNT_3(.I(top_cnt[3]),.PAD(cnt[3]));endmodule说明:关于PAD如何例化,首先要查看厂家提供的工艺库中的关于PAD的verilog 文件,如本例子中使用tsmc18工艺库,描述PAD的verilog文件为973g,这个文件是PAD文件的verilog描述,包括输入输出的端口等信息。

基于umc18工艺的SOC Encounter数字版图设计流程 000

基于umc18工艺的SOC Encounter数字版图设计流程V1.0 2014-02-28记录:张亮目录一、文件的准备 (3)1.1库文件的准备 (3)1.2根据设计准备所需文件 (3)二、运行软件 (3)三、版图设计流程 (4)3.1 Design_import (4)3.2 Global Net Connection (6)3.3 FloorPlan (7)3.4 Add Power Rings (8)3.5 Add Stripes (9)3.6 Placement Blockage (11)3.7 Placement (11)3.8 IO Filling (13)3.9 Special Route (SRoute) (13)3.10 Pre–CTS Optimization (15)3.11 Creat clock tree spec (16)3.12 Clock Tree Synthesis (18)3.13 Post–CTS Optimization (18)3.14 Trail Routing (20)3.15 Nano Routing (21)3.16 Add Filling (22)3.17 Post–Route Optimization (22)3.18 生成SDF 时序文件 (24)3.19 Verify connectivity (24)3.20 Verify Geometry (25)3.21 Export Files (26)四、DRC校验 (27)4.1库文件的准备 (27)4.2 根据设计准备所需文件 (28)4.3 修改库文件路径 (28)4.4 启动calibre (29)4.5 encourage 打开查看报告 (29)五、LVS校验 (31)5.1库文件的准备 (31)5.2 根据设计准备所需文件 (32)5.3 生成.spi文件 (32)5.4 启动LVS (32)5.5 查看报告 (32)一、文件的准备1.1库文件的准备对于SOC Encounter而言,后端设计所需的主要有由Foundry厂所提供的标准单元和I/O Pad的库文件,它包括物理库、时序库,分别以.lef、.tlf(或者.lib)的形式给出,其中I/O Pad 的相关库文件只有在做有Pad的版图时才需要。

使用Encounter进行电路布局布线

使用Encounter进行布局布线——By WangJZ magic14@2011-4-20 本文以一个简单设计为例,介绍Cadence公司的自动布局布线工具Encounter的基本使用流程。

下面是具体步骤:工程目录为存放在用户文件夹下的EDI_phy文件夹,文件夹中包括使用DesignCompiler对设计进行综合后输出的门级网表文件tt.v和约束文件constrain.sdc。

设置环境变量,进入工程目录,用encounter命令启动软件,如下图所示:软件启动后,encounter的图形界面如下图所示:导入设计文件,如下所示。

其他选项可暂时不填,保持默认设置,点击确认按钮。

成功导入设计文件后,Encounter视图如下所示:定义设计的尺寸、长宽比等信息,如下所示:完成后如下图所示,Core区和IO边缘有10um的距离。

添加全局连线,此处主要是电源和地的全局连线,分别把VDD的pin、net和高电平连接到全局连线VDD,把VSS的pin、net和低电平连接到全局连线VSS,如下所示:添加电源环,如下所示:填入电源环的宽度、距离、使用的金属层等信息,点击确认后,电源环添加到Core区和IO 边缘之间的空间,如下所示:添加core区中标准单元的电源连线,如下所示:添加电源连线后,视图如下所示:放置标准单元,然后切换到版图视图,可看到标准单元放置后的效果,如下所示:接着进行时钟树综合,可使用手动编写的时钟树配置文件或者用软件自动生配置文件进行时钟树综合。

此处采用软件自动生成配置文件的方式,如下所示:时钟树综合的同时会进行版图的初始布线。

完成时钟树综合后,进行版图的详细布线,如下所示:详细布线采用默认设置即可,完成详细布线后效果图如下:如果只是进行Encounter的学习,到此处即可保存并输出结果。

如果是要进行实际的流片生产,还需对各层进行填充,包括标准单元填充和各个金属层的填充,以保证满足生产所需的密度。

基于Encounter的自动布局布线

2、floorplan

Core规划 电源环 电源条

Core规划

1、点击Floorplanspecify floorplan 2、core utilization 是芯片 利用率,即标准单 元面积和core面积 的比率,一般默认 为70% 3、core to boundary 设置边 界,留给电源环的

Place 效果图

4、时钟树综合

5、route

Srote 标准单元和macro与电源网络的连接,这里主 要是标准单元的连接 Nanoroute 全局布线,工具会根据netlist的连接关系,进 行全局布线。

Sroute

点击OK,会得到下面的图:每行的row都有线连接到外面的电源环

调出Encounter

自动布局布线软件

芯片的工作时钟频率,时钟歪斜、抖动 输入输出延时以及输出负载

浙大微电子

35/74

布局流程—时序设置

在设计窗口中选择Timing-> Timing Setup, 在弹出的窗口中进行用于静态时序分析的选项 设置。

0.1

浙大微电子

36/74

布局流程—布局选项设置

在设计窗口中选择 InPlace>Placement Common Options, 在弹出菜单的 “Optimiaztion Mode”一栏中选择 “Congestion”和 “Timing”,表示 选用时序和拥塞共 同驱动的布局。其 他选项可以缺省。

浙大微电子

13/74

创建设计库

Technology File: /home/smic/smic_40/SCC40NLL_HS_RVT_V0p1a/astro/tf/scc40nll_hs_7l m_1tm.tf

浙大微电子

14/74

打开设计库

浙大微电子

15/74

设计文件导入1/3

任意名 逻辑综合后得 到的网表的顶 层模块名

浙大微电子

37/74

布局流程—预布局及时序分析

预布局阶段主要是对高扇出网线进行优化:

1.在设计窗口中选择InPlace->Auto Place, 2.在弹出窗口的“Stage”一栏选择“Pre-place”,并 点击菜单中的“Detail Options”按钮, 3.在“Pre-Place optimization”一栏中选择“Cell Down Size”,其他选项缺省

;1.1V digital core power/ground 注意空格 insertPad "VDD" "PVDD1RN" "VDD" "VDD" insertPad "VSS" "PVSS1RN" "VSS" "VSS" ;3.3V digital IO power/ground dbCreateCellInst (geGetEditCell) "" "PVDD2RN" "VDD_IO" "0" "No" '(0 0) "fsk0323" dbCreateCellInst (geGetEditCell) "" "PVSS2RN" "VSS_IO" "0" "No" '(0 0) "fsk0323" ;Corner cell dbCreateCellInst (geGetEditCell) "" "PCORNERRN" "CORNER1" "0" "No" '(0 0) "fsk0323" dbCreateCellInst (geGetEditCell) "" "PCORNERRN" "CORNER2" "0" "No" '(0 0) "fsk0323" dbCreateCellInst (geGetEditCell) "" "PCORNERRN" "CORNER3" "0" "No" '(0 0) "fsk0323" dbCreateCellInst (geGetEditCell) "" "PCORNERRN" "CORNER4" "0" "No" '(0 0) "fsk0323" tdfPurgePadConstr pad "CORNER1" "Bottom" insertPad 使用方法: pad "CORNER2" "Right" insertPad netName padCellName padName connectPin pad "CORNER3" "Top" pad "CORNER4" "Left" dbCreateCellInst 使用方法: pad "VDD_IO" "left" 1 pad "VSS_IO" "left" 2 dbCreateCellInst cellId childLibName chlidCellName pad "data_in_block" "top" 1 pad "fsk_out_block" "top" 2 chilidInstName rotationStr mirrorStr Points topCellName pad "VDD" "right" 1 pad "VSS" "right" 2 pad "clk_block" "bottom" 2 pad "en_block" "bottom" 1

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

Nanoroute

route效果图

6、verify

检查open 检查unconnect pin 检查antenna

6、时序检查 (Timing check)

Timing –timing analysis

8、数据导出 (stream out)

电源环

1、点ห้องสมุดไป่ตู้Floorplanconnect global nets 2、主要是将VDD, VSS和标准单元的 电源和地进行软连 接

电源环

填入VDD VSS

选择金属层

电源环的宽带和间距

电 源 环 效 果 图

电源条

3、place

Place就是将netlist中的单元放置到 encounter的row中去,便于后面的route

基于Encounter软件的自动布局 布线

2011-10-18

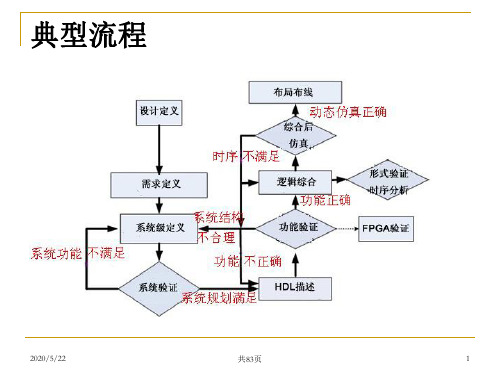

Encounter布局布线主要流程

1、设计输入 (Design import) 2、布局 (Floorplan) 3、放置标准单元 (Place) 4、时钟树综合 (Clock tree synthesis) 5、布线 (Route) 6、验证 (Verify) 7、时序检查 (Timing check) 8、数据导出 (stream out)

调出Encounter

终端输入:encounter

1、设计输入

点击Design-Design import 打开输入设计窗口

输入窗口

另外在advanced栏的Power相应位置填上VDD,和VSS。如下图,设置完以后,记 得把设置的配置文件做一个save以便于下次使用

综合后网表

顶层名 时序库文件 物理库文件 约束文件(DC综合后导出的)

Place 效果图

4、时钟树综合

5、route

Srote 标准单元和macro与电源网络的连接,这里主 要是标准单元的连接 Nanoroute 全局布线,工具会根据netlist的连接关系,进 行全局布线。

Sroute

点击OK,会得到下面的图:每行的row都有线连接到外面的电源环

2、floorplan

Core规划 电源环 电源条

Core规划

1、点击Floorplanspecify floorplan 2、core utilization 是芯片 利用率,即标准单 元面积和core面积 的比率,一般默认 为70% 3、core to boundary 设置边 界,留给电源环的