自动布局布线(SiliconEnsemble)

芯片设计中的自动化布局布线技术有哪些

芯片设计中的自动化布局布线技术有哪些在当今的科技领域,芯片作为各种电子设备的核心组件,其性能和功能的优劣直接决定了设备的整体表现。

而在芯片设计过程中,自动化布局布线技术扮演着至关重要的角色。

它不仅能够显著提高设计效率,还能优化芯片的性能、降低功耗、减小芯片面积等。

那么,芯片设计中的自动化布局布线技术究竟有哪些呢?首先,我们来了解一下全局布线技术。

全局布线是在芯片设计的早期阶段,对整个芯片的布线资源进行初步规划和分配。

它需要考虑芯片的各个模块之间的连接关系,以及布线资源的可用性和限制。

通过合理的全局布线,可以为后续的详细布线提供一个良好的基础,减少布线冲突和拥塞的可能性。

在全局布线中,常用的算法包括基于贪心策略的算法和基于启发式搜索的算法。

贪心策略算法会在每一步选择当前看起来最优的布线方案,但可能会陷入局部最优解。

而启发式搜索算法则会在搜索过程中综合考虑多种因素,试图找到更全局的最优解。

接下来是详细布线技术。

详细布线是在全局布线的基础上,对每一条信号线进行精确的路径规划。

这一过程需要处理大量的细节,包括线宽、间距、过孔的使用等。

为了实现高效的详细布线,通常会采用迷宫布线算法、线探索算法等。

迷宫布线算法通过在布线区域内逐步探索可行的路径,直到找到目标点。

这种算法相对简单,但在复杂的布线环境中可能效率较低。

线探索算法则通过对布线空间进行有针对性的搜索,能够更快地找到合适的布线路径。

除了上述两种基本的布线技术,还有一些优化技术用于进一步提升布线的质量。

例如,时序驱动的布线技术会根据芯片的时序要求,优先为关键信号规划布线路径,以确保芯片能够满足时序约束。

功耗优化的布线技术则关注于降低布线过程中的功耗。

这可以通过选择合适的布线材料、优化线宽和长度等方式来实现。

比如,使用低电阻的金属材料可以减少电流在布线上的损耗,从而降低功耗。

另外,面积优化的布线技术致力于减小布线所占用的芯片面积。

通过合理的布线规划和资源利用,可以在满足性能要求的前提下,尽量压缩布线区域,为其他电路模块腾出更多的空间。

《自动布局布线》课件

探索自动布局布线的奇妙世界,帮助你提高电路板或芯片的性能,节省时间, 减少错误。

什么是自动布局布线?

自动布局布线是一种方法,用于自动为电路板或芯片设计最佳电线布局。

为什么需要自动布局布线?

手动布线耗时且容易出错,而自动布局布线可以节省时间、减少错误,并提 高电路板或芯片的性能。

2 准确性

避免人为错误,提高电路板或芯片的性能。

4 高效

节省时间,快速完成布线任务。

自动布局布线的挑战

算法复杂度高

处理大规模网络布线的算法复杂度较高。

异常情况处理

对输入异常情况的处理较困难,需要更精细的算法设计。

CPU处理限制

处理大规模网络布线时,仅依靠CPU很难满足要求。

结论

自动布局布线能够帮助我们节省时间、减少错误,并提高电路板或芯片的性 能。

自动布局布线的流程,为后续布线准备。

2

网络构建

将电路元件在网格中建立连接,形成网络。

3

优化网络

对网络进行优化,使其满足性能要求。

4

生成布线

根据优化后的网络,生成最佳的电线布局。

自动布局布线的优势

1 自动化

提高效率,减少人工工作量。

3 可重复性

保持一致的布线质量。

尽管自动布局布线还面临一些挑战,但随着技术发展,我们可以期待它在未 来发挥更大的作用。

ASIC设计cadence自动布局布线工具_图文(精)

本节将使用综合工具(Design Compiler 对一个 8位全加器逻辑综合,并产生一个门级网表;利用该网表使用自动布局布线工具(Silicon Ensemble 生成一个全加器的版图。

首先输入 8位全加器 verilog 代码:module adder8(Cout,S,A,Cin;output Cout;output [7:0]S;input [7:0]A;input [7:0]B;input Cin;reg [8:0]SUM;reg [7:0]S;reg Cout;wire [7:0]A,B;always @(Aor B or CinbeginSUM [8:0]=A+B+Cin;S =SUM [7:0];Cout =SUM [8];endendmodule打开综合工具 DC (psyn_gui&File->Read..读入代码File->Setup..设置 3个相关工艺库将带红色 *号的 3个库设置如下图 Design->CompileDesign.. 编译Schematic->NewDesign Schematic View..可以看到综合后的顶层结构通过双击 C1模块还可以看到全加器的门级结构为了后面自动布局布线的需要, 这里我们要将这个综合结果保存为 adder8_nl.v 门级网表。

在 psyn_gui-xg-t>后输入如下命令下面进行自动布局布线 (一下有路径出现的地方要特别注意打开 Silicon Ensemble (sedsm&File->Import->LEF… 导入库的转换格式注意此文件的路径!File->Import->Verilog… 导入工艺库(此库为 verilog 描述的标准单元,包含各种延时信息这里去掉后面的!继续 File->Import->Verilog… 导入网表 adder8_nl.v(此处要先删掉第一个工艺库这里要加上顶层模块名 adder8Floorplan->InitializeFloorplan…准备工作完成开始布局布线点击 Variables 将里面的 PLAN.LOWERLEFT.ORIGIN 由 FALSE 改为 TUREEdit ->Add ->Row… Area 的区域可以直接点击 Area 并在图上拖拽,并使其大小与芯片核一致File->Saveas… 保存为 fplanRoute->PlanPower… 设置电源环在 Plan Power 窗口中点击 AddRings…Place->Ios…放置输入输出Place->Cells…放置单元Place->FillerCells->AddCells…Route->RoutePower->FollowPins… 添加管脚(金属线宽设为 1.8 Route->Wroute…布线View->DisplayOptions… 检查管脚名设置 Pin 为 ONFile->Export->DEF… 命名为adder8_wrouted.def打开 icfb &再导入 DEF文件之前要确保你有如下图中的一些库文件File->Import->DEF…Enter “ tutorial ” for Library Name, “ adder8” for Cell Name, and “ autoRouted ”for View Name.打开 View 中的autoRoutedDesign->Save..Tool->Layout..将提取图转换为版图,这里需要改变几个参数 Edit->Search..点击Add Criteria然后做如下图的几个改动Apply Replace AllDesign->SaveAs..现在就可以打开 layout 了DRC… 熟悉吧! !。

ic笔试题目汇总100

数字IC设计工程师笔试面试经典100题1:什么是同步逻辑和异步逻辑?同步逻辑是时钟之间有固定的因果关系。

异步逻辑是各时钟之间没有固定的因果关系。

同步时序逻辑电路的特点:各触发器的时钟端全部连接在一起,并接在系统时钟端,只有当时钟脉冲到来时,电路的状态才能改变。

改变后的状态将一直保持到下一个时钟脉冲的到来,此时无论外部输入 x 有无变化,状态表中的每个状态都是稳定的。

异步时序逻辑电路的特点:电路中除可以使用带时钟的触发器外,还可以使用不带时钟的触发器和延迟元件作为存储元件,电路中没有统一的时钟,电路状态的改变由外部输入的变化直接引起。

2:同步电路和异步电路的区别:同步电路:存储电路中所有触发器的时钟输入端都接同一个时钟脉冲源,因而所有触发器的状态的变化都与所加的时钟脉冲信号同步。

异步电路:电路没有统一的时钟,有些触发器的时钟输入端与时钟脉冲源相连,只有这些触发器的状态变化与时钟脉冲同步,而其他的触发器的状态变化不与时钟脉冲同步。

3:时序设计的实质:时序设计的实质就是满足每一个触发器的建立/保持时间的要求。

4:建立时间与保持时间的概念?建立时间:触发器在时钟上升沿到来之前,其数据输入端的数据必须保持不变的最小时间。

保持时间:触发器在时钟上升沿到来之后,其数据输入端的数据必须保持不变的最小时间。

5:为什么触发器要满足建立时间和保持时间?因为触发器内部数据的形成是需要一定的时间的,如果不满足建立和保持时间,触发器将进入亚稳态,进入亚稳态后触发器的输出将不稳定,在0和1之间变化,这时需要经过一个恢复时间,其输出才能稳定,但稳定后的值并不一定是你的输入值。

这就是为什么要用两级触发器来同步异步输入信号。

这样做可以防止由于异步输入信号对于本级时钟可能不满足建立保持时间而使本级触发器产生的亚稳态传播到后面逻辑中,导致亚稳态的传播。

(比较容易理解的方式)换个方式理解:需要建立时间是因为触发器的D端像一个锁存器在接受数据,为了稳定的设置前级门的状态需要一段稳定时间;需要保持时间是因为在时钟沿到来之后,触发器要通过反馈来锁存状态,从后级门传到前级门需要时间。

基于Silicon Ensemble的布局布线技术研究

NO 6 . De . 2 0 c ,07

微

处

理

机

第6 期

20 0 7年 l 2月

MI 0PR ES 0IS CR 0C S : L

基 于 Sl o ne be的布局 布线 技 术 研究 icnE sm l i

张 斌 蒋 晶鑫 周 刚 , ,

Re e r h o a ig a d Ro t g Te h i u s d o l o s mbe s a c n Plcn n u i c nq e Ba e n Si n En e l n i c

Z HANG n ,I G ig—xn , HO n Bi JAN Jn i Z U Ga g

—

n ot a d b t m u C de in。 o p I sg

_

Ke r y wo ds: a e& r u i g; o k Tr e; c p Plc o tn Clc e S r t i

l 引 言

随着大规模集成电路的发展, 人们对芯片的集 成 度及 成 品率提 出 了新 的要求 。深亚 微米技 术 的引

(. 1 中国 电子科 技 集 团公 司第 四十 七研 究所 , 阳 103 ;. 阳工业大 学 , 阳 102 ) 沈 1022 沈 沈 103

摘 要 : 绍 了 C d ne公 司的 Sl o n e be布局布 线工具 , 介 ae c icnE sm l i 以及 S E布线 器所用 到 的相 关

入 , 连线延时 成 为 电路设 计 过 程 中决 定 性 的 因 使得 素 。在 芯片设计 时将 不 得不 考 虑 诸如 速 度 、 积及 面 时序 收敛 等问题 。 目前有 多种 布线工具 可 以解 决这

IC设计中所使用的EDA工具

IC设计中所使用的EDA工具IC设计中EDA工具的日臻完善已经使工程师完全摆脱了原先手工操作的蒙昧期。

IC设计向来就是EDA工具和人脑的结合。

随着IC不断向高集成度、高速度、低功耗、高性能发展,没有高可靠性的计算机辅助设计手段,完成设计是不可能的。

IC设计的EDA工具真正起步于80年代,1983年诞生了第一台工作站平台apollo,20年的发展,从硬件描述语言(或是图形输入工具)到逻辑仿真工具(LOGIC SIMULICATIO N),从逻辑综合(Logic Synthesis)到自动布局布线(Auto Plane & Route)系统;从物理规则检测(DRC & ERC)和参数提取(LVS)到芯片的最终测试,现代EDA工具几乎涵盖了I C设计的方方面面。

提到IC设计的EDA工具就不能不说Cadence公司,随着compass的倒闭,它成为这个行业名副其实的“老大” Cadence提供了IC Design中所涉及的几乎所有工具;但它的工具和它的名气一样的值钱!现代IC技术的迅猛发展在EDA软件厂家中掀起并购、重组热潮。

除Cadence公司以外,比较有名的公司包括Mentor,Avanti,Synopsys和INVOEDA,M entor和Cadence一样是一个在设计的各个层次都有开发工具的公司,而Avanti因其模拟仿真工具HSPICE出名,Synopsys则因为逻辑综合方面的成就而为市场认可。

下面我们根据设计的不同阶段和层次来谈谈这些工具:一、输入工具(Design Input)对自顶而下的(Top-Down)设计方法,往往首先使用VHDL或是VERILOG HDL来完成器件的功能描述,代表性的语言输入工具有SUMMIT公司的VISUAL HDL和Mentor公司的RENIOR等。

虽然很多的厂家(多为FPGA厂商)都提供自己专用的硬件描述语言输入,如ALTRA公司的AHDL,但所有的公司都提供了对作为IEEE标准的VHDL,VERIL OGHDL的支持。

IC设计流程

一般的IC设计流程可以分为两大类:全定制和半定制,这里我换一种方式来说明。

1.1 从RTL到GDSⅡ的设计流程:这个可以理解成半定制的设计流程,一般用来设计数字电路。

整个流程如下(左侧为流程,右侧为用到的相应EDA工具):一个完整的半定制设计流程应该是:RTL代码输入、功能仿真、逻辑综合、形式验证、时序/功耗/噪声分析,布局布线(物理综合)、版图验证。

至于你说的FPGA设计,开发起来更加简单,结合第三方软件(像Modelsim 和Synplify Pro),两大FPGA厂商Altera和Xilinx自带的QuartusⅡ和ISE开发平台完全可以应付与之有关的开发。

整个完整的流程可以分为前端和后端两部分,前端的流程图如下:前端的主要任务是将HDL语言描述的电路进行仿真验证、综合和时序分析,最后转换成基于工艺库的门级网表。

后端的流程图如下,这也就是从netlist到GDSⅡ的设计流程:后端的主要任务是:(1)将netlist实现成版图(自动布局布线APR)(2)证明所实现的版图满足时序要求、符合设计规则(DRC)、layout与netlist一致(LVS)。

(3)提取版图的延时信息(RC Extract),供前端做post-layout 仿真。

1.2从Schematic到GDSⅡ的设计流程:这个可以理解成全定制的设计流程,一般用于设计模拟电路和数模混合电路。

整个流程如下(左侧为流程,右侧为用到的相应EDA工具):一个完整的全定制设计流程应该是:电路图输入、电路仿真、版图设计、版图验证(DRC和LVS)、寄生参数提取、后仿真、流片。

IC设计流程和设计方法集成电路设计流程. 集成电路设计方法. 数字集成电路设计流程. 模拟集成电路设计流程. 混合信号集成电路设计流程. SoC芯片设计流程State Key Lab of ASIC & Systems, Fudan University集成电路设计流程. 集成电路设计方法. 数字集成电路设计流程. 模拟集成电路设计流程. 混合信号集成电路设计流程. SoC芯片设计流程State Key Lab of ASIC & Systems, Fudan University正向设计与反向设计State Key Lab of ASIC & Systems, Fudan University自顶向下和自底向上设计State Key Lab of ASIC & Systems, Fudan UniversityTop-Down设计–Top-Down流程在EDA工具支持下逐步成为IC主要的设计方法–从确定电路系统的性能指标开始,自系统级、寄存器传输级、逻辑级直到物理级逐级细化并逐级验证其功能和性能State Key Lab of ASIC & Systems, Fudan UniversityTop-Down设计关键技术. 需要开发系统级模型及建立模型库,这些行为模型与实现工艺无关,仅用于系统级和RTL级模拟。

Cadence和Hspice详细介绍

Cadence 和Hspice 详细介绍

本文为大家带来两款EDA 软件:Cadence 和Hspice 的介绍。

Cadence 介绍

Cadence 是一个大型的EDA 软件,它几乎可以完成电子设计的方方面面,包括ASIC 设计、FPGA 设计和PCB 板设计。

Cadence 在仿真、电路图设计、自动布局布线、版图设计及验证等方面有着绝对的优势。

Cadence

包含的工具较多几乎包括了EDA 设计的方方面面。

Cadence 的底层软件

Cadence 的底层软件有下面这些:

逻辑设计规划器

这是用于设计早期的规划工具。

其主要用途是延时预测、生成供综合工具使用的线路负载模型。

这个工具是用来在物理设计的早期象逻辑设计者提供

设计的物理信息。

全定制芯片的设计与自动布局布线研究

全定制芯片的设计与自动布局布线研究全定制芯片的设计与自动布局布线研究随着电子技术的快速发展,芯片设计与制造技术也在不断进步。

全定制芯片是一种根据特定需求进行设计和制造的芯片,相比于通用芯片,全定制芯片具有更高的性能和更低的功耗。

而在全定制芯片的设计过程中,自动布局布线技术起到了至关重要的作用。

全定制芯片的设计与自动布局布线研究是为了解决芯片设计过程中的布局布线问题。

布局布线是指将芯片上的各个功能单元进行合理的布置,并通过导线进行连接。

合理的布局布线可以提高芯片的性能、降低功耗,并且减少芯片的面积。

在全定制芯片的设计中,自动布局布线技术起到了关键的作用。

自动布局布线技术可以根据设计规则和约束条件,自动确定各个功能单元的位置和导线的路径,以达到最佳的性能和功耗。

自动布局布线技术可以大大提高芯片设计的效率和准确性。

在全定制芯片的自动布局布线研究中,有几个关键的问题需要解决。

首先是如何确定各个功能单元的位置。

功能单元的位置决定了芯片的布局,直接影响到芯片的性能和功耗。

在确定功能单元位置时,需要考虑到各个功能单元之间的距离、相互之间的约束条件等因素。

其次是如何确定导线的路径。

导线的路径决定了芯片各个功能单元之间的连接方式。

在确定导线路径时,需要考虑到导线的长度、导线之间的相互干扰等因素。

同时,导线的路径还需要满足一定的设计规则,比如导线的宽度、间距等。

最后是如何优化布局布线的性能和功耗。

布局布线的性能和功耗可以通过优化功能单元的位置和导线的路径来实现。

通过合理的布局布线,可以减少信号传输的延迟、降低功耗,并提高芯片的可靠性。

为了解决上述问题,研究人员通过建立数学模型和算法来进行自动布局布线的研究。

数学模型可以描述芯片的布局布线问题,并通过优化算法来求解最优解。

通过不断改进和优化算法,可以提高自动布局布线的效率和准确性。

总之,全定制芯片的设计与自动布局布线研究是一个复杂而关键的领域。

通过自动布局布线技术,可以提高芯片设计的效率和准确性,实现更高性能和更低功耗的芯片设计。

自动布局布线

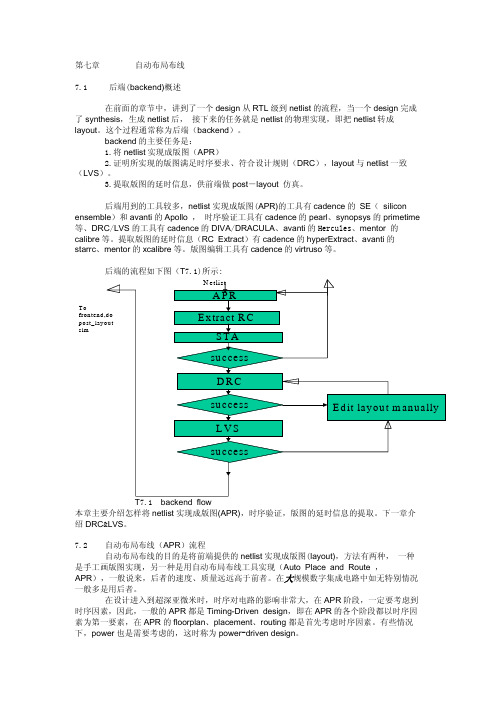

第七章 自动布局布线7.1 后端(backend)概述在前面的章节中,讲到了一个design从RTL级到netlist的流程,当一个design完成了synthesis,生成netlist后, 接下来的任务就是netlist的物理实现,即把netlist转成layout。

这个过程通常称为后端(backend)。

backend的主要任务是:1.将netlist实现成版图(APR)2.证明所实现的版图满足时序要求、符合设计规则(DRC),layout与netlist一致(LVS)。

3.提取版图的延时信息,供前端做post-layout 仿真。

后端用到的工具较多,netlist实现成版图(APR)的工具有cadence的 SE( silicon ensemble)和avanti的Apollo , 时序验证工具有cadence的pearl、synopsys的primetime 等、DRC/LVS的工具有cadence的DIVA/DRACULA、avanti的Hercules、mentor 的 calibre等。

提取版图的延时信息(RC Extract)有cadence的hyperExtract、avanti的starrc、mentor的xcalibre等。

版图编辑工具有cadence的virtruso等。

后端的流程如下图(T7.1)所示:T opost_laysim本章主要介绍怎样将netlist实现成版图(APR),时序验证,版图的延时信息的提取。

下一章介绍DRC&LVS。

7.2 自动布局布线(APR)流程自动布局布线的目的是将前端提供的netlist实现成版图(layout),方法有两种, 一种是手工画版图实现,另一种是用自动布局布线工具实现(Auto Place and Route , APR),一般说来,后者的速度、质量远远高于前者。

在大规模数字集成电路中如无特别情况一般多是用后者。

在设计进入到超深亚微米时,时序对电路的影响非常大,在APR阶段,一定要考虑到时序因素,因此,一般的APR都是Timing-Driven design,即在APR的各个阶段都以时序因素为第一要素,在APR的floorplan、placement、routing都是首先考虑时序因素。

Cadence软件介绍

Cadence软件介绍Cadence 是一个大型的EDA 软件,它几乎可以完成电子设计的方方面面,包括ASIC 设计、FPGA 设计和PCB 板设计。

Cadence 在仿真、电路图设计、自动布局布线、版图设计及验证等方面有着绝对的优势。

Cadence 包含的工具较多几乎包括了EDA 设计的方方面面。

下面主要介绍其产品线的范围。

1、板级电路设计系统包括原理图输入、生成、模拟数字/混合电路仿真,fpga设计,pcb 编辑和自动布局布线mcm电路设计、高速pcb版图的设计仿真等等。

包括:A、Concept HDL原理图设计输入工具, 有for NT和for Unix的产品。

B、Check Plus HDL原理图设计规则检查工具。

(NT & Unix)D、Allegro Expert专家级PCB版图编辑工具 (NT & Unix)E、SPECTRA Expert AutoRouter 专家级pcb自动布线工具F、SigNoise信噪分析工具G、EMControl 电磁兼容性检查工具H、Synplify FPGA / CPLD综合工具I、HDL Analyst HDL分析器J、Advanced Package Designer先进的MCM封装设计工具2、Alta系统级无线设计这部分包括:A、SPW (Cierto Signal Processing Work System)信号处理系统。

可以说,spw包括了matlab的很多功能,连demo都有点象。

它是面向电子系统的模块化设计、仿真和实现的环境。

它的通常的应用领域包括无线和有线载波通信、多媒体和网络设备。

在进行算法设计、滤波器设计、c Code生成、软/硬件结构联合设计和硬件综合的理想环境。

它里面非常有意思的就是信号计算器。

B、HDS (Hardware Design System)硬件系统设计系统它现在是SPW的集成组件之一。

包括仿真、库和分析扩展部分。

集成电路设计中的自动布局布线方法研究

集成电路设计中的自动布局布线方法研究在集成电路的设计过程中,自动布局布线是必不可少的一步。

它的目标是将电路中的各个组件合理地布局在芯片的表面,并通过导线将它们连接起来,以实现电路的功能。

自动布局布线方法的研究可以提高电路的性能、减小面积、降低功耗,对于集成电路的设计具有重要的意义。

自动布局布线方法的研究主要包括两个方面,即自动布局和自动布线。

自动布局是指在给定的芯片面积内,将电路中的各个组件按照一定的规则自动布置在芯片上,使得它们之间的距离适当,并且不产生电路冲突。

自动布线是指根据布局结果,自动地在芯片的表面上生成导线网络,使得电路中的各个组件之间能够正确地互连。

在自动布局的研究中,通常采用的方法是通过建立电路的等效模型,将布局问题转化为数学优化问题。

具体来说,可以使用基于禁忌搜索、模拟退火等启发式算法来求解布局问题。

另外,还可以利用迁移学习、强化学习等机器学习方法,通过训练模型来优化布局结果。

在自动布线的研究中,常常使用的方法是通过建立网络流模型,将布线问题转化为最小费用流、最大流等经典问题。

然后,可以采用广度优先搜索、深度优先搜索等算法来求解布线问题。

此外,还可以使用并行计算、多目标优化等技术,提高布线的效率和质量。

自动布局布线方法的研究不仅需要考虑电路的性能,还需满足芯片的制造工艺要求。

因此,在布局布线的过程中,需要考虑到电路的延迟、功耗、面积等指标,并且要遵守芯片制造的规则。

例如,可以利用线性规划等数学方法来求解布局布线问题中的多目标优化问题,以平衡不同指标的要求。

自动布局布线方法的研究还要考虑到不同工艺、不同电路结构之间的差异性。

因此,对于不同类型的电路,需要采用不同的布局布线方法。

例如,对于数字电路,可以采用网格化布局方法,将电路中的组件和导线都放置在网格交叉点上。

而对于模拟电路,可以采用层次化布局方法,将电路中的组件和导线分别放置在不同的层次上。

总的来说,自动布局布线方法的研究对于集成电路的设计具有重要的意义。

芯片设计中的自动化布局布线技术有哪些创新

芯片设计中的自动化布局布线技术有哪些创新在当今科技飞速发展的时代,芯片作为电子设备的核心组件,其性能和功能的提升对于推动整个电子行业的进步具有至关重要的意义。

而芯片设计中的自动化布局布线技术则是实现芯片高性能、低功耗和小尺寸的关键环节之一。

随着芯片制造工艺的不断进步和芯片复杂度的日益增加,自动化布局布线技术也在不断创新和发展,为芯片设计带来了新的机遇和挑战。

一、多层布线技术多层布线是自动化布局布线技术中的一项重要创新。

在过去,芯片布线通常只在一到两层金属层上进行,这限制了布线的灵活性和可扩展性。

而现代芯片设计中,多层布线技术已经成为主流,通过在多个金属层上进行布线,可以有效地减少布线长度、降低电阻和电容,从而提高芯片的性能和速度。

多层布线技术的实现需要依靠先进的布线算法和工具。

这些算法和工具能够根据芯片的功能和性能要求,自动规划布线的路径和层次,同时考虑信号完整性、电源完整性和电磁兼容性等因素。

通过合理地分配布线资源,多层布线技术可以在有限的芯片面积内实现更多的电路连接,从而提高芯片的集成度和功能。

二、全局布线与局部布线的协同优化在芯片设计中,全局布线和局部布线是两个不同但又相互关联的环节。

全局布线主要负责确定芯片中各个模块之间的连接关系和大致的布线路径,而局部布线则负责在模块内部进行详细的布线规划。

传统的自动化布局布线技术通常将全局布线和局部布线分开处理,导致在两个环节之间可能出现衔接不畅、资源分配不合理等问题。

为了解决这些问题,创新的自动化布局布线技术采用了全局布线与局部布线的协同优化方法。

在布线过程中,全局布线和局部布线相互反馈和调整,以实现整体布线性能的最优。

例如,全局布线可以根据局部布线的资源需求和约束条件,对布线路径进行优化和调整;局部布线则可以根据全局布线的结果,合理安排模块内部的布线细节,从而提高布线的效率和质量。

三、基于物理约束的布线技术在芯片设计中,物理约束是必须要考虑的重要因素,包括芯片的面积、功耗、散热等。

芯片设计中的自动布局布线策略研究

芯片设计中的自动布局布线策略研究在芯片设计中,自动布局布线策略是一个关键的环节,它涉及到芯片性能、功耗和可靠性等多个方面。

在本文中,我们将探讨芯片设计中的自动布局布线策略,并介绍一些相关的研究进展。

自动布局布线是指通过计算机算法自动地将电路元件进行位置布置以及确定它们之间的连线路径。

这是一个复杂而耗时的任务,因为它需要考虑到各种电路元件间的限制条件、信号传输的延迟等因素。

一种常用的自动布局布线策略是基于模块化的方法。

该方法将电路划分为多个模块,并对每个模块进行布局和布线。

这样做的好处是可以提高算法的可扩展性,使设计师可以更容易地处理复杂的芯片设计。

除了基于模块化的方法,还有一种常用的自动布局布线策略是基于图像处理的方法。

这种方法利用图像处理的技术,将电路定义为一个图形,并通过图形算法对其进行布局和布线。

与模块化方法相比,图像处理方法可以更好地处理各种电路拓扑结构的限制条件。

在自动布局布线策略的研究中,约束驱动布线是一个重要的方向。

约束驱动布线是指根据用户定义的一系列约束条件来进行布局和布线的方法。

这些约束条件可以包括布局区域的限制、功耗和时序等方面的要求。

通过约束驱动布线,设计师可以更加灵活地控制芯片的性能和功耗等因素。

除了上述的自动布局布线策略,在芯片设计中还有一些其他的研究方向。

例如,自适应布局布线是一种根据电路特性和输入约束条件自动调整布局和布线的方法。

这种方法可以在不同的设计场景下灵活地调整布局,以获得更好的性能和功耗平衡。

此外,还有一些研究致力于优化布局和布线的算法。

这些算法可以通过数学优化和机器学习等方法,自动地对布局和布线进行优化,以达到更好的芯片性能和功耗等指标。

在实际应用中,自动布局布线策略在芯片设计中具有重要的意义。

它可以大大提高设计效率,节省设计时间和成本。

另外,在新一代芯片设计中,由于电路规模的不断增大和复杂性的增加,自动布局布线策略将扮演更为重要的角色。

综上所述,自动布局布线策略在芯片设计中起着至关重要的作用。

Cadence 使用参考手册

Cadence 使用参考手册邓海飞微电子学研究所设计室2000年7月目录概述 (1)1.1 Cadence概述 (1)1.2 ASIC设计流程 (1)第一章Cadence 使用基础 (5)2.1 Cadence 软件的环境设置 (5)2.2 Cadence软件的启动方法 (10)2.3库文件的管理 (12)2.4文件格式的转化 (14)2.5 怎样使用在线帮助 (14)2.6 本手册的组成 (15)第二章Verilog-XL 的介绍 (16)3. 1 环境设置 (16)3.2 Verilog-XL的启动 (16)3.3 Verilog-XL的界面 (18)3.4 Verilog-XL的使用示例 (19)3.5 Verilog-XL的有关帮助文件 (20)第四章电路图设计及电路模拟 (22)4.1 电路图设计工具Composer (22)4.1.1 设置 (22)4.1.2 启动 (23)4.1.3 用户界面及使用方法 (23)4.1.4 使用示例 (25)4.1.5 相关在线帮助文档 (25)4.2 电路模拟工具Analog Artist (25)4.2.1 设置 (25)4.2.2 启动 (26)4.2.3 用户界面及使用方法 (26)4.2.5 相关在线帮助文档 (26)第五章自动布局布线 (28)5.1 Cadence中的自动布局布线流程 (28)5.2 用AutoAbgen进行自动布局布线库设计 (29)第六章版图设计及其验证 (31)6.1 版图设计大师Virtuoso Layout Editor (31)6.1.1 设置 (31)6.1.2 启动 (31)6.1.3 用户界面及使用方法 (31)6.1.4 使用示例 (32)6.1.5 相关在线帮助文档 (32)6.2 版图验证工具Dracula (32)6.2.1 Dracula使用介绍 (32)6.2.2 相关在线帮助文档 (33)第七章skill语言程序设计.................... 错误!未定义书签。

VLSI自动布局布线(APR)设计

VLSI自动布局布线(APR)设计实验教材大规模集成电路设计教学实验室前言在电子技术高速发展的今天,电子产品的应用领域日益广泛,小巧灵活的集成电路芯片以其体积小、成本低等特点普遍受到商家和消费者的宠爱,而这也给芯片设计者提出了更高的要求。

客户们希望IC芯片的功耗更低、速度更快、体积更小、性能更稳定、价格更便宜,更重要的是开发周期更短。

在微电子工艺技术不断推陈出新的同时,IC芯片的复杂程度也随之增加。

目前一些先进的处理器芯片已达到了8层金属立体布线,最小线宽也达到了深亚微米以下,可以说如果用手工布线的方式完成这么复杂的芯片几乎是不可能的。

另外,有许多工艺线厂家都提供经过验证的IP核和标准单元库,作为设计者没有必要每一个模块都亲历亲为,直接选用适当的IP来搭建自己的设计可以大大的缩短芯片面世的时间。

现在有许多EDA软件公司都开发了相应的EDA软件,借助快速的算法、简洁的操作来辅助IC设计师完成设计中繁重复杂的工作。

一个项目的成功与否与设计者对EDA软件的熟悉程度息息相关。

本书结合EDA软件的使用,讲述数字IC项目从设计到流片的整个过程,力求学员通过对本书的学习能够对数字IC设计的项目流程有一个清晰的认识、掌握一些常用EDA软件的使用方法。

鉴于作者的水平,书中若有不妥之处,请广大读者批评指正。

目 录第一章Sun Solaris操作系统的基本操作以及EDA软件Cadence 的基本结构1.1 硬件平台Sun工作站系统 (4)1.1.1 工作站登陆 (5)1.1.2 Solaris系统常用命令 (5)1.2 Cadence EDA产品简介 (7)第二章TOP-DOWN设计流程 (9)第三章 RTL级硬件描述语言源程序的Ambit综合 (12)3.1Ambit启动和文件输入 (12)3.2时序约束 (14)3.3 层次化与设计优化 (16)第四章 数字系统的自动布局布线流程 (18)4.1 SE环境启动及文件输入 (18)4.2 整体布局 (21)4.3 电源、地的布线 (24)4.4 单元放置 (25)4.5 布线 (27)附录 实验报告模板 (30)第一章Sun Solaris操作系统的基本操作以及EDA软件Cadence的基本结构随着集成电子技术的发展,数字系统的设计朝着容量大、功能强、体积小、重量轻的方向发展,在TOP-DOWN的设计流程里,除了系统的行为描述外,其余设计几乎都可以在人为控制下由EDA软件自动完成,从而大大的缩短系统的设计周期,提高竞争力。

14 第八讲 自动布局布线

setFormField "Verilog To Cell" "Verilog File Name" "Verilog网表文件名"

setFormField "Verilog To Cell" "Output Cell Name" "输出的设计单元名"

setFormField "Verilog To Cell" "Top Module Name" "Verilog网表文件中 最顶层的模块名"

dbCreateCellInst (geGetEditCell) "" "PVSS2W" "VSS33" "0" "No" '(0 0) "design_in"

//插入Corner

dbCreateCellInst (geGetEditCell) "" "PCORNERW" "CORNER1" "0" "No" '(0 0) "design_in"

2019/11/24

共83页

26

整体规划—标准单元布局

IO PAD Core Corner

2019/11/24

共83页

27

整体规划—标准单元布局

在设计窗口中选择 Design Setup->setup floorplan

2019/11/24

共83页

28

整体规划—标准单元布局

axgPlanner setFormField "Floor Planning" "Row/Core Ratio" "1" setFormField "Floor Planning" "Double Back" "1" setFormField "Floor Planning" "Start from first row" "1" setFormField "Floor Planning" "Flip first row" "1" setFormField "Floor Planning" "Core To Left" "100" setFormField "Floor Planning" "Core To Bottom" "100" setFormField "Floor Planning" "Core To Right" "100" setFormField "Floor Planning" "Core To Top" "100" formOK "Floor Planning"

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

Timing Library Format (TLF)

General Constraints Format (GCF) file Standard Delay Format (SDF) Constraints File

Library Requirements

LEF

• • LEF库是一个文本文件,描述目标工艺库中宏单元的局部的物 理信息。其描述必须符合LEF规定结构及语法。 LEF库描述标准单元库的工艺特性及单元(cell)数据 • • • • 描述用于宏单元互连的各布线层的详细信息 布线器要用的via单元 core和pad的位置定义

使用 Abstract Generator产生LEF库

• 可以使用Abstract Generator或 AutoABgen产生Abstract和LEF

View of a NAND Gate

TLF

• • • TLF文件描述单元库的时序信息 进行时序驱动布局布线及产生时钟树所必需 描述的元件与其它库一致,包括: • • • • LEF库所有单元,并有一致的单元信号引脚,除电源、地 引脚次序与Verilog库一致

LEF库可以有一个或多个 LEF库可以由Envisia™ Abstract Generator产生 注意LEF的版本。对于SEDSM, LEF版本要高于5.1。 用Import LEF命令读入LEF文件来建立设计数据库。

LEF — 工艺说明

• 不需要说明IC设计所需要的所有层的信息,如扩散层,就不需 要在LEF文件中描述,除非有在扩散层的pin

•

System support tools:导 入/导出数据、验证设计数据并可以手工进行 布局布线。

SE 特点

SE DSM是Silicon Ensemble深亚微米版本

• • • • • • QPlace, 百万门级的高速布局工具 时序驱动的布局布线 在布线前可压缩布局 基于面积的布线器,支持2~6层金属层 支持Scan chain 2.5维参数提取

自动布局布线(Silicon Ensemble)

于敦山

Tel: 62765928 Email: yds@

SE 简介

Silicon Ensemble 由几个功能子系统构成,如下图:

• • •

floorplanner: 建立放置标准单元的row placers: 自动的或增量式的进行单元布局,布局时可以优化 routers: 使用进行global、final、power、clock以及一些特殊连接线的 布线

如果LEF文件只包含单元的工艺信息,没有物理描述,可以使 用Input GDSII命令(在命令行)。Input GDSII命令建立一个 物理的LEF文件。然后可以用Import LEF命令将这些物理信息 加入设计数据库。也可以使用Abstract Generator产生的 abstract view的物理数据。

可以有一个或多个TLF库 可以用syn2tlf(Cadence)工具从Synopsys.lib库产生这个文件 使用GCF文件指定TLF(CTLF)文件。 可以使用tlfc命令将TLF文本文件编译为CTLF文件。

设计库的一致性

• • Silicon Ensemble ™提供宏单元验证工具 必须保证以不同格式保存的这些信息库的一致性。

• 下面是layer, via, and site定义的一个例子 LAYER M1

TYPE ROUTING ; PITCH 2.4 ; WIDTH 2.0 ; SPACING 1.0 ; DIRECTION VERTICAL ; END M1

VIA C2PLY DEFAULT

LAYER M1 ; RECT -2.0 -2.0 2.0 2.0 ; LAYER CUT01 ; RECT -1.0 -1.0 1.0 1.0 ; LAYER POLY ; RECT -3.0 -3.0 3.0 3.0 ; END C2PLY

Silicon Ensemble Ultra

• • • • 具有SE DSM的所有特性 Ultra router:基于面积的布线器,支持 7~ 9 金属层互连 使用 HyperExtract进行2.5维参数提取 在ultra placer的同时进行时序优化

SE 特点

Silicon Ensemble With Signal And Design Integrity(SESI): • • • 具有SE ultra的所有特性 Through-pin约束提高时序精确性 串扰(Crosstalk)分析、阻止及修复

SITE CORE21

CLASS CORE ; SIZE 2.4 BY 43.2 ; END CORE21

LEF — 宏单元

• 宏单元描述包括Site, Size, Origin, Pins以及Blockages. • Site:描述宏单元使用的site类型 Size:宏单元所有图形中外框,可以是长方形或正方形 Pin:表示连接宏单元输入/输出的点或点集 Blockage(obstructs ):表示阻止布线的区域(阻挡层)

LEF--宏单元定义的例子

MACRO AND2 SITE CORE21 ; SIZE 70 BY 85 ; PIN A PORT LAYER M1 ; RECT 32.5 32.5 37.5 52.5 ; END END A PIN B PORT ... OBS LAYER M1 ; RECT 22.5 10 27.5 20 ; END END AND2

•

• • • •

热电子分析及提高门的驱动的调整

连接线导热分析及加宽连接线的调整 静态及动态功耗分析 内部电源线的静态电迁移分析 布局布线后电源的电压降 (IR drop)分析

布局布线前的准备

• 进行自动布局布线,需准备下列文件: Verilog Netlist Design Exchange Format (DEF) Netlist Library Exchange Format (LEF)