课题 七人表决器

七人多路表决器实验总结

Eda与数字系统课程设计课题名称:用VHDL文本输入法设计一个7人多数表决电路班级:09电科四班学号:2220091497姓名:楚惠一.课题题目:多数表决电路的设计之二要求:用VHDL文本输入法设计一个7人多数表决电路二.实验内容所谓表决器就是对于一个行为,由多个人投票,如果同意的票数过半,就认为此行为可行;否则如果否决的票数过半,则认为此行为无效。

七人表决器顾名思义就是由七个人来投票,当同意的票数大于或者等于4人时,则认为同意;反之,当否决的票数大于或者等于4人时,则认为不同意。

实验中用7个拨挡开关来表示七个人,当对应的拨挡开关输入为‘1’时,表示此人同意;否则若拨挡开关输入为‘0’时,则表示此人反对。

表决的结果用一个LED表示,若表决的结果为同意,则LED被点亮;否则,如果表决的结果为反对,则LED不会被点亮。

三.设计步骤1、表决器主控电路代码如下:library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;entity biao isport (xin: in std_logic_vector ( 6 downto 0 );xout,xout0,xout1,xout2 : out std_logic_vector ( 6 downto 0 ));end entity ;architecture bev of biao isbeginprocess ( xin )variable j: integer :=0;beginj:=0;for i in 0 to 6 loopif xin(i)='1' thenj:=j+1;end if;end loop;if j>3 thenxout<="0110000";else xout<="1111110";end if;case j iswhen 0 =>xout1<="1111110";when 1 =>xout1<="0110000";when 2 =>xout1<="1101101";when 3 =>xout1<="1111001";when 4 =>xout1<="0110011";when 5 =>xout1<="1011011";when 6 =>xout1<="1011111";when 7 =>xout1<="1110000";when others =>xout1<="XXXXXXX";end case;case j iswhen 7 =>xout0<="1111110";when 6 =>xout0<="0110000";when 5 =>xout0<="1101101";when 4 =>xout0<="1111001";when 3 =>xout0<="1011011";when 2 =>xout0<="0010010";when 1 =>xout0<="1011111";when 0 =>xout0<="1110000";when others =>xout0<="XXXXXXX";end case;end process;end architecture bev;2、输出显示部分数码管扫描用到的六进制计数器library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;entity cnt6a isport(cp,reset : in std_logic;sel :out std_logic_vector(2 downto 0));end cnt6a;architecture behave of cnt6a issignal sec :std_logic_vector (2 downto 0);beginprocess(reset,cp)beginif (reset='0')thensec<="000";elsif (cp'event and cp='1')thenif(sec="101") thensec<="000";elsesec<=sec+1;end if;end if;end process;sel<=sec;end behave;数码管的七段输出library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;entity mux6 isport (cnthh,cnthl,cntmh,cntml,cntsh,cntsl :in std_logic_vector(6 downto 0);sel :in std_logic_vector(2 downto 0);cntout :out std_logic_vector(6 downto 0));end mux6;architecture behav of mux6 isbeginprocess(sel)begincase sel iswhen"000"=>cntout<=cntsl(6 downto 0);when"001"=>cntout<=cntsh(6 downto 0);when"010"=>cntout<=cntml(6 downto 0);when"011"=>cntout<=cntmh(6 downto 0);when"100"=>cntout<=cnthl(6 downto 0);when"101"=>cntout<=cnthh(6 downto 0);when others=>cntout<="0000000";end case;end process;end behav;顶层原理图:八.实验结果通过muxplus2对七人表决器进行设计,完成实验要求,得到实验结果,实现了七人表决的效果,4人或4人以上通过则亮绿灯,否则亮红灯。

七人表决器实验

3.3实验三七人表决器设计3.3.1实验目的1、掌握用QuartusII软件设计基本数字系统流程及注意事项。

2、进一步熟练掌握程序的编译、仿真、生成模块及芯片引脚号码锁定方法。

3、掌握分层设计的方法和注意事项4、在实验报告中,总结数字系统设计步骤及注意事项。

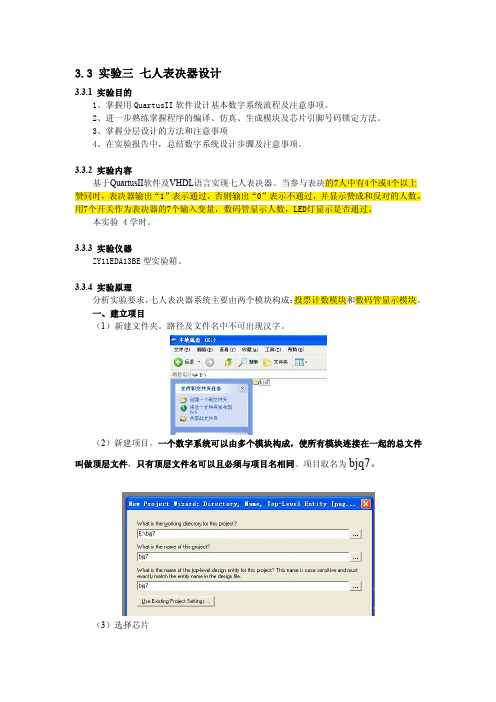

3.3.2实验内容基于QuartusII软件及VHDL语言实现七人表决器。

当参与表决的7人中有4个或4个以上赞同时,表决器输出“1”表示通过,否则输出“0”表示不通过,并显示赞成和反对的人数。

用7个开关作为表决器的7个输入变量,数码管显示人数,LED灯显示是否通过。

本实验4学时。

3.3.3实验仪器ZY11EDA13BE型实验箱。

3.3.4实验原理分析实验要求,七人表决器系统主要由两个模块构成:投票计数模块和数码管显示模块。

一、建立项目(1)新建文件夹。

路径及文件名中不可出现汉字。

(2)新建项目。

一个数字系统可以由多个模块构成,使所有模块连接在一起的总文件叫做顶层文件,只有顶层文件名可以且必须与项目名相同。

项目取名为bjq7。

(3)选择芯片二、建立文件首先,建立各个VHDL功能模块。

1.投票计数模块。

(1)新建VHDL文件编辑VHDL程序。

投票计数模块输入为七个电平开关input,输出为同意的人数agree,反对的人数disagree,是否通过指示灯y,程序清单如下:library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;entity BJQ isport(input:in std_logic_vector(6downto0);七个输入开关agree:out std_logic_vector(3downto0);同意的人数disagree:out std_logic_vector(3downto0);不同意的人数y:out std_logic);是否通过标志end;architecture one of BJQ isbeginprocess(input)variable cnt:integer range0to7;variable cnt0:integer range0to7;begincnt:=0;for i in6downto0loopif input(i)='1'thencnt:=cnt+1;end if;end loop;cnt0:=7-cnt;if cnt>3then y<='0';else y<='1';end if;case cnt iswhen0=>agree<="0000";when1=>agree<="0001";when2=>agree<="0010";when3=>agree<="0011";when4=>agree<="0100";when5=>agree<="0101";when6=>agree<="0110";when7=>agree<="0111";when others=>agree<="0000";end case;case cnt0iswhen0=>disagree<="0000";when1=>disagree<="0001";when2=>disagree<="0010";when3=>disagree<="0011";when4=>disagree<="0100";when5=>disagree<="0101";when6=>disagree<="0110";when7=>disagree<="0111";when others=>disagree<="0000";end case;end process;end;程序输入完成后进行保存,名字与实体名一致BJQ。

实验2七人表决器概要

1

ZY11EDA13BE实验箱简介

2

1. 实验箱俯视图

3

本实验箱采用先进的主板+适配板+扩展板的灵活 结构,并采用ALTERA公司ACEX系列3万门的 FPGA器件EP1K30QC208-2为核心处理芯片。提 供1968个寄存器,24576个存储位,30000个典型门 ,因此EP1K30非常适合于构建复杂逻辑功能和存 储功能。

8

电源的打开顺序是:先打开交流开关,再打开直流开关, 最后打开各个模块的控制开关。电源关掉的顺序刚 好相反。

9

4用配置/编程模块,可以使 用本模块对ALTERA、LATTICE、XILINX等国际著名P LD公司的几乎所有isp器件或FPGA/CPLD器件进行编程 下载并且能自动识别目标器件。

43

3)锁定后重新编译;

引脚重新定义后必须再通过编译器 “Compile”对文件重新进行编译,以 便将引脚信息编入下载文件中。此时 回到原来的设计文件“7vote.gdf”上 的输入输出信号旁都标有其对应的管 脚号。

44

编程下载

1)将25针下载电缆线一端插入LPT1(打印 机口即并行口),另一端连接到实验箱主板 系统的通用编程模块DB25接口,再用十针连 接线一端插入该模块JTAG下载接口固定不变, 另一端连接到主板系统的配置模块中目标芯 片的下载接口,打开系统主板电源。

4

2. 核心芯片俯视图

5

EP1K30包含一个嵌入式阵列来完成存储功能, 一个逻辑阵列来完成通用逻辑功能和众多的引 脚从而使其可以作为接口与系统组件有效连接。 做实验时切记不要用手触摸核心芯片A,静电可 能会损坏此贴片芯片。

6

3. 电源模块

7

电源模块包括3个开关,7个电压输出插孔。其 中交流开关用于打开从220V交流电源接入的内部 变压器,为实验箱提供基本工作电源。打开交流 开关,电源指示灯PL0亮,实验箱进入待机状态。 按钮开关APW1用于打开主板中模块工作电源,按 下APW1后,电源指示灯PL1亮,实验箱进入工作 状态,为系统提供+5V,+3.3V,+2.5V,+1.8V电源 。 按钮开关APW2用于打开+12V,-12V电源,按 下APW2后,电源指示灯PL2、PL3亮。

实验一七人表决器实验指导书

EDA实验指导书(EL-SOPC4000实验箱)指导老师:姚晓通电工电子实验中心七人表决器一、实验目的1.了解表决器的原理。

2.熟悉QuartusII软件建立工程,图形输入法进行设计。

3.熟悉整个开发的流程,初步使用EL-SOPC4000实验箱。

二、实验原理所谓表决器就是对于一个行为,由多个人投票,如果同意的票数过半,就认为此行为可行;否则如果否决的票数过半,则认为此行为无效。

七人表决器顾名思义就是由七个人来投票,当同意的票数大于或者等于4人时,则认为同意;反之,当否决的票数大于或者等于4人时,则认为不同意。

实验中用7个拨挡开关来表示七个人,当对应的拨挡开关输入为‘1’时,表示此人同意;否则若拨挡开关输入为‘0’时,则表示此人反对。

表决的结果用一个LED表示,若表决的结果为同意,则LED被点亮;否则,如果表决的结果为反对,则LED不会被点亮。

根据电路状态转换表→设计数值输出→运用门电路设计电路图→仿真运行→实现七人多数表决器的设计。

电路状态转换图:根据电路状态转换图设计电路,用一个半加器实现设计一个全加器,运用4个全加器实现七人表决器的设计。

(2)半加器电路设计:图 1 半加器的原理图(3)全加器电路设计:图 2 全加器的原理图(4)七人表决器电路设计:图3 七人表决器的原理图三、实验内容(1)根据设计要求,绘制出电路状态转换图,实现七人四票制表决。

(2)根据电路状态转换图,用门电路设计出七人表决器。

(3)运用半加器,全加器,实现表决器的设计。

(4)逻辑设计要求:用七个开关作为表决器的七个输入变量,逻辑“1”时表示“赞同”,逻辑“0”时表示“不赞同”,用发光二极管作为输出指令,输出逻辑“1”表示“通过”;输出逻辑“0”时表示“不通过”。

当表决器的七个输入变量中的4个以上(包含4个)为“1”时,则表决器输出为“1”;否则为“0”。

通过状态用LED1表示,未通过用LED2表示。

四、实验步骤1.首先打开QuartusII软件,新建工程voter7。

七人表决器实验报告

七人表决器实验报告七人表决器实验报告引言:在日常生活中,我们经常会遇到需要做决策的情况。

而在集体决策中,如何快速、公正地达成共识成为了一个重要的问题。

为了解决这一问题,我们进行了七人表决器的实验。

本实验旨在探索七人表决器在集体决策中的效果和影响因素。

实验设计:我们邀请了七位志愿者参与实验,每个人都具有不同的背景和观点。

在实验开始前,我们向每位参与者提供了相同的决策问题,并要求他们独立思考并给出自己的答案。

然后,我们将七人表决器放置在桌面上,并告知参与者如何使用。

在每次决策中,参与者需要将自己的决策结果输入到表决器中,然后等待其他人完成决策。

当所有参与者完成决策后,表决器会自动计算出最终的决策结果。

实验结果:通过观察实验过程和分析实验数据,我们得出了以下结论:1. 影响决策结果的因素:参与者的个人观点、决策顺序以及决策权重等因素都可能影响最终的决策结果。

在实验中,我们发现当个人观点相差较大时,决策结果往往会偏向于多数人的意见。

而当个人观点相似或相同时,决策结果则更容易达成一致。

2. 决策效率的提升:相比于传统的集体讨论和投票方式,七人表决器在决策效率上具有明显的优势。

参与者只需输入自己的决策结果,无需进行冗长的讨论和辩论过程,从而节省了时间和精力。

3. 决策公正性的保障:七人表决器在一定程度上保障了决策的公正性。

由于每个参与者的决策权重相等,没有任何一方能够主导决策结果。

这种平等的决策机制能够避免个别参与者的意见被忽视或压制,从而提高了决策的公正性。

讨论:尽管七人表决器在决策效率和公正性方面具有优势,但仍存在一些潜在的问题和限制。

首先,由于每个参与者只能输入一个决策结果,可能无法充分体现个体的多样性和复杂性。

其次,决策结果可能受到决策顺序的影响,先行决策者的意见可能会对后续决策者产生影响。

此外,表决器本身的设计和算法也可能存在一定的偏差,需要进一步优化和改进。

结论:通过本次实验,我们初步探索了七人表决器在集体决策中的应用。

可编程式逻辑器件设计试验报告实验二 七人表决器

昆明理工大学信息工程与自动化学院学生实验报告(2012———2013 学年第 2 学期)课程名称:可编程逻辑器件开课实验室:信自楼504 2013年4 月19日一.实验要求、本实验要求编写一个七人表决器,描述为:总共有7个人进行投票选择,只有达到4人或者4人以上才能够通过。

二.实验过程:输入为2进制7位的VOTE,输出为2进制4位的SUM,当SUM得第三位为1时,即SUM>=4,即通过PASS!三.实验代码:在本次试验中,我通过观察实验代码,自己编写了11人表决器:module vote_11(pass,vote);output pass;reg pass;input [10:0] vote;reg[3:0]sum;integer i;always@(vote)beginsum=0;for(i=0;i<=10;i=i+1)if(vote[i]) sum=sum+1;if(sum[3]) if(sum[2]) pass=1;else pass=0;endendmodule四.实验截图:五.实验总结:通过上次对Quartus Ⅱ环境的熟悉,这次的试验速度上就要比上次好得多,这也是上次试验多次实践讨论改错的功劳,这次我对于VERILOG HDL 的模拟功能有了一定的理解,通过对试验代码的调试,我发现了代码中存在很多的问题,查资料、与同学老师讨论使我最终解决了一个个问题和错误,在仿真后我得到了仿真波形,完成了这次试验任务。

通过这次试验,我发现对Quartus Ⅱ环境的熟悉是一个长期试验使用的过程,结果了两次的试验,我了解的知识微小的那一小部分。

我需要学习的还很多。

同时课本上的理论知识也是很重要的,扎实的基础使我们进一步提高自己的基础。

我们要扎住在校的学习时间为以后的工作打好基础。

七人表决器课程设计报告

课程设计课程名称硬件描述语言与EDA技术题目名称硬件描述语言与EDA技术实践学生学院材料与能源专业班级 11微电子学(1)班学号学生XX指导教师2021年 6月 27日XX工业大学课程设计任务书题目名称硬件描述语言与EDA技术实践学生学院材料与能源学院专业班级11微电子学(1)班姓名学号一、课程设计的内容与要求1.系统功能分析,分模块层次化设计;2.实现系统功能的方案设计;3.编写各功能模块VHDL语言程序;4.对各功能模块进展编译、综合、仿真和验证;5.顶层文件设计,可用VHDL语言设计,也可以用原理图设计;6.整个系统进展编译、综合、仿真和验证;7.在CPLD/FPGA实验开发系统试验箱上进展硬件验证;8.按所布置的题目要求,每一位学生独立完成全过程。

二、课程设计应完成的工作1.所要求设计内容的全部工作;2.按设计指导书要求提交一份报告书;3.提交电子版的设计全部内容:工程目录文件夹中的全部内容,报告书三、课程设计进程安排四、应收集的资料及主要参考文献1.陈先朝,硬件描述语言与EDA技术实践指导书,2021年3月2.曹昕燕等编著,EDA技术实验与课程设计,清华大学,2006年5月3.X欲晓等编著,EDA技术与VHDL电路开发应用实践,电子工业,2021年4月4.X昌华等编著,数字逻辑EDA设计与实践:MAX+plusⅡ与QuartusⅡ双剑合璧,国防工业,2021年5.X江海主编,EDA技术课程设计,华中科技大学,2021年1月发出任务书日期: 2021年6月 23日指导教师签名:方案完成日期: 2021年6月 27日基层教学单位责任人签章:主管院长签章:七人表决器1.设计目的(1)学习和掌握Quartus II软件的根本操作;(2)通过设计七人表决器,掌握基于可编程器件的VHDL硬件描述语言的设计方法;(3)学习用CPLD/FPGA 实践系统硬件验证电路设计的正确性2.设计题目及要求(1)题目:表决器(2)要求:设计一个七人表决器,当赞成人数大于等于四时显示表决通过,同时分别将投票中赞成的人数和反对的人数在数码管上显示出来。

七人表决器——精选推荐

七人表决器一:实验目的1.掌握用VHDL硬件描述语言做数字电路综合和设计的方法。

2.熟练掌握程序的编译,仿真,生成模块及引脚号码锁定方法并下载到目标芯片。

二:实验仪器ZY11EDA12BE三:实验要求设计一个七人表决电路,当参与表决的7人中有4人或4人以上赞同时,表决器输出“1”表示通过,否则输出“0”表示不通过。

实验时,可用7个电平开关作为表决器的7个输入变量,输入“1”表示表决者“赞同”输入“0”表示表决者“不赞同”。

可在上述电路的基础上,增加数码管显示功能,显示赞同和不赞同的票数。

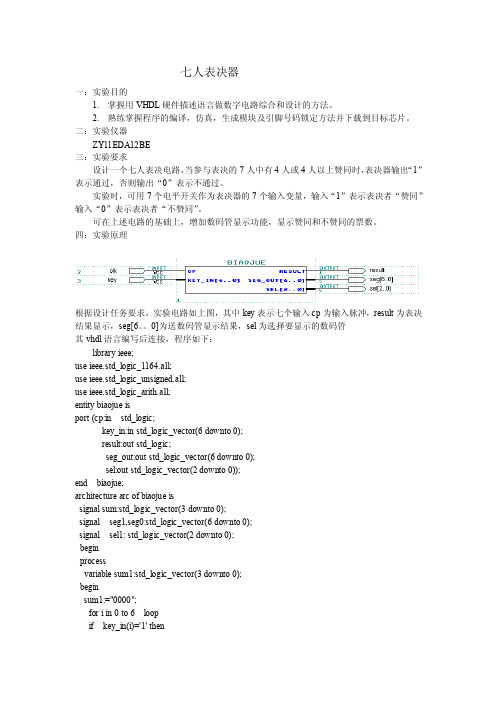

四:实验原理根据设计任务要求,实验电路如上图,其中key表示七个输入cp为输入脉冲,result为表决结果显示,seg[6。

0]为送数码管显示结果,sel为选择要显示的数码管其vhdl语言编写后连接,程序如下:library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;use ieee.std_logic_arith.all;entity biaojue isport (cp:in std_logic;key_in:in std_logic_vector(6 downto 0);result:out std_logic;seg_out:out std_logic_vector(6 downto 0);sel:out std_logic_vector(2 downto 0));end biaojue;architecture arc of biaojue issignal sum:std_logic_vector(3 downto 0);signal seg1,seg0:std_logic_vector(6 downto 0);signal sel1: std_logic_vector(2 downto 0);beginprocessvariable sum1:std_logic_vector(3 downto 0);beginsum1:="0000";for i in 0 to 6 loopif key_in(i)='1' thensum1:=sum1+"0001";elsesum1:=sum1;end if;end loop;sum<=sum1;if sum(2)='1' thenresult<='1';elseresult<='0';end if;case sum iswhen "0000"=>seg1<="0111111";seg0<="0000111";when "0001"=>seg1<="0000110";seg0<="1111101";when "0010"=>seg1<="1011011";seg0<="1101101";when "0011"=>seg1<="1001111";seg0<="1100110";when "0100"=>seg1<="1100110";seg0<="1001111";when "0101"=>seg1<="1101101";seg0<="1011011";when "0110"=>seg1<="1111101";seg0<="0000110";when"0111"=> seg1<="0000111";seg0<="0111111";when others=>seg1<="0000000";seg0<="0000000"; end case;end process;process(cp)beginif(cp'event and cp='1') thenif sel1<="001"thensel1<="000";else sel1<=sel1+"001";end if;end if;end process;sel<=sel1;process(cp)beginif(cp'event and cp='1')then--sel<=sel1;if sel1="001"thenseg_out<=seg0;--sel<=sel1;elsif sel1="000" thenseg_out<=seg1;--sel<=sel1;end if;end if;end process;end arc;五:管脚锁定输入:1.掌握了用vhdl语言常用的设计方法,原理图和vhdl语言硬件描述法2.理解动态扫描电路的基本原理并实现七:参考资料《EDA技术习题与实践》《EDA与数字系统设计》。

实验报告及心得体会

实验报告及心得体会实验名称:七人表决器实验目的:通过Max+plus2软件实现七人表决功能,熟练掌握用Max+plus2实现七人表决器的操作步骤实验步骤:1.打开Max+plus2软件2.打开file-open,在open对话框的Text Editor files选择后缀为*.vhd文件格式3.选择files为VOTE7.vhd的文件,单击ok,出现源程序文本4.单击file-project-set project to…,单击Assign-Device选择驱动,在弹出的Device窗口下选择Device为EPF1OK1OLC84-4,单击ok5.单击Assign-pin/location/chip…进行引脚锁定。

例如,输入从men0到men6,对应的input pin为28-30、35-38,在Node name中输入pass,对应输出pin为V ote7,output pin为23,在Node name中输入stop chip name为vote7,output pin为65,单击ok6.单击菜单下的compiler选项,在出现的窗口下单击start完成综合,单击确定,关闭窗口7.单击菜单下的programmer选项,若未出现Hardware setup窗口,则打开options菜单下的Hardware setup选项,在弹出的窗口下,选择Hardware type为Byteblaster(MV)选项,单击ok,然后再单击configure,完成进程8.使用仪器通过仪器观察,在K1-K8的八个输出发光二极管中(程序中选择七个)开始时都不亮。

在L1-L11,这十一个发光二极管中有L6开始时亮,L11不亮,依次按下K1-K8中的四个发光二极管的按钮使其发光,则L6熄灭,L11发光,说明实现了七人表决器实验结果:输出发光二极管K1-K8中有4个灯亮时,L6熄灭,L11发光,说明7人中只要有四人同意时,表决成功心得体会通过老师的实验演示,我基本明白了Max+plus2软件的使用方法。

7人表决电路设计

郑州航空工业管理学院EDA技术及应用课程设计说明书 12 届电子信息工程专业 1213082 班级题目7人表决电路设计学号121308239姓名赵维炜指导教师王春彦程铮张臻二О一四年六月二十四日一、7人表决电路设计原理此实验是用七个开关作为表决器的7个输入变量,输入变量为逻辑“1”时表示表决者“赞同”;输入变量为逻辑“0”时,表示表决者“不赞同”。

输出逻辑“1”时,表示表决“通过”;输出逻辑“0”时,表示表决“不通过”。

当表决器的七个输入变量中有4个以上(含4个)为“1”时,则表决器输出为“1”;否则为“0”。

七人表决器设计方案很多,比如用多个全加器采用组合电路实现。

用verilog语言设计七人表决器时,也有多种选择。

我们可以用结构描述的方式用多个全加器来实现电路,也可以用行为描述。

采用行为描述时,可用一变量来表示选举通过的总人数。

当选举人大于或等于4时为通过,绿灯亮;反之不通过时,黄灯亮。

描述时,只须检查每一个输入的状态(通过为“1”,不通过为“0”),并将这些状态值相加,判断状态值和即可选择输出。

二、7人表决电路设计的硬件(1)晶振为12 MHz(2)采用CPLD 器件,为MAX7000AE的EPM7064AELC44—10 (3)采用数码管显示1、电路图芯片图:CPLD的工作大部分是在电脑上完成的。

打开集成开发软件→画原理图、写硬件描述语言(VHDL,Verilog)→编译→给出逻辑电路的输入激励信号,进行仿真,查看逻辑输出结果是否正确→进行管脚输入、输出锁定(7064的44个输入、输出管脚可根据需要设定)→生成代码→通过下载电缆将代码传送并存储在CPLD芯片中。

7128这块芯片各管脚已引出,将数码管、抢答开关、指示灯、蜂鸣器通过导线分别接到芯片板上,通电测试,数码管:R26-r33 r12-r19 是限流电阻,位码由于电流过大,采用了三极管驱动,数码管为共阴极,当有信号1时,对应数码管才能操作。

七人表决器实验报告doc

七人表决器实验报告篇一:哈工大电工学新技术实践实验报告-7人表决器总成绩:一、设计任务1、有七人参与表决,显示赞同者个数。

2当赞同者达到及超过4人时,绿灯显示表示通过。

二、设计条件本设计基于软件Multisim10.0.1进行仿真,在电机楼实验室XX5进行验证。

三、设计要求1、熟悉74LS161,74LS151,数码管的工作原理。

2、设计相应的电路图,标注元件参数,并进行仿真验证。

四、设计内容1. 电路原理图(含管脚接线)电路原理图如图1所示图1 电路原理图2. 计算与仿真分析仿真结果如图2、3、4所示图2 仿真结果图4 仿真结果4. 调试流程调试流程如图5所示图5 调试流程5. 设计和使用说明74LS151芯片为互补输出的8选1数据选择器,引脚排列如图6所示,功能见表1。

选择控制端(地址端)为C~A,按二进制译码,从8个输入数据D0~D7中,选择一个需要的数据送到输出端Y,G为使能端,低电平有效。

(1)使能端G=1时,不论C~A状态如何,均无输出(Y=0,W=1),多路开关被禁止。

(2)使能端G=0时,多路开关正常工作,根据地址码C、B、A的状态选择D0~D7中某一个通道的数据输送到输出端Y。

如:CBA=000,则选择D0数据到输出端,即Y=D0。

如:CBA=001,则选择D1数据到输出端,即Y=D1,其余类推。

图6 74LS151引脚排列表1 74LS151功能表74LS161功能:(1)异步置“0”功能:接好电源和地,将清除端接低电平无论其他各输入端的状态如何,测试计数器的输出端,如果操作无误Q3~Q0均为0。

(2)预置数功能:将清除端接高电平,预置控制端接低电平,数据输入端D3~D0置0011,在CP的上升沿作用后,测试输出端Q3~Q0的电平。

如果操作准确,D3~D0的数据为0011,说明D3~D0的数据已预置到Q3~Q0端。

(3)计数和进位功能:将 LD、Cr 、CET、CEP端均接高电平,CLK端输入单脉冲,记录输出端状态。

七人表决器

彩灯正常, 数码管显示 不正常。

彩灯正常, 数码管没 有显示预 期效果

彩灯正常, 数码管显示正 常

FPGA/CPLD课程设计

题Байду номын сангаас 七人表决器

引言 设计实现功能

设计介绍

系统总体设计与实现 总结

设计实现功能

基于Quartus ii 9.0平台设计与实现7人表决器

基于可编程器件的VHDL硬件描述语言设计七人表决器

学习用CPLD/FPGA 在开发板上的具体应用

表决器的功能是将所投票者的结果综合起来,超过 半数赞成则表示结果通过,反之则不通过。而七人 表决器由七个人来投票,当赞成的票数大于或者等 于4人,则认为通过;当反对的票数大于或者等于4 人时,则认为不通过。所以这次设计中我将用7个数 据开关来表示七个人,当对应的按键按下输入为‘1’ 时,表示此人同意;否则若按键跳起输入为‘0’时, 则表示此人反对。表决的结果用一个LED表示,若表 决的结果为同意,则LED被点亮,否则,如果表决的 结果为反对,则LED不会被点亮。同时用七段显示数 码管来显示赞成的人数。

单片机七人表决器

单片机七人表决器一.方案设计1.设计题目:七人表决器。

2.实训要求利用at89s51单片机设计并制作会议投票表决计票器电路。

具体内容建议如下:1、可供57个人进行表决,每个人有一个“同意”和一个“反对”按键,表决时两个键先按下的一个有效,若再按另一个键将清楚前一次按键的效能;每次表决每个按键只能是第一次按的有效,多按的次数无效,除非前一次按键的效能已被清楚或没有生效。

2、会议主持人可以利用按键掌控投票表决已经开始和完结;已经开始投票表决后,照亮黄色指示灯,则表示可以展开投票表决,同时确切原来的投票表决结果;完结投票表决后表明投票表决结果;“同意”多于“反对”照亮绿色指示灯,反之照亮红色指示灯。

3、在实现上述功能的基础上增加“同意”数和“反对”数的显示。

二.硬件电路设计和原理。

1.硬件设计思路:设计题目为5―7人表决器,题目评选为七人表决器,七个按键表示同意,七个按键则表示反对,各按键与单片机的输出端口相连,因此可以采用单片机的四个i/o口,因为在单片机内部p1和p2都存有上啦电阻,而p0没上啦电阻,必须在外部加之一个上拉电阻,为了精简电路,把p1和p2口评选为按键同意和反对的输出端的,因为投票表决考试和完结必须利用主持人按键来控制,我采用外部中断0和外部中断一来控制其开始和结束;设计要求中需要四张灯,分别为2个红灯,一个黄灯,一个绿灯,其中三个灯用于输出显示,可用单片机的i/o口,另外一个红灯作为电源灯来显示,判断是否通电,因为p1口和p2口用做按键的同意和反对,把p2剩余的i/o口与三个灯连接,分别连接在p2.3,p2.4,p2.5口,因为p0口是低电平有效所以我的p0口与led现实器相连用于显示反对与同意的人数的多少,采用动态显示的方式,为了保证两个显示器不再相同时间显示相同的数字,所以led显示器的公共端受另外一组信号的控制,采用延时的方式让它们分别显示出来。

2.元件参数确认:设计中需要四盏灯,分别为两个红灯,一个绿灯,一个黄灯,p0口的输出端输出高电平一般为5伏左右,最大电流为五毫安,因此必须加上限流电阻,我选用的是470欧的电阻,然后将单片机的最小系统加入此次的电路中。

EDA技术实验报告七人表决器完美版

广东工业大学课程设计任务书一、课程设计的内容1. 系统功能分析;2. 实现系统功能的方案设计;3. 编写各功能模块VHDL语言程序;4. 对各功能模块进行编译、综合、仿真和验证;5. 顶层文件设计;6. 整个系统进行编译、综合、仿真和验证;二、课程设计的要求与数据1. 按所布置的题目要求,每一位学生独立完成全过程;2. 分模块层次化设计;3. 各功能模块的底层文件必须用VHDL语言设计,顶层文件可用VHDL语言设计,也可以用原理图设计。

三、课程设计应完成的工作1. 所要求设计内容的全部工作;2. 按设计指导书要求提交一份报告书;3. 提交电子版的设计全部内容:工程目录文件夹中的全部内容,报告书四、课程设计进程安排五、应收集的资料及主要参考文献1. 陈先朝,硬件描述语言与EDA技术实践指导书,2011年11月2. 曹昕燕等编著,EDA技术实验与课程设计,清华大学出版社,2006年5月3. 刘欲晓等编著,EDA技术与VHDL电路开发应用实践,电子工业出版社,2009年4月4. 刘昌华等编著,数字逻辑EDA设计与实践:MAX+plusⅡ与QuartusⅡ双剑合璧,国防工业出版社,2009年5. 刘江海主编,EDA技术课程设计,华中科技大学出版社,2009年1月发出任务书日期: 2011年12月 5日指导教师签名:计划完成日期: 2011年12月 9日基层教学单位责任人签章:主管院长签章:七人表决器设计一、设计目的1.熟悉Quartus II软件的使用。

2.熟悉七人表决器的工作原理3.熟悉EDA开发的基本流程。

二、设计要求表决器就是对于一个行为,由多个人投票,如果同意的票数过半,就认为此行为可行;否则如果否决的票数过半,则认为此行为无效。

七人表决器由七个人来投票,当同意的票数大于或者等于4人时,则认为同意;反之,当否决的票数大于或者等于4人时,则认为不同意。

实验中用7个拨挡开关来表示七个人,当对应的拨挡开关输入为‘1’时,表示此人同意;否则若拨挡开关输入为‘0’时,则表示此人反对。

七人表决器—VHDL

北方民族大学课设报告院系电气信息工程学院姓名张海强学号 2017xxxx专业电子信息工程班级 2017级(1)班同组人员课程名称 EDA技术基础题目名称七人表决器起止时间成绩指导教师教师评语:北方民族大学教务处制1.设计任务要求:七人表决器的设计内容主要是,用七个开关作为表决器的7个输入变量,输入变量为逻辑“1”时表示表决者“赞同”;输入变量为“0”时,表示表决者“不赞同”。

输出逻辑“1”时,表示表决“通过”;输出逻辑“0”时,表示表决“不通过”。

当表决器的七个输入变量中有4个以上(含4个)为“1”时,则表决器输出为“1”;否则为“0”。

实验要求:1)用VHDL语言进行上述电路设计。

2)仿真验证设计结果。

2.设计原理说明:七人表决器的设计方法很多,比如用多个全加器采用组合电路实现。

用VHDL语言设计七人表决器时,也有多种选择。

常见的VHDL语言描述方式有行为描述,寄存器传输(RTL)描述、结构描述以及这几种描述在一起的混合描述。

我们可以用结构描述的方式用多个全加器来实现电路,也可以进行行为描述。

采用行为描述时,可用一变量来表示选举通过的总人数。

当选举人大于或等于4时为通过,绿灯亮;反之不通过时,黄灯亮。

描述时,只须检查每一个输入的状态(通过为“1”不通过为“0”)并将这些状态值相加,判断状态值和即可选择输出。

这里我们采用的是VHDL行为描述,行为描述简单明了,思路清晰。

3.设计方法阐述:1)实验题目分析:通过分析题目可以发现,不论用何种方法进行设计,最终的结果是有七个输入端用来表示个人的投票观点,加上七个直接的输出端接到LED灯上,显示个人的投票观点。

开始时灯为全灭,如果个人表示同意,那么与个人相对应的LED灯亮,还有两个输出端接到绿色和黄色的LED灯上,若最终表决器的输出结果是通过,那么绿色的LED灯亮,否则在黄色LED灯亮。

上述为实验的基本功能,为了更加容易分析,可以在增加投票计数等程序,同时为了计数器功能上的实用性可以加入数码管显示电路,显示票数等信息。

七人表决器设计

七人表决器设计FPGA/CPLD 2009-07-25 10:31 阅读297 评论1 字号:大大中中小小鉴于MAXPLUSSII的很多BUG,如果当编译的程序文件出现不能“进入综合”或屡次编译CHECK 没有错误而COMPILER无法完成,这时应该考虑删去MAX2WORK中该程序文件,重新建立工程,再进行编译。

七人表决器设计是VHDL中的经典设计。

从网上下载的程序要么是功能不完善,要么是程序本身存在错误。

本人对一些设计思想好的程序进行了修改或重新编写。

所谓表决器就是对于一个行为,由多个人投票,如果同意的票数过半,就认为此行为可行;否则如果否决的票数过半,则认为此行为无效。

七人表决器顾名思义就是由七个人来投票,当同意的票数大于或者等于4人时,则认为同意;反之,当否决的票数大于或者等于4人时,则认为不同意。

实验中用7个拨挡开关来表示七个人,当对应的拨挡开关输入为‘1’时,表示此人同意;否则若拨挡开关输入为‘0’时,则表示此人反对。

表决的结果用一个LED表示,若表决的结果为同意,则LED被点亮;否则,如果表决的结果为反对,则LED不会被点亮。

程序一:library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;entity bjq7 isport (input:in std_logic_vector(6 downto 0);led:out std_logic_vector(6 downto 0);y:out std_logic);end;architecture one of bjq7 isbeginprocess(input)variable cnt:integer range 0 to 7;begincnt:=0;for i in 6 downto 0 loopif input(i)='1'thencnt:=cnt+1;end if;end loop;if cnt>3 then y<='1';else y<='0';end if;case cnt iswhen 0=>led<="1111110";when 1=>led<="0110000";when 2=>led<="1101101";when 3=>led<="1111001";when 4 =>led<="0110011";when 5=>led<="1011011";when 6=>led<="1011111";when 7=>led<="1110000";when others=>led<="0000000";end case;end process;end;程序二:library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;entity vote isport (a,b,c,d,e,f,g:in std_logic;y:out std_logic);end;architecture behave of vote isbeginprocess(a,b,c,d,e,f,g)variable cnt:integer range 0 to 7;begincnt:=0;if a='1' then cnt:=cnt+1;end if;if b='1' then cnt:=cnt+1;end if;if c='1' then cnt:=cnt+1;end if;if d='1' then cnt:=cnt+1;end if;if e='1' then cnt:=cnt+1;end if;if f='1' then cnt:=cnt+1;end if;if g='1' then cnt:=cnt+1;end if;if cnt>3 then y<='1';else y<='0';end if;end process;end;。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

课题七人表决器

一、课题目的

1 .了解VHDL语言语法结构。

2 .学会用行为描述方式来设计电路。

二、课题原理

用七个开关作为表决器的7个输入变量,输入变量为逻辑“1”时表示表决者“赞同”;输入变量为“0”时,表示表决者“不赞同”。

输出逻辑“1”时,表示表决“通过”;输出逻辑“0”时,表示表决“不通过”。

当表决器的七个输入变量中有4个以上(含4个)为“1”时,则表决器输出为“1”;否则为“0”。

七人表决器设计方案很多,比如用多个全加器采用组合电路实现。

用VHDL语言设计七人表决器时,也有多种选择。

常见的VHDL语言描述方式有行为描述、寄存器传输(RTL)描述、结构描述以及这几种描述在一起的混合描述。

我们可以用结构描述的方式用多个全加器来实现电路,也可以用行为描述。

采用行为描述时,可用一变量来表示选举通过的总人数。

当选举人大于或等于4时为通过,绿灯亮;反之不通过时,黄灯亮。

描述时,只须检查每一个输入的状态(通过为“1”不通过为“0”)并将这些状态值相加,判断状态值和即可选择输出。

三、课题内容

1.用VHDL语言设计上述电路。

2.下载并验证结果。

四、设计提示

1.初次接触VHDL语言应注意语言程序的基本结构,数据类型及运算操作符。

2.了解变量和信号的区别。

3.了解进程内部顺序执行语句及进程外部并行执行语句的区别。

五、课题报告要求

1.写出七人表决器的VHDL语言设计源程序。

2.书写课题报告时要结构合理,层次分明,在分析叙述时注意语言的流畅。