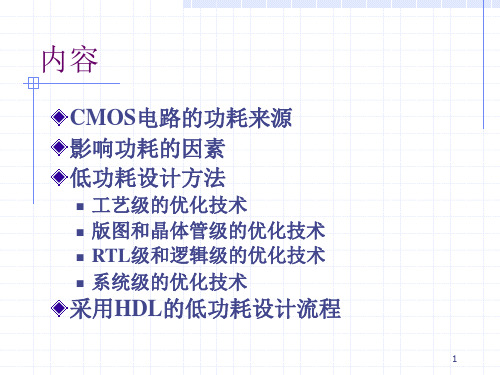

微处理器的低功耗芯片设计技术

低功耗设计方法

时序调整( retiming)

时序调整:

在流水化的电路中, 插入新的寄存器,或重新安排 寄存器的位置

减少门的翻转频率 或减少通过流水线的最长段延迟

27

组合逻辑综合和优化

逻辑提取:寻找在逻辑网表中多次重复出现的 表达式。用这个表达式的输出节点代替在网表 中出现的相同的式子, 达到节约面积的目的 提取公因子:在函数的积之和形式中导出公因 子 表达式替换:利用低有效电容的电路块代替网 表中的电路 节点消除:选择性地消除网表中的某些节点

开关活动性和数据频率f 以及开关活动率k有关:f 描述单位时间内信号到达节点的次数,而活动率k 则描述到达节点时信号的翻转几率

在有些CMOS电路中,伪跳变占据了相当一部 分开关活动性,由于此类信号没有任何作用, 因此它造成系统功耗的白白损失。

为了降低伪跳变带来的浪费,一种办法是消除伪跳 变的产生,另一办法是缩短其传播长度。

时钟是唯一在所有时间都充放电的信号 时钟信号通常要驱动大的时钟树 而且, 很多情况下会引起不必要的门的翻转

门控时钟(gated clock)技术:

将电路无计算任务的部分的时钟停下, 减少无用功 耗

22

门控时钟技术

门控时钟方法:

根据现态和输入,模块F 判定电路下一周期是否是空闲周期

如果是, 则停掉寄存器R 的时钟->避免下一个时钟周期时, 组 合电路的无用翻转。

19

20

RTL级和逻辑级的优化技术

在RTL级和逻辑门级电路设计和综合阶段,可 采用的功耗优化技术主要包括:

预计算技术 重定时技术 时钟受控技术 路径平衡技术 工艺映射技术 逻辑分解技术 状态分配技术 多级网络优化技术 公共表达式提取技术

21

门控时钟技术同步设计中, 很大一Fra bibliotek分功耗来自时钟。

mcu设计上的注意事项

mcu设计上的注意事项MCU(Microcontroller Unit)是一种集成了微处理器核心、存储器、输入输出接口和定时器计数器等功能的单芯片微型计算机。

在设计MCU时,需要注意以下几个方面。

一、功耗管理:MCU通常用于低功耗应用场景,因此功耗管理是设计中的重要考虑因素。

首先,选择适合应用需求的低功耗处理器核心,如ARM Cortex-M系列;其次,合理设计供电电路,采用多种节能技术,如功率管理单元(PMU)和智能电源管理等;此外,优化代码以降低功耗,如采用睡眠模式、动态电压频率调节等。

二、性能优化:MCU的性能优化主要包括两方面,一是提高处理器的计算能力,二是提高外设的响应速度。

在处理器方面,可以通过增加处理器的位宽、提高主频或者采用多核架构等方式提高计算能力。

在外设方面,可以采用DMA(Direct Memory Access)技术,减少处理器的负载,提高数据传输速度;同时,合理设计中断机制,确保外设的及时响应。

三、可靠性设计:可靠性设计是指MCU在工作过程中能够稳定可靠地运行。

首先,需要选择高品质的芯片供应商,确保芯片质量可靠;其次,合理设计供电电路,包括滤波电容、稳压电路等,保证电源稳定;此外,采用备份电源、故障检测和恢复机制等技术,提高系统的可靠性。

四、安全性设计:随着物联网的发展,MCU在安全性方面的设计变得愈发重要。

首先,需要采用安全芯片,具备硬件加密功能,保护数据的安全性。

其次,采用安全启动技术,确保系统的启动过程不受恶意攻击。

此外,合理设计访问控制机制、数据完整性校验等技术,提高系统的安全性。

五、软件开发:MCU的软件开发是整个设计过程中的关键环节。

首先,需要选择适合的开发工具和编程语言,如Keil MDK和C语言等。

其次,合理设计软件架构,包括任务调度、中断处理等。

此外,进行充分的测试和调试,确保软件的稳定性和可靠性。

六、外设选择:MCU通常需要与各种外设进行连接,因此在设计中需要选择合适的外设。

ARM芯片

ARM芯片ARM芯片(Advanced RISC Machine,高级精简指令集计算机)是一种基于精简指令集(RISC)设计思想的计算机微处理器架构,由ARM公司研发。

ARM芯片广泛用于各种移动设备、嵌入式系统和智能家居等领域,以其低功耗、高性能和低成本而闻名。

ARM芯片采用指令集中的精简指令,提供了相对较少但功能强大的指令,使得芯片设计更加简洁高效。

与传统的复杂指令集(CISC)不同,ARM芯片的指令更短、更简单,执行速度更快,并且具有更低的功耗。

这使得ARM芯片在移动设备领域得到广泛应用,如智能手机、平板电脑等。

ARM公司还通过核心协议(ARM Cortex)提供不同级别的指令集架构,以满足不同应用需求。

ARM Cortex-A系列面向高性能处理器,用于智能手机、平板电脑和移动终端设备;ARM Cortex-R系列面向实时应用,用于汽车电子、医疗设备等领域;ARM Cortex-M系列面向嵌入式系统,用于传感器、智能家居等领域。

ARM芯片的另一个突出特点是可定制性。

ARM公司提供了可许可(IP)设计的方式,允许其他公司自定义和定制ARM芯片,以满足其特定需求。

这使得ARM芯片在市场上非常灵活,可以根据不同厂商和设备制造商的需求进行定制,从而实现更好的性能和功耗平衡。

除了移动设备领域,ARM芯片还在嵌入式系统中得到广泛应用。

由于其低功耗、高性能和易于定制的特点,ARM芯片被广泛用于智能家居、工业自动化、物联网和医疗设备等领域。

在这些领域,ARM芯片可以提供高度集成的解决方案,同时保持低功耗和高稳定性。

未来,ARM芯片在人工智能(AI)和机器学习(ML)领域也有潜力得到更广泛的应用。

ARM公司已经推出了针对AI和ML工作负载的特定解决方案,例如ARM ML指令集和POP IP加速器,以提供更高的性能和效率。

总之,ARM芯片以其低功耗、高性能和易于定制的特点,在移动设备、嵌入式系统和智能家居等领域得到广泛应用。

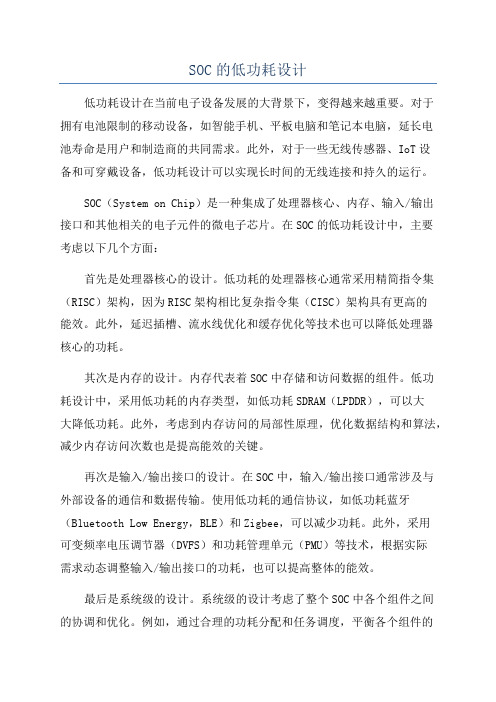

SOC的低功耗设计

SOC的低功耗设计低功耗设计在当前电子设备发展的大背景下,变得越来越重要。

对于拥有电池限制的移动设备,如智能手机、平板电脑和笔记本电脑,延长电池寿命是用户和制造商的共同需求。

此外,对于一些无线传感器、IoT设备和可穿戴设备,低功耗设计可以实现长时间的无线连接和持久的运行。

SOC(System on Chip)是一种集成了处理器核心、内存、输入/输出接口和其他相关的电子元件的微电子芯片。

在SOC的低功耗设计中,主要考虑以下几个方面:首先是处理器核心的设计。

低功耗的处理器核心通常采用精简指令集(RISC)架构,因为RISC架构相比复杂指令集(CISC)架构具有更高的能效。

此外,延迟插槽、流水线优化和缓存优化等技术也可以降低处理器核心的功耗。

其次是内存的设计。

内存代表着SOC中存储和访问数据的组件。

低功耗设计中,采用低功耗的内存类型,如低功耗SDRAM(LPDDR),可以大大降低功耗。

此外,考虑到内存访问的局部性原理,优化数据结构和算法,减少内存访问次数也是提高能效的关键。

再次是输入/输出接口的设计。

在SOC中,输入/输出接口通常涉及与外部设备的通信和数据传输。

使用低功耗的通信协议,如低功耗蓝牙(Bluetooth Low Energy,BLE)和Zigbee,可以减少功耗。

此外,采用可变频率电压调节器(DVFS)和功耗管理单元(PMU)等技术,根据实际需求动态调整输入/输出接口的功耗,也可以提高整体的能效。

最后是系统级的设计。

系统级的设计考虑了整个SOC中各个组件之间的协调和优化。

例如,通过合理的功耗分配和任务调度,平衡各个组件的工作负载,可以避免单个组件过度消耗能量。

此外,采用低功耗时钟源、电源管理和睡眠模式等策略,使得SOC在非活动状态下能够进入低功耗模式,从而延长电池的使用寿命。

综上所述,SOC的低功耗设计需要从处理器核心、内存、输入/输出接口和系统级等多个方面进行优化。

通过采用低功耗的技术和策略,可以降低功耗,延长电池寿命,从而提高电子设备的能效和用户体验。

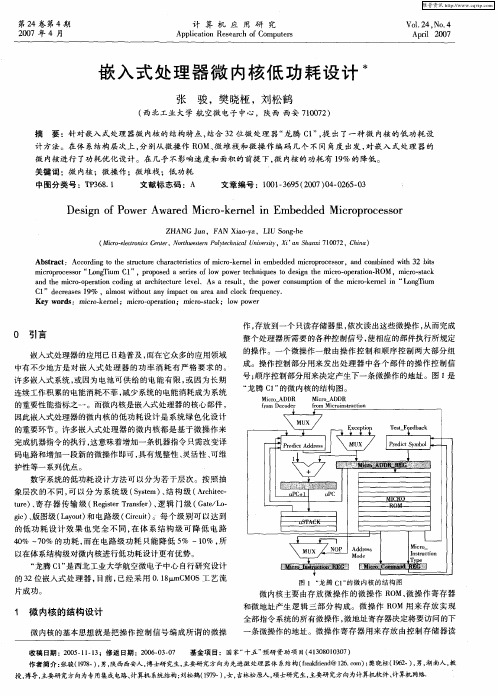

嵌入式处理器微内核低功耗设计

tr) 寄 存 器传 输 级 ( ei e Ta s r 、 ue 、 R gs r rnf ) 逻辑 门级 ( a / o t e G t L・ e

计 方 法。在体 系结构层 次上 , 别从微 操作 R 分 OM、 堆 栈 和微 操 作 编码 几个 不 同角度 出发 , 微 对嵌 入 式处 理 器的

微 内核进行 了功 耗优化 设计 。在 几乎 不影 响速度 和 面积的 前提 下 , 内核的 功耗有 1% 的 降低 。 微 9

关键词 :微 内核 ;微操 作 ;微 堆栈 ;低 功耗 中图分 类号 :T 3 8 1 P 6 . 文献标 志码 :A 文章 编号 :10 — 6 5 2 0 ) 4 0 6 - 3 0 13 9 ( 0 7 0 ・2 5 0 .

因此嵌入式处理器 的微 内核 的低 功耗设计 是 系统 绿色 化设计 的重要环节 。许多嵌入式处 理器 的微 内核都是 基于微 操作来 完成机器指令 的执行 , 这意味着增加一条机器指令 只需改 变译 码 电路和增加一段新 的微操作 即可 , 具有规整性 、 灵活性 、 可维

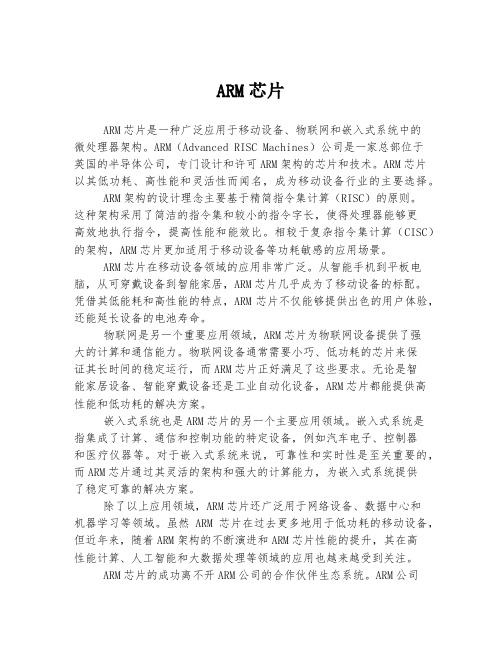

ARM芯片

ARM芯片ARM芯片是一种广泛应用于移动设备、物联网和嵌入式系统中的微处理器架构。

ARM(Advanced RISC Machines)公司是一家总部位于英国的半导体公司,专门设计和许可ARM架构的芯片和技术。

ARM芯片以其低功耗、高性能和灵活性而闻名,成为移动设备行业的主要选择。

ARM架构的设计理念主要基于精简指令集计算(RISC)的原则。

这种架构采用了简洁的指令集和较小的指令字长,使得处理器能够更高效地执行指令,提高性能和能效比。

相较于复杂指令集计算(CISC)的架构,ARM芯片更加适用于移动设备等功耗敏感的应用场景。

ARM芯片在移动设备领域的应用非常广泛。

从智能手机到平板电脑,从可穿戴设备到智能家居,ARM芯片几乎成为了移动设备的标配。

凭借其低能耗和高性能的特点,ARM芯片不仅能够提供出色的用户体验,还能延长设备的电池寿命。

物联网是另一个重要应用领域,ARM芯片为物联网设备提供了强大的计算和通信能力。

物联网设备通常需要小巧、低功耗的芯片来保证其长时间的稳定运行,而ARM芯片正好满足了这些要求。

无论是智能家居设备、智能穿戴设备还是工业自动化设备,ARM芯片都能提供高性能和低功耗的解决方案。

嵌入式系统也是ARM芯片的另一个主要应用领域。

嵌入式系统是指集成了计算、通信和控制功能的特定设备,例如汽车电子、控制器和医疗仪器等。

对于嵌入式系统来说,可靠性和实时性是至关重要的,而ARM芯片通过其灵活的架构和强大的计算能力,为嵌入式系统提供了稳定可靠的解决方案。

除了以上应用领域,ARM芯片还广泛用于网络设备、数据中心和机器学习等领域。

虽然ARM芯片在过去更多地用于低功耗的移动设备,但近年来,随着ARM架构的不断演进和ARM芯片性能的提升,其在高性能计算、人工智能和大数据处理等领域的应用也越来越受到关注。

ARM芯片的成功离不开ARM公司的合作伙伴生态系统。

ARM公司与众多半导体公司合作,许可其架构和技术,并且提供了丰富的开发工具和资源。

1302芯片

1302芯片1302芯片是一款微处理器芯片,由台湾公司联发科技(MediaTek)研发和制造。

该芯片采用先进的28纳米制程工艺,集成了ARM Cortex-A7处理器和ARM Mali-400 MP图形处理器,以实现高性能和低能耗的平衡。

下面将以1000字介绍1302芯片的主要特点和技术细节。

首先,1302芯片采用了ARM Cortex-A7处理器架构,该架构是一种低功耗、高度可扩展的处理器设计。

Cortex-A7处理器具有独特的big.LITTLE技术,可以与更高性能的Cortex-A15处理器相结合,实现大幅提升系统性能和功耗效率。

这种异构多核处理器设计可以根据实际需求自动调整使用的核心数量和频率,以平衡性能和能耗。

其次,1302芯片还集成了ARM Mali-400 MP图形处理器,为用户提供流畅的游戏和高清视频播放体验。

Mali-400 MP采用了高效的渲染引擎和灵活的着色架构,支持OpenGL ES 2.0和OpenVG 1.1等多种图形标准,可以处理复杂的3D图形和多媒体内容。

此外,1302芯片还支持多种高速接口和通信标准,包括USB 2.0、HDMI、SDIO和MMC等。

这些接口可以快速连接外部设备,如摄像头、显示器和存储卡等。

此外,1302芯片还支持无线通信标准,如WiFi、蓝牙和GPS等,可以实现无线连接和位置服务功能。

在能耗管理方面,1302芯片采用了先进的功耗优化技术,包括动态电压频率调整(DVFS)和智能功耗管理(ISP)等。

DVFS技术可以根据负载情况调整处理器的工作频率和电压,以实现最佳的能耗和性能平衡。

ISP技术可以对图像和视频进行实时处理和优化,以降低功耗和提升用户体验。

最后,1302芯片还具有安全性和可扩展性。

它提供了硬件级别的安全功能,包括高级加密标准(AES)、数据完整性校验(CRC)和随机数生成器等。

这些安全功能可以保护用户数据的机密性和完整性。

此外,1302芯片还支持软件升级和扩展存储,以适应不断变化的应用需求。

6502芯片

6502芯片6502芯片是一款8位微处理器芯片,由摩斯技术公司(MOS Technology)于1975年推出,并由苹果公司在1976年发布的Apple I计算机中使用。

6502芯片是当时市场上最便宜的微处理器之一,因此很受欢迎,被广泛应用于个人电脑、游戏机和其他各种电子设备中。

6502芯片的主要特点如下:1. 8位结构:6502芯片是一款8位微处理器,意味着它可以同时处理8位的数据。

每个字节可以存储8个二进制数字,范围从0到255。

2. 低功耗:6502芯片是基于MOS技术的,具有较低的功耗。

它采用了静态设计,只有在电压改变时才会消耗能量。

3. 低成本:6502芯片的制造成本较低,这是由于它的设计简单,特别注重经济性。

这使得6502芯片成为一种广泛应用于大众市场的处理器。

4. 低运行频率:6502芯片的最高时钟频率为1 MHz,比较低,但足够满足当时的计算需求。

5. 简化指令集:6502芯片具有一种精简的指令集架构,包括56条指令。

这些指令可以直接操作CPU寄存器和内存,加快了数据处理速度。

6. 易于编程:6502芯片使用汇编语言进行编程,汇编语言较为直接、简单,可以更好地控制和优化程序的执行。

6502芯片的应用广泛,特别是在个人电脑领域。

它被用于苹果公司的Apple II系列电脑、Atari游戏机、Commodore 64和BBC Micro等。

这些机器在当时非常受欢迎,为个人电脑的普及做出了重要贡献。

尽管6502芯片已经过时,但它仍然被一些人用于制作复古计算机和模拟器。

此外,6502的设计思想和部分指令集架构仍然影响着现代的微处理器设计。

总结起来,6502芯片是一款经典的8位微处理器芯片,具有低功耗、低成本和简化指令集等特点。

它对个人电脑的发展起到了重要的推动作用,并在当时广泛应用于各种电子设备中。

SoC设计中的低功耗技术

关键词

S C R L 低 功耗 设计 o T

1 引 言

随着深亚 微米 集成 电路 工 艺 技术 的突 破 , 可 以将用 于完成 某一 应用 领域 的一个 或多个 微处 理 器、 数字/ 模拟 转换 器 、 储 器 、 拟 及 接 口、 制 存 模 控

△ t 间 内的平均 功耗 。两 者意 义 不 同 ,有不 同 时 的应用 背 景和优 化策 略 。通 常两者 被笼 统地概 括

的器件和在数百兆 时钟频率下工作 , 将会有数 十

瓦的功耗 。 巨大 的功 耗给使 用封 装 和可靠性 方 面 都 带来 了问题 。 进入 SC时代 , o 低功耗 已经成为与面积 和性 能 同等重要 的设 计 目标 , 特 定领 域 , 在 功耗指 标 甚 至 成为第一大要素 。随着小型化 的需 求越来越 强烈 , 像手持设备 中的各 种应 用要 求其 中芯片 的速 度越 来越快 , 面积越来越大 , 能化越来 越高 , 然导 智 这必 致芯片 的功耗 呈指 数增 加 。SC技术 的发 展使 得 o 单个芯片集成所有 的处理部件成 为可能 , 处理 这些 部件可 以包括 基本 的晶体 管 、 同 的处理 器 核 、 不 内 存单元甚至模 拟单元 。包含 了如此众 多 的部 件 , 功 耗设计 将成为 一个 关键 而且 复 杂 的课题 。同 时 由 于电池 的技术相 对 落后 , 发展 缓慢 , 而快 速 散热 的 要求 又会导致 封装 和制 冷成本提高 , 大导致 温 功耗

减少系统 的面 积 , 降低 系统 成本 , 大地提 高系统 极 的性能价 格 比。SC系统 因 为集 成有 百万 门 以上 o

微处理器的低功耗芯片设计技术

维普资讯

l

另 一 种 常 用 的时 钟 技 术 就 是 可 变 频 率 时 钟 。它 根 据

2 常用 的低 功 耗设 计 技 术

低 功耗 设 计 是 一 个 复 杂 的综 合 性 课 题 。就 流程 而 言 ,

系 统 性 能 要 求 , 置 适 当 的 时 钟 频 率 以 避 免 不 必 要 的 功 配 耗 。门 控 时 钟 实 际 上 是 可 变 频 率 时 钟 的 一 种 极 限情 况 ( 即 只 有 零 和 最 高 频 率 两 种 值 ) 因 此 , 变 频 率 时 钟 比门控 时 , 可

lI0 _/

以其 独 特 的低 功 耗 设 计 技 术 和 非 凡 的超 低 功耗 表 现 , 业 在

界引 起 巨大 轰 动 , 发 了低 功 耗 处 理 器设 计 的激 烈 竞 争 。 引

在 20 0 6年 的 英 特 尔 开 发 者 论 坛 大 会 (n e De eo e Itl v lp r

积 转 为对 性 能 、 积 、 耗 的 综 合 要 求 。而 微 处 理 器 作 为 面 功

数 字 系 统 的 核 心 部 件 , 低功 耗 设 计 对 降低 整 个 系 统 的功 其 耗 具 有 重 要 的意 义 。

20 0 0年 年 初 , a s t 司 推 出 了 C u o Trn mea公 r s e处 理 器 ,

钟 技 术 更 加 有 效 , 需 要 系 统 内嵌 时 钟 产 生 模 块 P L, 但 L 增 加 了 设 计 复 杂 度 。去 年 I tl 司 推 出 的 采 用 先 进 动 态 功 ne 公 耗 控 制 技 术 的 Mo tct ne i o处 理 器 , 利 用 了 变 频 时 钟 系 就 统 。该 芯 片 内嵌 一 个 高 精 度 数 字 电 流 表 , 用封 装 上 的微 利

一种低功耗,高性能微处理器复位芯片的设计

关 键 词 :复位 芯 片 ;带 隙 基 准 ; 振 荡 器 ;逻 辑控 制

中图 分 类 号 : T N 4 7 文 献 标识 码 : A 文 章 编 号 :1 6 7 4 — 6 2 3 6 ( 2 0 1 3 ) 1 7 — 0 1 9 0 — 0 4

A d e s i g n o f a l o w- p o we r , l I i g l I - p e r f o r ma n c e mi c r o p r o c e s s o r r e s e t c h i p

非 常 重要 的作 用 , 本 文研 究 并 设 计 一 种 低 功 耗 , 高性 能 的 复位 芯 片 , 可 以在 系统 上 电 , 掉 电 的 情 况 下 向微 处 理 器提 供

复 位 信 号 。 当 电源 电压 低 于 预 设 的 门槛 电压 时 。 输 出 复位 信 号 并在 电 源 电 压 恢 复 到 门槛 电 压 以 上 继 续持 续 复 位 一 段

时间, 实现 整 个 系统 的 平 稳 恢 复 , 复位信 号低电平有 效。该芯 片采 用 C M S C 0 3 5标 准 C M O S工 艺 实 现 , 采用C a d e n c e

S p e c t r e仿 真 , 工作 电流 仅 为 l 0 A。该 芯 片 已成 功 应 用 于 工 业 类 控 制 系统 中 。

第. 1 7

电子设 计工 程

E l e c t r o n i c D e s i g n En g i n e e r i n g

2 0 1 3年 9月

Se p. 201 3

一

种低功耗 , 高性能微处理器 复位芯 片的设计

WU T o n g .Z HANG T a o

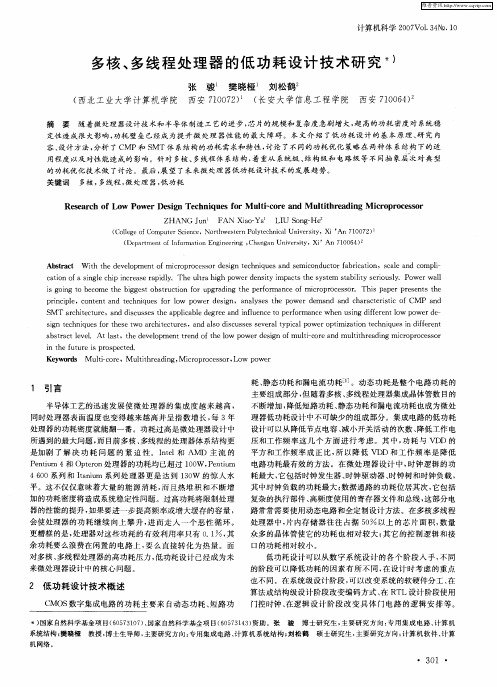

多核、多线程处理器的低功耗设计技术研究

用程度 以及 对性 能造成 的影 响。针 对多核 、 多线程体 系结构 , 着重从 系统级 、 结构级和 电路 级等 不同抽 象层 次对典型

的功 耗 优 化 技 术做 了讨 论 。 最后 , 望 了未 来 微 处 理 器低 功 耗 设 计 技 术 的发 展 趋 势 。 展

关键 词 多核 , 多线 程 , 处理 器 , 功 耗 微 低

Re e r h ofLo Po r De i n Te h qu s f r M u t— o e a d M u tt e di ir pr c s o s a c w we sg c ni e o lic r n lihr a ng M c o o e s r

ZHANG u F Jn AN a — LI S n — Xio Ya U o g He

( l geo mp t rS inc ,No t we tr lte ia ie st ,Xi’ 1 0 2) Col fCo u e ce e e rh sen Poye hnc lUnv r iy An 7 0 7 ( p rme fI fr ain En i e ig . De a t nto no m to gnern Cha g n Unv riy.Xi n a ie st ’An 7 0 6 1 0 4)

摘 要 随 着微 处理 器设 计 技 术和 半 导体 制造 3 艺 的进 步 , 片的 规 模 和 复 杂度 急剧 增 大 , 高的 功 耗 密 度 对 系统 稳 - 芯 超

定性 造 成 很 大 影响 , 耗 壁 垒 已经 成 为 提 升 微 处 理 器 性 能 的 最 大 障 碍 。本 文 介 绍 了低 功 耗 设 计 的 基 本 原 理 、 究 内 功 研 容、 计方法 , 析 了 C 设 分 MP和 S MT 体 系结 构 的 功 耗 需 求 和 特 性 , 论 了不 同 的 功耗 优 化 策 略 在 两 种 体 系 结 构 下 的 适 讨

低功耗设计方法范文

低功耗设计方法范文低功耗设计方法是指在电子产品设计过程中,通过合理的电路设计和软件优化,实现产品在正常工作状态下的电力消耗最小化。

低功耗设计方法对于节省能源、延长电池寿命、减少产品发热和环境保护等方面都具有重要意义。

以下是几种低功耗设计方法:1.选择低功耗组件:在电子产品设计中,选择低功耗的关键元件是降低功耗的一个有效方法。

例如,选择低功耗的微处理器、传感器和发射接收模块等元件,可以降低整个系统的功耗。

2.优化电源管理电路:电源管理电路对于整个系统的功耗非常重要。

通过采用高效的降压电源方案,可以减少能量损耗;通过设计适合产品需要的睡眠模式和待机模式,可以降低系统在闲置状态下的功耗。

3.优化电路布局和走线:合理的电路布局和走线可以减少电路的阻抗,降低功耗。

例如,减少电路的长度和厚度,降低走线的阻抗和电流损耗。

此外,通过使用最短路径和最小电容的连接方式,可以进一步降低功耗。

4.优化软件算法:软件优化是低功耗设计的关键。

通过优化算法,减少不必要的运算和数据存储,可以降低CPU的功耗。

此外,合理使用休眠和唤醒机制,以及调整任务优先级,都可以有效地降低系统功耗。

5.采用功耗管理策略:在设计时加入功耗管理功能,如动态频率调整、智能功耗调整等策略,可以根据系统负载和需求实时调整系统电压和频率,以达到最佳功耗效果。

6.使用节能模式:在电子产品设计中,引入特定的节能模式可以降低系统功耗。

例如,通过调整显示屏的亮度和背光强度,关闭不必要的外部设备,调整无线信号强度等方式,可以大幅度降低整个系统的功耗。

7.合理使用定时器和中断:定时器和中断是控制系统状态和响应外部事件的重要组成部分。

通过合理设置定时器和中断的参数,可以在必要时唤醒系统,以及在系统闲置时进入睡眠模式,从而降低功耗。

总之,通过以上低功耗设计方法,可以在满足产品功能和性能要求的前提下,降低整个系统的功耗,延长电池寿命,达到节能环保的目的。

在电子产品设计中,低功耗设计是一个非常重要的趋势,也是未来产品发展的方向之一。

低功耗技术发展

低功耗技术发展

目前的低功耗设计主要从芯片设计和系统设计两个方面考虑。随着半导 体工艺的飞速发展和芯片工作频率的提高,芯片的功耗迅速增加,而功耗增加 又将导致芯片发热量的增大和可靠性的下降。因此,功耗已经成为深亚微米集 成电路设计中的一个重要考虑因素。为了使产品更具竞争力,工业界对芯片设 计的要求已从单纯追求高性能、小面积转为对性能、面积、功耗的综合要求。 而微处理器作为数字系统的核心部件,其低功耗设计对降低整个系统的功耗具 有重要的意义。

在嵌入式系统的设计中,低功耗设计(Low-Power Design)是许多设计人 员必须面对的问题,其原因在于嵌入式系统被广泛应用于便携式和移动性较强 的产品中去,而这些产品不是一直都有充足的电源供应,往往是靠电池来供电, 所以设计人员从每一个细节来考虑降低功率消耗,从而尽可能地延长电池使用 时间。事实上,从全局来考虑低功耗设计已经成为了一个越来越迫切的问题。

为此,数模电路混合设计的工艺兼容性是一个值得探讨的问题。随着工艺 尺寸和电源电压的减小,模拟集成电路的设计将遇到诸多调整,采,将是 今后努力的方向。

欢迎指正!

人们对电子产品可移动化要求的提高受到电池 容量发展的限制,低压低功 耗设计越来越受到人们的重视。模拟电路的低压低功耗设计技术受电路工作原 理与数字电路兼容性的限制,面临着较大的挑战。今后可能的发展方向主要有:

一、在现有工艺下,进一步降低电源电压。采取的措施可以从改进电路拓扑 结构入手,使电路能在阈值电压一定的情况下降低电源电压来工作。Rout,S.早 在2000年就在普通工艺下实现了在1V电源电压下工作的开关电流单元。

低功耗技术发展

二、研究新的工艺,使模拟电路与数字电路能更好地兼容,降低所有器件的 漏电流,提供电路处理的信噪比。文献指出,采用新型的双栅MOS工艺,利用背栅 具有降低器件阈值电压的特性,可以保证在不牺牲电路性能的基础上,让设计的 自适应两级运算放大器电路在电源电压低至0.5V时依然能正常工作。

低功耗设计技术()(PDF)

基于Leon处理器的SoC的功耗特征

LEON处理器占据了44%, 存储器控制器占据了14%, AHB总线功耗为9% 两个UART的功耗占据了10%, 定时器功耗也达到8%。

基于字典的自适应编码

• N位数据被分为了三个区域,[N-1, WI], [WI-1, WO], [WO-1, 0](N=32, WO=6, WI=3),[WO-1, 0] 为固定传 输区域

• 以[WI-1, WO]作为访问字典的地址 ,并将字典中的数据与[N-1, WI]的 数据比较,

– 如果相同:

• 在数据总线方面,还包括 BITS, 码表编码,基于概率的 映射等等。

• 这些算法目的是减少总线上的 信号翻转率,但是过于复杂的 编解码方案可能导致额外的功 耗,甚至有超过在总线上节省 的功耗。

基于AHB总线编码的实际案例

• 有两个主要特点:

– 每个字节都有相应的INV标志位来单独 编解码。

– 外存包括两个体一个为8位的数据存储 器,一个为1位的INV标志存储器。

• 数据路径(包括执行部件,总线, 寄存器文件)

• 片上存储器(Cache, 转移缓冲) • 控制与I/O

Alpha 21264的功耗特征

DEC的21264于1998年研制成功,基本参数: 0.35工艺,15.2M个晶体管,2.2V, 600MHZ, 6路超标量乱序执行,64KB L1指令Cache和64KB L1 数据Cache, 平均功耗72W(最大95W),平均电流32.7Amps。

Off-Chip Memory

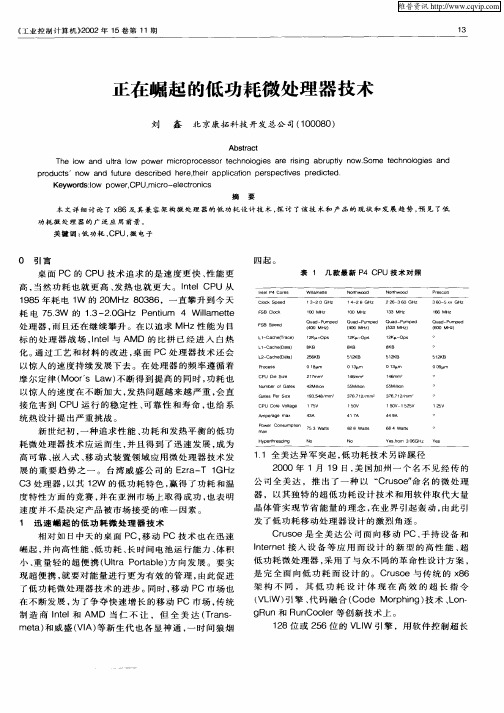

正在崛起的低功耗微处理器技术

处 理 器 , 且还 在 继 续 攀 升 。在 以 追 求 MH 而 z性 能 为 目 标 的 处 理 器 战 场 ,ne 与 AMD 的 比拼 已 经 进 入 白 热 It l 化 。 过 工 艺 和材 料 的 改 进 , 面 P 通 桌 C处 理 器 技 术 还 会

统 热 设 计 提 出严 重 挑 战 。

新 世 纪 初 , 种 追 求 性 能 、 耗 和 发 热 平 衡 的低 功 一 功

耗 微 处 理 器 技 术 应 运 而生 , 且 得 到 了迅 速 发 展 , 为 并 成 高 可 靠 、 入 式 、 动 式装 置领 域 应 用 微 处 理 器 技 术 发 嵌 移 展 的 重 要 趋 势 之 一 。 台 湾 威 盛 公 司 的 E r — GHz za T 1 C3处 理 器 , 其 1 W 的 低 功 耗 特 色 , 得 了功 耗 和温 以 2 赢 11 全 美 达 异军 突 起 , 功 耗 技 术 另 辟 蹊 径 . 低 20 0 0年 1月 1 日 , 国加 州 一 个 名 不 见 经 传 的 9 美

p o c s n w a d f t r d cr e h r t ei app i a i n pe s e t e pr c e r du t o n u u e es i d e e, b h r l t rp ci s c o v edit d.

Ke w o d : w wer y r sl o po , CPU. ir eI t is m c O— ec r c On

以惊 人 的速 度 持 续 发 展下 去 。 在 处理 器 的频 率 遵 循 着

MEMS技术在电子设计中的应用

MEMS技术在电子设计中的应用MEMS技术(微机电系统技术)是一种将微型传感器、执行器和微处理器集成在一起的技术,具有小巧、高效、低功耗等优点,被广泛应用于电子设计领域。

在电子设计中,MEMS技术可以发挥重要作用,为设备和系统提供更高的性能、更多的功能和更好的用户体验。

一方面,MEMS技术在电子设计中的应用主要体现在传感器方面。

由于MEMS传感器具有体积小、响应速度快、能耗低等特点,因此在电子产品中得到广泛应用。

比如,加速度传感器、陀螺仪、压力传感器等MEMS传感器可以用于智能手机、智能手表、健康监测设备等产品中,实现自动调节亮度、智能感应操作、高精度定位等功能。

此外,MEMS传感器还被广泛应用于汽车电子设计中,实现车辆稳定控制、自动泊车、碰撞预警等功能,提升了车辆的安全性和舒适性。

另一方面,MEMS技术在电子设计中还具有广泛的应用前景。

例如,MEMS执行器可以用于振动马达、微型投影仪、微型喷墨打印头等产品中,实现高精度的控制和驱动。

此外,MEMS技术还可以应用于微型光学器件的设计,比如微型声纳、微型干涉仪等,提升了光学传感器的性能和精度。

在无线通信设备中,MEMS 技术也被广泛应用,例如MEMS滤波器、MEMS天线等在射频系统中的应用,实现了高频率、高速率的无线通信传输。

综上所述,MEMS技术在电子设计中的应用前景广阔,可以为电子产品提供更高的性能、更多的功能和更好的用户体验。

随着MEMS技术的不断进步和发展,相信在未来会有更多新的应用场景和创新设计出现,推动电子产品的不断升级和创新。

MEMS技术的应用将成为电子设计领域的重要发展方向,为人们的生活带来更多便利和乐趣。

微型化与低功耗设计技术(1)幻灯片

单片机的多功能开展,集成了越来越多的外围电路 的功能。A/D、D/A(PWM)、LCD驱动、RAM、 ROM(EPROM、FLASH)等。

通讯一般采用线数最少的串行方式,低速用RS-232, 高速用USB,近距离无线通讯采用红外通讯(IrDA) 和宽带无线技术。

一般不配打印机,显示器大多采用低功耗的段式或 点阵图形液晶显示器。

第三节 微型化与低功耗设计

1. CMOS集成电 路与低功耗设计

CMOS数字集 成电路的静态 功耗几乎为0。

如接法适宜, 可降低到uA级

CMOS数字集成电路的动态功耗

发生在逻辑状态转换的 瞬间,由两个分量构成。

跳变时两个场效应管同 时导通所引起的尖峰电 流。与转换时间有关。

逻辑门节点电容的充电 电流。等于面积与重复 频率的乘积。

现场可编程逻辑器件(FPLD)。 PAL(可编程阵列逻辑)和GAL(通用阵列逻

辑)。 FPGA(现场可编程门阵列)和CPLD(复杂

可编程逻辑器件) 。

新兴技术的影响

硅微加工技术

在硅材料上进展微米级水平的三维加工 技术,包含模拟、数字电路和执行装置 的微机电系统(MEMS)。

可用于人体姿态监测的加速度传感器, 在3mmX3mm的芯片上加工出机械构造, 同时还有放大、信号处理和自校正电路。

电子元器件封装工艺的不断革新

外表安装技术(SMT)取代穿孔式安装(THT)。 外表安装元件(SMC)。 ቤተ መጻሕፍቲ ባይዱ表安装器件(SMD)。

大量以低功耗为目标的电子元器件问 世

以MSP430为代表的微处理器可工作在 uA级电流。

以3V供电的反射式图形液晶显示器(LCD) 模块耗电不到1mA。

ASIC技术的开展

低功耗微处理器监控芯片的设计

monitor system power voltage function,while the most static era-rent was only 3¨A.This chip This

can

realize the normal function requiring finished

no

external components. and layout.The technical target

结果表明,该带隙基准能够在lkts的时间内启动,产生温度特性和电压特性都非

常好的基准电压,而只用1心的电流。

通过设计双极型差分对管避免了常规带

隙中CMOS差分对管带来的失调问题, 从而为提高整个微处理器监控电路的各 方面性能奠定了基础: 2)系统时钟需要使用片肉一个振荡器,而且要在电源电压高于1.2V时就可 以工作,设计时利用模拟电路知识设计了一个可以工作在1.2V以上电源电压的 振荡器,该振荡器平均工作电流只有1.3“A,而且当系统不需要其工作时可以彻 底关断,完全不耗电流,从而实现低功耗的要求: 3)由于微处理器监控电路有多种不同的功能组合,在设计时利用金属选择

上海大学硕士学位论文

够掌握低功耗微处理器监控电路的设计和生产,将对我国军事、医疗、通信等方 面的发展有很大的促进作用。

1.3论文的主要研究内容及创新

1.3.1主要研究内容 本论文是以作者攻读硕士学位期间承担课题的工作为基础,对多种微处理器 监控电路结构及基本特性进行了仔细的研究,最终确定没计一款具有上电复位 (PowerOnRcset,POR)、掉电复位和手动复位以及看门狗外加一个系统电源电 压监控等五大功能的微处理器监控电路。经过近一年的研究工作,本文完成了基 于标准CMOS工艺的低功耗的微处理器监控集成电路设计,其中包括了带隙电 压基准、带迟滞的箝位比较器、CMOS振荡器、看门狗电路、逻辑电路、电阻分 压网络、手动复位电路等内部模块电路的设计。所设计完成的微处理器监控电路 可以在上电时维持200ms的延迟,有可监控1.6秒时间的看门狗电路,而静态电 流只有3uA。

982芯片方案

982芯片方案一、引言在数字时代的今天,微处理器芯片成为了各行各业的核心组成部分。

在这个快速发展的领域,982芯片方案应运而生。

本文将对982芯片方案进行全面的介绍和分析。

二、背景982芯片方案是一种新型的微处理器芯片方案,由一家领先的科技公司研发出来。

该公司秉承创新、高效、可靠的理念,旨在为广大用户提供性能卓越的解决方案。

三、982芯片方案的特点1. 高性能:982芯片方案采用了先进的制程工艺和设计技术,具有卓越的计算和处理能力。

无论是运行复杂的应用程序还是处理大量数据,982芯片方案能够快速高效地完成任务。

2. 低功耗:982芯片方案在高性能的同时,注重功耗的优化。

通过精确的能量管理和电源控制技术,能够在不降低性能的情况下实现功耗的极低化,延长设备的续航时间。

3. 强安全性:982芯片方案采用了多层次的安全防护机制,包括硬件加密模块、数据保护控制等。

能够有效防止恶意攻击和数据泄露,保障用户的隐私和信息安全。

4. 多样化应用:982芯片方案具有广泛的应用领域。

无论是智能手机、智能家居、工业控制,还是物联网等领域,982芯片方案都能够提供可靠的解决方案,并且能够满足不同行业、不同场景下的需求。

5. 易集成:982芯片方案在设计时充分考虑了集成性,具有较好的兼容性和可扩展性。

不仅能够与其他硬件设备无缝衔接,还能够方便地升级和扩展功能,提供更多的发展空间。

四、982芯片方案的优势1. 技术领先:982芯片方案引入了最新的芯片制造技术和设计理念,处于行业的前沿地位。

性能、功耗、安全等方面的优势使得982芯片方案成为第一选择。

2. 资源丰富:研发982芯片方案的公司拥有丰富的技术积累和研发资源,能够保证方案的稳定性和可靠性。

并且,公司还提供完善的技术支持和售后服务,为用户提供全方位的支持。

3. 市场竞争力:由于982芯片方案的高性能、低功耗和广泛应用的特点,使得其具有较强的市场竞争力。

用户可以借助982芯片方案提高产品竞争力,拓展市场份额。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

微处理器的低功耗芯片设计技术[日期:2008-1-7] 来源:单片机及嵌入式系统应用作者:同济大学周俊林正浩 [字体:大中小]摘要随着半导体工艺的飞速发展和芯片工作频率的提高,功耗已经成为深亚微米集成电路设计中的一个重要考虑因素。

本文介绍了低功耗微处理器的研究现状,讨论了几种常用的微处理器低功耗设计技术。

最后,对夸后低功耗微处理器设计的研究方向进行了展望。

关键词微处理器功耗低功耗芯片设计随着半导体工艺的飞速发展和芯片工作频率的提高,芯片的功耗迅速增加,而功耗增加又将导致芯片发热量的增大和可靠性的下降。

因此,功耗已经成为深亚微米集成电路设计中的一个重要考虑因素。

为了使产品更具竞争力,工业界对芯片设计的要求已从单纯追求高性能、小面积转为对性能、面积、功耗的综合要求。

而微处理器作为数字系统的核心部件,其低功耗设计对降低整个系统的功耗具有重要的意义。

2000年年初,Transmeta公司推出了Crusoe处理器,以其独特的低功耗设计技术和非凡的超低功耗表现,在业界引起巨大轰动,引发了低功耗处理器设计的激烈竞争。

在2006年的英特尔开发者论坛大会(Intel DeveloperForum)上,英特尔展示了多款基于下一代技术的微处理器。

其中,Metom主要用于笔记本电脑,最大功耗仅有5W,而将于2 006年底上市的超低电压版Merom的功耗则只有0.5W;Conroe主要面向台式机,其最大功耗为65W,远远低于现有Pentium 4处理器的95W;服务器处理器Woodcrest的最大功耗为80W,而现有的Xeon处理器的功耗为110W。

本文首先介绍了微处理器的功耗来源,重点介绍了常用的低功耗设计技术,并对今后低功耗微处理器设计的研究方向进行了展望。

1 微处理器的功耗来源研究微处理器的低功耗设计技术,首先必须了解它的功耗来源。

高层次仿真得出的结论如图1所示。

从图1中可以看出,时钟单元(Clock)功耗最高,因为时钟单元有时钟发生器、时钟驱动、时钟树和钟控单元的时钟负载;数据通路(Datapath)是仅次于时钟单元的部分,其功耗主要来自运算单元、总线和寄存器堆。

除了上述两部分,还有存储单元(Memory),控制部分和输入/输出(Control,I/O)。

存储单元的功耗与容量相关。

如图2所示,CMOS电路功耗主要由3部分组成:电路电容充放电引起的动态功耗,结反偏时漏电流引起的功耗和短路电流引起的功耗。

其中,动态功耗是最主要的,占了总功耗的90%以上,表达式如下:式中:f为时钟频率,C1为节点电容,α为节点的翻转概率,Vdd为工作电压。

2 常用的低功耗设计技术低功耗设计足一个复杂的综合性课题。

就流程而言,包括功耗建模、评估以及优化等;就设计抽象层次而言,包括自系统级至版图级的所有抽象层次。

同时,功耗优化与系统速度和面积等指标的优化密切相关,需要折中考虑。

下面讨论常用的低功耗设计技术。

2.1 动态电压调节由式(1)可知,动态功耗与工作电压的平方成正比,功耗将随着工作电压的降低以二次方的速度降低,因此降低工作电压是降低功耗的有力措施。

但是,仅仅降低工作电压会导致传播延迟加大,执行时间变长。

然而,系统负载是随时间变化的,因此并不需要微处理器所有时刻都保持高性能。

动态电压调节DVS(Dynarnic Voltage Scaling)技术降低功耗的主要思路是根据芯片工作状态改变功耗管理模式,从而在保证性能的基础上降低功耗。

在不同模式下,工作电压可以进行调整。

为了精确地控制DVS,需要采用电压调度模块来实时改变工作电压,电压调度模块通过分析当前和过去状态下系统工作情况的不同来预测电路的工作负荷。

2.2 门控时钟和可变频率时钟如图1所示,在微处理器中,很大一部分功耗来自时钟。

时钟是惟一在所有时间都充放电的信号,而且很多情况下引起不必要的门的翻转,因此降低时钟的开关活动性将对降低整个系统的功耗产牛很大的影响。

门控时钟包括门控逻辑模块时钟和门控寄存器时钟。

门控逻辑模块时钟对时钟网络进行划分,如果在当前的时钟周期内,系统没有用到某些逻辑模块,则暂时切断这些模块的时钟信号,从而明显地降低开关功耗。

图3为采用“与”门实现的时钟控制电路。

门控寄存器时钟的原理是当寄存器保持数据时,关闭寄存器时钟,以降低功耗。

然而,门控时钟易引起毛刺,必须对信号的时序加以严格限制,并对其进行仔细的时序验证。

另一种常用的时钟技术就是可变频率时钟。

它根据系统性能要求,配置适当的时钟频率以避免不必要的功耗。

门控时钟实际上是可变频率时钟的一种极限情况(即只有零和最高频率两种值),因此,可变频率时钟比门控时钟技术更加有效,但需要系统内嵌时钟产生模块PLL,增加了设计复杂度。

去年Intel公司推出的采用先进动态功耗控制技术的Montecito处理器,就利用了变频时钟系统。

该芯片内嵌一个高精度数字电流表,利用封装上的微小电压降计算总电流;通过内嵌的一个32位微处理器来调整主频,达到64级动态功耗调整的目的,大大降低了功耗。

2.3 并行结构与流水线技术并行结构的原理是通过牺牲面积来降低功耗。

将一个功能模块复制为n(n≥2)个相同的模块,这些模块并行计算后通过数据选择器选择输出,采用二分频的并行结构,如图4所示。

并行设计后,由于有多个模块同时工作,提高了吞吐能力,可以把每个模块的速度降低为原来的l/n。

根据延时和工作电压的线性关系,工作电压可以相应降低为原来的l/n,电容增大为原来的n倍,工作频率降低为原来的l/n,根据式(1)功耗降低为原来的1/n2。

并行设计的关键是算法设计,一般算法中并行计算的并行度往往比较低,并行度高的算法比较难开发。

例如:若原模块的功耗为P=a×CL×V2dd×f,采用二分频结构,由于增加了一个模块和数据选择器,整个电容负载为2.2CL,工作频率为f/2,工作电压可以降为O.6 V,则其功耗为:由此可见,二分频并行结构在保持原有电路性能的同时降低了60%的功耗。

流水线技术本质上也是一种并行。

把某一功能模块分成n个阶段进行流水作业,每个阶段由一个子模块来完成,在子模块之间插入寄存器,如图5所示。

若工作频率不变,对某个模块的速度要求仅为原来的1/n,则工作电压可以降低为原来的1/n,电容的变化不大(寄存器面积占的比例很小),功耗可降低为原来的1/n2,面积基本不变,但增加了控制的复杂度。

例如,若原模块的功耗为P=α×C1×V2dd×f,采用流水线技术,由于增加了寄存器,整个电容负载为1.2CL,工作频率不变,工作电压降为0.6 V,则其功耗为:由此可见,流水线技术能显著降低系统功耗。

通过流水线技术和并行结构降低功耗的前提是电路工作电压可变。

如果工作电压固定,则这两种方法只能提高电路的工作速度,并相应地增加了电路的功耗。

在深亚微米工艺下,工作电压已经比较接近阈值电压,为了使工作电压有足够的下降空间,应该降低阔值电压;但是随着阈值电压的降低,亚阈值电流将呈指数增长,静态功耗迅速增加。

因此,电压的下降空间有限。

2.4 低功耗单元库设计低功耗单元库是降低功耗的一个重要方法,包括调整单元尺寸、改进电路结构和版图设计。

用户可以根据负载电容和电路延时的需要选择不同尺寸的电路来实现,这样会导致不同的功耗,因此可以根据需要设计不同尺寸的单元。

同时,为常用的单元选择低功耗的实现结构,如触发器、锁存器和数据选择器等。

2.5 低功耗状态机编码状态机编码对信号的活动性具有重要影响,通过合理选择状态机状态的编码方法,减少状态切换时电路的翻转,可以降低状态机的功耗。

其原则是:对于频繁切换的相邻状态,尽量采用相邻编码。

例如:Gray码在任何两个连续的编码之间只有一位的数值不同,在设计计数器时,使用Gray码取代二进制码,则计数器的改变次数几乎减少一半,显著降低了功耗;在访问相邻的地址空间时,其跳变次数显著减少,有效地降低了总线功耗。

2.6 Cache的低功耗设计作为现代微处理器中的重要部件,Cache的功耗约占整个芯片功耗的30%~60%,因此设计高性能、低功耗的Cach结构,对降低微处理器的功耗有明显作用。

Cache低功耗设计的关键在于降低失效率,减少不必要的操作。

通常用来降低Cache功耗的方法有以下两种:一种是从存储器的结构出发,设计低功耗的存储器,例如采用基于CAM的Cache结构;另一种是通过减少对Cache的访问次数来降低功耗。

以上主要是从硬件的角度来实现功耗的降低。

除了硬件方法,通过软件方面的优化,也能显著地降低功耗。

例如:在Crusoe处理器中,采用高效的超长指令(VLIW)、代码融合(Code Morphing)技术、LongRun电源管理技术和RunCooler工作温度自动调节等创新技术,获得了良好的低功耗效果。

3 微处理器的低功耗设计研究展望功耗是微处理器设计长期面临的问题,分析当前的研究状况,未来的低功耗微处理器设计研究有如下发展趋势:首先,系统级的低功耗设计研究。

抽象层次越高,采用低功耗技术功耗可降低的比例越大。

其次,面向功耗的软硬件协同设计。

而向功耗的软硬件协同设计可以获得功耗优化的系统架构,再配合有效的功耗管理,可以大大降低最终的功耗。

再次,异步电路的研究。

同步电路的时钟功耗在整个系统的功耗中占了相当大的比例。

异步逻辑无需全局时钟,而是采用握手信号协调模块问的工作,减少了时钟驱动和同步电路中很多不必要的翻转,从而有效地降低了功耗。

然而,异步电路实现困难,且缺乏EDA软件的支持,因而还有待于进一步的研究。

4 结论本文介绍了低功耗微处理器的研究现状,讨论了几种常用的微处理器低功耗设计技术,展望了低功耗微处理器设计研究的发展趋势。

随着对高性能和移动计算需求的进一步增长,微处理器的低功耗设计研究已经成为处理器设计的一个重要研究方向。

开展微处理器的低功耗研究,对我国集成电路产业的发展具有重要意义。