全数字锁相环的设计

全数字锁相环设计研究

一、引言数字锁相环(DPLL)是一种相位反馈控制系统。

DPLL通常有三个组成模块:数字鉴相器(DPD)、数字环路滤波器(DLF)、数控振荡器(DCO)。

本文采用超前-滞后型数字锁相环(LL-DPLL)的设计方案,在LL-DPLL中,DLF用双向计数逻辑和比较逻辑实现,DCO采用加扣脉冲式数控振荡器。

这样设计出来的DPLL 具有结构简洁明快,参数调节方便,工作稳定可靠的优点。

二、数字锁相环的分类1.过零型数字锁相环路这种数字锁相环路采用过零采样数字鉴相器,即本地估算信号在输入信号的过零点上采样后进行A/D变换,得到数字相位误差信号输出。

2.触发器型数字锁相环路这类全数字锁相环路使用的数字鉴相器是触发器型数字鉴相器。

其特点是利用输入信号和本地估算信号的正向过零点对触发器进行触发,在触发器的置“ 0”和置“ 1” 的时间间隔内,得到相位误差信号。

置“ 0”和置“ 1”的时间间隔宽度就表征了输入信号和本地估算信号之间的相位误差大小。

3.超前-滞后型数字锁相环路这种数字锁相环路采用的鉴相器是超前-滞后型数字鉴相器。

超前-滞后型数字鉴相器在每一个周期内得到输入信号的相位比本地估算信号相位超前或滞后的信息。

因此,这种鉴相器的相位误差输出只有超前或滞后两种状态。

然后将误差相位的超前或滞后信息送到序列滤波器,产生对DCO的“ 加” 或“ 扣” 脉冲控制指令去改变DCO的时钟周期,使本地估算信号的相位输入信号相位靠拢。

4.奈奎斯特速率采样型数字锁相环路在这种数字锁相环路中,对输入信号的采样按照奈奎斯特速率进行。

也就是说,对输入信号进行A/D变换的采样频率必须按照奈奎斯特速率进行,以使输入信号能够依据奈奎斯特取样定理再现。

A/D变换后的输入信号与本地估算信号进行数字相乘,得到需要的相位误差数字信号,以完成鉴相功能。

三、系统设计本设计是基于直接数字频率合成器(Direct Digital Synthesizer)原理的信号发生器,用硬件描述语言Verilog来编程,用Altera公司的开发平台QUARTUSⅡ6.0来仿真,最后下载到StratixⅡ系列的EP2S60器件中进行验证。

基于FPGA的全数字锁相环设计与实现

基于FPGA的全数字锁相环设计与实现一、前言全数字锁相环(Digital Phase-Locked Loop,简称DPLL)是一种数字电路设计技术,可实现同步数字信号的调制和解调。

基于FPGA的全数字锁相环设计与实现,是一个极为重要的课题。

它可以有效地提高数字电路的性能,使得数字系统具有更优越的特性,并可广泛应用于数字电路的设计、数字信号的处理等领域。

二、DPLL 的体系结构DPLL是由相频检测器、滤波器、数字控制振荡器和时钟输出等多个部分组成的。

其中,相频检测器、滤波器和数字控制振荡器通常被集成到FPGA的内部,而时钟输出则需要通过FPGA的普通I/O口与市场上常见的外部输出设备相结合。

三、数字锁相环的工作原理数字锁相环的工作原理基于一个反馈循环系统,其中参考振荡器的频率与输入信号会被比较,然后通过差错检测网络来确定缺陷。

如果这些信号频率不匹配,则通过调整数字控制振荡器的频率来达到匹配。

然后,系统会根据输出信号和参考信号的相位差异来调整数字控制振荡器的频率,并通过PLL的反馈路径传输至输入端,进而得到和参考信号相同频率的输出信号。

四、数字锁相环的应用数字锁相环在通信领域有着广泛的应用,如数据码隆、数字调制、同步检测等;在数字领域,数字锁相环主要应用于数字信号处理、频谱分析、信噪比提高等方面;在电子仪器领域,数字锁相环可以被应用于测量领域、噪声分析、频率合成等方面。

五、基于FPGA的数字锁相环的设计数字锁相环的设计是一项非常复杂的工作,其中需要解决的问题主要有相频检测、低通滤波、数字控制振荡器的设计和时钟输出等方面。

在基于FPGA的数字锁相环设计过程中,可以采用很多不同的方法和技术来解决这些问题。

在数字锁相环的设计中,相频检测器是极其关键的部分,其主要功能是检测输入信号与数字控制振荡器的频率是否匹配。

其中,相频检测器常用的方式有两种:一是通过比较输入信号和数字控制振荡器的频率来实现;二是通过测量输入信号和数字控制振荡器的相位差来实现。

一种新型PID控制的全数字锁相环的设计与实现.

一种新型PID控制的全数字锁相环的设计与实现锁相环是一种能够跟踪输入信号相位的闭环自动控制系统,广泛应用于信号处理、时钟同步、倍频、频率综合等领域。

它根据输入信号和反馈信号的相位差来调整压控振荡器的输出频率,最终达到输入信号频率和输出信号频率相等,输入信号和输出信号保持恒定的相位差。

传统的PI控制器可以消除稳态误差,保证锁定精度,但是对阻尼有不利影响。

在PI控制器中引入微分项可以改善响应速度和阻尼,保证了锁定时间,但不能减少稳态误差,因此本文提出积分分离PID控制,能够大大改善响应时间和阻尼并减少稳态误差,从而保证了锁相精度和锁相时间。

1 电路结构与工作原理1.1 全数字锁相环电路结构快速全数字锁相环的系统框图如图1所示。

鉴相器采用JK触发器,该鉴相器结构简单,鉴相范围为±π,能够满足一般工程的需要。

由于鉴相器输出的是二值高低脉冲,后需接数字滤波器来平滑其中的起伏,消除噪声和干扰脉冲的影响。

一般数字序列滤波器有两种:N 先于M序列滤波器和随机徘徊滤波器,数字滤波器不是环路滤波器,它是无惰性的,加在环路中不影响环路的阶数,仅起到滤噪抗干扰的作用。

本文采用随机徘徊滤波器。

环路滤波器采用PID控制器,能够很好地控制环路相位校正的速度和精度,相对于文献[1]的PI控制器具有更好的特性。

数字压控振荡器采用可变模的分频器。

M分频器对输出信号进行分频,以使环路得到相应的倍频信号。

1.2 电路工作原理鉴相器比较输入信号和输出信号的相位差,产生一误差高低电平脉冲序列pha。

该脉冲的宽度和输入、输出信号的相位误差是成比例的。

K序列滤波器对相位误差信号进行量化,又可以消除输入信号噪声和干扰脉冲的影响。

当pha为高电平时,K序列滤波器对fO进行加计数,当计数器溢出时,一方面向环路滤波器产生一加脉冲i,同时对计数器进行复位,重新计数。

相反,当pha 为低电平时,K序列滤波器对fO进行减计数,当计数器减为零时,一方面向环路滤波器产生一减脉冲d,同时对计数器进行复位,重新计数。

全数字锁相环的VHDL设计【文献综述】

文献综述电子信息工程全数字锁相环的VHDL设计前言锁相环其实不是什么新东西,很早以前就有人使用了。

锁相技术的理论早在1932年就被提出来了,但直到40年代在电视机中才得到广泛的应用,用于改善电视接收机的行同步和帧同步,以提高抗干扰能力。

20世纪50年代后期随着空间技术的发展,锁相环用于对宇宙飞行目标的跟踪、遥测和遥控。

60年代初随着数字通信系统的发展,锁相环应用愈广,例如为相干解调提取参考载波、建立位同步等。

具有门限扩展能力的调频信号锁相鉴频器也是在60年代初发展起来的。

在电子仪器方面,锁相环在频率合成器和相位计等仪器中起了重要作用。

锁相环的英文全称是(Phase-Locked Loop),简称PLL,锁相的意义是相位同步的自动控制,能够完成两个电信号相位同步的自动控制闭环系统叫做锁相环。

是实现相位自动控制的负反馈系统,它使振荡器的相位和频率与输入信号的相位和频率同步。

主题从前言的论述中我们知道了锁相环路具有一些相当优良的功能,且成本低、使用方便,因而它已成为电子技术领域中一种相当有用的技术手段,获得了越来越广泛的应用。

锁相环可以分为模拟锁相环和数字锁相环。

模拟锁相环主要由相位参考提取电路、压控振荡器、相位比较器、控制电路等组成。

压控振荡器输出的是与需要频率很接近的等幅信号,把它和由相位参考提取电路从信号中提取的参考信号同时送入相位比较器,用比较形成的误差通过控制电路使压控振荡器的频率向减小误差绝对值的方向连续变化,实现锁相,从而达到同步。

数字锁相环主要由相位参考提取电路、晶体振荡器、分频器、相位比较器、脉冲补抹门等组成。

分频器输出的信号频率与所需频率十分接近,把它和从信号中提取的相位参考信号同时送入相位比较器,比较结果示出本地频率高了时就通过补抹门抹掉一个输入分频器的脉冲,相当于本地振荡频率降低;相反,若示出本地频率低了时就在分频器输入端的两个输入脉冲间插入一个脉冲,相当于本地振荡频率上升,从而达到同步[1]。

应用于SoC的全数字锁相环设计的开题报告

应用于SoC的全数字锁相环设计的开题报告1. 研究背景随着数字信号处理技术的不断发展,SoC(System on Chip)中集成的数字电路越来越复杂,其内部的时钟分频系统也变得异常重要。

在数字电路系统中,时钟信号的稳定性和精度直接影响数字系统的性能和稳定性。

因此,全数字锁相环(Digital Phase Locked Loop,DPLL)在SoC 中得到了广泛应用。

全数字锁相环是一种数字电路,能够使输入信号与VCO(Voltage-Controlled Oscillator)的频率同步,可以在高达数GHz的速度下实现精确的相位调整。

全数字锁相环没有模拟环路滤波器,具有抗干扰能力强、可调性和调试性好等优点。

因此,在数字电路系统中,全数字锁相环已成为最为常见的时钟同步方案之一。

2. 研究内容本文将深入探讨如何设计一种高性能的全数字锁相环电路,并将其应用于SoC中。

本文的研究内容如下:(1)锁相环的基本原理:介绍锁相环的基本工作原理,包括锁定范围、捕获范围、稳定性等指标的定义与计算。

(2)基本模块设计:详细介绍数字锁相环中的基本模块——相位检测器、数字控制器和VCO,并对每个模块的实现方式进行分析和设计。

(3)噪声分析及抑制:对锁相环中的噪声进行分析和抑制,例如抖动噪声、相位噪声等。

(4)时钟分频及输出:实现数字锁相环的时钟分频功能,并通过分频器输出相应的时钟信号。

(5)仿真分析:利用Cadence仿真工具对所设计的电路进行仿真分析,对电路的性能进行评估。

3. 研究意义本文设计的全数字锁相环电路具有以下特点:(1)采用数字电路实现,具有抗干扰能力强、可调性和调试性好等优点;(2)具有高速、高精度、低杂波等特性,能够满足SoC中对时钟同步的高要求;(3)在电路设计过程中,对噪声进行分析和抑制,提高了电路的稳定性和精度。

本文采用的研究方法为理论研究与实验仿真相结合,能够提高锁相环电路设计的可靠性和优化性。

全数字锁相环的VHDL设计【开题报告】

开题报告专业:电子信息工程全数字锁相环的VHDL设计一、综述本课题国内外研究动态,说明选题的依据和意义锁相技术是一种实现相位自动控制的方法,是专门研究相位的技术。

利用锁相技术得到的锁相环PLL是一个闭环的相位自动控制系统,它的输出信号能够自动跟踪输入信号的相位变化,也可以将之称为一个相位自动跟踪系统,它能够自动跟踪两个信号的相位差,并且靠反馈控制达到自动调节输出信号相位的目的。

锁相环的研究一直是学术界的一个研究重点,由于条件所限,国内对于锁相环的研究主要停留在理论方面,高性能锁相环的产品基本基本依赖进口。

而在国外,锁相环技术则在不断发展,从最初采用分离器件到采用集成电路,从采用双极工艺到使用CMOS 工艺,从需要挂电阻和电容到锁相环完全集成在一块芯片上,并且作为嵌入式IP核应用在大的数字系统中。

随着ASIC芯片电源电压下降,使得电源电压与核心薄氧化器件的阈值电压相比裕量有限从而使模拟电路设计,尤其是低噪声低电压锁相环的设计变得非常困难。

因而,当前锁相环的设计关键集中在高速、低电压、低噪声方面。

目前国外的锁相环产品大多采用3.3V电源电压的CMOS工艺,工作频率可从100MHz一直达到2.4GHz,输出噪声(周期到周期)在几十皮秒左右。

VHDL语言的英文全写是:VHSIC(Very High Speed Integrated Circuit)Hardware Description Language.翻译成中文就是超高速集成电路硬件描述语言。

因此它的应用主要是应用在数字电路的设计中。

其是一种行为描述语言, 其编程结构类似于计算机中的C 语言, 在描述复杂逻辑设计时, 非常简洁,具有很强的逻辑描述和仿真能力,是未来硬件设计语言的主流。

基于VHDL 语言的数字锁相环设计,不仅简化了硬件的开发和制作过程,而且使硬件体积大大减小,并提高了系统的可靠性。

该方法可以在不修改硬件电路的基础上,通过修改设计软件、更改移相范围就可满足不同用户的需要。

基于FPGA的全数字锁相环的设计

基于FPGA的全数字锁相环的设计l 前言锁相环(PLL)的理论与研究日趋完善,应用范围遍及整个电子技术领域,如信号处理,调制解调.时钟同步,倍频,频率综合等都应用到了锁相环技术。

随着集成电路技术的发展,集成锁相环和数字锁相环技术日趋成熟,不仅能够制成频率较高的单片集成锁相环路,还可以把整个系统集成到一个芯片上去,实现所谓的片上系统SOC。

因此,可以把全数字锁相环路(ADPLL)作为一个功能模块嵌入SOC,构成片内锁相环。

这里在简单介绍片内全数字锁相环系列结构的同时,给出一种智能控制捕获范嗣中全数字锁相环(ADPLL)的设计方法,并进行仿真和实践验证。

2 ADPLL 的结构及工作原理图1 给出全数字锁相环(ADPLL)的基本结构。

主要由数字鉴相器DPD,数字环路滤波器DLF,数控振荡器DC0,分频器4 部分组成,其中心频率为fc。

DPLL 是一种通过相位反馈来控制系统的电路结构。

根据输入信号Fin 和本地时钟输出信号Fout 之间的相位误差信号送入数字环路滤波器,并对相对误差进行平滑滤波,生成控制信号carry 和bor―row,数字振荡器根据控制信号调节反馈,使输出信号Fout 的相位逐渐跟踪输入信号Fin 的相位,最终达到锁定。

3 ADPLL 各模块的功能和具体实现方法3.1 数字鉴相器常用的鉴相器有2 种类型:异或门(X0R)鉴相器和边沿控制鉴相器(ECPD),设计中采用异或门鉴相器。

异或门鉴相器用于比较输入信号Fin 和输出信号Fout 之间的相位差,并输出误差信号Dout,Dout 作为计数的方向信号输入给下一级。

3.2 数字环路滤波器数字环路滤波器(DLF)由一个模值为变量K 的可逆计数器来实现。

其作用首先用于消除数字鉴相器输出的相位误差信号Dout 中的高频分量,保证锁相环路性能的稳定性和准确性:其次K 变模计数器再根据鉴相器的相位误差。

全数字锁相环的设1

全数字锁相环的设计摘要:在FPGA片内实现全数字锁相环用途极广。

本文在集成数字锁相环74297的基础上进行改进,设计了锁相状态检测电路,配合CPU对环路滤波参数进行动态智能配置,从而使锁相环快速进入锁定状态,在最短时间内正常工作并且提高输出频率的质量。

关键词:全数字锁相环数字环路滤波器数字单稳态振荡器1 引言数字锁相环路已在数字通信、无线电电子学及电力系统自动化等领域中得到了极为广泛的应用。

随着集成电路技术的发展,不仅能够制成频率较高的单片集成锁相环路,而且可以把整个系统集成到一个芯片上去。

在基于FPGA的通信电路中,可以把全数字锁相环路作为一个功能模块嵌入FPGA中,构成片内锁相环。

锁相环是一个相位误差控制系统。

它比较输入信号和振荡器输出信号之间的相位差,从而产生误差控制信号来调整振荡器的频率,以达到与输入信号同频同相。

所谓全数字锁相环路(DPLL)就是环路部件全部数字化,采用数字鉴相器(DPD)、数字环路滤波器(DLF)、数控振荡器(DCO)构成的锁相环路,其组成框图见图1示。

当锁相环中的鉴相器与数控振荡器选定后,锁相环的性能很大程度依赖于数字环路滤波器的参数设置。

2 K计数器的参数设置74297中的环路滤波器采用了K计数器。

其功能就是对相位误差序列计数即滤波,并输出相应的进位脉冲或是借位脉冲,来调整I/D数控振荡器输出信号的相位(或频率),从而实现相位控制和锁定。

K计数器中K值的选取需要由四根控制线来进行控制,模值是2的N次幂。

在锁相环路同步的状态下,鉴相器既没有超前脉冲也没有滞后脉冲输出,所以K计数器通常是没有输出的;这就大大减少了由噪声引起的对锁相环路的误控作用。

也就是说,K计数器作为滤波器,有效地滤除了噪声对环路的干扰作用。

显然,设计中适当选取K值是很重要的。

K值取得大,对抑止噪声有利(因为K值大,计数器对少量的噪声干扰不可能计满,所以不会有进位或借位脉冲输出),但这样捕捉带变小,而且加大了环路进入锁定状态的时间。

基于VHDL的全数字锁相环的设计

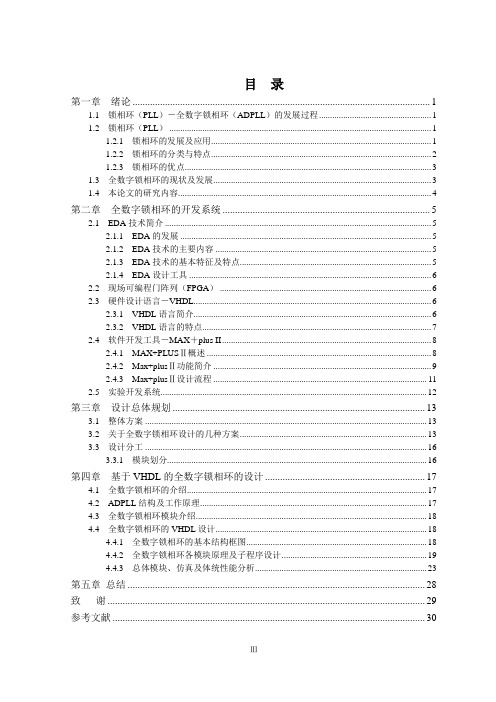

目录第一章绪论 (1)1.1锁相环(PLL)-全数字锁相环(ADPLL)的发展过程 (1)1.2锁相环(PLL) (1)1.2.1锁相环的发展及应用 (1)1.2.2锁相环的分类与特点 (2)1.2.3锁相环的优点 (3)1.3全数字锁相环的现状及发展 (3)1.4本论文的研究内容 (4)第二章全数字锁相环的开发系统 (5)2.1EDA技术简介 (5)2.1.1EDA的发展 (5)2.1.2EDA技术的主要内容 (5)2.1.3EDA技术的基本特征及特点 (5)2.1.4EDA设计工具 (6)2.2现场可编程门阵列(FPGA) (6)2.3硬件设计语言-VHDL (6)2.3.1VHDL语言简介 (6)2.3.2VHDL语言的特点 (7)2.4软件开发工具-MAX+plus II (8)2.4.1MAX+PLUSⅡ概述 (8)2.4.2Max+plusⅡ功能简介 (9)2.4.3Max+plusⅡ设计流程 (11)2.5实验开发系统 (12)第三章设计总体规划 (13)3.1整体方案 (13)3.2关于全数字锁相环设计的几种方案 (13)3.3设计分工 (16)3.3.1模块划分 (16)第四章基于VHDL的全数字锁相环的设计 (17)4.1全数字锁相环的介绍 (17)4.2ADPLL结构及工作原理 (17)4.3全数字锁相环模块介绍 (18)4.4全数字锁相环的VHDL设计 (18)4.4.1全数字锁相环的基本结构框图 (18)4.4.2全数字锁相环各模块原理及子程序设计 (19)4.4.3总体模块、仿真及体统性能分析 (23)第五章总结 (28)致谢 (29)参考文献 (30)第一章绪论1.1锁相环(PLL)-全数字锁相环(ADPLL)的发展过程锁相环从30年代开始发展,1932年,De Bellescize实现了第一个PLL,这个法国工程师称该发明为“相关通信”(coherent conmmunication)。

全数字锁相环设计

桂林电子科技大学毕业设计(论文)报告用纸第 1 页共27 页引言锁相的概念是在19世纪30年代提出的,而且很快在电子学和通信领域中获得广泛应用。

尽管基本锁相环的从开始出现几乎保持原样,但是使用不同的技术制作及满足不同的应用要求,锁相环的实现对于特定的设计还是蛮大的挑战。

锁相环在通信、雷达、测量和自动化控制等领域应用极为广泛,已经成为各种电子设备中必不可少的基本部件。

随着电子技术向数字化方向发展,需要采用数字方式实现信号的锁相处理。

锁相环技术在众多领域得到了广泛的应用。

如信号处理,调制解调,时钟同步,倍频,频率综合等都应用到了锁相环技术。

传统的锁相环由模拟电路实现,而全数字锁相环(DPLL)与传统的模拟电路实现的锁相环相比,具有精度高且不受温度和电压影响,环路带宽和中心频率编程可调,易于构建高阶锁相环等优点,并且应用在数字系统中时,不需A/D及D/A转换。

随着通讯技术、集成电路技术的飞速发展和系统芯片(SoC)的深入研究,全数字锁相环必然会在其中得到更为广泛的应用。

因此,对全数字锁相环的研究和应用得到了越来越多的关注。

传统的数字锁相环系统是希望通过采用具有低通特性的环路滤波器,获得稳定的振荡控制数据。

对于高阶全数字锁相环,其数字滤波器常常采用基于DSP 的运算电路。

这种结构的锁相环,当环路带宽很窄时,环路滤波器的实现将需要很大的电路量,这给专用集成电路的应用和片上系统SOC(system on chip)的设计带来一定困难。

另一种类型的全数字锁相环是采用脉冲序列低通滤波计数电路作为环路滤波器,如随机徘徊序列滤波器、先N后M序列滤波器等。

这些电路通过对鉴相模块产生的相位误差脉冲进行计数运算,获得可控振荡器模块的振荡控制参数。

由于脉冲序列低通滤波计数方法是一个比较复杂的非线性处理过程,难以进行线性近似,因此,无法采用系统传递函数的分析方法确定锁相环的设计参数。

不能实现对高阶数字锁相环性能指标的解藕控制和分析,无法满足较高的应用需求。

全数字锁相环的研究与设计毕业设计本科学位论文

本科毕业论文(设计、创作)题目:全数字锁相环的研究与设计全数字锁相环的研究与设计摘要本文主要描述了一种设计一阶全数字锁相环的方法,首先分析了课题研究的意义、锁相环的发展历程研究现状,然后描述了全数字锁相环的各个组成部件,并且详细分析了锁相环鉴相器、变模可逆计数器、加减脉冲电路、除H计数器和除N计数器各个模块的工作原理。

接着我们使用了VHDL语句来完成了鉴相器、数字滤波器和数字振荡器的设计,并且分别使用仿真工具MAX+plus II逐个验证各个模块的功能。

最后,将各个模块整合起来,建立了一个一阶全数字锁相环的电路,利用仿真工具MAX+plus II 验证了它的功能的能否实现,仿真结果与理论分析基本符合。

关键词:全数字锁相环;VHDL;数字滤波器;数字振荡器;锁定时间Design and research of ALL Digital Phase-LockedLoopAbstractIn this brief, we presented a way of designing a first-order ALL Digital Phase-Locked Loop (ADPLL) first analyzes the significance of research, the development course of phase-locked loop current research status, and then describes the component parts of all digital phase-locked loop, and detailed analysis of the phase lock loop phase discriminator, reversible counter change mould, add and subtract pulse circuit, in addition to H counter and divide N working principle of each module. Then we use the VHDL statements to complete the phase discriminator, digital filter and the design of the digital oscillator, and using the simulation tool of MAX + plus II one by one to verify the function of each module. Finally, the various modules together, established a first-order digital phase-locked loop circuit, using the simulation tool of MAX + plus II verify the realization of its function, the simulation results and principleKeywords: All Digital Phase-Locked Loop; VHDL; Digital filter; Digitaloscillator, Locking time目录1 引言(绪论) (5)1.1 课题研究的目的意义 (5)1.2 锁相环到全数字锁相环的发展历程 (5)1.3现状和发展 (6)1.4设计工具及设计语言 (7)2 全数字锁相环的结构与工作原理 (7)2.1 鉴相器 (10)2.2变模可逆计数器(模数K可预置) (10)2.3加减脉冲电路 (10)2.4除H计数器 (10)2.5 除N计数器 (10)3全数字锁相环的设计与仿真 (10)3.1鉴相器的设计 (11)3.2 数字环路滤波器的设计 (12)3.3 用VHDL语言实现除H计数器 (15)3.4 用VHDL语言实现加/减脉冲控制器 (15)3.5 除N计数器(分频器)的实现 (16)4 全数字锁相环的整体仿真 (17)5 结论(结束语) (19)主要参考文献 (20)致谢 (21)1.绪论1.1 课题研究的目的意义本次进行研究的课题是全数字锁相环。

全数字锁相环设计 (1)

二、原理

1、锁相法

位同步锁相法的基本原理与载波同步的类似, 在接收端利用鉴相器比较接受 码元和本地产生的位同步信号的相位,若两者相位不一致(超前或滞后) ,鉴相 器就产生误差信号去调整位同步信号的相位直到获得准确的位同步信号为止。 前 面介绍的滤波法中的窄带滤波器可以是简单的单调谐回路或晶体滤波器, 也可以 是锁相环路。 我们把采用锁相法来提取位同步信号的方法称为锁相法。通常分两类:一类 是环路中误差信号去连续的调整位同步信号的相位,这一类属于模拟锁相法; 另 有一类锁相环位同步法是采用高稳定度的振荡器(信号钟) ,从鉴相器所获得的 与同步误差成比例的误差信号不是直接用于调整振荡器, 而是通过一个控制器在 信号钟输出的脉冲序列中附加或扣除一个或几个脉冲, 这样同样可以调整加到减 相器上的位同步脉冲序列的相位,达到同步的目的。这种电路可以完全用数字电

ΔT=|T1-T2|=

F F 1 1 F 2 1 2 F1 F2 F2 F1 F0

式中,F0 为收发两端固有码元重复频率的几何平均值, 且有

T0

1 F0

由式(11.3 - 8)可得

F F0|T1-T2|= F0

再由式(11.3 - 9) ,上式可写为

T1 T2 T0

F F0

第 2页 共 26页

全数字锁相环设计

除(或添加)脉冲。 分频器:一个计数器,每当控制器输出 n 个脉冲时,它就输出一个脉冲。 控 制器与分频器的共同作用的结果就调整了加至比相器的位同步信号的相位。 这种 相位前、后移的调整量取决于信号钟的周期,每次的时间阶跃量为 T0,相应的 相位最小调整量为Δ=2πT0/T=2π/n。 相位比较器: 接收脉冲序列与位同步信号进行相位比较, 以判别位同步信号 究竟是超前还是滞后,若超前就输出超前脉冲,若滞后就输出滞后脉冲。 位同步数字环的工作过程简述如下: 由高稳定晶体振荡器产生的信号, 经 整形后得到周期为 T0 和相位差 T0/2 的两个脉冲序列, 如图 11 - 17(a)、(b)所示。 脉冲序列(a)通过常开门、或门并经 n 次分频后,输出本地位同步信号,如图 11 17(c)。 为了与发端时钟同步, 分频器输出与接收到的码元序列同时加到相位比较 器进行比相。如果两者完全同步, 此时相位比较器没有误差信号,本地位同步 信号作为同步时钟。如果本地位同步信号相位超前于接收码元序列时,相位比较 器输出一个超前脉冲加到常开门(扣除门)的禁止端将其关闭, 扣除一个(a)路 脉冲(图 11 - 17(d)),使分频器输出脉冲的相位滞后 1/n 周期(360°/n) ,如图 11 - 17(e)所示。如果本地同步脉冲相位滞后于接收码元脉冲时,比相器输出一个滞 后脉冲去打开“常闭门(附加门) ” ,使脉冲序列(b)中的一个脉冲能通过此门及 或门。正因为两脉冲序列(a)和(b)相差半个周期, 所以脉冲序列(b)中的一个脉冲 能插到“常开门”输出脉冲序列(a)中(图 11 - 17(f)),使分频器输入端附加了一个 脉冲,于是分频器的输出相位就提前 1/n 周期, 如图 11 -17(g)所示。经过若干 次调整后, 使分频器输出的脉冲序列与接收码元序列达到同步的目的,即实现了 位同步。 根据接收码元基准相位的获得方法和相位比较器的结构不同, 位同步数字锁 相环又分微分整流型数字锁相环和同相正交积分型数字锁相环两种。 这两种环 路的区别仅仅是基准相位的获得方法和鉴相器的结构不同, 其他部分工作原理相 同。下面我们重点介绍鉴相器的具体构成及工作情况。

全数字锁相环 (ADPLL)设计

全数字锁相环(ADPLL)设计

6月12日,由工业和信息化部人才交流中心主办,IC智慧谷、上海林恩信息咨询有限公司承办,南京江北新区人力资源服务产业园、中国半导体行业协会集成电路分会、上海集成电路技术与产业促进中心协办的第65期国际名家讲堂在上海举办,来自加利福尼亚大学洛杉矶分校(UCLA)的着名教授Behzad Razavi为中国的学员们带来了高性能锁相环设计短期高级课程。

PLL电路是用于生成与输入信号相位同步的新的信号电路,无论是工业还是民用,PLL电路的应用范围非常广,教授首先介绍了PLL的基本结构与各部分工作原理,对鉴相器和压控振荡器的设计都做了大致的说明,在稳定性、纹波和相位偏移之间的设计折衷给出了自己的建议。

PLL电路的特性由环路滤波器决定,因此设计PLL电路时,将其深刻理解为负反馈电路非常重要,稳定的PLL电路的环路滤波器的设计方法是PLL设计的精髓。

随后教授连续讲解了4篇ISSCC发布的最新成果,传递最新的设计技术,包括PLL中各模块的滤波、叠加等相位噪声抑制技术,FinFET技术节点上的版图设计问题,更小的随机抖动设计方法,以及5G应用中低于-

50dBm的功率设计技术和低于-40dBc的噪声设计技术。

学员们都在电路实例中收获了应对PLL非理想效应的实际设计经验。

课程的最后一个专题是环形振荡器的相位噪声分析,影响相位噪声的因素

具有不同的性质,然而很难找到一种通用的方法来包含各种影响因素以获得PLL系统的总相位噪声,教授在噪声分析方面也提出了两个基本的设计准则,并介绍了一种没有电感元件的低噪声PLL设计技术。

采用VHDL设计的全数字锁相环电路设计

采用VHDL设计的全数字锁相环电路设计叙述了全数字锁相环的工作原理,提出了应用VHDL 技术设计全数字锁相环的方法,并用复杂可编程逻辑器件CPLD 予以实现,给出了系统主要模块的设计过程和仿真结果。

0 引言全数字锁相环(DPLL) 由于避免了模拟锁相环存在的温度漂移和易受电压变化影响等缺点。

从而具备可靠性高、工作稳定、调节方便等优点。

在调制解调、频率合成、FM立体声解码、图像处理等各个方面得到广泛的应用。

随着电子设计自动化(EDA) 技术的发展,采用大规模可编程逻辑器件(如CPLD 或FPGA) 和VHDL 语言来设计专用芯片ASIC 和数字系统,而且可以把整个系统集成到一个芯片中,实现系统SOC ,构成片内锁相环。

下面介绍采用VHDL技术设计DPLL 的一种方案。

1 DPLL 的基本结构全数字锁相环结构框图如图1 所示, 由数字鉴相器、数字环路滤波器和数控振荡器3 部分组成。

'0') ;end if ;elseif cq > 0 then cq '0') ;end if ;end if ;end process ;process (en ,j ,cq ,k)beginif en = '1'thenif j = '0'thenf cq = k then cao1图4 变模可逆计数器(取k = 24) 的仿真波形图2. 3 数控振荡器的设计数控振荡器由加/ 减脉冲控制器和除N 计数器组成的。

加/ 减脉冲控制器其实是一个增量—减量计数器式DCO。

它和环路滤波器连用。

如果在环路滤波器无进位、错位的时候,加/ 减脉冲控制器对时钟2NFo 进行二分频。

当加/ 减脉冲控制的增量输入端( I = 1) 输入一个进位脉冲时, 输出脉冲中通过该计数器内部加上一个时钟脉冲。

反之,当加/ 减脉冲控制的减量输入端( D = 1) 时输入一个借位脉冲输出脉冲中就减去一个时钟脉冲。

全数字锁相环的VHDL设计【开题报告】

开题报告专业:电子信息工程全数字锁相环的VHDL设计一、综述本课题国内外研究动态,说明选题的依据和意义锁相技术是一种实现相位自动控制的方法,是专门研究相位的技术。

利用锁相技术得到的锁相环PLL是一个闭环的相位自动控制系统,它的输出信号能够自动跟踪输入信号的相位变化,也可以将之称为一个相位自动跟踪系统,它能够自动跟踪两个信号的相位差,并且靠反馈控制达到自动调节输出信号相位的目的。

锁相环的研究一直是学术界的一个研究重点,由于条件所限,国内对于锁相环的研究主要停留在理论方面,高性能锁相环的产品基本基本依赖进口。

而在国外,锁相环技术则在不断发展,从最初采用分离器件到采用集成电路,从采用双极工艺到使用CMOS工艺,从需要挂电阻和电容到锁相环完全集成在一块芯片上,并且作为嵌入式IP 核应用在大的数字系统中。

随着ASIC芯片电源电压下降,使得电源电压与核心薄氧化器件的阈值电压相比裕量有限从而使模拟电路设计,尤其是低噪声低电压锁相环的设计变得非常困难。

因而,当前锁相环的设计关键集中在高速、低电压、低噪声方面。

目前国外的锁相环产品大多采用3.3V电源电压的CMOS工艺,工作频率可从100MHz一直达到2.4GHz,输出噪声(周期到周期)在几十皮秒左右。

VHDL语言的英文全写是:VHSIC(Very High Speed Integrated Circuit)Hardware Description Language.翻译成中文就是超高速集成电路硬件描述语言。

因此它的应用主要是应用在数字电路的设计中。

其是一种行为描述语言, 其编程结构类似于计算机中的C 语言, 在描述复杂逻辑设计时, 非常简洁,具有很强的逻辑描述和仿真能力,是未来硬件设计语言的主流。

基于VHDL 语言的数字锁相环设计,不仅简化了硬件的开发和制作过程,而且使硬件体积大大减小,并提高了系统的可靠性。

该方法可以在不修改硬件电路的基础上,通过修改设计软件、更改移相范围就可满足不同用户的需要。

基于FPGA的全数字锁相环的设计与实现

基于FPGA的全数字锁相环的设计与实现一、本文概述本论文聚焦于基于现场可编程门阵列(FieldProgrammable Gate Array, FPGA)技术设计与实现全数字锁相环(AllDigital PhaseLocked Loop, ADPLL)的研究工作。

全数字锁相环作为一种关键的信号处理模块,广泛应用于通信系统、雷达系统、高速数据采集、频率合成等领域,其性能直接影响到整个系统的稳定性和精度。

随着FPGA技术的发展,ADPLL在灵活性、集成度、可编程性及实时调整等方面展现出显著优势,成为现代电子系统中实现高精度频率合成与同步控制的理想选择。

本文旨在深入探讨基于FPGA平台构建全数字锁相环的理论基础、设计方案及关键技术,并通过实际工程实践验证其性能。

研究内容主要涵盖以下几个方面:理论背景与技术综述:对全数字锁相环的基本原理、组成结构以及工作模式进行全面阐述,对比分析其与传统模拟锁相环和混合信号锁相环的优缺点。

在此基础上,详细介绍FPGA技术的特点及其在ADPLL设计中的应用价值,为后续设计工作奠定理论基础。

系统架构与模块设计:详细阐述所设计的基于FPGA的全数字锁相环的整体架构,包括鉴相器(Phase Detector)、数字环路滤波器(Digital Loop Filter)、数控振荡器(Digitally Controlled Oscillator, DCO)等核心组件的设计思路与实现细节。

针对FPGA资源特性,优化各模块算法及硬件实现,确保其在有限逻辑资源下达到高性能指标。

关键算法与技术实现:探讨用于提升ADPLL性能的关键技术,如低噪声鉴相算法、快速锁定策略、频率牵引与抖动抑制技术等,并展示如何将其有效融入FPGA实现中。

同时,阐述如何利用FPGA的可编程特性实现实时参数调整与在线监控,增强系统的动态适应能力和故障诊断能力。

仿真验证与实验结果:通过高级硬件描述语言(HDL)对设计进行建模,并利用FPGA开发环境进行功能仿真与时序分析,验证设计的正确性和稳定性。

基于matlab的全数字锁相环的设计与实现

基于matlab的全数字锁相环的设计与实现

全数字锁相环在微型机控制系统中被广泛应用,它能够通过控制脉冲重复率来控制检测信号的角度位置。

本文介绍如何使用Matlab来设计,以及在实际系统中实现一个全数字锁相环。

界面及模型的设计

首先,我们使用Matlab建立一个简单的GUI界面,以实现设定各项参数,以及便于观察系统数据的功能。

该界面包括可控变量,输入和输出变量以及控制参数三个部分,根据系统具体要求调整不同变量的值,以获得最佳性能。

然后,根据硬件设备的特性和系统要求,我们在Matlab中建立一个可表达系统真实行为的模型,并调整参数,将GUI界面设置的参数映射到模型上,以得到期望的结果和性能。

其中,模型的构成包括:比较电路、相位比较器、滤波电路、激励采样电路、控制逻辑等。

硬件和固件的实现

接着,根据模型获得的参数,我们使用C语言在DSP或MCU上编写实时系统固件,以便实现基于模型的控制算法,实时调整检测信号的角度位置。

此外,基于硬件资源的限制,在设计过程中,可以根据实际需求和模型分析结果,采用软件/硬件混合的方法设计相应的功能,以降低系统硬件资源的占用。

仿真与验证

最后,我们使用Matlab作为仿真平台,对所设计的模型进行仿真分析,验证模型的正确性,确保模型的准确性与实时性。

实验结果表明,基于Matlab的全数字锁相环设计方法以及在实际系统中实现,基本上是可行的。

不仅可以满足系统检测信号角度位置的控制要求,还可以很好地保证系统性能和可靠性。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

全数字锁相环的设计锁相环(PLL)技术在众多领域得到了广泛的应用。

如信号处理,调制解调,时钟同步,倍频,频率综合等都应用到了锁相环技术。

传统的锁相环由模拟电路实现,而全数字锁相环(DPLL)与传统的模拟电路实现的PLL相比,具有精度高且不受温度和电压影响,环路带宽和中心频率编程可调,易于构建高阶锁相环等优点,并且应用在数字系统中时,不需A/D及D/A转换。

随着通讯技术、集成电路技术的飞速发展和系统芯片(SoC)的深入研究,DPLL必然会在其中得到更为广泛的应用。

这里介绍一种采用VERILOG硬件描述语言设计DPLL的方案。

DPLL结构及工作原理一阶DPLL的基本结构如图1所示。

主要由鉴相器、K变模可逆计数器、脉冲加减电路和除N计数器四部分构成。

K变模计数器和脉冲加减电路的时钟分别为Mfc和2Nfc。

这里fc是环路中心频率,一般情况下M和N都是2的整数幂。

本设计中两个时钟使用相同的系统时钟信号。

图1 数字锁相环基本结构图鉴相器常用的鉴相器有两种类型:异或门(XOR)鉴相器和边沿控制鉴相器(ECPD),本设计中采用异或门(XOR)鉴相器。

异或门鉴相器比较输入信号Fin相位和输出信号Fout相位之间的相位差Фe=Фin-Фout,并输出误差信号Se作为K变模可逆计数器的计数方向信号。

环路锁定时,Se为一占空比50%的方波,此时的绝对相为差为90°。

因此异或门鉴相器相位差极限为±90°。

异或门鉴相器工作波形如图2所示。

图2 异或门鉴相器在环路锁定及极限相位差下的波形K变模可逆计数器K变模可逆计数器消除了鉴相器输出的相位差信号Se中的高频成分,保证环路的性能稳定。

K变模可逆计数器根据相差信号Se来进行加减运算。

当Se 为低电平时,计数器进行加运算,如果相加的结果达到预设的模值,则输出一个进位脉冲信号CARRY给脉冲加减电路;当Se为高电平时,计数器进行减运算,如果结果为零,则输出一个借位脉冲信号BORROW给脉冲加减电路。

脉冲加减电路脉冲加减电路实现了对输入信号频率和相位的跟踪和调整,最终使输出信号锁定在输入信号的频率和信号上,工作波形如图3所示。

图3 脉冲加减电路工作波形除N计数器除N计数器对脉冲加减电路的输出IDOUT再进行N分频,得到整个环路的输出信号Fout。

同时,因为fc=IDCLOCK/2N,因此通过改变分频值N可以得到不同的环路中心频率fc。

DPLL部件的设计实现了解了DPLL的工作原理,我们就可以据此对DPLL的各部件进行设计。

D PLL的四个主要部件中,异或门鉴相器和除N计数器的设计比较简单:异或门鉴相器就是一个异或门;除N计数器则是一个简单的N分频器。

下面主要介绍K变模可逆计数器和脉冲加减电路的设计实现。

K变模可逆计数器的设计实现K变模可逆计数器模块中使用了一个可逆计数器Count,当鉴相器的输出信号dnup为低时,进行加法运算,达到预设模值则输出进位脉冲CARRY;为高时,进行减法运算,为零时,输出借位脉冲BORROW。

Count的模值Ktop由输入信号Kmode预设,一般为2的整数幂,这里模值的变化范围是23-29。

模值的大小决定了DPLL的跟踪步长,模值越大,跟踪步长越小,锁定时的相位误差越小,但捕获时间越长;模值越小,跟踪步长越大,锁定时的相位误差越大,但捕获时间越短。

K变模可逆计数器的VERILOG设计代码如下(其中作了部分注释,用斜体表示):module KCounter(Kclock,reset,dnup,enable,Kmode,carry,borr ow);input Kclock; /*系统时钟信号*/input reset; /*全局复位信号*/input dnup; /*鉴相器输出的加减控制信号*/input enable; /*可逆计数器计数允许信号*/input [2:0]Kmode; /*计数器模值设置信号*/output carry; /*进位脉冲输出信号*/output borrow; /*借位脉冲输出信号*/reg [8:0]Count; /*可逆计数器*/reg [8:0]Ktop; /*预设模值寄存器*//*根据计数器模值设置信号Kmode来设置预设模值寄存器的值*/always @(Kmode)begincase(Kmode)3'b001:Ktop<=7;3'b010:Ktop<=15;3'b011:Ktop<=31;3'b100:Ktop<=63;3'b101:Ktop<=127;3'b110:Ktop<=255;3'b111:Ktop<=511;default:Ktop<=15;endcaseend/*根据鉴相器输出的加减控制信号dnup进行可逆计数器的加减运算*/always @(posedge Kclock or posedge reset)beginif(reset)Count<=0;else if(enable)beginif(!dnup)beginif(Count==Ktop)Count<=0;elseCount<=Count+1;endelsebeginif(Count==0)Count<=Ktop;elseCount<=Count-1;endendend/*输出进位脉冲carry和借位脉冲borrow*/assign carry=enable&(!dnup) &(Count==Ktop);assign borrow=enable&dnup& (Count==0);endmodule脉冲加减电路的设计实现脉冲加减电路完成环路的频率和相位调整,可以称之为数控振荡器。

当没有进位/借位脉冲信号时,它把外部参考时钟进行二分频;当有进位脉冲信号CAR RY时,则在输出的二分频信号中插入半个脉冲,以提高输出信号的频率;当有借位脉冲信号BORROW时,则在输出的二分频信号中减去半个脉冲,以降低输出信号的频率。

VERILOG设计代码如下:module IDCounter(IDclock,reset,inc,dec,IDout);input IDclock; /*系统时钟信号*/input reset; /*全局复位信号*/input inc; /*脉冲加入信号*/input dec; /*脉冲扣除信号*/output IDout; /*调整后的输出信号*/wire Q1, Qn1, Q2, Qn2, Q3, Qn3;wire Q4, Qn4, Q5, Qn5, Q6, Qn6;wire Q7, Qn7, Q8, Qn8, Q9, Qn9;wire D7, D8;FFD FFD1(IDclock, reset, inc, Q1, Qn1);FFD FFD2(IDclock, reset, dec, Q2, Qn2);FFD FFD3(IDclock, reset, Q1, Q3, Qn3);FFD FFD4(IDclock, reset, Q2, Q4, Qn4);FFD FFD5(IDclock, reset, Q3, Q5,Qn5);FFD FFD6(IDclock, reset, Q4, Q6,Qn6);assign D7=((Q9 & Qn1 & Q3) | (Q9 & Q5 & Qn3));assign D8=((Qn9 & Qn2 & Q4) | (Qn9 & Q6 & Qn4));FFD FFD7(IDclock, reset, D7, Q7, Qn7 );FFD FFD8(IDclock, reset, D8, Q8, Qn8);JK FFJK(IDclock, reset, Qn7, Qn8, Q9, Qn9);assign IDout = (!Idclock)|Q9;endmodule其中,FFD为D触发器,JK为JK触发器。

当环路的四个主要部件全部设计完毕,我们就可以将他们连接成为一个完整的DPLL,进行仿真、综合、验证功能的正确性。

DPLL的FPGA实现本设计中的一阶DPLL使用XILINX公司的FOUNDATION4.1软件进行设计综合,采用XILINX的SPARTAN2系列的XC2S15 FPGA器件实现,并使用Modelsim5.5d软件进行了仿真。

结果表明:本设计中DPLL时钟可达到120MH z,性能较高;而仅使用了87个LUT和26个触发器,占用资源很少。

下面给出详细描述DPLL的工作过程。

(1) 当环路失锁时,异或门鉴相器比较输入信号(DATAIN)和输出信号(CLO CKOUT)之间的相位差异,并产生K变模可逆计数器的计数方向控制信号(DNU P);(2) K变模可逆计数器根据计数方向控制信号(DNUP)调整计数值,DNUP 为高进行减计数,并当计数值到达0时,输出借位脉冲信号(BORROW);为低进行加计数,并当计数值达到预设的K模值时,输出进位脉冲信号(CARRY);(3) 脉冲加减电路则根据进位脉冲信号(CARRY)和借位脉冲信号(BORRO W)在电路输出信号(IDOUT)中进行脉冲的增加和扣除操作,来调整输出信号的频率;(4) 重复上面的调整过程,当环路进入锁定状态时,异或门鉴相器的输出DNUP为一占空比50%的方波,而K变模可逆计数器则周期性地产生进位脉冲输出CARRY和借位脉冲输出BORROW,导致脉冲加减电路的输出IDOUT周期性的加入和扣除半个脉冲。

有关一阶DPLL的一些讨论“波纹”(Ripple)消除在DPLL工作过程中,环路锁定时,异或门鉴相器的输出DNUP是一个占空比50%的方波。

因为在DPLL的基本结构中,K变模可逆计数器始终起作用。

因此当环路锁定后,如果模数K取值较小,K变模可逆计数器会频繁地周期性输出进位脉冲信号CARRY和借位脉冲信号BORROW,从而在脉冲加减电路中产生周期性的脉冲加入和扣除动作,这样就在脉冲加减电路的输出信号IDOUT中产生了周期性的误差,称为“波纹”;如果模数K取值足够大——对于异或门鉴相器,K应大于M/4;对于边沿控制鉴相器,K应大于M/2,则这种“波纹”误差通过除N计数器后,可以减少到N个周期出现一次,也就是说K变模可逆计数器的进位脉冲信号CARRY和借位脉冲信号BORROW的周期是N个参考时钟周期。

为了消除“波纹”误差,可以为K变模可逆计数器产生一个计数允许信号EN ABLE,环路失锁时,此信号有效,允许计数;环路锁定时,此信号无效,禁止计数,则不会产生周期性的进位和借位脉冲信号。