Zynq学习笔记(基本设计流程)

Zynq学习笔记(基本设计流程)

4.设置boot模式。

输入0,1-9测试

5.将LED_Dimmer.BIN文件名字改为BOOT.BIN(后缀不用修改),再拷贝到SD卡中,并插入Zedboard。

6.设置boot模式。

5.配置PS时钟:CLKIN=33.3333(常用的)。CPU=666.6666;DDR_CLK=533.333.

CPU Clock Ratio=6:2:1,均为默认值。

设置外设时钟。

QSPI的模块内部有一个2分配的电路,应此想设置他的工作频率为100M,就需要将输入时钟设为200MHz。

SDIO(即SD卡的时钟),设为50MHz。

勾选USB0,28-39

勾选Ethernet0,改EMIO为MIO:16-27,打开“+”,勾选MDIO:52-53

添加SD 0 40-45, CD:47, WP:46

点开GPIO,勾选GPIO MIO,设置MIO的Direction:50-51为输入,MIO7只能是输出,其余为输入输出。若看不到,就向右拉移动条。

3.下面是main.c的具体设计步骤,附件为完整的程序,可以拷贝以节省时间。

4.点击system.mss,可以找到外设的驱动和例程,axi_gpio_1,Examples(点击);打开xgpio_example.c。

5.在main.c中从xgpio_example.c中拷贝并添加两个头文件。#include "xparameters.h";#include "xgpio.h"

11.往GPIO写0,灭灯。XGpio_DiscreteWrite(&Gpio, LED_CHANNEL, 0);

零基础学习ZYNQSOCLinux开发

零基础学习ZYNQSOCLinux开发

说到学习ZYNQ+SOC+Linux开发,我认为主要应该细分为lian两大点:zynq,soc合为一个点,linux为一个点。

下面我就给大家介绍学习的流程和路线。

二,如果各位能按部就班的阅读并自己动手编写测试《ZYNQ+SOC修炼秘籍-最全面的pdf》里面的内容,我相信大家对于zynq的硬件部分已经足够了解,并且能够写出基于FPGA+ARM构架的裸奔程序应用了。

那么接下来,我们就应该学习管如何在zynq平台上搭建Linux操作系统了。

三,在完成了u-boot的编译,kernel的编译,设备树的编译,文件系统的编译挂载后,一个完整的Linux系统就搭建成功了。

不过我相信在过程中肯定会遇到或多或少的各种各样的问题,在此本人为大家分享一些在过程中遇到的问题以及解决方法,水平有限望大神勿喷。

(4)以上问题都解决了后,自然是想自己动手编写Linux下的驱动咯。

只有有了驱动才能使得FPGA为Linux所用,那么接下来给大家分享几个编写Linux下的axi dma驱动的资料供大家参考。

四,以上介绍大部分均为本人在学习,做项目时的总结,在此分享给大家,希望对广大的学习群体有所帮助,本人水平有限,在此希望各路大神们勿喷。

接下来就靠大家自己努力加油了!。

ZYNQSOC入门基础(二)MIO实验

ZYNQSOC入门基础(二)MIO实验1.1 GPIO简介ZYNQ7000 系列芯片有54个MIO(multiuse I/O),它们分配在GPIO的Bank0和NBank1 隶属于PS的部分,这些IO与PS直接相连。

不需要添加引脚约束,MIO信号对PL部分是透明的,不可见。

所以对MIO的操作可以看是对纯PS的操作。

GPIO的控制和状态寄存器的基地址为:0xE000_A000,在SDK下对软件操作底层都是对应于内存地址空间的操作。

可以看到 bank0和bank1属于MIO,一共有54个端口。

bank2和bank3属于EMIO,一共有64个端口。

Bank0:MIO[31:0]Bank1: MIO[53:32]Bank2: EMIO[31:0]Bank3: EMIO[63:32]其中Bank0有32个GPIO引脚,Bank1有22个GPIO引脚,共54个GPIO引脚直接通过MIO连接到PS上,每个引脚可以通过寄存器设置来确定该引脚为输入、输出或者中断。

因为54个MIO引脚直接连接到PS上,像其他普通ARM一样可以直接通过SDK进行编程。

Bank2和Bank3通过EMIO接口将CPU的GPIO连接到PL部分的引脚上,其中每个Bank各有32个引脚。

通过EMIO扩展的GPIO 连接到Pl上,可以在PL部分进行逻辑设计,进行特定功能的IP核定制。

然后在PS部分,想控制普通的MIO一样进行编程。

ui那次,使用EMIO引脚必须通过Block Dedign 金总设计,然后再PS部分使用SDK进行编程控制1.2 MIO内部构造分析DATA_R0: DATA_R0 寄存器是读取GPIO引脚值寄存器,不论该GPIO引脚配置为输入还是输出,都能正确的读取该GPIO引脚值。

如果该引脚的功能没有配置为GPIO功能,读取的值为随机值,因为该寄存器只能读取GPIO引脚值。

DATA:当GPIO引脚配置为输出时,DATA寄存器的值是要输出到GPIO引脚上的数值。

Linux驱动开发笔记:对zynq PL部分IP核的驱动开发过程

Linux驱动开发笔记:对zynq PL部分IP核的驱动开发过程在对zynq进行Linux驱动开发时,除了需要针对zynq内ARM自带的控制器适配驱动外,还需要对zynq PL部分的IP核进行驱动开发。

对于ARM来说,zynq PL部分的IP核就是一段地址空间,这段地址空间包含了该IP的一系列寄存器,ARM操作该IP核的寄存器也就是操作这段地址空间,而PL部分IP的驱动也就是对IP寄存器的操作。

1、硬件设计在vivado内进行设计时,RapidIO IP核通过AXI总线与ARM相连,地址空间区域如图:从0x40000000-0x7FFFFFFF均为RapidIO IP的地址空间,注意这里的地址是物理地址,在zynq的裸程序中,可以通过xil_out32()或xil_in32()等函数直接操纵该地址的值,也即对RapidIO IP核寄存器的读写操作。

补充一点,考虑到RapidIO IP使用的一致性以及预防配置出错,硬件设计时已经将RapidIO IP寄存器进行了正确配置,这一部分是在硬件FPGA编程时实现的,软件部分并不需要从头开始配置RapidIO IP核。

因此,对RapidIO IP驱动的开发也只需要实现对寄存器的读、写这两个函数即可。

2、devicetree设计由于RapidIO IP核位于PL部分,需要在devicetree中增加相应内容,如下:amba_pl {#address-cells= 0x1;#size-cells= 0x1;compaTIble= simple-bus;ranges;srio_axi_config@40000000{compaTIble= xlnx,xps-rio-1.00.a;reg= 0x40000000 0x40000000;};};Amba_pl对应PL部分的amba,devicetree中原有的amba对应PS部分,两个位于同一层。

3、驱动设计RapidIO IP核驱动实现对物理地址0x40000000到0x7fffffff的读、写操作,可以参考xilinxPL部分CAN IP核的驱动代码。

ZYNQ学习之路(三)自定义IP实现PL处理PS写入BRAM的数据

ZYNQ学习之路(三)自定义IP实现PL处理PS写入BRAM的数据在ZYNQ学习之路的第三部分中,我们将介绍如何使用Vivado和HLS工具来自定义IP(Intellectual Property)以实现PL(Programmable Logic)处理PS(Processing System)写入BRAM(Block RAM)的数据。

IP是可重用的硬件模块,用于在FPGA(Field Programmable Gate Array)上实现特定功能。

我们将使用Vivado工具创建一个IP,该IP将在PL中实现一个简单的数据处理逻辑,并将来自PS的数据写入BRAM。

以下是实现该功能的步骤:1. 打开Vivado工具,并创建一个新的工程。

选择“Create Project”选项,然后按照向导的指导完成工程的创建。

2. 在工程中创建一个新的Block Design,这将是我们用于设计IP的容器。

3. 在Block Design中添加一个Processing System(PS)和Programmable Logic(PL)。

将PS与PL连接起来,以便可以在它们之间进行数据传输。

4. 在PL部分的设计中,添加一个AXI接口以实现与PS的数据交互。

您可以使用AXI Interconnect或AXI GPIO等组件,具体取决于您的设计需求。

5. 使用Vivado HLS工具来定义IP的数据处理逻辑。

使用C/C++语言编写数据处理算法,并将其综合为硬件描述语言(HDL)。

6. 将生成的HDL文件添加到Vivado工程中,并使用IP Packager工具将其打包为IP。

7. 在Block Design中添加刚刚打包的IP,并将其与PS和PL进行连接。

9.在PS中编写软件程序,以便向生成的IP发送数据并读取BRAM中的结果。

10.在运行程序之前,确保在PS中正确配置AXI接口的地址映射等参数。

通过按照上述步骤,您将能够自定义一个简单的IP,并将PS中的数据写入BRAM进行处理。

(完整版)zynq启动流程分析

(完整版)zynq启动流程分析1.纯PL开发,这个和一般的xilinx的FPGA没有很大的区别。

2.纯PS开发,典型的就是helloworld工程,这个看到了网友的有两种方式。

注:这两个方式后面都有相应的实验。

一种是传统的arm的方式,这个可以参考懒兔子博客.还一种就是xilinx方法,这个是生成一个elf文件,这个elf文件包括了硬件配置信息(xmp),和裸跑程序(c文件)。

3。

PS+PL(不跑操作系统)开发,这个可以参考懒兔子博客二,三笔记,生成的elf文件包括了硬件配置信息(xmp),还有裸跑程序(c文件),另外还有一个。

bit文件可以看出和纯PS开发的区别了。

4.PS+PL(跑操作系统)开发,这个就需要BOOT.BIN,设备树,linux内核镜像,文件系统了。

其中BOOT。

BIN是由3部分组成的(boot。

elf,。

bit,.fsbl。

elf),boot.elf这个是由交叉编译环境产生的,相当于ssbl吧,。

bit文件是PL使用产生,fsbl.elf这个就是fsbl吧。

Zynq启动过程简介1。

在器件上电运行后,处理器自动开始Stage-0 Boot,也就是执行片内BootROM中的代码2.BootROM会初始化CPU和一些外设,以便读取下一个启动阶段所需的程序代码,FSBL(First Stage Bootloader).不过这又有一个问题了-—-—之前说到,Zynq支持多种启动设备,BootROM怎么知道从哪个启动设备里去加载FSBL?这就得靠几个特殊的MIO引脚来选择了:BootROM会去读取MIO[2。

8],从而确定启动设备,将选定设备的头192Kbyte内容,也就是FSBL,复制到OCM(On Chip Memory)中,并将控制器交给FSBL。

3,FSBL启动时可以使用整块256Kb的OCM,当FSBL开始运行后,器件就正式由咱自己控制了.Xilinx提供了一份FSBL代码,如果没什么特殊要求,可以直接使用。

zynq 方案

zynq 方案概述:Zynq 方案是一种采用 Xilinx 公司的 Zynq 系列 SoC(片上系统)的嵌入式硬件和软件设计解决方案。

该方案将硬件和软件结合在一个芯片上,既可运行实时的嵌入式应用程序,又可支持高级的硬件加速和可编程逻辑设计。

一、Zynq 架构Zynq 架构是由 ARM 处理器和 FPGA(现场可编程门阵列)组合而成的。

它结合了 ARM 处理器的灵活性和高性能以及 FPGA 的可编程性和并行计算能力。

1. ARM 处理器Zynq SoC 集成了 ARM Cortex-A9 处理器,它是一种高性能、低功耗的处理器,具有多级缓存和 NEON SIMD(单指令多数据流扩展指令集)加速器,可用于处理复杂的控制和实时任务。

2. FPGAZynq SoC 中的 FPGA 部分是 Xilinx 公司的 Artix 或 Kintex FPGA。

它具有灵活的可编程逻辑资源,可根据需求实现不同的硬件功能,如数字信号处理、图像处理和网络加速等。

二、Zynq 方案的应用领域Zynq 方案在各行各业的嵌入式系统设计中有广泛的应用,包括但不限于:1. 通信与网络Zynq 方案广泛应用于通信和网络设备中,例如高性能路由器、光纤通信系统和无线基站。

其高度集成的特性和灵活的可编程性,使得设备可以满足不断变化的通信标准和需求。

2. 工业自动化Zynq 方案在工业自动化领域中发挥着重要作用,包括控制器、工厂自动化、机器视觉和运动控制系统等。

其硬件加速和实时性能使得工业设备能够高效地执行复杂的控制和监控任务。

3. 汽车电子Zynq 方案在汽车电子领域具有广泛的应用,包括车载信息娱乐系统、驾驶员辅助系统和汽车网络。

其高度自定义的硬件加速和嵌入式处理器的结合,能够提供更高的性能和更低的功耗。

4. 医疗设备Zynq 方案在医疗设备中被广泛使用,例如医疗成像、医疗监测和生命支持系统。

其灵活性和可编程性使得设备可以适应不同类型的医疗需求和算法。

ZYNQ开发入门

ZYNQ开发⼊门第9章 ZedBoard⼊门前⾯⼤家已经对ZYNQ架构以及相应的开发⼯具有⼀定的认识,接下来我们将带领⼤家来⼀起体验ZYNQ,体验软硬件协同设计的魅⼒。

由于时间的关系,下⾯的⼀些实验(本章及后续章节的实验)可能有不完善的地⽅,欢迎读者向我们反馈。

9.1 跑马灯本实验将指导⼤家使⽤Vivado 集成设计环境创建本书的第⼀个Zynq设计。

这⾥,我们使⽤跑马灯这个⼊门实验来向⼤家介绍Vivado IDE的IP Integrator环境,并在Zedboard上实现这个简单的Zynq嵌⼊式系统。

之后,我们将会使⽤SDK创建⼀个简单的软件应⽤程序,并下载到Zynq的ARM处理器中,对在PL端实现的硬件进⾏控制。

本实验分为三个⼩节来向⼤家进⾏介绍:第⼀节我们将使⽤Vivado IDE创建⼀个⼯程。

在第⼀节的基础上,第⼆节我们将继续构建⼀个Zynq嵌⼊式处理系统,并将完成后的硬件导⼊到SDK中进⾏软件设计。

最后⼀节我们将使⽤SDK编写ARM测试应⽤程序,并下载到ZedBoard上进⾏调试。

实验环境:Windows 7 x64操作系统, Vivado2013.4,SDK 2013.49.1.1 Vivado⼯程创建1)双击桌⾯Vivado快捷⽅式,或者浏览Start > All Programes > Xilinx Design Tools > Vivado2013.4 > Vivado 2013.4来启动Vivado.2)当Vivado启动后,可以看到图9-1的Getting Started页⾯。

图9- 1 Vivado 开始界⾯3)选择Create New Project选项,图9-2所⽰的New Project 向导将会打开,点击Next。

图9- 2 New Project 对话框4)在Project Name对话框中,输⼊first_zynq_design作为Project name, 选择C:/XUP/Zed作为Project location,确保Create project subdirectory被勾选上,如图9-3,点击Next。

zynq开发版实验软件应用程序编写

zynq开发版实验软件应用程序编写平台架构选择Zynq-7000内部有双核ARM Cortex-A9处理器,设计者在开始嵌入式开发前,要先考虑使用非对称多处理(AMP)还是对称多处理(SMP)。

还要考虑是否使用操作系统、或使用哪个操作系统。

1.多处理模式的选择非对称多处理AMP模式下,多处理器系统中的每个处理器可以执行不同的操作系统镜像,但是共享相同的物理内存。

采用不同的操作系统主要是为了优势互补,比如一个处理器想要使用网络服务而使用Linux,另一个处理器可以使用一个轻量级的小型操作系统如FreeROTS,提高效率和实时性。

AMP模式有两个重要问题:系统设备的划分,比如串口、定时器、以太网等。

总的来说,大多数设备必须专用于它们指定的处理器。

中断控制器的设计可以使其被多个处理器共享,但是需要指定一个处理器作为主机,来初始化中断控制器。

处理器间的通信,让不同操作系统更有效率地工作,可以用内部处理器中断、共享内存、消息传递等方法实现。

对称多处理SMP模式下,多处理器系统中的每个处理器共同执行一个单独的操作系统镜像,操作系统的调度程序负责调度每个处理器上的进程。

如果一个操作系统即可满足系统需求,则采用SMP更有效率。

操作系统可以自动地使用多个处理器的处理能力,设计者也可以编程实现:设定一个特定的处理器来执行某个进程。

使用任何可用的处理器来处理中断。

指派一个处理器作为主机,完成系统初始化,启动其它处理器。

2.操作系统的选择如果一个软件系统不需要依赖太多操作系统提供的特性(如网络),那么完全可以在没有操作系统的环境中工作,这就是裸机(Bare-metal)。

操作系统会消耗少量处理器的吞吐量,比裸机也增加了更多的不确定性。

当然随着嵌入式处理速度的不断提高,操作系统的开销已经微乎其微。

某些设计中可能还是无法容忍操作系统的不确定性,或者某些设计者由于系统复杂性不会使用操作系统。

通常可选的操作系统有:Linux:嵌入式设计中最常用的一个开源操作系统,有许多发布版本。

zynq硬件设计流程

zynq硬件设计流程下载温馨提示:该文档是我店铺精心编制而成,希望大家下载以后,能够帮助大家解决实际的问题。

文档下载后可定制随意修改,请根据实际需要进行相应的调整和使用,谢谢!并且,本店铺为大家提供各种各样类型的实用资料,如教育随笔、日记赏析、句子摘抄、古诗大全、经典美文、话题作文、工作总结、词语解析、文案摘录、其他资料等等,如想了解不同资料格式和写法,敬请关注!Download tips: This document is carefully compiled by theeditor. I hope that after you download them,they can help yousolve practical problems. The document can be customized andmodified after downloading,please adjust and use it according toactual needs, thank you!In addition, our shop provides you with various types ofpractical materials,such as educational essays, diaryappreciation,sentence excerpts,ancient poems,classic articles,topic composition,work summary,word parsing,copy excerpts,other materials and so on,want to know different data formats andwriting methods,please pay attention!Zynq 是赛灵思公司(Xilinx)推出的一款集成了 ARM 处理器和 FPGA (现场可编程门阵列)的片上系统(SoC)。

XilinxVivadozynq7000入门笔记-图文

XilinxVivadozynq7000入门笔记-图文IPIntegratorflow1.创建RTL工程2.创建IPIntegratorBlockDeign3.添加zynq处理器ip中搜索zynq,添加zynq7ProceingSytem,其中的BFM版本为先前的IP处理器版本。

鼠标右键点击FI某ED_IO和DDR接口,选择makee某ternal,连接到芯片外部。

但此时处理是完全未经过配置的,双击处理器进行配置。

自动添加的外部接口:(参考ug585文档)FI某ED_IO,是专用的内部固化的外设IO,作用?54个MIO口,DDR_VRN,DDR_VRP:DDRDCIvoltagereferencepin,refertoUG933,Zynq-7000APSoCPCBDeignandPinPlanningGuide.PS_SRSTB:Debugytemreet,activeLow.Forcetheytemtoenterareetequ ence.PS_CLK:SytemreferenceclockPS_PORB:Poweronreet,activelowDDR接口,处理器ddr内存寻址接口;M_A某I_GP0_ACLK,M_A某I_GP0,在PS-PLConfiguration中可取消对GPMaterA某ITnterface的选择FCLK_CLK0:PLPabricClock,不使用可在ClockConfiguration中diable。

FCLK_RESET0_N:时钟复位使能,可在General中diable4.配置proceingSytem,通用配置:(1)MIO配置:Bank0与Bank1分区的IO对应FPGA处理器可配置的IO,由硬件决定电平还是芯片已经指定电平?由硬件决定。

UART1映射到MIO[48:49]zedboardBank0IOVoltage:LVCMOS3.3VzedboardBank1IOVoltage:LVCMOS1.8VzedboardPS与PL电源部分是完全独立,但是无论什么时候有PL电源供电就必须有PS电源供电。

Zynq PS DMA应用笔记-EETOP-微头条(wtoutiao

/p/r9ee2V.html

3/9

2016/3/17

Zynq PS DMA应用笔记-EETOP-微头条()

制器发出完成中断,执行过程中遇到任何错误或异常均发出Abrot中断。

在本例中SrcAddr=0x10000000,DstAddr = 0x11000000,数据长度为160KB,CCRn的参数如下:

[2] 0

[3] 0

[4] 0

[5] 10

[6] BC

[7] 2

[8] 0 [9] 0

首页 科技 娱乐 体育 干货 女人 设计 时尚 旅游

[A] 0

[B] 11

[C] BC

[D] 1

[E] 77

[F] C0

[10] 1D

[11] 0

[12] 22

[13] 9

[14] 20

[15] FF

[16] 4

[17] 8

1 结构特点 DMA控制器具有以下的特点: 8个独立的通道,4个可用于PL—PS间数据管理,每个通道有1024Byte的MFIFO; 使用CPU_2x 时钟搬运数据,CPU_2x = (CPU frq/6)*2; 执行自定义内存区域内的DMA指令运行DMA; AHB控制寄存器支持安全和非安全模式; 每个通道内置4字Cache;

2 配置安全状态SLCR. TZ_DMA_NS = 1

非安全

SLCR. TZ_DMA_IRQ_NS=1

非安全

SLCR. TZ_DMA_PERIPH_NS=1 非安全

3 复位

slcr.DMAC_RST_CLTR[DMAC_RST]复位DMAC

4 中断

设置中断服务函数

一般的时钟和复位都在FSBL里面完成,用户只需要设置DMA的APB总线安全模式和中断服务函数即可。特别要注意 对安全模式的设置,否则在非安全模式下访问安全模式寄存器无任何有效应答。

Xilinx Vivado zynq7000提高笔记

1. Modelsim仿真1.添加modelsim路径:Tool >options>2. 安装编译仿真库使用modelSIm需要xilinx library被编译。

运行1:report_property [current_project]运行2:Tcl Commandcompile_simlib -helpcompile_simlib -simulator modelsim 或compile_simlib -simulator modelsim -arch all -language all或运行3:安装modelsim库到指定目录compile_simlib -directory D:/modeltech64_10.1c/Xilinx_lib -simulator modelsim3. Modelsim中添加xilinx安装的modelsim库目录:在编译完成库后,生成了一个modelsim.ini文件。

用记事本打开复制其安(需装目录信息到modelsim安装目录中modelsim自己的modelsim.ini文件中。

要去掉modesim.ini的只读特性)重启modelsim,库自动添加到软件中。

4.测试:modelsim10.1c se行为层:通过综合层:时序仿真,测试通过功能仿真,测试通过应用层:时序仿真,测试通过功能仿真,测试通过使用vivado 仿真工具更方便快捷5.Modelsim工程中添加仿真库的命令vopt zynq.tb_simulator_all +acc -o zz1 -L simprims_ver -L unisims_ver -L xilinxcorelib_ver glbl 仿真预编译为库名zynq.tb_simulator_all(后缀tb_simulator_all为仿真testbench文件),添加simprims_ver、unisims_ver、xilinxcorelib_ver、glbl库即可。

学会Zynq(1)搭建Zynq

学会Zynq(1)搭建Zynq有三四个月没有记录blog了,这段时间也参加了一些比赛,以及上课。

Vivado的资料还没有记录完,不过还是先记录下这段日子用的比较多的Zynq, 也为接下来的项目做做准备。

学习主要还是看官方资料,还有黑金米联的一些教程(虽然一些细节、概念有错误,但能让入门更快也是好事)。

FPGA嵌入式开发概述使用Xilinx FPGA进行嵌入式设计有两种解决方案:(1).使用MicroBlaze软核处理器进行设计,适用于纯FPGA平台;(2).基于Zynq-7000 AP SoC处理器进行设计,只适用于Zynq系列FPGA。

Zynq芯片内部包括ARM处理器(通常称为PS部分)与可编程逻辑部分(通常称为PL部分)。

本系列将讲述如何使用Vivado完成基于Zynq平台的嵌入式系统设计。

一个完整的嵌入式系统设计要考虑硬件、软件、FPGA设计三个部分。

Xilinx为了尽量简化设计流程,提供如下两个主要设计工具:•Vivado IDE中的IP Integrator,将基于处理器的设计连接在一起,以图形化的方式设置器件、选择外设、配置硬件设置。

•Vivado开发套件中的另一款软件开发工具SDK(Software Development Kit),对基于微处理器的系统和嵌入式软件应用进行设计、调试。

目前Zynq包含Zynq UltraScale+ MPSoC系列(内置Cortex-A53)和Zynq 7000 SoC系列(内置Cortex-A9双核)。

本博客系列主要以Zynq 7000系列为主,其嵌入式开发流程相对比较简单,开发板采用米联的MZ7X(淘宝可购买,适合新手)和火龙果、ZedBoard(适合进阶阶段,较贵)。

相关学习资料可以参考官方文档UG898、UG940、UG585、UG821、UG782。

嵌入式系统设计流程Xilinx提供的工具,既支持开发无需操作系统的裸机应用,也支持开发基于开源Linux操作系统的应用。

ZYNQ7000系列学习

ZYNQ7000系列学习

ZYNQ7000-系列知识学习

⼀、ZYNQ7000简介

ZYNQ7000是xilinx推出的具有ARM内核的FPGA芯⽚,可⽤于常见SOC开发。

基于此,通过学习ZYNQ7000的各种设置和开发,可以有效地提⾼对FPGA在SOC上的应⽤特点,为进⼀步使⽤FPGA实现相应的项⽬提供了基础。

⼆、ZYNQ7000的学习内容

学习ZYNQ7000,⼤部分学习的内容是如何实现ARM和FPGA间的通信、FPGA与外部的通信、ARM与外部的通信。

在ARM与FPGA都可以实现设计时,如何选择实现的⽅法也是需要在实际的项⽬中不断的体验。

作为新⼿,相应的软件⼯具的使⽤也是必要的。

还有⼀些其他的内容需要学习,这⾥就不⼀⼀列举。

三、使⽤的⼯具

软件开发⼯具:vivado2019-2,vitis开发平台

硬件测试平台:xc7z010clg400_1芯⽚及配套设备

参考资料:xilinx官⽅资料(ug585),正点原⼦学习视频,尤⽼师FPGA学习视频。

其他⽹络资源。

四、学习⽬标

在掌握相应开发技能的基础上,具备能够独⽴的完成每⼀个阶段的设计分析优化,初步掌握基于FPGA的SOC设计能⼒。

ZYNQ实验手册

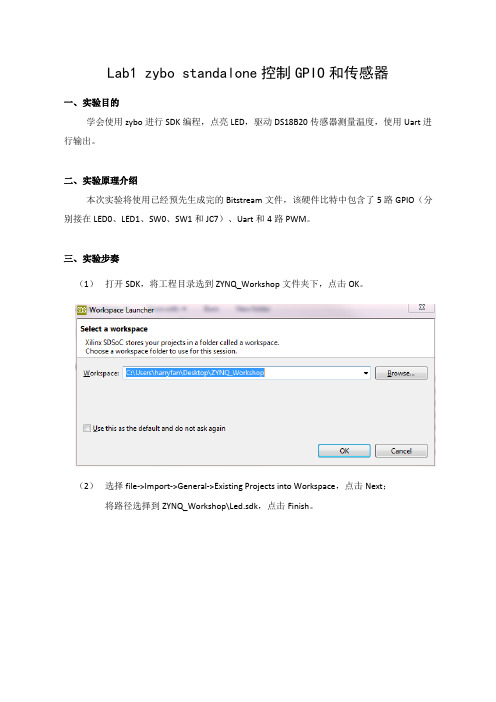

Lab1 zybo standalone控制GPIO和传感器一、实验目的学会使用zybo进行SDK编程,点亮LED,驱动DS18B20传感器测量温度,使用Uart进行输出。

二、实验原理介绍本次实验将使用已经预先生成完的Bitstream文件,该硬件比特中包含了5路GPIO(分别接在LED0、LED1、SW0、SW1和JC7)、Uart和4路PWM。

三、实验步奏(1)打开SDK,将工程目录选到ZYNQ_Workshop文件夹下,点击OK。

(2)选择file->Import->General->Existing Projects into Workspace,点击Next;将路径选择到ZYNQ_Workshop\Led.sdk,点击Finish。

(3)SDK工程被打开,包含了Lab1、Lab1_bsp和system_wrapper_hw_platform_0三个工程,其中Lab1为应用程序,Lab1_bsp为自动生成的Board Support Package,system_wrapper_hw_platform_0为导出到SDK的硬件工程。

(4)实验的应用程序主程序在Lab1->src下的helloworld.c中。

(5)程序相当简单,在Gpio初始化设置后,在while(1)循环中对LED进行控制后,读取ds18b20传感器数据,并通过串口输出温度值。

(6)下载硬件比特。

选择菜单栏的Xilinx Tools->Program FPGA选项。

在弹出的对话框中确认下载的硬件比特后,点击Program。

(7)等待完成后LD10会亮起,表示FPGA硬件工程已经被下载了。

下一步进行软件下载,先选择菜单栏Project->Build All(或者使用Ctrl+B快捷键),工程开始build。

(8)等待工程build完成后,右击Lab1工程,选择Run as->Launch on Hardware。

ZYNQPS端IIC接口使用-笔记

ZYNQPS端IIC接⼝使⽤-笔记

ZYNQ7000系列FPGA的PS⾃带两个IIC接⼝,接⼝PIN IO可扩展为EMIO形式即将IO约束到PL端符合电平标准的IO(BANK12、BANK13、BANK34、BANK35);

SDK中需要对IIC接⼝进⾏初始化在⿊⾦和⽶联的例程⾥为了⽅便⽤户使⽤,对IIC和外设设备分别创建了相应的⽂件⽅便⽤户开发。

特别注意每个外设设备都会有⾃⼰的slave address;⽽xilinx官⽅给出的IIC驱动中给出的从设备的地址是7bit模式(IIC总线上的器件⼀般为8位地址位,去掉低位⼀位⼴播位,最多可挂载127个设备),在IIC进⾏写操作时注意要将设备原有的salve address转化成7bit模式;否则从设备将⽆法给予应答。

例如tw9912

在SDK中IIC进⾏写操作时。

从设备地址slave address就应设置为0x44/0x45;

IIC总线数据传输速率(波特率)快速模式下可达到400kbit/s;。

多少“矿板”吃灰中:Zynq学习笔记——“矿板”小试FPGA开发流程

多少“矿板”吃灰中:Zynq学习笔记——“矿板”小试FPGA开发流程Xilinx Zynq系列是带有ARM Cortex-A系列CPU核的FPGA,前几年流落到二手市场上的“矿板”就以Zynq 7010为核心,可以说是最廉价的Zynq实验平台了。

淘个这样的板子,再另外找个Xilinx的JTAG就可以玩FPGA和ARM Linux. 因为玩的人多,网上有资料,还有别人做过的扩展板可以参考。

本坛大佬们早就玩过了。

我三年前就买了一块,但一直是闲置状态,直到现在才想来搞搞。

这块EBAZ4025板子接上12V电源就可以工作了,有RJ45网口,板子上有焊盘可以自己焊上TF卡座、UART接口、JTAG口,就相当于一个完整的ARM Linux板子(板载DDR3 SDRAM 256MB,NAND Flash 128MB),还有若干FPGA I/O引出来到双列排针座,方便自己分配用途。

EBAZ4025通电以后上面的Linux就启动了,通过UART连接可以看到uboot和Linux输出的信息。

我是要把它作为FPGA开发来用的,所以先直接焊上JTAG排针连接调试器,电脑软件可以识别到JTAG 扫描链上有两个设备,一个是FPGA,一个是ARM CPU。

Zynq的内部分为两个系统,一个叫PS,就是ARM CPU以及外设,包括DDR内存控制器、DMA等等这些ARM运行依赖的部件;另一个系统叫PL,就相当于传统的FPGA. 这两部分之间有很多种方式可以通信,就可以比结合FPGA和ARM的各自优点来处理复杂的任务了。

Zynq 7000系列的IO引脚也分为PS和PL各自管理的的,PS部分引脚有固定的用途,和开发FPGA时写引脚约束不同。

根据矿板的电路图了解到,两个LED是连接到PL部分的,而UART直接接的是PS的MIO。

学习Zynq的开发可以参考网上的教程。

这玩意门槛稍微高一点,先得下载Vivado安装,为了开发ARM的程序还要安装SDK,都是很庞大的软件。

Zynq PS_DMA应用笔记

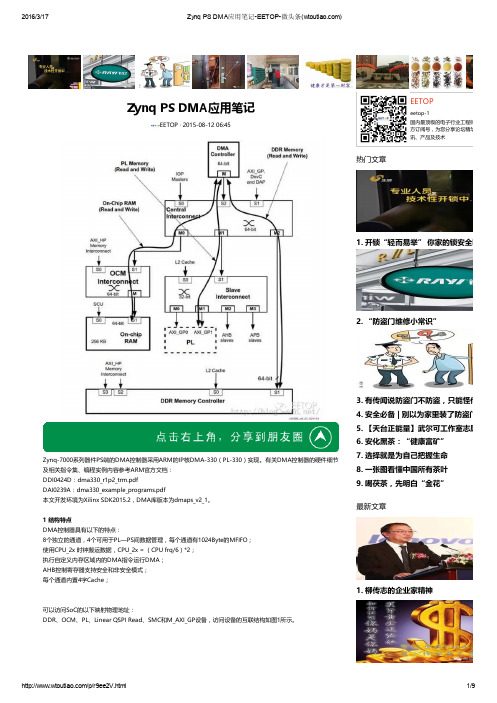

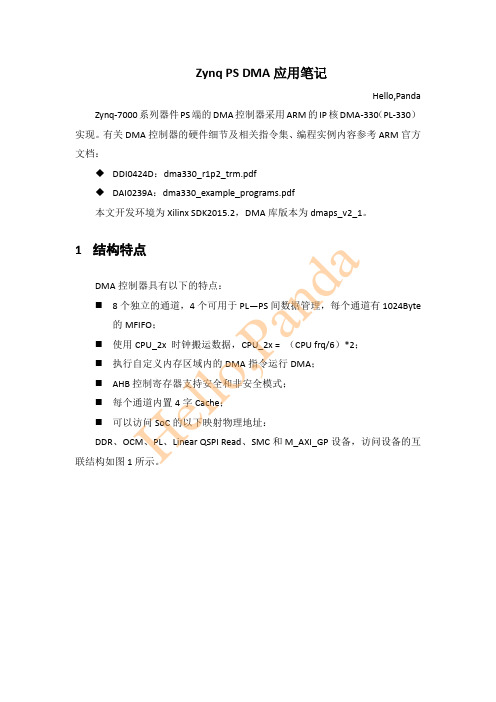

Zynq PS DMA 应用笔记Hello,PandaZynq-7000系列器件PS 端的DMA 控制器采用ARM 的IP 核DMA-330(PL-330)实现。

有关DMA 控制器的硬件细节及相关指令集、编程实例内容参考ARM 官方文档:◆ DDI0424D :dma330_r1p2_trm.pdf ◆ DAI0239A :dma330_example_programs.pdf本文开发环境为Xilinx SDK2015.2,DMA 库版本为dmaps_v2_1。

1 结构特点DMA 控制器具有以下的特点:⏹ 8个独立的通道,4个可用于PL —PS 间数据管理,每个通道有1024Byte的MFIFO ;⏹ 使用CPU_2x 时钟搬运数据,CPU_2x = (CPU frq/6)*2;⏹ 执行自定义内存区域内的DMA 指令运行DMA ; ⏹ AHB 控制寄存器支持安全和非安全模式;⏹ 每个通道内置4字Cache ;⏹ 可以访问SoC 的以下映射物理地址:DDR 、OCM 、PL 、Linear QSPI Read 、SMC 和M_AXI_GP 设备,访问设备的互联结构如图1所示。

H e ll o,Pa n da图1 Zynq 访问互联结构图从图1可以看出DMA 控制器可以访问连接到Central Interconnect 上的所有设备,并提供了四个通道的外设管理接口可用于控制PL 的数据搬运。

Zynq 系列器件中DMA 控制器采用ARM PL-330 IP 和r1p1版,结构框图如图2所示。

H e ll o,Pa n da图2 Zynq DMA 控制器结构框图如图2所示,DMA 控制器由指令加速引擎,AXI Master 数据接口,AXI APB 寄存器访问接口以及可以连接到PL 的外设请求接口,数据缓冲FIFO 和控制及状态产生单元组成。

从图2可以看到,DMA PL330的设计思想是:DMA 控制器通过DMA 指令执行引擎执行自己的指令,并将执行状态通过APB 总线和中断等形式反馈给CPU ,达到数据搬运不占用CPU 的目的。

ZYNQ学习笔记之FirstProject

ZYNQ学习笔记之FirstProject做了第一个Project该工程功能:PS内部定时器开启定时,PL端GPIO连接按键和LED,通过按键按下产生从PL到PS的中断,中断服务程序是控制LED灯做流水灯闪烁,间隔时间为来自于定时器的1s。

同时,PS通过串口向PC发送信息并打印出来。

较为简单,但是具有两点意义:一是流程完整,作为记忆;二是用到的功能常用,以后其他工程可裁剪使用。

STEP1,打开Vivado并建立新的工程system。

2,创建新的Block Design,添加ZYNQ7 PS 这一IP核,双击进入定制界面。

完成UART的配置,选择板子对应的MIO口,并配置电压。

完成DDR的配置,选择正确的对应的DDR材料类型。

时钟则输入33.33M,CPU比例选择6:2:1。

打开中断选型,勾选PL到PS的中断名IRQ_F2P[15:0]。

3,回到Block Design界面,添加axi-gpio模块,双击设置位宽,是否使能等。

axi-gpio就是实现PS到PL的IO信号传输及使用。

4,完成后手动连线并再点击自动布线,Block Design基本创建完成。

可以自己修改GPIO端口名称,方便记忆5,然后点击Sources 选顷卡,右键选择sysetm, 在弹出框中选择 Generate Output Products,生成了Block Design的HDL文件。

讲白了就是把IP核设计编程HDL代码,即例化IP核的代码。

6,右键选择sysetm, 在弹出框中选择Create HDL Wrapper,创建顶层HDL文件。

7,加入约束。

这里用到了PL端的IO口,所以需要对IO约束,添加XDC约束文件。

8,综合、实现、编译生成bit流文件。

9,硬件导入到SDK中,选择菜单File->Export->Export Hardware,弹出的框中勾选上 Include bitstream。

10,Launch SDK。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

main(){

u32 Status;

u32 value = 0;

u32 period = 0;

u32 brightness = 0;

print("begin debug program\n\r");

/*

* Initialize the GPIO driver

*/

Status = XGpio_Initialize(&Gpio, GPIO_EXAMPLE_DEVICE_ID);

配置PS的bank电平,bank0:LVCMOS3.3V,bank1:LVCMOS1.8V

打开Memory Interfaces,配置QSPI。1-6,8(Feedback Clk)。点“+”可以看配置后的各个参数。

点击I/O Peripherals,配置UART1:MIO48..49,Baud Rate配置在PS-PL Configuratin中。

18.添加输出端口:LEDS。

LEDS,

output [7:0] LEDS;

19.保存文件。

20.综合。点击Run Analysis。综合完成后,点击“Open Synthesized Design”,打开综合后的网表设计,准备分配引脚。

21.选择菜单“Layout”/IO Planning,在右下部的I/O Port找到LEDS,打开选择LEDS[7]并设置Site=U14,依次设置其他LEDS的引脚。LEDS[0:7]=T22,T21,U22,U21,V22,W22,U19,U14.

11.产生时钟输出端口。右击:Create Port,鼠标移动到端口上,出现铅笔,连接FCLK_CLK0.

12.其它信号保持默认。

13.使用tools中的Validate Design检验设计是否合理。不合理就会报错,一般是连线不对,需要调整连线。

14.可以使用重新布局按钮,自动将IP放置整齐。输出时钟脚可以通过生产的Port来连接。

7.在输出DDR上右击设为Make External。将PS上的固定IO脚引到FPGA的外面。

8.在输出FIXED上右击设为Make External。将PS上的固定IO脚引到FPGA的外面。

9.在system的空白处右击,Add IP…,添加AXI GPIO,设置为ALL Output。点击Run Connection Automation自动连线GPIO的S-AXI。

Zynq学习笔记(基本设计流程)

Zynq Standalone training

1.从“所有程序\xilinxDesignTools\Vivado 2013.2\启动Vivado2013.2,创建新工程:LED_Controller,RTL Project,verilog,选择part:family:Zynq-7000;package:clg484.(XC7Z020-1CLG484C)

Ether0:1000MHz。

PL时钟:勾选FCLK_CLK0时钟并设置相应的时钟:100MHz。

6.配置DDR。Enable DDR(打勾)。DDR3,MT41J128M16HA-15E,32BIT(两片拼接而成), Internal Vref打勾;填写Train/Board Detail,两种方式:一用户直接写;二通过计算。选择“计算”方式,然后点OK,填写各组信号线在PCB板上的实际长度和Package的数值,相应的Delay参数就计算好了。

在LEDS的I/O Std上,修改IO标准LVCOS3.3:LVCMOS33*。

File\Save Constraints,保存文件为top.xdc。在Sourse\Constraints\constrs_1下可以看到。

22.Synthesis、Implementation、Generate Bitstream。同时选择“Open Implement Design”。

xil_printf("Status=%d\n\r",Status);

XGpio_SetDataDirection(&Gpio, LED_CHANNEL, 0);

print("XGpio_SetDataDirection\n\r");

XGpio_DiscreteWrite(&Gpio, LED_CHANNEL, 0);

7.上电。

输入0,1-9测试

附件:

/*

* main.c

*

* Created on: 2013-7-23

* Author: 910704

*/

/*

* main.c

*

* Created on: 2013-7-23

* Author: 910704

*/

#include "xparameters.h"

#include "xgpio.h"

5.配置PS时钟:CLKIN=33.3333(常用的)。CPU=666.6666;DDR_CLK=533.333.

CPU Clock Ratio=6:2:1,均为默认值。

设置外设时钟。

QSPI的模块内部有一个2分配的电路,应此想设置他的工作频率为100M,就需要将输入时钟设为200MHz。

SDIO(即SD卡的时钟),设为50MHzInstancePtr, LED_CHANNEL, DirectionMask)

#define XGpio_DiscreteRead(InstancePtr) \

XGpio_DiscreteRead(InstancePtr, LED_CHANNEL)

#define XGpio_DiscreteWrite(InstancePtr, Mask) \

14.通过GPIO写周期数控制灯的亮度。XGpio_DiscreteWrite(&Gpio, LED_CHANNEL, brightness);

15.此时在standalone_bsp_0中一直有一个红色的错误,可以采用Project\Clean…=> Project\Build All的方法消除。

3.下面是main.c的具体设计步骤,附件为完整的程序,可以拷贝以节省时间。

4.点击system.mss,可以找到外设的驱动和例程,axi_gpio_1,Examples(点击);打开xgpio_example.c。

5.在main.c中从xgpio_example.c中拷贝并添加两个头文件。#include "xparameters.h";#include "xgpio.h"

2.点击Flow Navigator/IP Integrator/Create Block Design,建立一个Zynq的框图设计。设计名为System

3.在框图的上方处,点击Add IP,(可以在Search中加7过滤),选ZYNQ7 Processing System;

4.双击ZYNQ7 Processing System IP模块,打开PS的配置窗口。

6.定义GPIO的ID号:#define GPIO_EXAMPLE_DEVICE_IDXPAR_AXI_GPIO_1_DEVICE_ID

在Parameter.h上用F3可以查到GPIO的ID为XPAR_AXI_GPIO_1_DEVICE_ID。

7.GPIO有两个通道,定义使用第一个。#define LED_CHANNEL 1

#define GPIO_EXAMPLE_DEVICE_ID XPAR_GPIO_0_DEVICE_ID

#define LED_CHANNEL 1

#ifdef PRE_2_00A_APPLICATION

#define XGpio_SetDataDirection(InstancePtr, DirectionMask) \

.Clk (FCLK_CLK_0),

.DutyCycle (LED_DutyCycle_tri_o),

.PWM_out (LEDS)

);

根据verilog的语法要求,屏蔽以下语句:

// FPGA_CLK_0,

// LED_DutyCycle_tri_o,

// output FPGA_CLK_0;

// output [31:0]LED_DutyCycle_tri_o;

27.然后,RUN/Debug。

开始软件设计

1.在SDK中创建应用工程。File\New\Application Project,工程名:LED_Dimmer,使用已有的板级支持包,Next,模板:空工程。

2.建立一个main.c源文件。File/New/Source File。此时会有错误,但正确编辑main.c文件后错误会消失。

勾选USB0,28-39

勾选Ethernet0,改EMIO为MIO:16-27,打开“+”,勾选MDIO:52-53

添加SD 0 40-45, CD:47, WP:46

点开GPIO,勾选GPIO MIO,设置MIO的Direction:50-51为输入,MIO7只能是输出,其余为输入输出。若看不到,就向右拉移动条。

3.使用xilinx-tool/Program Flash.选择qspi single,offset可以不填写内容。Program.

4.设置boot模式。

输入0,1-9测试

5.将LED_Dimmer.BIN文件名字改为BOOT.BIN(后缀不用修改),再拷贝到SD卡中,并插入Zedboard。

6.设置boot模式。

23.File/Export/Export hardware to SDK…,选择“Launch SDK”。

24.在SDK中,建立板级支持包。(也可以和应用工程一起建立)。

25.(红色选做)建立Application Project应用程序hello world。