ISA总线接口实验

系统ISA接口实现原理

系统ISA接口实现原理钧天科技有限公司版权所有侵权必究目录上框ISA接口的具体实现:(AUX侧) (4)上框ISA接口的具体实现:(单板侧) (5)下框ISA接口的具体实现:(TSI侧) (6)下框ISA接口的具体实现:(单板侧) (6)8930系统的ISA总线按照上下框分了两路,上框由AUX出,下框由主备TSI分别出主备ISA总线。

上下框的ISA总线原理一样,所不同的是下框ISA总线有主备,各线路板的ISA接口需要进行选择。

上框ISA接口的具体实现:(AUX侧)AUX上面的数据,地址总线由850小系统扣板而来,到上框各单板的片选信号由AUX扣板的高位地址A[24:21]经FPGA译码而得,读写信号直接由850小系统扣板而来24位地址用CPU输出的读写信号MR/W控制245的数据方向,用/CS_OUTA信号控制245的通断。

MR/W:MR/W由扣板的CPU经过244直接输出MR/W为高时,AUX读上框各单板的数据,245数据由背板到AUXMR/W为低时,AUX写上框各单板的数据,245数据由AUX到背板/CS_OUTA:/CS_OUTA由AUX输出的到各单板的片选信号在逻辑里或门输出/CS_OUTA为高时,245关断,/CS_OUTA为低时,245打开请看原理图。

地址线不经过任何控制,仅由244隔离,直接输出到背板。

上框ISA接口的具体实现:(单板侧)在8930系统中,通过244,245把背板ISA总线和单板ISA总线进行隔离,通过CPLD管脚输出2个信号/OE_ADDR_A, /OE_DATA_A控制244,245的通断。

这2个OE信号在单板进行上拉.单板ISA总线能进行工作条件:(由245的/OE管脚控制)1. 扣板不在位2. 该槽位的片选信号有效在CPLD检测到扣板不在位或片选信号有效时,打开245的\OE门。

各单板还用DIR_DA TA_A信号控制ISA数据总线的流向DIR_DATA_A由背板WR信号决定:(可以不经过CPLD,直接把由母板过来的W/R信号连接到245的DIR管脚。

AS-I总线教程

对于普通I/O设备来说,如果想接入AS-I系统,必须提供一个带有ASIC的AS-I模块,I/O设备与这些模块连接。

·供电电源

供电电源为30VDC,必须使用专用的AS-I电源,并且直接与数据线连接。AS-I从站正常工作的电压至少在26.5V以上。一个从站消耗的电流在100mA以上,一个分支上的所有从站消耗电流大约为2A,AS-I电缆能提供的最大容量为8A。当消耗的电流过大时,需要添加辅助电源。辅助电源为24VDC,用一个双芯黑色无屏蔽的电缆将辅助电源与从站连接起来。辅助电源线同样使用穿刺技术连接。

·具有坚固的网络拓扑,不需要屏蔽和终端电阻,即使在恶劣环境中也能保证通信的可靠性。

·网络中只有1个主站,最多31个从站,每个从站有4位I/O可以利用。

·最多124个I/O传感器和执行器。

·主从站间采用循环方式进行访问。

·循环时间最大5ms。

·网络连接电缆为双芯、非屏蔽、1.5mm²的黄色异型电缆或圆形电缆。最大长度为100m。使用中继器可扩展到300m。但最多只能使用两个中继器。

每个等级的网络都与上下相邻的网络连接,可以判定相互间通讯的需求。在最上层网络,存在众多复杂的计算机系统,能够不定期的对各种复杂数据进行响应,大量的通讯参与者和响应者在网络中相互协调。

在最底层,依然有很大的信息吞吐量,只是数据相对要少于上层结构。

在自动化系统网络中可以分为以下5层结构:

·计划编制层(Planning Level),对来自生产层的信息进行评价,组织编排并协助生产部门进行决策。在这一层中,不论是信息量还是传输速率和距离都是最大的。

AS-I主站采用轮询方式访问,即按照顺序一个一个的对从站进行访问。这个顺序就是在上电时,主站第一次访问时建立的地址列表。如果在访问时,从站在规定时间内没有对主站的请求作出响应,主站会立即重复访问一次。还没有响应的话,主站将访问下一地址。在后面的两个周期内,主站会继续尝试访问先前丢失的地址,如果依然没有回应,故障错误位会被置位,并将该信息发送给PLC。

精简ISA扩展总线应用

精简ISA扩展总线应用英创公司的嵌入式网络模块系列产品均具有精简ISA 扩展总线,通常包括若干地址总线、8 位数据总线、读写控制线、片选控制线以及中断请求线。

英创公司所提供的评估开发底板将这些信号线制定了一个接口标准,采用双排20 芯IDC 插针,交错排列,用户可用该扩展总线进行硬件扩展。

片选线CS1出厂默认选择地址段为300H—37FH,例如,当(A6A5A4A3A2A1A0)=(0000101’b),CS1 加5 条地址线的译码输出端口地址为305H,以下是扩展总线接口的定义:1、总线时序图,以及和C 语言、汇编指令之间的关系为了便于用户理解精简ISA 总线接口如何进行编程,本文简单介绍C 语言中的指令、用户操作的函数与总线的时序之间的关系。

各个不同模块的CS1#片选地址范围不同,详见相关技术手册,下面以ETR232i 的使用为例进行讲解,在此CS1#对应的片选地址范围为300h——37Fh,其中A0——A6 的译码为0ah。

C 语言端口输出函数:outportb (0x30a, ub1 );//把ub1 字节送到0x30a 寄存器对应的汇编指令为:mov dx , 0x30a mov al , byte ptr ub1;byte ptr ub1 为变量ub1 对应的存储器out dx , al 对应的总线写时序图为(本文中的总线周期均以ETR232i 模块为例):C 语言端口输入函数:char ub1 = inportb (0x30a ); //把0x30a 地址寄存器的内容读入变量ub1 对应的汇编指令为:mov dx , 0x30a in al , dx mov byte ptr ub1, al ; byte ptr ub1 为变量ub1 对应的存储器tips:感谢大家的阅读,本文由我司收集整编。

仅供参阅!。

ISA总线

ISA总线ISA总线(或称工业标准结构总线)在与IBM兼容的PC系统刚起步时就已出现了(约1982年)。

实际上,任何早期PC中的功能卡均可插入最先进的基于Pentium4的计算机中,并且发挥作用。

这是因为在所有这些计算机都有ISA总线接口,从而与早期的PC仍然兼容。

ISA总线最近在家用计算机中已几乎不用了,但仍用于许多工业应用,且越来越受到限制。

ISA总线已经不同于它的早期版本。

ISA总线已从最初的8位标准总线发展为在大多数系统中广泛应用的16位标准总线。

在发展过程中甚至出现过一种称为EISA(扩展ISA)总线的32位标准总线,但已基本消失。

在一些比较老的主板上仍保留有ISA插槽,既可以插入8位ISA卡,又可以插入16位ISA卡。

32位的印制电路板则经常是PCI卡。

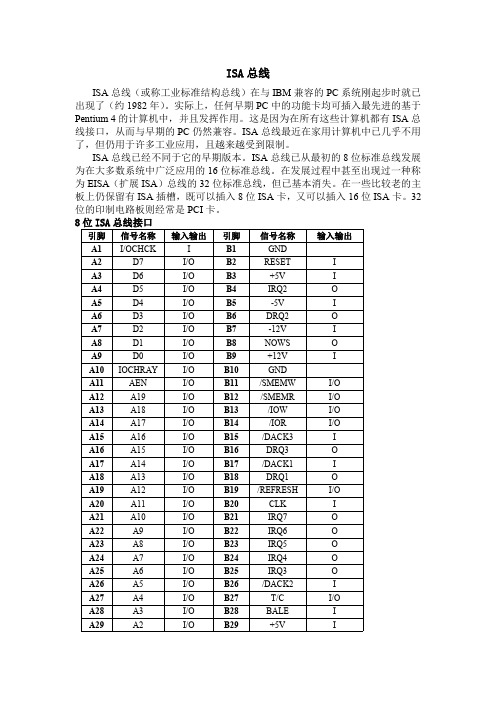

8位ISA总线接口引脚信号名称输入输出引脚信号名称输入输出A1I/OCHCK I B1GNDA2D7I/O B2RESET IA3D6I/O B3+5V IA4D5I/O B4IRQ2OA5D4I/O B5-5V IA6D3I/O B6DRQ2OA7D2I/O B7-12V IA8D1I/O B8NOWS OA9D0I/O B9+12V IA10IOCHRAY I/O B10GNDA11AEN I/O B11/SMEMW I/OA12A19I/O B12/SMEMR I/OA13A18I/O B13/IOW I/OA14A17I/O B14/IOR I/OA15A16I/O B15/DACK3IA16A15I/O B16DRQ3OA17A14I/O B17/DACK1IA18A13I/O B18DRQ1OA19A12I/O B19/REFRESH I/OA20A11I/O B20CLK IA21A10I/O B21IRQ7OA22A9I/O B22IRQ6OA23A8I/O B23IRQ5OA24A7I/O B24IRQ4OA25A6I/O B25IRQ3OA26A5I/O B26/DACK2IA27A4I/O B27T/C I/OA28A3I/O B28BALE IA29A2I/O B29+5V IA30A1I/O B30OSC IA31A0I/O B31GND1、下面对引脚信号做一些简要说明:D7~D0:8位数据线,双向,三态。

实验:系统总线和具有基本输入输出功能的总线接口实验

山西大学计算机与信息技术学院实验报告为了实现对于MEM 和外设的读写操作,还需要一个读写控制逻辑,使得CPU 能控制MEM 的读写,实验中的读写控制逻辑如图 4-2 所示,由于 T3 的参与,可以保证写脉宽与 T3 时序单元的TS3 给出(时序单元的介绍见附录2)。

IOM 用来选择是对I/O 设备还是对 MEM 作,IOM=1 时对 I/O 设备进行读写操作,IOM=0 时对 MEM 进行读写操作。

RD=1 时为读,④将R0 寄存器中的数用LED 数码管显示。

先将WR、RD、IOM 分别置为1、0、1,对OUT 单元进行写操作;再将K7 置为0,打开R0 寄存器的输出;K6 置为 0,关闭 R0 寄存器的输入;LDAR 置为 0,不将数据总线的数打入地址寄存器。

连续四次点击图形界面上的“单节拍运行”按扭,观察图形界面,在T3时刻完成对OUT 单元的写入操作。

三、实验总结:1、存储器和输入、输出设备最终是要挂接到外部总线上,因此需要外部总线提供数据信号以及控制信号。

2、外部总线和CPU 内总线之间通过三态门连接,同时实现了内外总线的分离和对于数据流向的控制。

而地址总线可以为外部设备提供地址信号和片选信号。

3.为了实现对于MEM 和外设的读写操作,还需要一个读写控制逻辑,使得CPU 能控制MEM和 I/O读写4、WR=0,RD=1,IOM=0时 E0 灭,表示存储器读功能信号有效。

WR=1,RD=0,IOM=0)连续按动开关ST,当指示灯显示为 T3 时刻时,E1 灭,表示存储器写功能信号有效。

WR=0,RD=1,IOM=1时,E2 灭,表示I/O 读功能信号有效。

WR=1,RD=0,IOM=1)时,观察扩展单元数据指示灯,指示灯显示为T3 时刻时,E3 灭,表示功能信号有效。

ISA总线

ISA总线接口ISA总线又称AT总线,是在PC/AT微机上所配备的扩展系统总线。

PC/AT的扩展总线系统设计的最大速度为...(Industry Standard Architecture),即ISA总线标准。

EISA总线是由COMPAQ等兼容机厂商联合于1988年9月推出的一种与IBM的MCA总线抗衡的增强型总线。

EISA总线是对ISA总线的扩展,除了保留符合ISA标准的98个引脚外,又增加了90个引脚,这90个引脚包括16条数据线、27条地址线、12条控制线、26条电源线和地线、5条保留线和4条系统制造商专用线。

EISA总线本质上是32位的ISA总线,插槽与所有ISA卡完全兼容。

与MCA类似的是,它也可以允许通过软件来配置EISA卡PCI总线接口PCI总线的英文全称为Peripheral Component Interconnect。

即外部设备互联总线,是于1993年推出的PC局部总线标准。

PCI总线的主要特点是传输速度高,目前可实现66M 的工作频率,在64位总线宽度下可达到突发(Burst)传输速率533MB/s。

可以满足大吞吐量的外设的需求。

VESA(video electronics standard association)总线标准是1992年由60家附件卡制造商联合推出的一种局部总线,简称为VL(VESA local bus)总线。

它的推出为微机系统总线体系结构的革新奠定了基础。

VESA总线主要目的是用于视频插卡,以提高视频性能。

VESA总线系统考虑到CPU与主存和Cache 的直接相连,通常把这部分总线称为CPU总线或主总线,其他设备通过VL总线与CPU总线相连,所以VL总线被称为局部总线。

并行外部设备总线SCSI第6章系统总线接口本章介绍了微机主板的各种标准系统总线和通用,专用接口的技术规格特点,也介绍了它们的使用方法等. 6.1 主板上的系统总线6.2 系统I/O总线的标准6.3 系统设备接口退出6.1 主板上的系统总线6.1.1 总线原理主板上的系统总线是传输数据的通道,就物理特性而言就是一些并行的印刷电路导线,通常根据传送信号的不同将它们分别称为地址(address bus),数据(data bus)和控制(Control bus)三大总线.在数字电路中,逻辑信号1,0是采用电平的高低来表示的,假如高电平表示1,低电平就表示0,由此抽象为二进制数的1和0,并以数位二进制数组成各种代码,来表示各种信息,如用7位二进制数的ASCII码表示英文字符.系统处理各种信息,实际上就是处理一组组二进制数,进一步说,就是在总线上不断传送高,低电平信号.由于元器件性能所限,电路的工作速度也是有限的,即不可能在一秒钟内开关任意多次.我们把系统总线电路每秒钟电平转换的最高次数,称为总线频率f,单位为MHz.频率f的倒数1/f称为总线时钟周期.6.1.2 总线分类总线大致可以分为四类:1.片内总线片内总线也称为CPU总线.它位于CPU处理器内部,是CPU内部各功能单元之间的连线,片内总线通过CPU 的引脚延伸到外部与系统相连.2.片间总线片间总线也称为局部总线(Local BUS).它是主板上CPU与其它一些部件间直接连接的总线.3.系统总线:系统总线也称为系统输入输出总线(System I/O Bus).它是系统各个部件连接的主要通道,它还具有不同标准的总线扩展插槽对外部开放,以便各种系统功能扩展卡插入相应的总线插槽与系统连接.4.外部总线外部总线也称为通信总线.它是电脑与电脑之间的数据通信的连线,如网络线,电话线等.外部总线通常是借用其它电子工业已有的标准,如RS-232C,IE1364标准等.6.1.3 总线构成这里主要介绍的是系统总线,即主板的系统I/O总线和总线扩展插槽.系统I/O总线是数据总线,地址总线和控制总线的总称.数据总线传送的是数据信号,可双向传送.它的线数即总线宽度取决于系统采用的CPU的字长指标.系统总线的宽度是指其数据线的位数.地址总线传送的是内存(或I/O接口)的地址信号,单向传送.它的线数与系统采用的CPU的地址线宽度一致,它决定了CPU直接寻址的内存容量.控制总线传送的是CPU和其它控制芯片发出的各种控制信号,如:读/写周期W/R,指令/代码传送D/C,存储器或IO口访问M/IO和系统复位Reset等.系统中的各个局部电路均需通过这三大总线互相连接,实现了全系统电路的互连.在主板上,系统I/O总线还连接到一些特定的插槽上去对外开放,以便于外部的各种扩展电路板连入系统.这些插座被称为系统I/O总线扩展插槽(System Input/Output Bus Expanded Slot).系统I/O总线的示意图如图6-1.图6-1 微机的系统I/O总线6.2 系统I/O总线的标准PC机主板上采用最多的系统I/O总线标准有ISA,VESA,PCI和AGP等,目前仍保留着ISA,但主要是使用PCI和AGP.主板上的系统总线插槽如图6-2所示.图6-2 主板上的系统I/O总线插槽6.2.1 以往的总线标准1.PC总线和ISA总线PC总线最初用于IBM PC/XT机主板,并在以后的PC/AT和各种286,386兼容机主板上继续使用,目的是便于保留老的PC扩展卡.在后来制定的ISA总线标准中被称为8位ISA总线,目前已被淘汰.PC总线是配合Intel 8088处理器的,因此是8位总线,具有8位数据线和20位地址线,直接内存寻址能力为220即1MB.它的扩展插槽是黑色的,有62个触点,分列两边,每边31个.PC总线扩展插槽的引脚配置如图6-3所示.图6-3 PC总线扩展插槽的引脚配置ISA总线标准来源于IBM PC/AT机主板使用的系统I/O总线和扩展插槽,所以也称为AT总线(AT Bus),87年成为国际通用总线标准ISA(Industry Standard Architecture)即工业标准结构总线.ISA是针对Intel 80286 CPU设计的,因此是16位总线,数据线16位和地址线24位,即直接内存寻址为16MB.它的工作时钟是8.33MHz,数据传输率为8.33MB/S.16位ISA总线是在8位ISA总线插槽的沿伸方向上增加了一个双排共36触点的插槽,新增的插槽引脚把8位数据和20位地址扩展成16位数据线和24位地址线.因此16位ISA插槽同8位ISA插槽保持了互换性,即16位ISA槽也可以使用8位ISA卡.低速ISA标准与高速的32位386,486和Pentium CPU形成了一定的矛盾,但为了允许保留使用老的ISA 卡,主板仍保留至少一个ISA插槽.ISA总线扩展插槽的引脚配置如图6-4所示,插槽的触点信号定义如表6-1.图6-4 ISA总线扩展插槽表6-1 ISA总线插槽的信号定义2.MCA和EISA总线这两种总线由于特定的原因,在PC机上很少采用.MCA(Micro Channel Architecture)即微通道结构总线来源于IBM PS/2机,是为32位的Intel 80386 CPU设计的.MCA是32位总线,数据线32位,地址线32位,直接内存寻址为4GB.它工作时钟为33MHz,数据传输率提高到20MB/S.它可以接16个外设.由于MCA技术不开放,且与ISA不兼容,以后在微机上很少使用.EISA(Extend Industry Standard Architecture)即扩展ISA总线,它是Compaq等兼容机厂商为对抗IBM的32位MCA总线和保持对ISA总线的兼容性而推出的.EISA支持386CPU,是32位总线.它的32位地址也可直接寻址4GB内存.EISA的工作时钟与ISA一样是8.33MHz,数据传输率是33MB/S.EISA的插槽外形与ISA一样,但在槽内的底部又增加了一排触点,用以扩充32位数据,32位地址和控制信号等.这样EISA既可用于32位扩展卡,又可兼容老的8位,16位ISA扩展卡.在EISA插槽上,EISA卡可以更深地插入,以便与下一排触点连接,取得32位支持.EISA的结构用当时的工艺技术制做是比较复杂的,因而成本很高,通常用于服务器和工作站.EISA总线扩展插槽的引脚配置如图6-5所示.图6-5 EISA总线扩展插槽3.VESA总线VESA(Video Electronic Standard Association)总线是以视频电子标准协会制定而得名,也叫VL BUS(VESA Local Bus)即VESA局部总线.它是专门为Intel 80486 CPU系统的高速视频信号处理而设计的.VESA是32位高速总线,也允许扩展到64位.它的工作时钟为33MHz,最大允许到66MHz,数据传输率高达133MB/S.VESA是在ISA总线的黑色插槽的延伸方向上增加了一个新的浅色插槽,它有双排共116个触点,单独提供32位数据线和32位地址线.因此32位的VESA总线槽同16位的ISA总线槽保持了互换性,即在VESA 扩展槽上也可以插ISA扩展卡,只是VESA扩展卡比较长.只有使用VL BUS扩展卡才能发挥它的32位高速总线的优势.最典型的VESA显示卡是ET-4000 VGA 和Trident 9440 VL-BUS Graphics Adaptor等.VL BUS还允许在32位插槽上再延长一个50引脚的插槽,从而扩展为64位的VESA总线.32位的VESA 总线扩展插槽的引脚配置如图6-6所示.图6-6 VESA总线扩展插槽6.2.2 目前主流总线标准6.2.2.1 PCI总线PCI(Peripheral Component Interconnect)即外部设备互联总线,顾名思义,它的初衷就是使外设主芯片能快捷地连入系统.PCI是专门为Intel Pentium处理器设计的,它也是一种高性能的PC机局部总线(Local Bus).PCI是32位总线,工作时钟是33MHz,数据传输率为133MB/S.PCI的高速性能使之能支持各种高速设备,特别是3D图形加速卡.目前PCI扩展卡已成为微机高速扩展卡的主流,包括显示卡,声卡,Modem卡,网卡和视频卡等.目前在一些高档机上也有64位PCI总线,工作时钟提高到66MHz,数据传输率可达528MB/S.PCI还有如下优点:1.PCI支持PnP(Plug and Play)即插即用功能.2.PCI总线支持猝发数据传送方式,大大提高了总线的数据传输率.3.PCI支持总线主控和同步操作.4.PCI采用多路复用技术,可以在有限的空间里加大总线宽度,提高总线利用率.5.PCI总线通过局部总线控制器与CPU相连,因此PCI可以不依赖于CPU的主频和种类,接入的PCI设备也不影响CPU.6.主板的芯片组内含PCI桥(PCI Bridage),通过这个缓冲控制器,可以实现6个PCI扩展槽同时工作.PCI 是白色插槽独立结构,与ISA扩展卡不兼容.它的插槽每边62线,共124线.64位的PCI总线扩展槽是在32位PCI插槽上延长,每边增加32线而成.PCI总线插槽分为5V供电电源和3.3V供电电源两种,为避免这两种不同的扩展卡插错,3.3V的插槽的定位挡片Key的位置改设在12,13引脚处.电源为3.3V和5V的32位PCI总线扩展插槽的引脚配置如图6-7所示.插槽的触点信号定义如表6-2.图6-7 5V和3.3V电源的PCI扩展槽的引脚配置6.2.2.2 AGP总线AGP(Accelerate Graphic Port)即加速图形接口,它是Intel专门为Pentium Ⅱ系统的图形控制器设计的系统总线结构,它十分默契地配合着Pentium Ⅱ的高速浮点运算能力和MMX技术,目前几乎垄断了3D 图形加速卡的接口.AGP是32位数据总线,工作时钟是66MHz,数据传输率为264MB/S,是PCI的二倍.第二代增强AGP 2×的工作时钟是133MHz,数据传输率达到532MB/S,是PCI的四倍.目前奔腾III主板已采用了AGP 4×,数据宽度扩展到64位,工作时钟133MHz,数据传输率高达1GB/S.AGP总线将显示卡与主板的芯片组直接相连,进行点对点传输,所以它不是那种通用性的总线,它只用于支持AGP图形加速卡.Intel公司推出了支持AGP的440LX和BX等芯片组.Pentium II CPU,440BX和AGP的系统结构如图6-8.图6-8Pentium Ⅱ,440BX和AGP系统结构AGP加速图形接口在PC图形控制器和系统内存之间提供了高速通道,可使图形控制器直接从主内存执行纹理映射,而不必局限于少量的显示缓存中.AGP还有助于加速从CPU到图形控制器的解码视频流,不需要将预取的纹理缓存到显存中,这使得3D程序运行更快.AGP插槽完全独立于原系统总线,且与以前的图形控制芯片,PCI控制芯片和CPU不兼容.AGP插槽为棕色,124个触点分列两边和上下两排,结构较复杂.AGP扩展插槽的引脚配置如图6-9所示.Intel还推出了一种AGP Pro插槽,目的是解决显示卡的电源供应和散热问题.它比原来的AGP插槽加长,并且要占用与其相邻的PCI插槽.图6-9 AGP扩展插槽6.3 系统设备接口6.3.1 主板上的设备接口主机的重要性前面已经充分说明了,但是作为一个有效的计算机系统,外部设备也是不可或缺的.如果没有最基本的外存设备和输入输出设备,计算机主机系统就无法运行和与用户交互.微型计算机的外部设备主要包括外存设备和输入输出设备(I/O设备),常用的外部存储器有软盘和软盘驱动器,硬盘,光盘和光盘驱动器,磁带和磁带机等,常用的输入设备有键盘,鼠标,扫描仪,麦克风,数码相机,摄像机和光笔等,常用的输出设备有显示器,打印机,功放扬声器和绘图仪等.在安装新硬件时,常常要为其配置I/O口地址(I/O Port Address),端口地址是CPU访问,区别各个不同硬件设备的标志,任何设备占用的I/O口地址都不相同,而一个设备也可能占用几个连续或不连续的I/O口地址.比如声卡就可能占用0220-022FH这16个连续的I/O口地址.如果几个硬件分配了相同的I/O口地址,CPU就无法正确访问它们,这些硬件也就无法正常工作,这种故障叫做I/O口地址冲突.由于外部设备各自的特点,主机与外设间交换的信息载体形式(模拟,数字,电压,电流),数据传送的速率和方式(串行,并行)等都会有所不同,因此必须在它们之间建立多种数据转换和缓冲的界面,这就是各种规格的输入输出接口(Input/Output Interface Port),简称I/O接口.微机采用的通信接口标准有计算机专用的也有电器设备领域通用的,有某一类外设专用的也有不同外部设备通用的.专用接口如硬盘接口IDE,键盘鼠标接口PS/2和显示器接口(VGA口)等.通用I/O通信接口按其数据传送的形式不同可以分为串行接口和并行接口两大类.串行接口是用一条线路将二进制数据按顺序一位位地传送,每个时钟传送一位,至少8个时钟才能传送1字节二进制数据.它的特点是线路简单但速度较慢,适合于慢速远距离的数据传送.例如RS-232C串行接口就用于鼠标器,Modem和终端等.并行接口是用8条线路同时分别传送1字节二进制数据的8位,1个时钟就可以传送1字节二进制数据.它的特点是线路复杂(8条数据线)但速度较快,适合于快速近距离的数据传送.例如通用并行接口就用于打印机,扫描仪等外设.软盘,硬盘和光盘等也都采用专门的并行接口.在早期的PC机上,各个I/O接口都集中做在一块"I/O多功能卡"上,包括1个软盘口,1或2个硬盘口,2个通用串口,1个通用并口和1个游戏棒口,将此卡插入ISA槽便使系统增加了各个接口的功能.到了586机,就把接口的控制芯片集成到主板上,进一步地又把接口控制功能集成到南桥芯片中,把各个接口插座直接做到主板后沿,形成标准ATX主板.这样就简化了结构,提高了接口性能和可靠性,还降低了成本.6.3.2 硬件I/O接口的系统资源1.硬件设备的I/O端口地址CPU与外设之间的访问要通过硬件的I/O接口,相互交换的数据要在I/O接口电路的数据缓冲寄存器中暂存,CPU控制硬件工作方式和速度的命令也要存入I/O接口电路的控制寄存器,这些寄存器统称为I/O端口.CPU正是通过访问硬件设备的各个I/O端口来控制该设备工作的,因此所有设备的I/O端口寄存器都必须统一编码,并且不能重复.系统会自动(或用户手工)为每个设备的各个端口分配相应的I/O口地址.下面是在Windows 98系统工具的"系统信息"窗口中摘录的某一台微机从0000-04D1H段的I/O口地址的硬件占用情况:x0000-xFFFF……(也可以见:控制面板,系统,设备管理,计算机属性)要求熟悉几个基本硬件的I/O口地址:串口1(COM1)3F8-3FF,串口2(COM2)2F8-2FF,并口1(LPT1)即打印机378-37B,声卡的游戏棒,声音SB16,MIDI(MPU401)和声音WSS,显示卡,标准IDE硬盘控制器170-177和370-377,标准软盘控制器3F0-3F5.2.硬件设备的IRQ号一些硬件设备除了占用I/O端口地址外,还具有向CPU申请硬件中断的能力,因此还占有中断请求(IRQ)号的系统资源.PC系统的IRQ中断号共有16个(IRQ 0-15),可以分配给16个设备使用,每个设备单独占用一个IRQ号.当某个设备向CPU发出中断申请,CPU可以根据其IRQ号加以响应,运行相应的中断处理程序.下面是在Windows 98系统工具的"系统信息"窗口中摘录的某一台微机的16个IRQ中断申请号的分配情况:IRQ0-15(也可以见:控制面板,系统,设备管理,计算机属性)3.硬件设备的DMA通道号DMA(Direct Memory Access)是某些数据量大的硬件设备与主机快速交换数据的特殊工作方式,如软盘,硬盘,声卡等.在DMA控制器的控制下,设备与内存直接交换数据,并不占用CPU时间,CPU再与内存交换数据.因此DMA方式比CPU直接访问速度较慢的设备的方式要高效得多.PC系统的DMA通道共有8个(DMA0-7),DMA通道号不一定被一个设备独占,几个硬件设备可以共用一个DMA通道,只要它们不是同时使用它.下面是在Windows 98系统工具的"系统信息"窗口中摘录的某一台微机的8个DMA通道号的分配情况:DMA0-7(也可以见:控制面板,系统,设备管理,计算机属性)6.3.3 标准串行接口和并行接口1.串行接口PC机通常配置有两个RS-232C异步串行通信接口和一个并行接口.串口一的逻辑名为COM1/COM3,9针D型插座,通常用来接鼠标.串口二的逻辑名为COM2/COM4,25针D型插座,连接Modem,数码相机和磁卡机等外设.串行接口的9针和25针插座针孔配置见图6-10,各针孔的信号定义如表6-3.图6-10 串口插座针孔配置2.并行接口标准并行接口的逻辑名为LPT1,也叫打印机接口(Printer),是一个25针的D型插座,用来连接打印机和扫描仪等外设.并行接口插座针孔配置见图6-11.各针孔的信号定义如表6-4.图6-11 并口的引脚配置在BIOS Setup中,并行接口有Normal,EPP和ECP三种模式供选择.Normal接口是一种低速的并口模式,也叫SPP(Singl Parallel Port)即单向并口,它的数据传输率为40Kb/S,适合将结果输出到普通打印机上,所有并口外设都支持此种模式.EPP接口(Enhanced Parallel Port)即增强并行接口,在外部设备间进行双向通信,数据传输率在400Kb/S 以上.目前多数打印机和扫描仪都支持EPP模式.ECP接口(Extended Capabilities Port)即扩展并行接口,具有和EPP一样高的速率和双向通信能力,但在多任务环境下,它能使用直接存储器访问方式(DMA),所需缓冲区也不大.但ECP模式容易引起冲突.许多新型的并行设备,如激光打印机,扫描仪等要求EPP,ECP或EPP+ECP模式.因此在CMOS Setup中应根据设备的要求适当选择并口模式.6.3.4 新型串口USBUSB(Universal Serial Bus)是通用串行总线,是一种新型高速串行接口.USB仅用一个4针方形标准插座,采用菊花链的形式就可以把许多外设逐一连接起来,并且不会损失信号带宽.USB的推出使得接口性能大大提高,主机与外设的连接变得非常简单和有效,它正在逐步取代PC机上原有的串行,并行等各种接口.目前USB能支持的外设有扫描仪,数码相机,打印机,显示器,键盘,鼠标等.要使用USB设备,就要求主板和操作系统都支持USB接口.Pentium以上的主板一般都采用了支持USB 的芯片组和BIOS程序,主板上也都有USB插座.Windows 97,98和NT4.0等都支持USB接口.如果使用早期的Windows 95和NT 3.0等,就需要安装USB接口驱动程序.最后还需在安装了USB设备后安装相应的设备驱动程序.目前市场上有USB扩展卡,将其插到PCI插槽上,引导Windows 98后就可以方便地为系统增加两个USB.Pentium MMX主板上一般有一个10针的双USB接口,需要用USB转接电缆将两个USB插座引出. 与以往的接口相比,USB有许多优点:B的12Mb/s的数据传输率比以前的串口快100倍,比并口快10倍,即使多个设备接在一个USB口上,也能获得满意的操作速度.B接口允许带电"热插拔"设备,无须关机.而且USB接口控制器可以立即感知拔去或插上的设备,直接驱动,无须重新启动系统.因此只有USB设备才算是真正意义的即插即用设备.B接口设备可采用"级联"方式连接,即每个接入设备也提供一个USB插座供下一个设备连接.一个USB控制器可以支持最多127个设备,每个设备的连接电缆可长达5米.B接口可以向外部提供+5V,0.5A电源,这使得一些小功率的外设可以省去自身的电源电路.B接口简单可靠,4个连线分别是:+5V电源,信号1(-),信号2(+)和接地GND.6.3.5 新型串口IEEE 1394IEEE 1349是一种新型高效的串行接口,它与USB有不少相似之处.它使用六芯电缆,包括两对双绞线信号线和两根电源线.它的最大传输电流可达1.5A,传输数据的直流电压可以在8到40V之间变换.1394与USB一样,也可以"热插拔",是真正的即插即用接口.它也向外设提供电源,也采用串行链接方式,可以连接多台设备.1394与USB的主要差别在于它无须Hub就可以连接63台设备.1394还规定了两种传输模式,一种是传输速率为12.5,25或50Mb/S的底版模式(Backplane Mode),另一种是传输速率为100,200或400Mb/S的电缆模式(Cable Mode).在400Mb/S时只要用50%的带宽就可以支持高质量的数字化视频信息流.IEEE1394的传输速率远高于USB,它支持的产品范围也涵盖了USB,所以IEEE1394应该比USB更具前景.但是由于IEEE1394的技术要求和生产成本较高,目前价格昂贵,还很少被家用和商用PC采用.习题1.微机系统有哪几类总线,总线的三个组成部分是什么2.掌握ISA,VESA,PCI和AGP总线的规格和特点.3.掌握串口,并口的规格,特点和系统资源.4.掌握USB接口的规格和特点.。

基于ISA部线的微机接口板的研究与设计实例

/ L W (/ 写 命 令 输 出 ) 信 号有 效 时 把 数 据 总 线 上 的数 据 写 至 所 选 中 的 I O设 备 接 口 SO I 0 : /

中.

/ E ( M MR 存储器读 命令 j信 号 效 时, : 有 将所选 中的存储单 元 的数据 读到数据 总线. O C 是 一个周期 为 7 n ( S: 0 s 频率为 1 . 1 M Z 的高 速时钟. 4 38 H ) C K: 一 个 6—8 Z的 系统 时钟 . L 是 MH RE E/ “ 位 驱 动 ” 号 , 于 在 系 统 初 始 加 电时 或 线 电 压 消 失 时 复 位 或 初 始 化 系 统 逻 S' 复 ’ : 信 用 辑 . 信 号高 电 平有 效 . 此

1 总线 与地 址 空 间

11 IA总 线 . S

IA 总 线 共 有 9 S 6个 信 号 引 脚 , 中 包 括 地 址 线 、 据 线 、 c G D、 、 控 制 信 号 等 ( 其 数 Vc 、 N 读 写 这

里仅介绍 部分 引脚 , 余请 读者参 阅参考文献 [ 】 其 1) S 0~S 9 2 A AI (0根 地 址 线 )这 些 信 号用 来 对 系统 中 的存 储 器 与 I O设 备 寻址 . : / S0 D ( D ~S 7 8位职 向数据线 j为 C U 存 储器及 I O设备 提供数据 信息 传输 通道 . : P、 / A N( E 地址锁 存 允许 输出信 号 )A E有效 时, A E的下 降沿处 把来 自 C U的地 址进行 :L 在 L P

0 0 一0 F 被 系 统 板 使 用 0H FH

1 O 一1 S 硬 盘 FH FH

2 0 ~2 F 游 戏 I 0 口 0H 0H / 2 8 ~2 F 并 行 打 印 口 2 7H 7H

ISA总线

一、ISA插槽:基于ISA总线的扩展插槽ISA插槽ISA插槽是基于ISA总线(Industrial Standard Architecture,工业标准结构总线)的扩展插槽,其颜色一般为黑色,比PCI接口插槽要长些,位于主板的最下端。

其工作频率为8MHz左右,为16位插槽,最大传输率16MB/sec,可插接显卡,声卡,网卡以及所谓的多功能接口卡等扩展插卡。

其缺点是CPU资源占用太高,数据传输带宽太小,是已经被淘汰的插槽接口。

目前还能在许多老主板上看到ISA插槽,现在新出品的主板上已经几乎看不到ISA插槽的身影了,但也有例外,某些品牌的845E 主板甚至875P主板上都还带有ISA插槽,估计是为了满足某些特殊用户的需求。

最早的PC总线是IBM公司1981年在PC/XT 电脑采用的系统总线,它基于8b it的8088 处理器,被称为PC总线或者PC/XT总线。

在1984年的时候,IBM 推出基于16-bit Intel 80286处理器的PC/AT 电脑,系统总线也相应地扩展为16bit,并被称呼为PC/AT 总线。

而为了开发与IBM PC 兼容的外围设备,行业内便逐渐确立了以IBM PC 总线规范为基础的ISA(工业标准架构:Industry Standard Architect ure )总线。

ISA 是8/16bit 的系统总线,最大传输速率仅为8MB/s ,但允许多个CPU 共享系统资源。

由于兼容性好,它在上个世纪80年代是最广泛采用的系统总线,不过它的弱点也是显而易见的,比如传输速率过低、CPU占用率高、占用硬件中断资源等。

后来在PC‘98 规范中,就开始放弃了ISA 总线,而Intel 从i810 芯片组开始,也不再提供对ISA 接口的支持。

使用286和386SX以下CPU的电脑似乎和8/16bit ISA 总线还能够相处融洽,但当出现了32-bit 外部总线的386DX处理器之后,总线的宽度就已经成为了严重的瓶颈,并影响到处理器性能的发挥。

PCI总线与ISA总线转换设计研究

P L X公 司的 P C I 9 0 5 2 、 P C I 9 0 5 4等。使 用这 类专用 芯片 开发 P C I

STUDY oN PCI BUS AND I SA BUS CoNVERS I oN D o

( D e p a r t m e n t o fC o m p u t e r S c i e n c e a n d T e c h n o l o g y, D e z h o u U n i v e r s i t y , D e z h o u 2 5 3 0 2 3 , S h a n d 。 n g, C h i n a )

总线接 口电路设计 、 I S A总线接 口电路设计和 I / O检测模块 设计 ; 介 绍 串行 E E P R O M 9 3 L C 4 6 B的接 口设计 与配置 ; 最后对 I / O检测 模块和 基于 I S A接 口设备进行调试 , 调试 结果及 实践表 明该设 计可行 、 合理 、 有用。

关键词 P C I总线 T P 3 9 1 I S A总线 P C B E E P R O M A D O I : 1 0 . 3 9 6 9 / j . i s s n . 1 0 0 0 — 3 8 6 x . 2 0 1 3 . 0 8 . 0 6 5

中图分类号

文献 标 识 码

第3 O卷 第 8期

2 0 1 3年 8月

计 算机 应 用与软 件

C o mp u t e r Ap p l i c a t i o n s a n d S o f t wa r e

V0 1 . 3 0 No . 8

Au g .2 01 3

P C I 总线与 I S A 总 线 转换 设计 研 究

ISA(PC104)总线信号时序简介

ISA(PC/104) 总线信号时序简介SBS Science & Technology Co., Ltd.APPN-002ISA(PC/104)总线信号时序简介目录1.0 ISA概况 2.0 ISA文献2.1 ISA规范 2.2 ISA书籍3.0 ISA结构形式 4.0 PC/104结构形式 5.0 ISA信号描述 6.0 ISA时序图 7.0 ISA信号用法 8.0 ISA连接器引脚 9.0 PC/104总线连接引脚盛博科技1APPN-002ISA(PC/104)总线信号时序简介1.0 ISA 概况ISA总线 即工业标准结构 Industry Standard Architecture 十世纪八十年代早期IBM在佛罗里达州Boca Raton研发实验室 出的个人电脑 其中包括了8位ISA总线 1984年 最早起源于二 IBM于1981年推IBM推出了PC-AT 这是第一个全面实现16位结构的ISA总线 IBM最初命名的 AT总线 首先被记录于IBM出版的 The PC-AT TechnicalReference 上 此书包括了图表和BIOS清单 这样类似于康柏的其它公司很容易 就生产出了IBM兼容的产品 由于IBM将 AT总线”作为一项商标进行保护 其它生产兼容IBM产品的公司就不能使用 AT总线 这个名称 结果 人们在行业 中创造了 ISA 并将其作为这种总线的新名称 这个名称最后被包括IBM在内的所有公司采用 尽管 The PC-AT Technical Reference 包含了详细的图表和BIOS清单 但其 因未包含严格的时序 规范及其它必要条件而未成为一个很好的总线规范 结果 对ISA各种各样的实现造成了一些产品之间的兼容性问题 的问题 迄今为止 渐渐形成了许多ISA总线规范 但是不幸的是 为了减轻因兼容造成 这些规范也不尽相同没有产生出一个完全统一的ISA总线规范2.0 ISA 文献2.1 ISA 规范有关ISA总线规范的文档有如下几篇 EISA Specification, Version 3.12――这篇文档包括ISA总线规范 并规定了 扩展工业标准结构 定义了ISA总线上32位扩展 IEEE Draft Standard P996 这篇文档描写了标准PC类系统的机械和电 子规范 通过/.付费可以向IEEE订购 PS/2 Technical Reference 这篇来自IBM的文档内容包括在一些IBM计 算机PS/2线上使用ISA总线的信号定义和时序图2.2 ISA书籍两本对ISA总线进行了详细描述的书是 ISA & EISA Theory and Operation, by Edward Solari. (Annabooks) (ISBN 0-929392-15-9) ISA System Architecture, by Don Anderson and Tom Shanley. (MindShare) (ISBN 0-201-40996-8)盛博科技2APPN-002ISA(PC/104)总线信号时序简介3.0 ISA结构形式8 位卡:(At the card)(At the computer)16 位卡:(At the card)(At the computer)盛博科技3APPN-002ISA(PC/104)总线信号时序简介4.0 PC/104结构形式与ISA板不同 义相同PC/104 8位/16位总线模块具有同样尺寸 全为地 Gnd与ISA板总线信号定但多A32/B32;C0/D0;C19/D19引脚盛博科技4APPN-002ISA(PC/104)总线信号时序简介5.0 ISA 信号描述SA19-SA0System Address 地址位19:0用于对系统中内存和I/O设备的寻址 内存寻址时 使用SA19:SA0配合LA23:LA17 能寻址多达16兆的内存 低16位,可以用来定位64K的I/O地址 号在BALE为高时有效 持有效 SA19是最高位 I/O寻址中 只使用 地址信SA0为最低位而由BALE的下降沿锁定通过读或写命令使信号保 但也可以由ISA这些信号通常由系统微处理器或DMA控制器驱动扩展板的Bus Master 来取得ISA总线的控制权LA23-LA17Unlatched Address 23:17位是系统中内存地址 址多达16兆的内存 它们和SA19:SA0可以共同寻 由于它们是非锁存的 当BALE为高时这些信号才有效故在整个总线周期中它们并不总是保持有效状态 用BALE下降沿锁存这些信 号的译码AENAddress Enable 用于DMA传送过程中关闭总线系统微处理器和其它设备的 传送通道 制 当AEN有效时 总线上的地址 数据和读写信号由DMA控制器控 以防止DMA周期中出现不正确ISA扩展板的片选译码应包含AEN信号的片选BALEBuffered Address Latch Enable 用来锁存LA23:LA17信号或者译码这些信号 BALE下降沿用于锁存LA23:LA17 在DMA周期中BALE被强制为高 此信号 与AEN并用时表明一个有效的微处理器或DMA地址CLKSystem Clock 是一个自行运转的时钟 它的频率一般在7MHz到10MHz之间 系统时钟在一些ISA板的应用中保证与 该频率值在ISA标准中并未严格定义 系统微处理器的同步工作盛博科技5APPN-002ISA(PC/104)总线信号时序简介SD15 - SD0System Data SD15:SD0是ISA总线上的数据总线 最低位 8位设备的数据传送通过SD7:SD0来完成 其中SD15是最高位 SD0是 SD15:SD0则用于传送16位设备的数据 当16位设备向8位设备传送数据时 需将16位信号转换成两个8位 周期通过SD7:SD0来进行传送-DACK0 to -DACK3 and -DACK5 to -DACK7DMA Acknowledge 0:3和5:7分别被用来确认DRQ0:DRQ3和DRQ5:DRQ7的 DMA请求DRQ0 to DRQ3 and DRQ5 to DRQ7DMA Requests 用于ISA板向DMA控制器提出服务请求 或者Bus Master设备 申请总线控制权的请求 多个DMA请求可能同时断定有效 发出请求的设备必须保持请求信号有效直到系统板发出相应的DACK信号-I/O CH CKI/O Channel Check I/O CH CK由ISA板生成进而引发非屏蔽中断 时表明发现了不可恢复的错误 当它有效I/O CH RDYI/O Channel Ready 允许较慢速ISA板通过插入等待状态 延长I/O或内存读写 周期 好 I/O CH RDY通常处于高 以插入等待状态 就绪 ISA板将I/O CH RDY拉低 未准备使用I/O CH RDY插入等待状态的设备需可以完成读写周期时 地址译码和读/写信号有效后立即使I/O CH RDY信号为低 当设备释 放 I/O CH RDY回高-IORI/O Read 线上 由总线控制设备驱动 并且指令所选的I/O设备将数据读到数据总-IOWI/O Write 由总线控制设备驱动 指令所选的I/O设备从数据总线上获取数据盛博科技6APPN-002ISA(PC/104)总线信号时序简介IRQ3 to IRQ7 and IRQ9 to IRQ12 and IRQ14 to IRQ15Interrupt Requests 向系统微处理器发出信号 提示来自ISA板的请求 当IRQ 线由低向高跳变时产生中断请求 请求必须一直保持为高直到CPU通过其中断 服务程序确认了这个请求 请求有不同的优先权 来自IRQ9:IRQ12 而来自IRQ3:IRQ 7IRQ14 :IRQ15的请求优先被处理 的请求较后处理 IRQ7优先级最低IRQ9优先级最高-SMEMRSystem Memory Read 指令一个所选定的Memory设备将数据送到数据总线 该信号仅在对1M以内的Memory空间读时才有效 SMEMR来源于MEMR及低 于1兆的存储译码-SMEMWSystem Memory Write 指令将当前数据总线上的数据写入一个所选定的 Memory设备 该信号仅在对1M以内的Memory空间写时才有效 SMEMR来源 于MEMR及低于1兆的存储译码-MEMRMemory Read 指令将一个所选定的Memory设备数据读出送到数据总线 它在 整个Memory存储读周期中都有效-MEMWMemory Write 指令将当前数据总线上的数据存储到一个所选定的Memory设 备中 它在整个Memory存储写周期中都有效-REFRESHMemory Refresh 该信号为低时表明正在进行内存刷新操作OSCOscillator 是一个时间段为70毫微秒的时钟(14.31818 MHz) 该信号与系统时 钟不同步盛博科技7APPN-002ISA(PC/104)总线信号时序简介RESET DRVReset Drive在电源开启或系统复位时来复位或初始化系统逻辑 高电平有效TCTerminal Count 在DMA通道操作中当计数完成时产生的终端计数信号-MASTERMaster 和DRQ线一起获得ISA板上ISA总线的控制权 后 权 设备将MASTER信号拉低 在此状态下 使得其获得系统地址 当接收到一个DACK 数据和控制线的控制 在读/设备将在驱动地址和数据线之前等待一个时钟周期写命令之前等待两个时钟周期-MEM CS16Memory Chip Select 16 ISA板将该信号拉低以指示这是一个16位的Memory读 写操作 它由LA23:LA17地址线译码来驱动-I/O CS16I/O Chip Select 16 I/O设备将该信号拉低以指示这是一个16位的Memory读写操 作 它由SA15:SA0地址线译码来驱动-0WSZero Wait State 由一个总线从设备驱动使其拉低 状态即可完成一个总线周期 由地址译码产生 说明不插入任何额外等待 -OWS 完成一个无需等待的16位Memory周期-SBHESystem Byte High Enable 该信号为低时表明数据在数据总线高位部分传送(D15 至 D8)盛博科技8APPN-002ISA(PC/104)总线信号时序简介6.0 ISA总线时序图8位 I/O 总线周期BALE SA(15:0) -SBHE -IOR/W SD(7:0) (READ) SD(7:0) (WRITE) I/OCHRDY ________ __| |_________________________________________ _ ______________________________________________ __ _><______________________________________________><__ ______________ _______ |______________________________| _____________ -------------------------------------<_____________>__________________________________ ----------------<__________________________________>__________________ _ _ _ _ _ _ _ _ _ _ _ _ _________ |________________________|8 位 Memory 总线循环_____ ________| |______________________________________ _ ________________ ________________________________ LA(23:17) _><________________><________________________________ _______ ________________________________________ __ SA(19:0) _______><________________________________________><__ ______________ _______ -MEMR/W |______________________________| _____________ SD(7:0) -------------------------------------<_____________>(READ) __________________________________ SD(7:0) ----------------<__________________________________>(WRITE) __________________ _ _ _ _ _ _ _ _ _ _ _ _ _________ I/OCHRDY |________________________| BALE盛博科技916位I/O总线周期________BALE ______________| |_____________________________ _____________ __________________________________ __ SA(15:0) _____________><__________________________________><__ _________________ ___ -IOCS16 |_______________________________|_____________________ ______ -IOR/W |________________________|__________________SD(15:0) -----------------------------<__________________>---- (READ)________________________SD(15:0) -----------------------<________________________>---- (WRITE)_______________________ _ _ _ _ _ _ _ _ _ _ ______I/OCHRDY |___________________|16位Memory总线周期1个或多个等待状态______BALE _________________| |____________________________ ___ ________________________ ______________________ LA(23:17) ___><________________________><______________________ ________________ ________________________________ _ SA(19:0) ________________><________________________________><_ _______ ______________________ -MEMCS16 |______________________|________________________ ______ -MEMR/W |_____________________|_______________SD(15:0) --------------------------------<_______________>---- (READ)_____________________SD(15:0) --------------------------<_____________________>---- (WRITE)__________________________ _ _ _ _ _ _ _ _ __________ I/OCHRDY |_______________|6位Memory总线周期0等待状态______BALE _________________| |____________________________ ___ ________________________ ______________________ LA(23:17) ___><________________________><______________________ ________________ _________________________ ________ SA(19:0) ________________><_________________________><________ _______ ______________________ -MEMCS16 |______________________|_________________________ ______________________ -0WS |____|________________________ ________________ -MEMR/W |___________|______SD(15:0) --------------------------------<______>------------- (READ)____________SD(15:0) --------------------------<____________>------------- (WRITE)DMA读______________DRQ(n) __| |___________________________________ _______________ __________ -DACK(n) |__________________________|____________________________________AEN,BALE ________| |_______ _______________ ___________________________ _______ SA(15:0) _______________><___________________________><_______ -SBHE________________ ________________________ _________ SA(19:16) ________________><________________________><_________ LA(23:17)____________________ __________ -MEMR |_____________________|____________SD(15:0) -------------------------------<____________>-------- ______________________ ___________ -IOW |__________________|__________TC _______________________________| |__________ ________________________ _____________________ I/OCHRDY |______|DMA写______________DRQ(n) __| |___________________________________ _______________ __________ -DACK(n) |__________________________|____________________________________AEN,BALE ________| |_______ _______________ ___________________________ _______ SA(15:0) _______________><___________________________><_______ -SBHE________________ ________________________ _________ SA(19:16) ________________><________________________><_________ LA(23:17)____________________ __________ -IOR |_____________________|____________SD(15:0) -------------------------------<____________>-------- ______________________ ___________ -MEMW |__________________|__________TC _______________________________| |__________ ________________________ _____________________ I/OCHRDY |______|Bus Master周期___________________________________DRQ(n) __| |______________ _______________ __________ -DACK(n) |__________________________|__________________ _______ -MASTER |__________________________|__________________ _______ AEN ________| |__________________________| |_ _____________________________________________________ BALE ________| |_ ________________________ ___________ ______________ SA(19:0) ________________________><___________><_______________ -SBHE________________________ ___________ ______________ LA(23:17) ________________________><___________><___________________________________________ _________________ -IOR,-IOW |_____|-MEMR,-MEMW_____SD(15:0) -------------------------------<_____>---------------内存刷新周期_______________ _______________ -REFRESH |_____________________|_________________ ____________ ____________________ SA(9:0) _________________><____________><____________________ ______________________ ________________ -SMEMR |_____________|_________________________ _ _ _ _ ___________________ I/OCHRDY |_______|7.0 ISA信号用法图例I/O = 输入/输出I = 输入O = 输出- = 不需要的信号I/O出现在括号里表明这个信号是可选信号下表是ISA系统板上典型的信号使用情况Signal Name System Board Usage Signal Name System BoardUsageAEN O-MEM CS16 I/O BALE O-MEMR I/O CLK O-MEMW I/O -DACK O OSC O DRQ I-REFRESH I/O -IO CS16 I RESET DRV O -I/O CH CK I SA I/O I/O CH RDY I/O SD I/O -IOR I/O-SBHE I/O -IOW I/O-SMEMR I/O IRQ I-SMEMW I/O LA I/O TC I/O -MASTER I-0WS I下表是ISA扩展板上典型的信号使用的情况Signal Name ISA BusMasterISA 16-bitMem SlaveISA 16-bitI/O SlaveISA 8-bitMem SlaveISA 8-bitI/O SlaveISA DMADeviceAEN --I-I-BALE -I-(I)--CLK (I)(I)(I)(I)(I)(I) -DACK I----I DRQ O----O -IO CS16 I-O----I/O CH CK(O)(O)(O)(O)(O)(O) I/O CH DY I(O)(O)(O)(O)--IOR O-I-I I -IOW O-I-I I IRQ (O)(O)(O)(O)(O)(O) LA(23:17) O I-(I)---MASTER O------MEM CS16 I0-----MEMR O I-(I)---MEMW O I-(I)--OSC (I)(I)(I)(I)(I)(I) -REFRESH (O)I-I--RESET DRV I I I I I I SA(16:0) O I I I I-SA(19:17) -(I)-(I)--SD(7:0) I/O I/O I/O I/O I/O I/O SD(15:8) I/O I/O I/O--(I/O) -SBHE O I I----SMEMR ---I---SMEMW ---I--TC -----(I) -0WS -(O)-(O)(O)-8.0 ISA 连接引脚Signal Name Pin Pin Signal Name Ground B1A1-I/O CH CK RESET DRV B2A2SD7+5 V dc B3A3SD6IRQ 9B4A4SD5-5 V dc B5A5SD4DRQ2B6A6SD3-12 V dc B7A7SD2-0WS B8A8SD1+12 V dc B9A9SD0Ground B10A10I/O CH RDY -SMEMW B11A11AEN-SMEMR B12A12SA19-IOW B13A13SA18-IOR B14A14SA17-DACK3B15A15SA16DRQ3B16A16SA15-DACK1B17A17SA14DRQ1B18A18SA13-REFRESH B19A19SA12 CLK B20A20SA11IRQ7B21A21SA10IRQ6B22A22SA9IRQ5B23A23SA8IRQ4B24A24SA7IRQ3B25A25SA6-DACK2B26A26SA5TC B27A27SA4BALE B28A28SA3+5 V dc B29A29SA2OSC B30A30SA1Ground B31A31SA0Key Signal Name Pin Pin Signal Name -MEM CS16D1C1-SBHE-IO CS16D2C2LA23IRQ10D3C3LA22IRQ11D4C4LA21IRQ12D5C5LA20IRQ15D6C6LA19IRQ14D7C7LA18-DACK0D8C8LA17DRQ0D9C9-MEMR -DACK5D10C10-MEMWDRQ5D11C11SD08-DACK6D12C12SD09DRQ6D13C13SD10-DACK7D14C14SD11DRQ7D15C15SD12+5 V dc D16C16SD13-MASTER D17C17SD14Ground D18C18SD159.0 PC/104总线引脚引脚信号名用途In/OutA1 -IOCHCK Bus NMI input INA2 SD7 Data Bit 7 I/OA3 SD6 Data Bit 6 I/OA4 SD5 Data Bit 5 I/OA5 SD4 Data Bit 4 I/OA6 SD3 Data Bit 3 I/OA7 SD2 Data Bit 2 I/OA8 SD1 Data Bit 1 I/OA9 SD0 Data Bit 0 I/OA10 IOCHRDY Processor Ready Ctrl INEnable I/O A11 AEN AddressA12 SA19 Address Bit 19 I/OA13 SA18 Address Bit 18 I/OA14 SA17 Address Bit 17 I/OA15 SA16 Address Bit 16 I/OA16 SA15 Address Bit 15 I/OA17 SA14 Address Bit 14 I/OA18 SA13 Address Bit 13 I/OA19 SA12 Address Bit 12 I/OA20 SA11 Address Bit 11 I/OA21 SA10 Address Bit 10 I/OA22 SA9 Address Bit 9 I/OA23 SA8 Address Bit 8 I/OA24 SA7 Address Bit 7 I/OA25 SA6 Address Bit 6 I/OA26 SA5 Address Bit 5 I/OA27 SA4 Address Bit 4 I/OA28 SA3 Address Bit 3 I/OA29 SA2 Address Bit 2 I/OA30 SA1 Address Bit 1 I/OA31 SA0 Address Bit 0 I/OA32 GND Ground N/APC/104总线接口P1A引脚信号名用途In/OutB1 GND Ground N/AReset OUT B2 RESET SystemPower N/A B3 +5V +5vB4 IRQ9 Int Request 9 INPower N/A B5 -5V -5vB6 DRQ2 DMA Request 2 INPower N/A B7 -12V -12vB8 ENDXFR Zero wait state INPower N/A B9 +12V +12vPin N/A B10 N/A KeyB11 -SMEMW Mem Wrt, Io 1M I/OB12 -SMEMR Mem Rd, Io 1M I/OWrite I/O B13 -IOW I/Oread I/O B14 -IOR I/OB15 -DACK3 DMA Ack 3 OUTB16 DRQ3 DMA request 3 INB17 -DACK1 DMA Ack 1 OUTB18 DRQ1 DMA request 1 INB19 -REFRESH MemoryRefresh I/OClock OUTB20 SYSCLK SysB21 IRQ7 Int Request 7 INB22 IRQ6 Int Request 6 INB23 IRQ5 Int Request 5 INB24 IRQ4 Int Request 4 INB25 IRQ3 Int Request 3 INB26 -DACK2 DMA Ack 2 OUTCount OUT B27 T/C TerminalB28 BALE Addrs Latch En OUTPower N/A B29 +5V +5vClk OUT B30 OSC 14.3MHzB31 GND Ground N/A B32 GND Ground N/APC/104总线接口P1B引脚信号名用途In/OutC0 GND Ground N/A C1 SBHE Bus High Enable I/OC2 LA23 Address bit 23 I/OC3 LA22 Address bit 22 I/OC4 LA21 Address bit 21 I/OC5 LA20 Address bit 20 I/OC6 LA19 Address bit 19 I/OC7 LA18 Address bit 18 I/OC8 LA17 Address bit 17 I/ORead I/O C9 -MEMR MemoryWrite I/OC10 -MEMW MemoryC11 SD8 Date Bit 8 I/OC12 SD9 Date Bit 9 I/OC13 SD10 Date Bit 10 I/OC14 SD11 Date Bit 11 I/OC15 SD12 Date Bit 12 I/OC16 SD13 Date Bit 13 I/OC17 SD14 Date Bit 14 I/OC18 SD15 Date Bit 15 I/OPin N/AC19 Key KeyPC/104总线接口P2C引脚信号名用途In/OutD0 GND Ground N/A D1 -MEMCS16 16-bit Mem Access IND2 -IOCS16 16-bit I/O Access IND3 IRQ10 Interrupt Request 10 IND4 IRQ11 Interrupt Request 11 IND5 **D6 IRQ15 Interrupt Request 15 IND7 IRQ14 Interrupt Request 14 IND8 -DACK0 DMA Acknowledge 0 OUTD9 DRQ0 DMA Request 0 IND10 -DACK5 DMA Acknowledge 5 OUTD11 DRQ5 DMA Request 5 IND12 -DACK6 DMA Acknowledge 6 OUTD13 DRQ6 DMA Request 6 IND14 -DACK7 DMA Acknowledge 7 OUTD15 DRQ7 DMA Request 7 INPower N/A D16 +5V +5VD17 -MASTER Bus Master Assert IND18 GND Ground N/A D19 GND Ground N/APC/104总线接口P2D。

高精度ISA总线测试板卡设计

墨 皇 燕查 o 年第4 总第15 2 期 3 期

收 稿 日期 :2 0 —0 — 1 02 2 5

高精度 IA总线测试板卡设计 S

Hi gh— pr c s o sg b u S Bu s a d — e i i n De i n a o tI A s Te tBo r

史镇 风

Ai e g e g Zh n fn

( 安 电子 科 技 大 学 西

( iiy i ,Xi . 7 0 7 j ’ 札 1  ̄ 1

摘

要

舟绍 丁Wid ws9 n o 8环境 下基于 P C机 工生控制 器自动测试 系统 .着重论速 丁如何保证 自行设计 的IA 总 S

Ke ywor s m a ge en om p e e e d na m tofc ut rc nt r,PC o k,I c r lc C a d

t

A道I控通D 卜 O A业O 通 _ 通 通 制道f 工器 道 _ 道D

图 1 测 试 系统 总 体 框 图

( O,D A O)和 控 制器的信 号输 人端 ( ,DI AI )连接 ,

Ab t a t I t o u e e i n p o o e a d i mp e n a i n a o ta t le s o u e n g me ts s e o h e e rn s r c n r d c d a d s r p s n t i lme t t b u m v r M c mp t rma a e n y t m ft e r fr ig g s o c m p t rt r n l n a p b i i f r t n c n e n wh c l t e t r ia s a e c n e t d t r u h L c l e wo k o u e e mi a u l n o ma i e t r i ih a l h e m n l r o n c e h o g o a t r .Ths ma a e n i c o n i n g me t s s e i c mp s d o p c a h wa e o t r e mi a a d s f wa eil e  ̄ v rb s d o id wsOS M am va o t h y t m s o o e fas e i[ a d r ,s fwa e i t r n [ n o t r r n ts r e a e n W n o r n i b u e t d sg f h p ca h r wa e wh c sb s d O lt e u i g o C c r .e p c _ h e i n wo k o o t p o et e s s e s e i n o e s e il a d r i h i a e i h sn fI a d t s e i 1 t e d sg r fh w O i r v h y t m’ ly m s c r y a d r l blt h o g a d r . e u i n e i i y t r u h h r wa e t a i

(单片机原理与应用实验)实验12SPI总线接口

本实验介绍SPI总线接口的工作原理、通信原理、接口电路、数据传输操作、 实验过程,以及可能遇到的问题和解决方法,最后总结实验心得。

SPI总线简介

SPI(Serial Peripheral Interface)总线是一种串行通信协议,用于在微控制器和外部设备之间进 行高速、全双工的数据传输。

实验中可能遇到的问题及解决方法

1 通信错误

检查硬件连接和程序逻辑,确保信号线连接正确,程序没有错误。

2 时序问题

调整时钟频率和时钟相位,保证主设备和从设备之间的时序匹配。

总结和实验心得

通过本次实验,我深入了解了SPI总线的工作原理和通信过程,并掌握了如何 使用SPI总线进行数据传输的方法。这对我今后的嵌入式系统开发有很大帮助。

SPI总线通信原理

SPI总线通过四条信号线进行通信,包括时钟信号、主设备输出(MOSI)信号、主设备输入(MISO) 信号以及片选信号(SS)。数据在通信时通过时钟信号同步传输。

SPI总线接口电路

SPI总线接口通常由一个主设备和一个或多个从设备组成。主设备控制通信时 序,并发送和接收数据。从设备响应主设备的操作,并进行数据传输。

SPI总线数据传输操作

数据传输过程包括主设备生成时制。

SPI总线实验过程

1

2. 程序编写

2

编写单片机程序以控制SPI总线的数

据传输。

3

1. 实验准备

连接电路,准备实验所需的器件和材 料。

3. 实验测试

进行SPI总线的数据传输测试,观察 结果和信号波形。

ISA总线

ISA总线插槽信号说明3

• BALE(O) 缓冲地址锁存使能信号,此信号在高电平 时动作,用来锁存地址信号用,它可供I/O通 道作为一个有效的微处理器或DMA地址指示器。 在PC AT机中此信号经过缓冲器以增加驱动能 力,当BALE在下降沿时,微处理器的地址线 (SA19~SA0)被锁存于地址锁存器的输出端。 在DMA周期,BALE是在高电平状态,此时该信 号若与AEN信号共用时,可以指定I/O通道上的 口地址。

ISA总线插槽信号说明2

• LA23~LA17(I/O) 未锁定地址信号线,它们配合SA19~ SA0用来寻址16M存储器空间。当这些信 号经BALE信号锁定时才有效,所以并非 整个扩充槽周期都可以使用,当这些信 号由80X86和8237产生时为输出状态,当 这些信号由接口卡上的微处理机产生时 为输入状态。

VIDEO EPROM对应存储区 (EGA或VGA)

支援I/O控制卡上的 EPROM对应存储区 外加控制扩充存储区 外加扩充存储区 64KEPROM I/O SLOT EXPANTION CARD MEMORY 128K EPROM

保 护 模 式

100000H FDFFFFH FE0000H FFFFFFH

主机接口

利用主机接口,可以实现以下功能: 1. 可以控制处理器和处理器的外部总线,访问任何处理 器资源; 2. 可以读写处理器的 IOP 寄存器,以及 EPBx FIFO 缓冲区, 完成对处理器操作模式的配置,以及建立DMA传输等; 3.利用外部口DMA通道,可以实现主机与处理器之间的程 序与数据传输; 4.可以将主机的8位、16位或32位主机数据打包成32位或 48位内部数据; 5. 使用处理器内部消息和向量中断能确保主机命令的有 效执行; 6.能控制与监控处理器的操作; 7.在多处理器系统中,主机对主从处理器都可以访问。

计算机接口技术实验

第1章 性 能 特 点1.1 系统组成HK8086TE 微机教学实验系统是武汉恒科电子教学仪器有限公司在继承8086TE 和 8086T1微机教学实验机优点的基础上,广泛地吸取用户的使用意见和建议,结合8086/88仿真技术,推出的新一代微机教学实验系统。

本实验系统由HK8086TE 实验机外配计算机和其他一些附件及选配件组成(图1.1所示)。

该实验系统,既可以在无PC 机的状态下独立运行,又可以接PC 机通过串口用上位机软件进行调试。

在扩展功能上,可以通过实验机的25芯插座外接机电实验平台,做机电一体化实验。

1.2 HK8086TE 实验机性能特点1.2.1 性能特点HK8086TE 教学实验系统集微处理器8086和外配PC /80286/386/486/586及其兼容机于一体的高科技实验系统,具有实验、开发、自诊断等功能,是目前实验机市场上较先进的一种学习微机外围接口技术和微处理器原理的教学实验系统。

该实验系统自带键盘、八位七段数码管、微处理器8088和RS-232通讯接口,可以接PC 机做实验,也可以无须任何辅助设备而独立做实验。

实验机上提供32KB RAM 的程序和数据空间,具有无条件暂停(夭折处理)等功能。

综合下来,它具有如下性能特点:1、两种配置工作方式:(1)独立运行的单板机配置方式。

在HK8086TE 教学实验机上,提供8088微处理器和键盘监控程序,可以在脱离PC 机的情况下,利用实验板上的键盘和七段数码管,独立运行8088微处理器接口实验。

(2)串行监控配置方式。

利用计算机的串行监控通讯口,通过RS-232通讯电缆,与实验机连接。

此时不用在总线槽中插入缓冲驱动卡。

而是利用实验机上的微处理器8088进行微处理器原理实验和微处理器接口技术实验。

提供可视化窗口调试软件.● 具有夭折处理功能。

在串行监控方式或单板机方式下,执行用户程序后,按暂停键,能保存用户现场返回监控,帮助查找程序跑飞、死循环等原因。

微机原理与接口技术实验指导书(硬件部分)

微机原理与接口技术实验指导书(硬件部分)北京邮电大学自动化学院检测技术及自动化教研中心2007年9月目录硬件实验部分TPC-2003A通用32位微机接口实验台介绍 (2)实验时应注意的问题 (8)实验一 I/O地址译码 (9)实验二 简单并行接口 (11)实验三 可编程定时器/计数器(8253) (13)实验四 可编程并行接口(一)(8255方式0) (16)实验五 交通灯控制实验 (17)实验六 七段数码管 (19)实验七 继电器控制 (24)实验八 数/模转换器 (27)实验九 模/数转换器 (30)TPC-2003A通用32位微机接口实验台硬件:PCI接口卡一块;实验台一个;50线扁平电缆一根;自锁紧导线50根。

实验箱上有微机原理硬件实验最常用接口电路芯片,包括:可编程定时器/计数器( 8253 ) 、可编程并行接口( 8255 ) 、数/ 模转换器( DAC0832 ) 、模/ 数转换器(ADC0809)。

另外,还另附加集成电路芯片(8251、74LS273、74LS244、6116)共4片。

实验台上除了上述接口实验常用的集成电路外、还设有I/O地址译码电路、总线插孔、外围电路及通用IC插座等部分组成。

外围电路包括逻辑电平开关电路、LED显示电路、时钟电路、单脉冲电路、逻辑笔、复位电路、七段数码管显示电路、基本门电路、继电器及步进电机、小直流电机的驱动电路等。

接口卡可以插入PC系列微机中任意一个PCI扩展插槽,它的主要功能是将与实验有关的总线信号加以驱动后引到实验台上。

PLX9054PCI总线扩展卡结构,该卡使用PLX9054和CPLD把PCI总线时序转换成50芯ISA 总线时序,提供给微机实验台使用。

PC/AT ( ISA工业标准总线) PC/XT 总线图1 TPC-2003A通用32位微机接口实验台实验台提供的电路1、I/O地址译码电路如图所示,地址空间:280H~2BFH共分8条译码输出线:Y0~Y7,其地址分别是280H~287H;288H~28FH;290H~297H;298H~29FH;2A0H~2A7H;2A8H~2AFH;2B0H~2B7H;2B8H~2BFH,8根译码输出线在实验台“I/O地址”处分别由“自锁紧”插孔引出,供实验选用。

ISA总线

ISA总线ISA总线是采用80286 CPU的 IBM PC/AT机中使用的总线,它是在8位的PC/XT总线的基础上扩展而成的16位总线结构。

该总线同8位的 PC/XT总线保持了即兼容性。

80286与8088 CPU最明显的差别在于数据信号的位数,8088对外的数据总线只有8位,而80286为16位。

为了使ISA总线与原有的XT总线相兼容,ISA 总线保留了原有XT总线的所有信号,仅作了部分新的定义,而另外增加了高位的数据信号和与此有关的扩展信号,诸如SBHE、-MEMCS16、-IOCS16等信号。

除了数据传输线增加外,寻址能力的增加也是提高性能的方式。

80286的寻址能力达到了16MB,这样相应的 ISA总线上的地址信号也增加到了24条,即增加了4条(LA20~LA23)。

随着 PC系统的发展,外围设备的类型也不断增加,对于硬件中断与 DMA 通道也提出了更多的要求,原有的6个中断请求与3个 DMA通道已不能满足需要, ISA总线将中断的数目由6个扩充到15个,而 DMA通道则由3个增加到8个。

ISA总线扩展槽的插座是在原来 XT总线(62线)的基础上增加了一条短插座,该短插槽有36个引脚,并且与原 XT插槽在一条直线上,因此加上原来 XT 总线的62线,一共有98个引脚。

表3- 5列出了 ISA总线增加信号的排列。

表3- 5 ISA总线增加的36芯的信号定义在ISA总线上62芯和36芯插座上重新定义和增加的信号:(l)地址总线LA17~LA23(I/O):ISA总线中新增的地址信号线,可以给系统提供多达16MB 的寻址能力。

此信号在ALE信号为高电平时才有效,并且在 CPU周期过程中是不锁定的,因此并不保持整个周期有效,它们的用途是为一个等待状态存储周期生成存储器译码信号。

(2)数据总线SD8~SD15(I/O):系统数据总线的高字节信号,为存储器和I/O接口提供高8位总线数据。

为保持与XT总线的兼容性,可通过增加的16位存储器或16位I/O接口控制信号确定所用的数据线位数。

微机原理实验报告

微机原理实验报告西安电⼦科技⼤学实验报告班级:1303018学号:130********姓名:李胜东地点: EII-312批次:第批时间: 2015.11-2015.12实验⼀汇编语⾔编程实现1.实验⽬的(1)掌握汇编语⾔的编程⽅法(2)掌握DOS功能调⽤的使⽤⽅法(3)掌握汇编语⾔程序的调试运⾏过程2.实验内容(1)将指定数据区的字符串数据以ASCII码形式显⽰在屏幕上,并通过DOS功能调⽤完成必要提⽰信息的显⽰。

(2)在屏幕上显⽰⾃⼰的学号姓名信息。

(3)循环从键盘读⼊字符并回显在屏幕上,然后显⽰出对应字符的ASCII码,直到输⼊”Q”或“q”时结束。

实验中使⽤的DOS功能调⽤: INT 21H3.实验步骤及原理(1)运⾏QTHPCI软件,根据实验内容编写程序,参考程序流程如下图所⽰。

(2)使⽤“项⽬”菜单中的“编译”或“编译连接”命令对实验程序进⾏编译、连接。

(3)“调试”菜单中的“进⾏调试”命令进⼊Debug调试,观察调试过程中数据传输指令执⾏后各寄存器及数据区的内容。

按F9连续运⾏。

(4)更改数据区的数据,考察程序的正确性。

4.实验源代码DATA SEGMENTNUMBER DB 'SNO:130********',0AH,'NAME:lishengdong',0DH,0AH,'$';0DH (回车))0AH(换⾏)24H($)结束MSG1 DB 0AH,0DH,'If you want to leave,please input: q or Q ',0AH,0DH,'$'MSG2 DB 0AH,0DH,0AH,0DH,'Input: $'RESULT DB 0AH,0DH,'ASCII is: $'SD DB ' 'DATA ENDSCODE SEGMENTASSUME CS:CODE,DS:DATASTART:MOV SI,OFFSET DATAMOV CX,5A:MOV AL,DS:[SI]AND AL,0F0HCMP AL,0A0HJB A1ADD AL,07HA1:SHR AL,1SHR AL,1SHR AL,1SHR AL,1OR AL,30HMOV AH,02HMOV DL,ALINT 21HMOV AL,DS:[SI]AND AL,0FHCMP AL,0AHJB A2ADD AL,07HA2:OR AL,30HMOV AH,02HMOV DL,ALINT 21HINC SILOOP AMOV AX,DATAMOV DS,AXMOV DX,OFFSET NUMBERMOV AH,09HINT 21HMOV DX,OFFSET MSG1 MOV AH,09H INT 21HC1: MOV DX,OFFSET MSG2 MOV AH,09H INT 21HMOV AH,01HINT 21HCMP AL,'Q'JZ EXITCMP AL,'q'JZ EXITMOV SD,ALMOV DX,OFFSET RESULTMOV AH,09HINT 21HMOV SI,OFFSET SDMOV AL,DS:[SI]AND AL,0F0HMOV CL,4SHR AL,CLCMP AL,0AHJB C2ADD AL,07HC2: ADD AL,30HMOV DL,ALMOV AH,02HINT 21HMOV AL,DS:[SI]AND AL,0FHCMP AL,0AHJB C3ADD AL,07HC3: ADD AL,30HMOV DL,ALMOV AH,02HINT 21Hloop C1EXIT: MOV AX,4C00HINT 21HCODE ENDSEND START实验⼆数码转换实验1.实验⽬的(1)掌握不同进制数及编码相互转换的程序设计⽅法。

实验3(A-D接口实验)

实验3:A/D接口实验一、实验目的了解在linux环境下对S3C2410芯片的8通道10位A/D的操作与控制。

二、实验内容学习A/D接口原理,了解实现A/D系统对于系统的软件和硬件要求。

阅读ARM芯片文档,掌握ARM的A/D相关寄存器的功能,熟悉ARM系统硬件的A/D相关接口。

利用外部模拟信号编程实现ARM循环采集全部前4路通道,并且在超级终端上显示。

三、预备知识有C语言基础。

掌握在Linux下常用编辑器的使用。

掌握Makefile 的编写和使用。

掌握Linux下的程序编译与交叉编译过程。

四、实验设备及工具硬件:UP-NETARM2410-S嵌入式实验平台、PC机Pentium 500以上, 硬盘10G以上。

软件:PC机操作系统REDHAT LINUX 9.0+MINICOM+ARM-LINUX开发环境五、实验原理1、A/D转换器A/D转换器是模拟信号源和CPU之间联系的接口,它的任务是将连续变化的模拟信号转换为数字信号,以便计算机和数字系统进行处理、存储、控制和显示。

在工业控制和数据采集及许多其他领域中,A/D转换是不可缺少的。

A/D转换器有以下类型:逐位比较型、积分型、计数型、并行比较型、电压-频率型,主要应根据使用场合的具体要求,按照转换速度、精度、价格、功能以及接口条件等因素来决定选择何种类型。

常用的有以下两种:双积分型的A/D转换器双积分式也称二重积分式,其实质是测量和比较两个积分的时间,一个是对模拟输入电压积分的时间T0,此时间往往是固定的;另一个是以充电后的电压为初值,对参考电源Vref反向积分,积分电容被放电至零所需的时间T1。

模拟输入电压Vi与参考电压V Ref之比,等于上述两个时间之比。

由于V Ref、T0固定,而放电时间T1可以测出,因而可计算出模拟输入电压的大小(V Ref与Vi符号相反)。

由于T0、V Ref为已知的固定常数,因此反向积分时间T1与输入模拟电压Vi在T0时间内的平均值成正比。

计算机系统接口技术-ISA总线

总线信号

LA17-LA23:扩展地址从1M到 LA17-LA23:扩展地址从1M到16M SD08-SD15:16位数据的高8 SD08-SD15:16位数据的高8位 SBHE:总线高字节允许 SBHE:总线高字节允许 IRQ10-IRQ15:中断请求(13给协处理器) IRQ10-IRQ15:中断请求(13给协处理器) 13 DMA请求线:DRQ DMA请求线:DRQ DMA响应线:DACK DMA响应线:DACK MEMR/MEMW:存储器读写 MEMR/MEMW:存储器读写 MEM CS16/IO CS16:16位MEM/IO片选 CS16:16位MEM/IO片选 MASTER:总线控制有效 MASTER:总线控制有效

计算机接口技术(5 计算机接口技术(5总线 ISA总线

ISA总线(Industry Standard ISA总线(Industry Architecture)——工业标准体系结构总线, Architecture)——工业标准体系结构总线, 又称AT总线 又称AT总线 PC总线+36线扩展插槽 PC总线+36线扩展插槽 PC总线即XT总线。 PC总线即XT总线。

DACK1 DRQ1 DACK0 CLK IRQ7 IRQ6 IRQ5 IRQ4 IRQ3 DACK2 T/C ALE +5V OSC GND

PC总线 PC总线

A0-A19:地址线 A0-A19:地址线 D0-D7:数据线 D0-D7:数据线 AEN:地址允许 AEN:地址允许 ALE:地址锁存 ALE:地址锁存 IOR/W:IO读写 IOR/W:IO读写 MEMR/W:MEM读写 MEMR/W:MEM读写 T/C:DMA终止计数 T/C:DMA终止计数 IRQ3-IRQ9:中断请求 IRQ3-IRQ9:中断请求 DRQ1-DRQ3:DMA请求 DRQ1-DRQ3:DMA请求 DACK1-DACK3:DMA响应 DACK1-DACK3:DMA响应 RST:系统复位 RST:系统复位 I/O CHECK:通道检查 CHECK:通道检查 I/O READY:增加I/O时延 READY:增加I/O时延 OSC: OSC:8MHz CLK: CLK:12.31818MHz

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

实验内容

实验目的 实验方法 实验原理 实验步骤 结果与分析

实验目的

了解ISA总线的相关知识; 了解通过ISA接口扩展的实验设备; 掌握在Linux下访问ISA设备的方法; 掌握在Linux下编程访问指定设备寄存器的

方法; ……

实验方法

阅读实验原理中的相关介绍,了解ISA总线 的历史发展与技术特点

•

7、最具挑战性的挑战莫过于提升自我 。。20 20年9 月2020/ 9/1520 20/9/15 2020/9 /159/1 5/2020

•

8、业余生活要有意义,不要越轨。20 20/9/1 52020/ 9/15Sep tember 15, 2020

•

9、一个人即使已登上顶峰,也仍要自 强不息 。2020 /9/152 020/9/1 52020/ 9/1520 20/9/15

device_release函数

关闭设备时驱动需要完成的工作 这里仅仅将设备使用次数减1

驱动程序分析(续2)

device_read函数

将需要输出的信息拷贝到用户空间,也就是提交给 对设备进行读操作的程序

device_write函数

这里不支持写操作,因此仅仅打印出提示信息

cleanup_module函数

•

2、阅读一切好书如同和过去最杰出的 人谈话 。2020 /9/152 020/9/1 52020/ 9/159/ 15/2020 8:17:47 AM

•

3、越是没有本领的就越加自命不凡。 2020/9 /15202 0/9/152 020/9/ 15Sep-2 015-Se p-20

•

4、越是无能的人,越喜欢挑剔别人的 错儿。 2020/9 /15202 0/9/152 020/9/ 15Tues day, September 15, 2020

控制寄存器地址:283H 计数器0地址:280H 计数器1地址:281H

……

可使用IO命令访问设备(续)

ICH4中的实时钟RTC

RTC寄存器地址索引端口:70H RTC数据端口:71H

扩展实验板上的并口控制器(8255)+7段数码 管

8255控制寄存器端口:28BH 8255 A口地址:288H 8255 C口地址:28AH

ioperm

设置IO端口读写许可 需要有root权限 ioperm(from, num, turn_on)

可以使用IO命令访问的设备

ICH4中的定时器(8254)

0通道计数器:40H 1通道计数器:41H 2通道计数器:42H 计数器控制器:43H

扩展实验板上的定时器(8253)

函数依次对应了对设备读、写、打开、释放等操作 对应内核驱动需要进行的工作

设备通过主设备号与次设备号进行区分。在确 定系统中设备号可以在代码中指定,也可以由 系统自动分配

驱动程序分析

包括的头文件

<linux/fs.h>:定义了结构体 <asm/uaccess.h>:定义了其中用到的put_user函数

init_module函数

调用register_chrdev向系统注册字符设备,返回值即 系统分配的主设备号

分配的主设备号小于0,则表示注册设备错误

驱动程序分析(续1)

device_open函数

打开设备时驱动需要完成的工作

由于这里是虚拟设备,因此只是完成了部分内部变 量的初始化,以及设备使用次数加1

• 10、你要做多大的事情,就该承受多大的压力。

9/15/2020 8:17:47 AM2020/9/1520.9.15

• 11、自己要先看得起自己,别人才会看得起你。

•Leabharlann 5、知人者智,自知者明。胜人者有力 ,自胜 者强。 2020/9 /15202 0/9/152 020/9/ 152020 /9/159/ 15/202 0

•

6、意志坚强的人能把世界放在手中像 泥块一 样任意 揉捏。 2020年 9月15 日星期 二2020/ 9/1520 20/9/15 2020/9 /15

实验步骤

Linux下使用IO命令访问下列设备:

ICH4中的定时器(8254) ICH4中的实时钟(RTC) 扩展实验板上的定时器(8253) 扩展实验板上的7段数码管 ……

编写下列设备的字符设备驱动程序

ICH4中的RTC 扩展实验板上的7段数码管

•

1、有时候读书是一种巧妙地避开思考 的方法 。2020 /9/152 020/9/1 5Tuesday, September 15, 2020

调用unregister_chrdev从系统注销字符设备

Linux下直接访问IO地址

in,out,ins,outs

inb、inw、inl:从指定IO地址读1、2、4个字节 outb、outw、outl:向制定IO地址写入数据 inb_p、inw_p、……、outl_p:在执行完读写命

令后,执行一条空指令,暂停一下CPU

Linux下编程访问ICH4的计数器、RTC等功 能部分

Linux下编程访问扩展实验板上7段数码管、 8253定时器、8255并口等设备

学习字符设备驱动程序,编写实际的字符 设备驱动程序

实验原理

ISA总线

全称:Industry Standard Architecture总线 最初用于IBM PC,为8位总线 IBM PC/AT中扩展为16位 EISA协会开发的EISA总线为32位,向下兼容8

将底层设备抽象为设备文件 属于内核代码,运行在内核空间 可以使用Module模式,可以动态加载

字符设备驱动程序

定义了Module中必须定义的函数init_module和 cleanup_module

定义了结构体struct fops,里面定义了对应的 read、write、open、release等函数

位与16位ISA总线

PC104总线

用于工业控制计算机、嵌入式领域 具有功耗低、占用空间小、可扩展等特点

Linux设备驱动程序

Linux中IO设备分为:

字符设备:无需缓冲区直接读写,只能顺序访问 块设备 :以块为单位读写,可随即访问 网络设备:通过BSD套接口访问

Linux驱动程序