mux4_1四选一选择器的3种写法对比

数电 (15)

A2A1A0D3 mi Di

i 0

7

八选一MUX的功能表 使能 输入 EN 1 0 0 0 0 输 入 输出 使能 输入 EN 0 0 0 0 输 入 A2 1 1 1 1 A1 0 0 1 1 A0 0 1 0 1 输出 Y D4 D5 D6 D7

A2 Ø 0 0 0 0

A1 Ø 0 0 1 1

D3~D0 :数据输入端;

四选一

Y

EN:使能端; Y:输出端;

简化逻辑符号

A0 A1 D0

四选一

Y

四选一MUX的逻辑表达式

D1 D 2 M UX D3 EN

EN = 1, Y = 0 ;

EN = 0, Y = A1A0D0+ A1A0D1+ A1A0D2 + A1A0D3

mi Di

i 0

F Y 比较两卡诺图,若A、B、C分别接A2、A1、A0, 再令D0 =D1= D2 = D3 = D5 ,D4 =D6 =D7 =1,则

Y=F,相应的电路图如下所示:

C B A

V CC

EN A0 A1 A2 D0 D1 7 41 51 Y D2 D3 D4 D5 D6 D7

F

A对应最高位权

注意:用数据选择器实现逻辑函数时,输入变量 的高低位与地址端高低位的对应关系

0 1 0 0 1 0 1 1

0 0 1 0 1 1 0 1

1 0 0 1 0 0 0 0

0 1 0 1 0 0 0 0

0 0 1 0 1 1 0 1

2. 数据比较器的扩展 (1) 串联方式

A0 A1 A2 A3 0 1 0 B 0 B1 B2 B3 A0 A1 A2

A 3

7 48 5 F A>B

四选一多路选择器

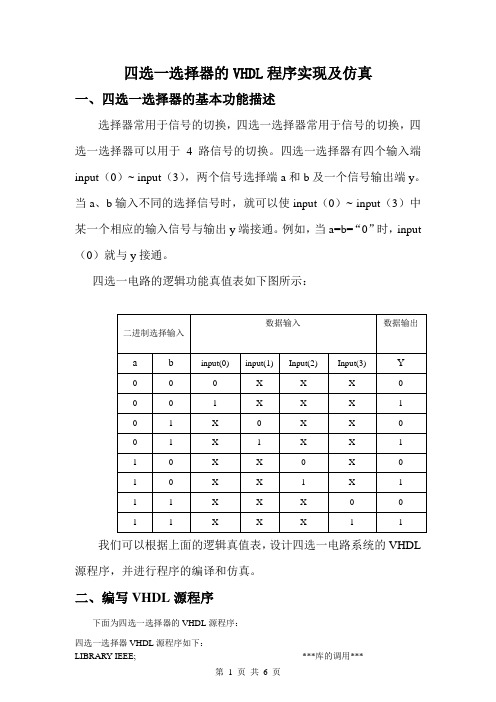

四选一选择器的VHDL程序实现及仿真一、四选一选择器的基本功能描述选择器常用于信号的切换,四选一选择器常用于信号的切换,四选一选择器可以用于4路信号的切换。

四选一选择器有四个输入端input(0)~ input(3),两个信号选择端a和b及一个信号输出端y。

当a、b输入不同的选择信号时,就可以使input(0)~ input(3)中某一个相应的输入信号与输出y端接通。

例如,当a=b=“0”时,input (0)就与y接通。

四选一电路的逻辑功能真值表如下图所示:我们可以根据上面的逻辑真值表,设计四选一电路系统的VHDL 源程序,并进行程序的编译和仿真。

二、编写VHDL源程序下面为四选一选择器的VHDL源程序:四选一选择器VHDL源程序如下:LIBRARY IEEE; ***库的调用***USE IEEE.STD_LOGIC_1164.ALL; ***库的调用***ENTITY mux4 IS ***实体定义*** PORT (input:IN STD_LOGIC_VECTOR(3 DOWNTO 0); ***输入管脚的定义***a,b:IN STD_LOGIC; ***输入管脚的定义***y:OUT STD_LOGIC ); ***输出管脚的定义***END mux4;ARCHITECTURE rtl OF mux4 IS ***结构的定义***SIGNAL sel:STD_LOGIC_VECTOR (1 DOWNTO 0); ***信号定义***BEGINsel<=b&a;PROCESS (input,sel) ***进程的定义***BEGINIF(sel="00") THENy<=input(0);ELSIF(sel<="01") THENy<=input(1);ELSIF(sel<="10") THENy<=input(2);ELSEy<=input(3);END IF;END PROCESS;END rtl;三、文本文件的编译及仿真全过程在编辑器中输入并保存了以上四选一选择器的VHDL源程序后就可以对它进行编译了,编译的最终目的是为了生成可以进行仿真、定时分析及下载到可编程器件的相关文件,如*.cnf,*.rpt,*.snf,*.pof 等。

四选一数据选择器

根据给定的输入地址代码,数据选择器从一组输入信号中选择一个指定的,并将其发送到输出端的组合逻辑电路。

有时也称为多路复用器或多路复用器。

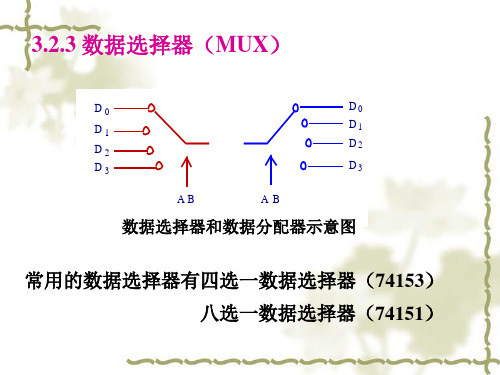

该图显示了四分之四数据选择器的示意图。

在图中,D0,D1,D2和D3是四个数据输入端子,Y是输出端子,而A1和A0是地址输入端子。

从表中可以看出,可以使用指定A1A0的代码选择四个输入数据D0,D1,D2和D3中的任何一个并将其发送到输出。

因此,数据选择器可以实现数据的多通道分时传输。

另外,数据选择器被广泛用于生成任何种类的组合逻辑功能。

在图中所示的电路中,如果将y视为A0,A1和D0,D1,D2和D3的函数,则可以写为。

如果将A1和A0视为两个输入逻辑变量,并且将D0,D1,D2和D3视为第三输入逻辑变量A2的不同状态(即A2,/ A2、1或0),则任何所需的组合逻辑函数可以生成三个变量A2,A1和A0。

可以看出,具有N位地址输入的数据选择器可以生成输入变量数量不大于n +1的任何组合逻辑函数。

实验步骤

1.打开莱迪思钻石并设置项目。

2.创建一个新的Verilog HDL设计文件,然后输入设计代码。

3.合成并分配引脚,将输入信号a和b分配给DIP开关,并将输出信号led0〜led3分配给板上的LED。

sel [0] / N14,sel [1] / M14,a / M7,b / M8,,c / M9,d / M10,led / N13

4.构建并输出编程文件,并将其刻录到FPGA的Flash中。

5.按下相应的键/拨动DIP开关并观察输出结果。

4选1多路选择器VHDL语言设计

4选1多路选择器VHDL语言设计在VHDL语言中设计一个4选1多路选择器主要涉及到以下几个方面:实体声明、端口声明、内部信号声明、内部结构设计、行为建模以及仿真测试。

下面是一个VHDL语言设计的参考模板,详细解释了每个步骤的实现方法。

1. 实体声明(Entity Declaration)```vhdlentity mux_4to1 isportA, B, C, D : in std_logic;S : in std_logic_vector(1 downto 0);CLK : in std_logic;Y : out std_logicend mux_4to1;```2. 端口声明(Port Declaration)端口声明定义了输入和输出端口的类型。

在这个例子中,输入和输出端口的类型都是标准逻辑类型。

```vhdlarchitecture behavioral of mux_4to1 issignal input_mux : std_logic_vector(3 downto 0);beginA <= input_mux(0);B <= input_mux(1);C <= input_mux(2);D <= input_mux(3);end behavioral;```3. 内部信号声明(Internal Signal Declaration)内部信号声明是为了辅助模块内的信号传输和处理。

在这个例子中,我们需要声明一个内部信号来保存选择信号S对应的多路选择器输入信号。

```vhdlarchitecture behavioral of mux_4to1 issignal input_mux : std_logic_vector(3 downto 0);signal mux_out : std_logic;beginA <= input_mux(0);B <= input_mux(1);C <= input_mux(2);D <= input_mux(3);end behavioral;```4. 内部结构设计(Internal Structure Design)内部结构设计定义了多路选择器的逻辑结构。

verilog4选一数据选择器原理

verilog4选一数据选择器原理Verilog中的4选1数据选择器(MUX)是一种多路选择器,可以从4个输入信号中选择一个输出信号。

这种数据选择器的原理在于根据控制信号的不同将其中一些输入信号传递到输出端。

以下是对Verilog中的4选1数据选择器的原理的详细解释。

首先,一个4选1数据选择器包括4个输入信号(A,B,C,D),一个控制信号(S),以及一个输出信号(Y)。

控制信号(S)决定了哪个输入信号将被传递到输出端。

这里采用二进制的表示方法,控制信号(S)的取值范围为0到3、具体来说,当S=00时,输入信号A将被传递到输出端,当S=01时,输入信号B将被传递到输出端,当S=10时,输入信号C将被传递到输出端,当S=11时,输入信号D将被传递到输出端。

实现4选1数据选择器需要用到逻辑门电路。

常用的逻辑门有与门(AND),或门(OR),非门(NOT)等。

首先,将控制信号(S)的两个比特分别作为两个输入端口A和B的输入信号。

这两个输入端口将分别与输入信号的每一位进行与运算,得到4个输出信号。

那么接下来,控制信号(S)的两个比特将作为输入信号的每一位的控制信号。

假设输入信号为(A0,A1)。

当控制信号(S)为(0,0)时,即A0=0,A1=0,与运算得到的输出信号为(0,0,0,0),此时输出端Y将传递输入信号A。

当控制信号(S)为(0,1)时,即A0=0,A1=1,与运算得到的输出信号为(0,1,0,0),此时输出端Y将传递输入信号B。

当控制信号(S)为(1,0)时,即A0=1,A1=0,与运算得到的输出信号为(0,0,1,0),此时输出端Y将传递输入信号C。

当控制信号(S)为(1,1)时,即A0=1,A1=1,与运算得到的输出信号为(0,0,0,1),此时输出端Y将传递输入信号D。

最后,将4个输出信号通过或门进行运算,得到输出信号Y。

具体地,将4个输出信号的每一位进行或运算,得到的结果就是输出信号Y的每一位。

实验二 四选一多路选择器的设计

实验二四选一多路选择器的设计姓名:庞啟明学号:1112120110 专业:自动化一、实验目的进一步熟悉QuartusⅡ的Verilog HDL文本设计流程,学习组合电路的设计、仿真和硬件测试。

二、实验原理if_else条件语句描述方式,以过程语句引导的顺序语句,适合描述复杂逻辑系统的行为描述语句。

(1)以模块定义语句关键词module_endmodule引导完整的电路模块。

(2)以input和output语句引导模块的外部端口。

(3)以reg等关键词定义模块内将出现的相关信息的特征和数据类型。

(4)以always @ 等关键词引导对模块逻辑功能描述的语句。

负责描述电路器件的内部逻辑功能和电路结构。

三、实验设备与软件平台实验设备:计算机、FPGA硬件平台是Cyclone系列FPGA软件平台:Quartus II 9.1 (32-Bit)、5E+系统四、实验内容编写Verilog程序描述一个电路,实现以下功能:具有6个输入端口 A、B、C、D、S1、SO,A、B、C、D均为输入端口,位宽为1;Sl、S0为通道选择控制信号端,位宽为1;Y为输出端口,位宽为1。

当S1S0为“00”时,A的数据从Y输出,S1S0为“01”时,B的数据从Y输出,S1S0为“10”时,C的数据从Y输出,S1S0为“11”时,D的数据从Y输出。

五、实验步骤设计流程:1、编辑和输入设计文件(1)、新建一个文件夹如D:\MUX41 ,本工程所有文件将存放在此目录中。

1)输入VHDL源程序打开QuartusII,选择菜单File->New。

选择Verilog HDL File,输入源程序。

2)文件存盘选择File->Save As命令,找到已设立的文件夹D:\MUX41,存盘文件名应与实体名一致,存盘为MUX41.v。

当出现语句“do you want to create…..”的对话框,选择“是”自动创建工程。

这里先选择“否”,即暂时不创建工程流程。

verilog4选一数据选择器原理(一)

verilog4选一数据选择器原理(一)Verilog中的4选1数据选择器简介在数字电路中,数据选择器是一种常见的电路组件,用于从多个数据输入中选择一个输出。

Verilog是一种硬件描述语言,广泛用于数字电路的设计和仿真。

本文将介绍Verilog中的4选1数据选择器的原理和实现方法。

原理4选1数据选择器有4个输入和1个输出。

根据选择信号,从4个输入中选择一个输入作为输出。

选择信号是2位的二进制数,共有4种可能的状态,每种状态对应一个输入。

当选择信号为00时,输出为第一个输入;当选择信号为01时,输出为第二个输入;当选择信号为10时,输出为第三个输入;当选择信号为11时,输出为第四个输入。

逻辑电路图以下是4选1数据选择器的逻辑电路图:______S0 ----| || |S1 ----| |----- Y|______|Verilog实现下面是实现4选1数据选择器的Verilog代码示例:module mux4to1 (input [3:0] D, input [1:0] S, outpu t Y);assign Y = (S[1] & S[0] & D[3]) | (S[1] & ~S[0] & D [2])| (~S[1] & S[0] & D[1]) | (~S[1] & ~S[0] & D[0]);endmodule在上面的代码中,D是4个输入的信号线,S是选择信号线,Y是输出信号线。

根据选择信号的不同状态,使用逻辑运算符进行输入的选取,然后将结果输出到输出信号线Y上。

仿真测试为了验证4选1数据选择器的正确性,可以进行仿真测试。

以下是一个简单的测试示例:module test_mux4to1;// Declare signalsreg [3:0] D;reg [1:0] S;wire Y;// Instantiate the modulemux4to1 mux (D, S, Y);// Stimulusinitial begin// Test case 1D = 4'b0001; S = 2'b00; // Expect Y to be 0 #10;// Test case 2D = 4'b0001; S = 2'b01; // Expect Y to be 0 #10;// Test case 3D = 4'b0001; S = 2'b10; // Expect Y to be 0 #10;// Test case 4D = 4'b0001; S = 2'b11; // Expect Y to be 1 #10;$finish;endendmodule上述代码中,D和S是输入信号,Y是输出信号。

数据选择器(MUX)

数据选择器(MUX)4.4.3 数据选择器(MUX)数据选择器原理集成数据选择器数据选择器扩展数据选择器应用(MUX-Multiplexer)11. 数据选择器原理数据选择器功能: 将多路输入数据中由n位通道选择信号确定的其中一路数据传送到输出端。

又称为“多路选择器”或“多路(数字)开关”。

数据输入D0 D1 DN-1n位通道选择信号(N=2n)同相或 Y 反相输出数据选择器功能示意图2…数据选择器原理例: 一种4-1MUX的功能表逻辑符号: S1 S0 0 0 1 1 0 1 0 1 F D0 D1 D2 D3S1 S0 F 4-1MUX D0 D1 D2 D3输出表达式: F = S 1 S 0 D 0 + S 1 S 0 D1 + S 1 S 0 D 2 + S 1 S 0 D 3= m0 D0 + m1 D1 + m2 D2 + m3 D3= ∑ mi Dii =03(其中mi是由通道选择信号S1,S0构成的最小项)3MUX的输出信号一般表达式2n -1 MUX的输出信号一般表达式:F = m 0 D 0 + m1 D1 + ? ? ? + m 2 n ? 1 D 2 n ? 1 =2 n ?1 i=0∑m Dii(其中mi 是n 位通道选择信号构成的最小项)42. 集成数据选择器例:8-1 MUX 74151S2X功能表使能 E 1 0 0 0 0 0 0 0 0 输出 Y 0 D0 D1 D2 D3 D4 D5 D6 D7 Y 1 D0 D1 D2 D3 D4 D5 D6 D7通道选择 S1 S0X X输出表达式为:Y = E (∑ mi Di )i =07(mi 是S2,S1,S0构成的最小项)0 0 0 0 1 1 1 10 0 1 1 0 0 1 10 1 0 1 0 1 0 1574151逻辑符号与引脚排列D0 D1 D2 D3 D4 D5 D6 D7 E S2 S1 S0Y8YD3 D2 D1 D0 Y Y G GND11674HC151Vcc D4 D5 D6 D7 S0 S1 S274LS151 74HC1516具有三态输出的集成数据选择器例:8-1 MUX 74251 功能表S2X通道选择 S1 S0X X0 0 0 0 1 1 1 10 0 1 1 0 0 1 10 1 0 1 0 1 0 1使能 E 1 0 0 0 0 0 0 0 0输出 Y Z D0 D1 D2 D3 D4 D5 D6 D7 Y Z D0 D1 D2 D3 D4 D5 D6 D7(Z:高阻态)73. 数据选择器扩展例:用2片74151扩展成16-1MUXY ≥1 Y &- 通道扩展YY 74151(2)YG A 2 A1 S00 E S2 S 1 AD7 D6 D 5 D4 D 3 D2 D1 D0 1E A2 A 0 G S2 S11SA 0D7 D 6 D5 D4 D3 D2 D 1 D0D15 D14 D13 D12 D11 D10 D 9D8S A A A A33 S2 2 S11 S00D7 D6 D 5 D4 D3 D2 D1 D08数据选择器扩展 - 位扩展例:两位数的8-1 数据选择电路 S2 S1 S0 0 0 0 0 0 1 0 1 0 0 1 1 1 0 0 1 0 1 1 1 0 1 1 1 Y1 Y0 I10 I00 I11 I01 I12 I02 I13 I03 I14 I04 I15 I05 I16 I06 I17 I07 I17 I10 I11D0 D1I00 I01D0 D18-1 MUXY0I07D7 S ~S E 2 08-1 MUXY1D7 S ~S E 2 03S2~ S0 E94. 数据选择器应用-多通道数据传输例:I 0 8-1 I 1 MUX I2 I3 Y I4 I5 I6 I 7 S2 S1 S0S2 S1 S0公共数据线Y0 Y1 Y2 Y3 D Y4 Y5 Y6 A2 A1A0 Y71-8 DEMUXA2 A1 A0利用数据选择器与数据分配器实现多路数据的分时传输10数据选择器应用-实现逻辑函数任何逻辑函数都可表示成最小项之和形式:F =∑ m (此 m 是由F的输入变量构成的最小项)i iiMUX的输出表达式: Y =∑2 n ?1i =0mi Di(此mi是由通道选择信号构成的最小项)一般,当用具有n个通道选择端的MUX实现n变量的逻辑函数时,只需将逻辑函数的输入变量与MUX的通道选择端一一对应,并令逻辑函数中mi所对应MUX输出表达式中的Di=1,其余项对应的Di=0,即可实现。

四选一多路选择器三种方法

四选一多路选择器三种方法四选一多路选择器三种方法module MUX41a(a,b,c,d,s1,s0,y); input a,b,c,d; input s1,s0;output y;reg y;always@(a or b or c or d or s1or s0); begin:MUX41 case({s1,s0})2'b00:y<=a;2'b01:y<=b;2'b10:y<=c;2'b11:y<=d;default:y<=a;endcaseendendmodule计数器module CTR(CLK,Q,R);input CLK,R;output[3:0]Q;reg[3:0]Q;always@(posedge CLK or negedge R)if(!R)Q<=0;else Q<=Q+4'b0001;endmoduleD触发器module DFF(CLK,D,Q,RST0,RST1);input CLK,D,RST0,RST1;output Q;reg Q;always@(posedge CLK or negedge RST1) begin if(!RST1)Q<=0;else if(RST0==1)Q<=0;else if(RST0==0)Q<=D;endendmoduleSR锁存器module SR(S,R,CLK,RD,Q);input S,R,RD,CLK;output Q;reg Q;wire[3:0]H;assign H={CLK,RD,S,R};always@(*)begincase(H)H<=4'b1000:Q<=Q; H<=4'b0:Q<=0; H<=4'b?1??:Q<=0; H<=4'b1010:Q<=1;H<=4'b1001:Q<=0; default:Q<=0; endcaseendendmodule二进制转换成格雷码module btog(b,g); input[3:0]b;output[3:0]g; assign g[3]=b[3]; assign g[2]=b[3]^b[2]; assign g[1]=b[2]^b[1]; assign g[0]=b[1]^b[0]; endmodule格雷码转换二进制module gtob(b,g); input[3:0]g;output[3:0]b;assign b[3]=g[3];assign b[2]=g[3]^g[2];assign b[1]=g[2]^g[1];assign b[0]=g[1]^g[0];endmodule乘法器module mul2(H,F,R);input[1:0]H,F;output[3:0]R;assign R[0]=H[0]&F[0];assign R[1]=(H[1]&F[0])^(H[0]&F[1]);assign R[2]=(H[1]&F[0]&H[0]&F[1])^(H[1]&F[1]); assign R[3]=H[1]&F[0]&H[0]&F[1]&H[1]&F[1]; //*assign R={R[3],R[2],R[1],R[0]};/*//*assign H={H[1],H[0]};/*//*assign F={F[1],F[0]};/*Endmodule七段数码管显示module SMG(A,B);input[3:0]A;output[6:0]B;reg[6:0]B;always@(A)case(A)4'b0000:B<=7'b0111111;4'b0001:B<=7'b0000110;4'b0010:B<=7'b1011011;4'b0011:B<=7'b1001111;4'b0100:B<=7'b1100110;4'b0101:B<=7'b1101101;4'b0110:B<=7'b1111101;4'b0111:B<=7'b0000111;4'b1000:B<=7'b1111111;4'b1001:B<=7'b1101111;4'b1010:B<=7'b1110111;4'b1011:B<=7'b1111100;4'b1100:B<=7'b0111001;4'b1101:B<=7'b1011110;4'b1110:B<=7'b1111001;4'b1111:B<=7'b1110001;default:B<=7'b0111111;endcaseendmodule同步复位:顾名思义,同步复位就是指复位信号只有在时钟上升沿到来时,才能有效优点:a、有利于仿真器的仿真。

CMOS四选一多路选择器的线路设计与版图设计

vf D Gnd PULSE (0 5 15n 2n 2n 25n 50n).tran 1n 400n.print tran v(ctrl1) v(ctrl2) v(A) v(B) v(C) v(D) v(F)* Main circuit: Module0M1 C N1 N5 Gnd NMOS L=2u W=22u AD=66p PD=24u AS=66p PS=24uM2 N1 ctrl1 Gnd Gnd NMOS L=2u W=22u AD=66p PD=24u AS=66p PS=24u M3 N18 ctrl2 Gnd Gnd NMOS L=2u W=22u AD=66p PD=24u AS=66p PS=24u M4 A ctrl1 N5 Gnd NMOS L=2u W=22u AD=66p PD=24u AS=66p PS=24uM5 B ctrl1 N2 Gnd NMOS L=2u W=22u AD=66p PD=24u AS=66p PS=24uM6 D N1 N2 Gnd NMOS L=2u W=22u AD=66p PD=24u AS=66p PS=24uM7 N5 ctrl2 F Gnd NMOS L=2u W=22u AD=66p PD=24u AS=66p PS=24uM8 N2 N18 F Gnd NMOS L=2u W=22u AD=66p PD=24u AS=66p PS=24uM9 C ctrl1 N5 Vdd PMOS L=2u W=22u AD=66p PD=24u AS=66p PS=24uM10 A N1 N5 Vdd PMOS L=2u W=22u AD=66p PD=24u AS=66p PS=24uM11 N1 ctrl1 Vdd Vdd PMOS L=2u W=22u AD=66p PD=24u AS=66p PS=24u M12 N18 ctrl2 Vdd Vdd PMOS L=2u W=22u AD=66p PD=24u AS=66p PS=24u M13 B N1 N2 Vdd PMOS L=2u W=22u AD=66p PD=24u AS=66p PS=24uM14 D ctrl1 N2 Vdd PMOS L=2u W=22u AD=66p PD=24u AS=66p PS=24uM15 N5 N18 F Vdd PMOS L=2u W=22u AD=66p PD=24u AS=66p PS=24uM16 N2 ctrl2 F Vdd PMOS L=2u W=22u AD=66p PD=24u AS=66p PS=24u* End of main circuit: Module0电路图瞬时分析波形图:版图设计:内容(方法、步骤、要求或考核标准及所需工具、设备等)一、实训设备与工具1.PVI计算机一台;2.Tanner Pro集成电路设计软件二、项目总体要求采用全CMOS线路结构,实现如下电路功能:对应选择信号的四种组合,将输入数据信号一一传送到输出端。

四选一数据选择器的设计

XX大学实习(实训)报告实习(实训)名称:电工电子实习学院:专业、班级:指导教师:报告人:学号:时间: 2011年7月1日至 2011年7月8日实习主要内容:(1)了解EDA技术的发展及应用(2)掌握VHDL语言的基础知识,熟悉在数字电路系统设计中VHDL程序设计(3)学习MAX+PLUSⅡ软件的应用方法(4)应用EDA技术的设计方法完成4选1数据选择器的设计(采用原理图和文本法两种方法实现),并在MAX+PLUSⅡ上仿真主要收获体会与存在的问题:通过课程设计,发现自己的很多不足,自己知识的很多漏洞,看到了自己的实践经验还是比较缺乏,理论联系实际的能力还急需提高。

同时也体会到设计课的重要性和目的性所在。

同时这次实习也有很多收获,首先我们学会了MAX+PLUSⅡ软件的应用方法,并且能够独立设计出原理图,其次本次设计课培养了我们实际操作能力,也培养了我们灵活运用课本知识,理论联系实际,独立自主的进行设计的能力。

指导教师意见:建议成绩:指导教师签字:年月日备注:实习报告1.目的(1)通过实习掌握maxplus2软件的使用和VHDL语言的基础知识(2)应用maxplus2完成四选一数据选择器的设计,并实现仿真。

2.内容2.1 maxplus2的认识(1)Max+plusⅡ是Altera公司提供的FPGA/CPLD开发集成环境,Altera 是世界上最大可编程逻辑器件的供应商之一。

Max+plusⅡ界面友好,使用便捷,被誉为业界最易用易学的EDA软件。

在Max+plusⅡ上可以完成设计输入、元件适配、时序仿真和功能仿真、编程下载整个流程,它提供了一种与结构无关的设计环境,是设计者能方便地进行设计输入、快速处理和器件编程。

(2)、Max+plusⅡ开发系统的特点很多,比如开放性的界面,编辑过程与结构无关,丰富的设计库,硬件描述语等。

(3)、Max+plusⅡ软件具有开放核的特点,允许设计人员添加自己认为有价值的宏函数。

4选1选择器

第4章 VHDL应用实例

2019年1月17日3时6分

简述WITH_SELECT_WHEN选择信号赋值 语句和CASE_WHEN 顺序语句的异同。 • 答:WITH_SELECT_WHEN选择信号赋值 语句中是逗号,最后是分号;是并行语句, 必须放在结构体中。 • CASE_WHEN

• 顺序语句中是分号;是顺序语句,必须放 在进程中。

ELSIF (SEL="11")THEN Y<=INP(2);

ELSE Y<=INP(3); END IF;

END PROCESS;

END ART;

2

第4章 VHDL应用实例

2019年1月17日3时6分

【例2.28】用条件信号赋值语句描述的四选一数据选择器 LIBRARY IEEE; USE IEEE.STD_LOGIC_1164.ALL; ENTITY mux44 IS PORT(i0,i 1,i2,i3,a,b:IN STD_LOGIC; q:OUT STD_LOGIC); END mux44; ARCHITECTURE aa OF mux44 IS SIGNAL sel: STD_LOGIC_VECTOR(1 DOWNTO 0); BEGIN sel<=b & a; q<= i0 WHEN sel="00" ELSE i1 WHEN sel="01" ELSE i2 WHEN sel="10" ELSE i3 WHEN sel="11" ; END aa

SIGNAL SEL :STD_LOGIC_VECTOR(1 DOWNTO 0);

1

第4章 VHDL应用实例

BEGIN SEL<=B&A; PROCESS(INP,SEC)

EDA论文4选1多路选择器的设计

4选1多路选择器的设计班级xxxxx 姓名xxxxx 学号xxxxxx一、内容摘要多路选择器是数据选择器的别称。

在多路数据传送过程中,能够根据需要将其中任意一路选出来的电路,叫做数据选择器,也称多路选择器或多路开并。

数据选择器的电路结构一般由于活门阵列而成,也有用传输门开关和门电路混合而成的。

多路选择器可以从多组数据来源中选取一组送入目的地。

它有4选1数据选择器、8选1数据选择器(型号为74151、74LS151、74251、74LS151)、16选1数据选择器(可以用两片74151连接起来构成)等之分。

多路选择器还包括总线的多路选择,模拟信号的多路选择等,相应的器件也有不同的特性和使用方法它的应用范围相当广泛,从组合逻辑的执行到数据路径的选择,经常可以看到它的踪影。

另外在时钟、计数定时器等的输出显示电路中经常利用多路选择器制作扫描电路来分别驱动输出装置,以降低功率的消耗。

有时也希望把两组没有必要同时观察的数据,设置为共享一组显示电路,以降低成本。

二、关键词关键词:多路选择器,逻辑图,逻辑函数三、问题分析设计内容一:根据以下流程,利用QuartusII完成四选一多路选择器的文本编辑输入和仿真测试等步骤,给出仿真波形。

设计内容二:在试验系统上硬件测试,验证此设计的功能。

对于引脚锁定以及硬件下载测试。

设计内容三:对VHDL不同描述方式的四选一多路选择器进行硬件实验,比较他们的特性。

四选一选择器VHDL源程序如下:LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;ENTITY mux4a1 ISPORT (input:IN STD_LOGIC_VECTOR(3 DOWNTO 0);a,b:IN STD_LOGIC;y:OUT STD_LOGIC );END ENTITY mux4a1;ARCHITECTURE rtl OF mux4a1 ISSIGNAL sel:STD_LOGIC_VECTOR (1 DOWNTO 0);BEGINsel<=b&a;PROCESS (input,sel) IS BEGIN IF(sel="00") THEN y<=input(0); ELSIF(sel="01") THEN y<=input(1); ELSIF(sel="10") THEN y<=input(2); ELSE y<=input(3); END IF;END PROCESS;END ARCHITECTURE rtl;程序分析:四选一多路选择器设计时,定义输入S 为标准以内漏记为STD_LOGIC,输出的信号y 的数据类型定义为2位标准逻辑矢量位STD_LOGIC_VECTOR( 1 DOWNTO 0 ).使用LIBRATY 语句和USE 语句,来打开IEEE 库的程序包STD_LOGIC_1164.ALL 。

四选一数据选择器

四选一数据选择器

数据选择器(data selector) 根据给定的输入地址代码,从一组输入信号中选出指定的一个送至输出端的组合逻辑电路。

有时也把它叫做多路选择器或多路调制器。

在多路数据传送过程中,能够根据需要将其中任意一路选出来的电路,叫做数据选择器,也称多路选择器或多路开关

图所示的是四选一数据选择器的原理图。

图中的D0、D1、D2、D3是四个数据输入端,Y为输出端,A1、A0是地址输入端。

从表中可见,利用指定A1A0的代码,能够从D0、D1、D2、D3这四个输入数据中选出任何一个并送到输出端。

因此,用数据选择器可以实现数据的多路分时传送。

此外,数据选择器还广泛用于产生任意一种组合逻辑函数。

在图示电路中,若将Y看成是A0、A1及D0、D1、D2、D3的函数,则可写成

图1

如果把A1、A0视为两个输入逻辑变量,同时把D0、D1、D2和D3取为第三个输入逻辑变量A2的不同状态(即A2、/A2、1或0),便可产生所需要的任何一种三变量A2、A1、A0的组合逻辑函数。

可见,

利用具有n位地址输入的数据选择器可以产生任何一种输入变量数不大于n +1的组合逻辑函数。

其工作原理是你给A1A0一组信号比如1 0 那么就相当于给了他一个2进制数字2 也就相当于选通了D2这个输入端这个时候输出Y 输出的就是D2的信号

D2是什么Y就输出什么

输出表。