数字集成电路chapter1

《数字集成电路》课件

1 滤波

去除噪声、增强信号的关键技术。

2 变换

将信号在时域与频域之间转换的方法。

3 压缩

减少数据量,方便存储和传输。

数字信号处理中的滤波器设计

FIR滤波器

时域响应仅有有限个点,稳定性好。

IIR滤波器

时域响应呈指数衰减,延时较小。

模拟/数字混合信号集成电路

1

基础理论

混合信号电路设计所需的模拟电路与数字电路基础知识。

时序逻辑电路

触发器与锁存器

用于存储时钟信号冲突消除和数 据暂存。

计数器

移位寄存器

用于计算和记录触发事件的数量。

用于数据移位操作,实现数据的 串行传输。

数字信号处理技术

数字信号处理(DSP)是用数字计算机或数字信号处理器对原始信号进行处理、分析和存储的一 种技术。它在通信、音频处理和图像处理等领域具有广泛应用。

《数字集成电路》PPT课 件

数字集成电路PPT课件大纲: 1. 什么是数字集成电路 2. 数字集成电路的分类和结构

数字电路设计的流程

1

需求分析

确定数字电路的功能与性能要求,并定义输入输出及约束条件。

2

电路设计

利用逻辑门、触发器等基本组件进行数字电路设计。

3

电路仿真

使用仿真软件验证数字电路中的电气特性和功能。

2 低功耗设计

3 增强型通信

减少功耗,延长电池寿命。

提升通信性能和速度。

2

模拟数字转换

模拟和数字信号之间的转换方法和技术。

3

功耗与噪声

如何平衡功耗Βιβλιοθήκη 噪声性能。电路模拟与仿真SPICE仿真

使用电路仿真软件模拟电路 的工作状态。

参数提取与建模

数字集成电路设计第1章引论讲义.

v0

v1

v2

v3Biblioteka v4v5v6

v1 = f(v0) v1 = finv(v2)

v3

v1 finv(v)

f(v)

v1 v3

finv(v)

f(v)

v2

v0

v0

v2

2.4抗噪声能力

噪声容限描述的一个电路超过一个 噪声源的能力。 抗噪声能力则表明系统在噪声存在的情况下 正确处理和传递信息的能力。许多数字电路, 它们的噪声容限很小,但却有很好的抗噪声 能力。

4、工艺尺寸的缩小会使以抽象为基础的模型的其 它一些缺陷更为明显。例如时钟分布、电源分布 这样的问题更为关键。 5、工艺水平提高导致新的设计问题和约束条件会 不断出现。如功耗、器件和互连线寄生参数之间的 比例。 6、对一个设计进行检查和排错需要电路方面的 专门知识。

数字电路设计中运用的典型抽象层次按抽象程度增加的顺序依次为:

三、为什么在设计自动化可以解决所有的设计问题后, 我们还要去关心数字集成电路的设计呢?

原因如下:

1、工艺升级后,而模型库不能直接移植

2、对模块内部的理解。例如数字电路中对一个单元内部的 关键是时序路径的寻找 3、以抽象为基础的方法只在一定程度上是正确的。例如一个 加法器的性能还与其环境连接方式的影响。

二、功能性和稳定性

1电路响应出现偏离的原因: a,制造过程中存在差异 b,芯片上或芯片外存在的干扰噪声源。对数字电路而言,噪声 为指在逻辑节点上不希望发生的电压或电流的变化。 数字系统中的大多数噪声都是内部产生的,噪声的值与信号的 摆幅成正比。 如何克服这些噪声干扰是高性能数字电路设计所面临的主 要挑战之一。

噪声源可分为以下两种类型: A,与信号摆幅VSW成正比的噪声。它对信号节点的影响用gVsw来 表示 B,固定噪声。它对信号节点的影响等于fVNf,VNf是噪声源的幅值, 而f是从噪声到信号节点的传递函数

数字集成电路知识点整理

Digital IC:数字集成电路是将元器件和连线集成于同一半导体芯片上而制成的数字逻辑电路或系统第一章引论1、数字IC芯片制造步骤设计:前端设计(行为设计、体系结构设计、结构设计)、后端设计(逻辑设计、电路设计、版图设计)制版:根据版图制作加工用的光刻版制造:划片:将圆片切割成一个一个的管芯(划片槽)封装:用金丝把管芯的压焊块(pad)与管壳的引脚相连测试:测试芯片的工作情况2、数字IC的设计方法分层设计思想:每个层次都由下一个层次的若干个模块组成,自顶向下每个层次、每个模块分别进行建模与验证SoC设计方法:IP模块(硬核(Hardcore)、软核(Softcore)、固核(Firmcore))与设计复用 Foundry(代工)、Fabless(芯片设计)、Chipless(IP设计)“三足鼎立”——SoC发展的模式3、数字IC的质量评价标准(重点:成本、延时、功耗,还有能量啦可靠性啦驱动能力啦之类的)NRE (Non-Recurrent Engineering) 成本设计时间和投入,掩膜生产,样品生产一次性成本Recurrent 成本工艺制造(silicon processing),封装(packaging),测试(test)正比于产量综合可以相互转化加了功耗信息一阶RC网路传播延时:正比于此电路下拉电阻和负载电容所形成的时间常数功耗:emmmm自己算4、EDA设计流程IP设计系统设计(SystemC)模块设计(verilog)版图设计(.ICC) 电路级设计(.v 基本不可读)综合过程中用到的文件类型(都是synopsys):.db(不可读) .lib(可读).sdb .slib第二章器件基础1、保护IC的输入器件以抗静电荷(ESD保护)2、长沟道器件电压和电流的关系:3、短沟道器件电压和电流关系速度饱和:当沿着沟道的电场达到临界值ξC时,载流子的速度由于散射效应(载流子之间的碰撞)而趋于饱和。

数字集成电路设计英文版课程设计

Digital Integrated Circuit Design Course Design(English Version)AbstractDigital integrated circuit design is an important subject in thefield of electrical engineering. With the rapid development ofelectronic technology, digital integrated circuits have been widely used in various electronic devices. In this course design, the theoretical knowledge of digital integrated circuit design will be combined with practical applications, and students are required to design and simulate various digital integrated circuits.Learning GoalsThe goal of this course design is to enable students to understand the basic principles of digital integrated circuit design and to master the key design techniques and methods. By completing this course design, students will be able to:•Understand the principles and design methods of basic digital circuits•Design and simulate various digital integrated circuits•Analyze and optimize circuit performance•Apply design principles to solve practical problemsCourse OutlineChapter 1 - Introduction•Overview of digital integrated circuit design•Design flow of digital integrated circuits•Different CAD tools and simulation methodsChapter 2 - Combinational Logic Circuit Design•Boolean algebra and logic gate symbols•Minimization of Boolean function•Design of combinational logic circuits using gate-level and HDL-based methodsChapter 3 - Sequential Logic Circuit Design•Basic sequential circuits: latch and flip-flop•State machines and state diagrams•Design of sequential logic circuits using HDL-based methods Chapter 4 - Arithmetic Circuit Design•Design of half and full adders•Design of subtractors, multipliers, and dividers•Design of ALU and data path circuitsChapter 5 - Memory Circuit Design•SRAM and DRAM cell design•ROM and PLA circuit design•Design of register files and memory hierarchyChapter 6 - Verification and Testing•Overview of verification and testing•Test pattern generation and fault simulation•Design for testability and built-in self-testChapter 7 - Advanced Topics•Low-power design techniques•Clock distribution and clock gating design•Digital signal processing and custom circuitsCourse Design RequirementsThe following requirements should be met by students in the course design:1.Choose a digital integrated circuit design topic from thecourse outline.2.Write a design proposal that includes the design goal,specifications, and implementation plan.e industry-standard CAD tools to design and simulate thecircuit.4.Analyze the circuit performance and optimize the design ifnecessary.5.Write a final report that includes the circuit design,simulation results, and analysis.ConclusionBy completing this course design, students will have a deep understanding of digital integrated circuit design and simulation. They will be able to apply their knowledge to practical circuit design and bewell prepared for further study or work in the field of digital integrated circuits.。

数字集成电路简介.ppt

v(t)

– 耦合电容 - 其中一条导线上电压的 变化会影响相邻导线上的信号

i(t)

– 耦合电感 - 其中一条导线上电流的 变化会影响相邻导线上的信号

VD

• 电源线和地线上的噪声

D

– 会影响该门的信号电平

说明:噪声是数字电路工程中一个主要关注的问题。如何克服所有这 些干扰是高性能数字电路设计所面临的主要挑战之一。

2019年12月31日12时10分

例题1.2 电源分布网络对系统设计的挑战

功能块A

功能块B

功能块A

功能块B

A. 布线通过功能块

引论. 26

B. 布线绕过功能块

2019年12月31日12时10分

1.3 数字设计的质量评价

• 集成电路的成本 • 功能性和稳定性 • 性能 • 功耗和能耗

• 为了保证整个设计层次中定义的一致性,我们采用了从下 而上的设计方法:从定义一个简单反相器基本的质量评定 标准开始,并逐渐将它们扩展到如逻辑门、模块和芯片这 些更为复杂的功能

数字IC(组合/时序) 模拟IC(线性/非线性)

模数混合IC 通用IC、专用IC

2019年12月31日12时10分

划分集成电路规模的标准

类型

SSI MSI LSI VLSI ULSI GSI

数字集成电路

MOS IC

双极 IC

<100

<100

100~1000

100~500

103 ~ 105

500~2000

引论. 14

2019年12月31日12时10分

集成电路的概念

• Integrated Circuit,缩写IC

• 通过一系列特定的加工工艺,将晶体管、二极管等有源 器件、电容和电阻等无源器件,按照一定的电路互连, “集成”在一块半导体单晶片(如硅或砷化镓)上,封 装在一个外壳内,执行特定电路或系统功能

数字电子电路第二版电子课件第一章数字电路基础

§1—1 数字信号与数字电路

4

第一章 数字电路基础

当人们在超市购物结账付款时,收银员只要把条形码扫描器对准货物上 的条形码一扫,计算机屏幕上立刻就会显示该物品的价格。这是因为条形 码经扫描器扫描后,会产生相应的“数字信号”,经计算机处理后就可以 显示为货物的名称及价格等信息,进而可刷卡付款,打印付款收据。超市 自动收款设备如图所示。

非逻辑开关电路

44

第一章 数字电路基础

图所示为非门逻辑符号。非门真值表见表。 非门的逻辑功能可概括为“有0出1,有1出0”。非门的逻辑表达式为:

该表达式读作Y等于A非。

非门真值表

非门逻辑符号

45

28

第一章 数字电路基础

几种常见的BCD码

29

第一章 数字电路基础

(1)8421BCD码 最常用的BCD码是8421BCD码。 (2)5421BCD码 5421BCD码也是一种有权码,从高位到低位分别是5、4、2、1。 (3)2421BCD码 2421BCD码也是一种有权码,从高位到低位的权分别是2、4、2、1。 (4)余3码 这是一种无权码,它是在相应的8421BCD码上加0011(3)得到的。

15

第一章 数字电路基础

用数字电路测量电动机转速的原理框图

16

第一章 数字电路基础

2. 四人抢答器 四人抢答器原理框图如图所示。

四人抢答器原理框图

17

第一章 数字电路基础

从以上两个电路的工作过程可以看出,数字电路大致包含数字信号的产 生与整形、编码、寄存、译码、显示等典型单元数字电路。

此外,为了将传感器转换而来的模拟信号转换成控制系统所需要的数字 信号,必须采用模数转换器(A/D Converter)。数字信号被处理后,通常 还要经过数模转换器(D/A Converter)恢复成模拟信号,去驱动执行元件, 如图所示。

《数字集成电路设计》课件

深入研究加法器和减法器的原理,了解如何进行数字的加法和减法运算。

贝叶斯定理在电路设计中的应 用

介绍贝叶斯定理在电路设计中的应用场景,讲解如何利用先验知识和观测结 果进行后验概率的计算。

层级与模块化设计

层级设计

了解层级设计的原理和方法,掌握如何将复杂的电 路分解为多个模块进行设计和测试。

仿真实例

通过案例分析和实际仿真实例,加深对 电路仿真工具和流程的理解和应用。

计算机辅助设计方法与工具介 绍

介绍计算机辅助设计的基本原理和方法,以及常用的电路设计工具,包括EDA 软件和硬件描述语言。

引言

数字集成电路设计是现代信息技术的关键领域,本课程将深入探讨数字电路 设计的理论和实践,为学生打下坚实的基础。

逻辑门与布尔代数

了解常用逻辑门的工作原理,掌握布尔代数的基本概念和运算规则,为后续的电路设计奠定基础。

时序逻辑电路设计基础

1

触发器和计数器

2

深入研究各种触发器和计数器的原理和

应用,掌握时序逻辑电路的设计技巧。

《数字集成电路设计》PPT课件

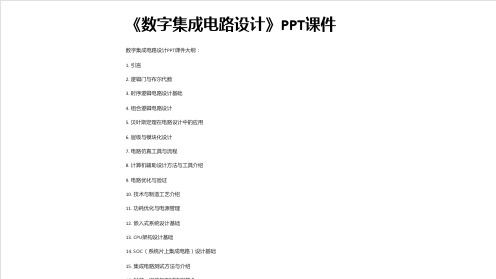

数字集成电路设计PPT课件大纲: 1. 引言 2. 逻辑门与布尔代数 3. 时序逻辑电路设计基础 4. 组合逻辑电路设计 5. 贝叶斯定理在电路设计中的应用 6. 层级与模块化设计 7. 电路仿真工具与流程 8. 计算机辅助设计方法与工具介绍 9. 电路优化与验证 10. 技术与制造工艺介绍 11. 功耗优化与电源管理 12. 嵌入式系统设计基础 13. CPU架构设计基础 14. SOC(系统片上集成电路)设计基础 15. 集成电路测试方法与介绍

模块化设计

学习模块化设计的思想和技术,掌握如何将多个模 块进行组合,实现复杂功能的集成电路设计。

数字集成电路第1章PPT课件

双极集成电路的基本制造工艺

掺硼P型硅作为衬底材料并进行初始氧化,以形 成二氧化硅表层,然后再进行隐埋层光刻以形 成一个窗口后进行N+层掺杂,接着就用外延层 所覆盖,故称隐埋层

制作隐埋层后,去除表面的二氧化硅,再进行N 型外延层生长

掺P型材料进行隔离扩散. 用第三块掩模版完成基区光刻

双极集成电路的基本制造工艺

基区重掺杂 制作晶体管发射极和集电极 形成表面金属互连接的接触区 完成一层金属铝膜的沉积,然后再介质淀积 在介质层上蚀刻出连接通孔 成第二层金属铝膜的沉积 后续工序,划片,粘片,压焊,封装,测试分类,筛选,

成品测试,入库

双极集成电路应用

TTL,DTL,RTL,HTL,ECL STLL,SLTTL,I2L,I3L ASTLL.ASLTTL

环 长PSG 引线孔光刻 铝引线光刻 压焊块光刻

N阱硅栅CMOS工艺(略)

▪ 双阱硅栅CMOS工艺

BI---CMOS工艺

双极工艺特点: 速度高、驱动能力强、模拟精度高 但功耗、集成度无法满足VLSI的

要求

BI---CMOS工艺

CMOS工艺特点: 功耗低、集成度高、抗干扰能力强 但速度低、驱动能力差

成

P+

NPN管的基区扩散 PMOS管的源、漏区扩散 横向PNP管集电区、发射区扩散 纵向PNP管的发射区扩散可以同时进行完成

以双极性工艺为基础的P阱BICMOS工艺

栅氧化在PMOS管沟道注入以后进行 可获的大电流、高压 LDMOS-LOW DOUBLE MOS VDMOS-VERTICAL DOUBLE MOS

以双极性工艺为基础的BI-CMOS工艺

以双极性工艺为基础的P阱BI-CMOS工艺 以双极性工艺为基础的双阱BI-CMOS工艺 特点是对双极器件有利

数字集成电路

CMOS - 数字集成电路(讲义)编著吴金东南大学无锡分校2008.09目录第一章 绪论1.1信号处理的对象方式与特点1.2教学方法与重要知识点1.3课程目标与要求1.4主要参考文献1-5第二章静态组合逻辑电路2.1概述2.2组合逻辑2.3 NMOS反相器2.4 CMOS组合逻辑的实现原理2.4.1 CMOS逻辑原理2.4.2 静态CMOS倒相器2.4.3 CMOS逻辑门2.5 NMOS组合逻辑逻辑2.5.1 NMOS基本逻辑门2.5.2 伪NMOS逻辑2.6传输门开关逻辑2.6.1 CPL逻辑2.6.2、DPL逻辑2.6.3 多路开关MUX逻辑2.7 差分逻辑2.8本章小结2-23第三章动态组合逻辑电路3.1 概述3.2动态逻辑3.3多米诺动态组合逻辑电路3.3.1 同型Domino-CMOS动态逻辑3.3.2 np-CMOS 动态逻辑3.4 钟控逻辑3.5 钟控动态逻辑电路3.4.1 无竞争动态逻辑 NPORA3.4.2 单相位时钟动态逻辑3.4.3 差分动态逻辑3.6本章小结 3-13第四章时序逻辑电路4.1概述4.2锁存器 - Latch4.3触发器 – Flip-Flop4.3.1 边沿型触发器4.3.2主从R-S触发器4.4逻辑电路结构4.4.1 D_Latch电路4.4.2 D_FF电路4.5寄存器 Register4.5.1 双港口寄存器4.5.2 移位寄存器4.6分频器 Frequency Divide4.6.1 基本1/2分频单元4.6.2 规则分频器/计数器4.6.3 奇数分频器4.6.4 任意占空比和任意进制的分频器4.6.5 1:1占空比的奇数分频器(1/N, Odd N)4.7计数器 - Counter4.7.1 N进制异步计数器4.7.2 N进制同步计数器4.8 本章小结4-25第五章数据与控制通道5.1概述5.2 1-bit加法器5.2.1 1bit 半/全加器原理5.2.2 基于传输逻辑的1bit全加器5.3 N-bit加法器5.3.1 进位完成加法器CCA(Carry Completion Adder)5.3.2 条件加法器-Conditional Sum Adder(CSA)5.3.3 进位选择加法器-Carry Select Adder(CSA)5.3.4 超前进位加法器-Carry Lookahead Adder(CLA)5.4编码/解码电路5.4.1 组合逻辑译码电路5.4.2 阵列译码电路5.4.3 可编程译码电路5.5控制电路5.6本章小结5-26第六章存储器6.1概述6.2 SRAM存储器6.2.1 存储单元6.2.2 存储阵列的系统结构6.2.3地址译码器6.2.4灵敏放大器6.3 非挥发存储器6.3.1 ROM6.3.2 EPROM和E2PROM6.4本章小结6-17第七章时钟与时序7.1 概述7.2 正弦波振荡器7.2.1振荡原理7.2.2 RC振荡器7.2.3 石英谐振器7.2.4并联石英晶振电路7.2.5 串联晶振电路7.3 矩形波振荡器7.3.1基于迟滞比较器结构7.3.2基于迟滞触发器结构7.3.3基于CMOS倒相器结构7.3.4晶体多谐振荡器7.3.5环形振荡器7.4 三角波振荡器7.5 Ramp锯齿波振荡器7.6 集成振荡电路7.6.1七级恒流环振7.6.2频率可配置环形振荡电路7.6.3弛豫振荡器7.7 非交叠时钟7.8 时钟相对延迟7.9 流水线7.10 本章小结7-34第八章 比较器与接口电路8.1概述8.2比较器结构与功能类型8.2.1 结构类型8.2.2 功能类型8.2.3 迟滞比较器8.3电压差分比较器8.3.1 多级差分比较器结构8.3.2 多级差分迟滞比较器8.3.3 CMOS施密特触发器8.3.4 电源电压比较器8.3.5动态电压比较器8.3.6 锁存比较器8.4 数字接口电路8.4.1 逻辑电平接口8.4.2功能接口电路8.5 本章小结 8-30。

数字集成电路(时序逻辑电路)

目录

• 引言 • 时序逻辑电路的基本概念 • 数字集成电路的组成 • 时序逻辑电路的分析方法

目录

• 引言 • 时序逻辑电路的基本概念 • 数字集成电路的组成 • 时序逻辑电路的分析方法

目录

• 时序逻辑电路的设计方法 • 时序逻辑电路的应用 • 时序逻辑电路的发展趋势和挑战

逻辑门

01

逻辑门是数字集成电路的基本组成单元,用于实现逻辑运算(如AND、 OR、NOT等)。

02

常见的逻辑门有TTL(Transistor-Transistor Logic)和CMOS (Complementary Metal-Oxide Semiconductor)等类型。

03

逻辑门通常由晶体管组成,通过不同的组合和连接方式实现各种逻辑 功能。

目录

• 时序逻辑电路的设计方法 • 时序逻辑电路的应用 • 时序逻辑电路的发展趋势和挑战

01

引言

01

引言

主题简介

数字集成电路

数字集成电路是利用半导体技术将逻 辑门、触发器等数字逻辑单元集成在 一块衬底上,实现数字信号处理功能 的集成电路。

时序逻辑电路

时序逻辑电路是一种具有记忆功能的 电路,其输出不仅取决于当前的输入 ,还与电路的先前状态有关。常见的 时序逻辑电路有寄存器、计数器等。

时序图

通过图形方式表示时序逻辑电路的输入和输出随时间变化的规律,能够直观地展 示电路的工作过程。

逻辑方程和时序图

逻辑方程

描述时序逻辑电路输入和输出关系的数学表达式,通常由触发器的状态方程和输 出方程组成。

时序图

通过图形方式表示时序逻辑电路的输入和输出随时间变化的规律,能够直观地展 示电路的工作过程。

数字集成电路设计 第一章

▪ 以 X-Fab 、 Jazz Semiconductor 为 代 表 的 企 业 以 提 供 特 殊 Foundry服务(RF、Analog)而拥有自己的一席之地。

无生产线的IC设计公司(Fabless)与IC代工制造公司 (Foundry) 相配合的方式成为IC产业发展的重要模式。

© DEEig1i4ta1l Integrated Circuits2nd

Digital Integrated Circuits

A Design Perspective

Jan M. Rabaey Anantha Chandrakasan Borivoje Nikolic

Introduction

吉林大学课程中心:数字集成电路设计

材料、设备业开发技术难度大,属于基础科学类 开发费用高,因此进入门槛高。

半导体设备制造业被AMAT(应材)、ASML( 艾司摩尔)-光刻机、Lam Research(科林研 发)-等离子刻蚀和单晶圆清洗、LKA-Tencor( 科磊)、Dainippon Screen(迪恩仕)等欧美 企业垄断。

© DEEig1i4ta1l Integrated Circuits2nd

7

Introduction

硅纳米电子学材料

早期所需材料种类相比于目前很少

©Hale Waihona Puke DEEig1i4ta1l Integrated Circuits2nd

8

Introduction

三、封装、测试业分离后的集成电路产业

二十世纪70年代,封装、测试业逐渐从整个产业 中分离出来。

数字集成电路知识点整理

Digital IC:数字集成电路是将元器件和连线集成于同一半导体芯片上而制成的数字逻辑电路或系统第一章引论1、数字IC芯片制造步骤设计:前端设计(行为设计、体系结构设计、结构设计)、后端设计(逻辑设计、电路设计、版图设计)制版:根据版图制作加工用的光刻版制造:划片:将圆片切割成一个一个的管芯(划片槽)封装:用金丝把管芯的压焊块(pad)与管壳的引脚相连测试:测试芯片的工作情况2、数字IC的设计方法分层设计思想:每个层次都由下一个层次的若干个模块组成,自顶向下每个层次、每个模块分别进行建模与验证SoC设计方法:IP模块(硬核(Hardcore)、软核(Softcore)、固核(Firmcore))与设计复用Foundry(代工)、Fabless(芯片设计)、Chipless(IP设计)“三足鼎立”——SoC发展的模式3、数字IC的质量评价标准(重点:成本、延时、功耗,还有能量啦可靠性啦驱动能力啦之类的)NRE (Non-Recurrent Engineering) 成本设计时间和投入,掩膜生产,样品生产一次性成本Recurrent 成本工艺制造(silicon processing),封装(packaging),测试(test)正比于产量一阶RC网路传播延时:正比于此电路下拉电阻和负载电容所形成的时间常数功耗:emmmm自己算4、EDA设计流程IP设计系统设计(SystemC)模块设计(verilog)综合版图设计(.ICC) 电路级设计(.v 基本不可读)综合过程中用到的文件类型(都是synopsys版权):可以相互转化.db(不可读).lib(可读)加了功耗信息.sdb .slib第二章器件基础1、保护IC的输入器件以抗静电荷(ESD保护)2、长沟道器件电压和电流的关系:3、短沟道器件电压和电流关系速度饱和:当沿着沟道的电场达到临界值ξC时,载流子的速度由于散射效应(载流子之间的碰撞)而趋于饱和。

数字集成电路1PPT课件

非转换电路

转换电路

“1 ” “0 ”

V OH V IH 不确定区域

V IL V OL

V out V OH

V OL

斜率 = -1

V DD

Vin

Vout

斜率 = -1

V IL V IH

V in

噪声容限

"1" V

OH

V OL

"0" 逻辑门输出

NM H NM L

高噪声容限

V IH 不确定区

V IL

低噪声容限

LOG2 OF THE NUMBER OF COMPONENTS PER INTEGRATED FUNCTION

1959 1960 1961 1962 1963 1964 1965 1966 1967 1968 1969 1970 1971 1972 1973 1974 1975

16 15

• Electronics, April

芯片面积

约为 3

芯片成本 f (芯片面积 )4

可靠性―集成电路中的噪声

i ( t)

电感耦合

v (t)

电容耦合

V DD

电源、地噪声

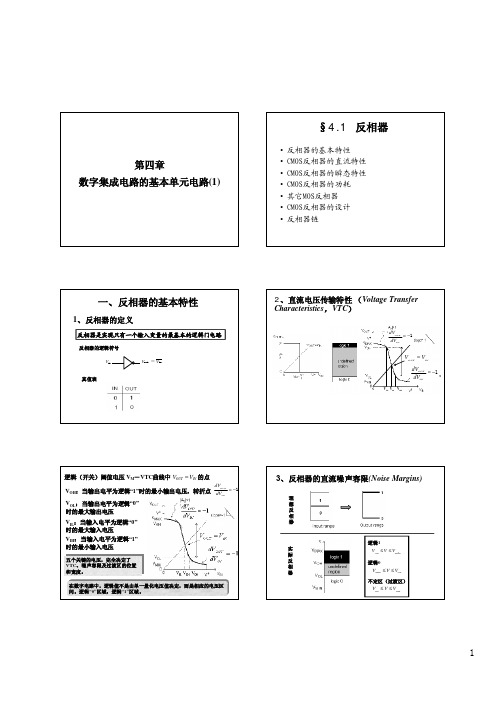

直流特性:电压传输特性( VTC ) (Voltage Transfer Characteristic)

理想的数字电路

直流特性:电压传输特性( VTC ) (Voltage Transfer Characteristic)

• 数字电路与模拟电路相比的优势 • 功能增加灵活 • 规模/速度随工艺按比例下降而优化 • 对工艺/电压/温度不敏感

• 电路设计应考虑: • 可靠性 • 速度 • 功耗 • 面积 • 成本

1.1 绪论

集成电路功能分类 归类 电压

集成电路功能分类归类电压1.引言1.1 概述概述部分的内容应该是对整篇文章的大致介绍和背景说明。

以下是一种可能的写作方式:引言部分是对集成电路功能分类和电压相关知识的全面介绍。

在这篇文章中,我们将详细探讨集成电路的功能分类和电压的重要性。

集成电路是现代电子设备中的基础组件,它们被广泛应用于计算机、通信、控制系统等领域。

首先,我们将介绍集成电路的功能分类。

在不同的应用场景中,集成电路具有不同的功能和特点。

我们将探讨数字集成电路、模拟集成电路和混合集成电路等不同类型的功能分类,以及它们在不同领域的应用。

其次,我们将讨论集成电路的归类方法。

根据不同的标准和特征,集成电路可以被归类为不同的类型。

我们将介绍常见的归类方式,如按集成度、按封装形式、按应用领域等进行归类,并分析其优缺点和适用范围。

最后,我们将重点关注电压在集成电路中的重要性。

电压是集成电路正常运行的关键因素之一,合适的电压水平可以保证电路的稳定性和性能。

我们将探讨不同电压水平对集成电路的影响,以及如何选择适当的电压供应方案。

通过对集成电路功能分类和电压的详细分析,我们可以更好地理解集成电路的特点和应用。

这对于电子工程师和电路设计者来说是非常重要的,也有助于推动集成电路技术的发展。

在接下来的章节中,我们将进一步展开对集成电路功能分类和电压的讨论,以期增加读者对这些内容的深入理解。

文章结构部分为:1.2 文章结构本篇文章主要分为三个部分:引言、正文和结论。

以下是对每个部分的具体介绍:引言部分(Chapter 1)主要包括概述、文章结构和目的。

在概述中,将简要介绍集成电路功能分类的重要性和应用。

文章结构部分将对整篇文章的结构进行说明,使读者了解到文章的整体脉络。

最后,在目的部分将明确指出本文的目标是什么,以便读者可以清晰地了解文章的意义和价值。

正文部分(Chapter 2)将详细介绍集成电路功能分类、归类和电压等相关内容。

在2.1小节中,将详细探讨集成电路功能分类的不同方面,包括根据功能进行分类的标准和方法。

数字集成电路第一章

Complexity Logic Transistor per Chip (M)

100,000 100,000,000

1,000 1,000,000 58%年增长率 100 100,000 10 10,000 21%年增长率 1 1,000 0.1 100 0.01 10

0.01 10 0.001 1

286 486 8086 386 10 8085 8080 8008 1 4004 0.1

1971 1974 1978 1985 1992 2000 2004 2008 Year

EE141 数字集成电路

引言

29

CMOS的摩尔定律

功率密度

– 功率密度过高导致结温升高!

10000 Power Density (W/cm2)

– Bardeen – Schockley

EE141 数字集成电路

引言

15

集成电路革命

双极型

– 1960年代

发明人

– Jack Kilby

ECL 3输入逻辑门

– 1966年

发明人

– Motorola

EE141 数字集成电路

引言

16

集成电路工艺沿革

双极型

– 1947年:晶体管(Bardeen/Bell Lab) – 1949年:双极型晶体管(Schockley) – 1956年:数字逻辑门(Harris) – 1962年:TTL系列( Beeson/Fairchild ) – 1974年:ECL高速系列(Masaki) – 1972年:I2L低功耗高密度系列(Hart)

1981

1983

1985

1987

1989

1991

数字集成电路物理设计

数字集成电路物理设计作者:陈春章艾霞王国雄出版社:科学出版社出版日期:2008年1月页数:285 装帧:开本:16 版次:商品编号:2022071 ISBN:703022031 定价:36元丛书序前言第1章集成电路物理设计方法1.1数字集成电路设计挑战1.2数字集成电路设计流程l.2.1展平式物理设计1.2.2硅虚拟原型设计1.2.3层次化物理设计1.3数字集成电路设计收敛1.3.1时序收敛1.3.2功耗分析1.3.3可制造性分析1.4数字集成电路设计数据库1.4.1数据库的作用与结构1.4.2数据库的应用程序接口1.4.3数据库与参数化设计1.5总结习题参考文献第2章物理设计建库与验证2.1集成电路工艺与版图2.1.1 CMOS集成电路制造工艺简介2.1.2 CMOS器件的寄生闩锁效应2.1.3版图设计基础2.2设计规则检查2.2.1版图设计规则2.2.2 DRC的图形运算函数2.2.3 DRC在数字IC中的检查2.3电路规则检查2.3.1电路提取与比较2.3.2电气连接检查2.3.3器件类型和数目及尺寸检查数字集成电路物理设计2.3.4 LVS在数字IC中的检查2.4版图寄生参数提取与设计仿真2.4.1版图寄生参数提取2.4.2版图设计仿真2.5逻辑单元库的建立2.5.1逻辑单元类别2.5.2逻辑单元电路2.5.3物理单元建库与数据文件2.5.4时序单元建库与数据文件2.5.5工艺过程中的天线效应2.6总结习题参考文献第3章布图规划和布局3.1布图规划3.1.1布图规划的内容和目标3.1.2 I/0接口单元的放置与供电3.1.3布图规划方案与延迟预估3.1.4模块布放与布线通道3.2电源规划3.2.1电源网络设计3.2.2数字与模拟混合供电3.2.3时钟网络3.2.4多电源供电3.3布局3.3.1展平式布局3.3.2层次化布局3.3.3布局目标预估3.3.4标准单元布局优化算法3.4扫描链重组3.4.1扫描链定义3.4.2扫描链重组3.5物理设计网表文件3.5.1设计交换格式文件3.5.2其他物理设计文件3.6总结习题参考文献第4章时钟树综合4.1时钟信号4.1.1系统时钟与时钟信号的生成4.1.2时钟信号的定义4.1.3时钟信号延滞4.1.4时钟信号抖动4.1.5时钟信号偏差4.2时钟树综合方法4.2.1时钟树综合与标准设计约束文件4.2.2时钟树结构4.2.3时钟树约束文件与综合4.3时钟树设计策略4.3.1时钟树综合策略4.3.2时钟树案例4.3.3异步时钟树设计4.3.4锁存器时钟树4.3.5门控时钟4.4时钟树分析4.4.1时钟树与时序分析4.4.2时钟树与功耗分析4.4.3时钟树与噪声分析4.5总结习题参考文献第5章布线5.1全局布线5.1.1全局布线目标5.1.2全局布线规划5.2详细布线5.2.1详细布线目标5.2.2详细布线与设计规则5.2.3布线修正5.3其他特殊布线5.3.1电源网络布线5.3.2时钟树布线5.3.3总线布线数字集成电路物理设计5.3.4实验布线5.4布线算法5.4.1通道布线和面积布线5.4.2连续布线和多层次布线5.4.3模块设计和模块布线5.5总结习题参考文献第6章静态时序分析6.1延迟计算与布线参数提取6.1.1延迟计算模型6.1.2电阻参数提取6.1.3电容参数提取6.1.4电感参数提取6.2寄生参数与延迟格式文件6.2.1寄生参数格式sPF文件6.2.2标准延迟格式SDF文件6.2.3 sDF文件的应用6.3静态时序分析6.3.1时序约束文件6.3.2时序路径与时序分析6.3.3时序分析特例6.3.4统计静态时序分析6.4时序优化6.4.1造成时序违例的因素6.4.2时序违例的解决方案6.4.3原地优化6.5总结习题参考文献第7章功耗分析7.1静态功耗分析7.1.1反偏二极管泄漏电流7.1.2门栅感应漏极泄漏电流7.1.3亚阈值泄漏电流7.1.4栅泄漏电流7.15静态功耗分析第8章信号完整性分析第9章低功耗设计技术与物理实施第10章芯片设计的终验证与签核附录索引数字专用集成电路的设计与验证本书作者:杨宗凯,黄建,杜旭编著第1章概述1.1 引言1.2 ASIC的概念1.3 ASIC开发流程1.4 中国集成电路发展现状第2章Verilog HDL硬件描述语言简介2.1 电子系统设计方法的演变过程2.2 硬件描述语言综述2.3 Verilog HDL的基础知识2.4 Verilog HDL的设计模拟与仿真第3章ASIC前端设计3.1 引言3.2 ASIC前端设计概念3.3 ASIC前端设计的工程规范3.4 设计思想3.5 结构设计3.6 同步电路3.7 ASIC前端设计基于时钟的划分3.8 同步时钟设计3.9 ASIC异步时钟设计4.10 小结第4章ASIC前端验证4.1 ASIC前端证综述4.2 前端验证的一般方法4.3 testbench4.4 参考模型4.5 验证组件的整合与仿真4.6 小结第5章逻辑综合5.1 综合的原理和思路5.2 可综合的代码的编写规范5.3 综合步骤5.4 综合的若干问题及解决……第6章可测性技术第7章后端验证附录A 常用术语表附录B Verilog语法和词汇惯用法附录C Verilog HDL关键字附录D Verilog 不支持的语言结构参考文献yoyobao编号:book194094作者:杨宗凯,黄建,杜旭编著(点击查看该作者所编图书)出版社:电子工业出版社(点击查看该出版社图书)出版日期:2004-10-1ISBN:7121003783装帧开本:胶版纸/0开/ 0页/480000字版次:1原价:¥28VLSI设计方法与项目实施点击看大图市场价:¥43.00 会员价:¥36.55【作者】邹雪城;雷鑑铭;邹志革;刘政林[同作者作品]【丛书名】普通高等教育“十一五”规划教材【出版社】科学出版社【书号】9787030194510【开本】16开【页码】487【出版日期】2007年8月【版次】1-1【内容简介】本书以系统级芯片LCD控制器为例,以数模混合VLSI电路设计流程为线索,系统地分析了VLSI系统设计方法,介绍了其设计平台及流行EDA软件。

数字集成电路--电路、系统与设计(第二版)复习资料

第一章 数字集成电路介绍第一个晶体管,Bell 实验室,1947第一个集成电路,Jack Kilby ,德州仪器,1958 摩尔定律:1965年,Gordon Moore 预言单个芯片上晶体管的数目每18到24个月翻一番。

(随时间呈指数增长)抽象层次:器件、电路、门、功能模块和系统 抽象即在每一个设计层次上,一个复杂模块的内部细节可以被抽象化并用一个黑匣子或模型来代替。

这一模型含有用来在下一层次上处理这一模块所需要的所有信息。

固定成本(非重复性费用)与销售量无关;设计所花费的时间和人工;受设计复杂性、设计技术难度以及设计人员产出率的影响;对于小批量产品,起主导作用。

可变成本 (重复性费用)与产品的产量成正比;直接用于制造产品的费用;包括产品所用部件的成本、组装费用以及测试费用。

每个集成电路的成本=每个集成电路的可变成本+固定成本/产量。

可变成本=(芯片成本+芯片测试成本+封装成本)/最终测试的成品率。

一个门对噪声的灵敏度是由噪声容限NM L (低电平噪声容限)和NM H (高电平噪声容限)来度量的。

为使一个数字电路能工作,噪声容限应当大于零,并且越大越好。

NM H = V OH - V IH NM L = V IL - V OL 再生性保证一个受干扰的信号在通过若干逻辑级后逐渐收敛回到额定电平中的一个。

一个门的VTC 应当具有一个增益绝对值大于1的过渡区(即不确定区),该过渡区以两个有效的区域为界,合法区域的增益应当小于1。

理想数字门 特性:在过渡区有无限大的增益;门的阈值位于逻辑摆幅的中点;高电平和低电平噪声容限均等于这一摆幅的一半;输入和输出阻抗分别为无穷大和零。

传播延时、上升和下降时间的定义传播延时tp 定义了它对输入端信号变化的响应有多快。

它表示一个信号通过一个门时所经历的延时,定义为输入和输出波形的50%翻转点之间的时间。

上升和下降时间定义为在波形的10%和90%之间。

对于给定的工艺和门的拓扑结构,功耗和延时的乘积一般为一常数。

数字集成电路第一章

微系统(续)

• 狭义:信息系统的芯片集成,即片上系统 (Sytem on a chip,SOC)

– SOC是微电子技术当前最迫切、现实的方向

• IC制造技术已经提供了构成SOC的能力,IC设计技 术相对落后于这一形势成为瓶颈 • 人类社会信息化迫切需求:计算机、通信与网络、 消费信息产品(3G) • IC向IS转变需要概念上的突破

2013-8-7

上海大学《数字集成电路设计》

深亚微米(DSM)挑战

2013-8-7

上海大学《数字集成电路设计》

设计能力的发展趋势

芯片复杂度的增长速度超过了设计能力的增长速度

2013-8-7 上海大学《数字集成电路设计》

第二节 微电子技术发展的两个方向

• 由微电子学向纳电子学转变——纳电子学

– 纳电子学两重意义:(1)在现在电子器件基础上把微电子器件尺 寸推进到纳米范畴:(2)发展新原理的纳米器件。 – 狭义上:纳器件 – 广义上:纳系统

2013-8-7

上海大学《数字集成电路设计》

• (一)深亚微米与超深亚微米设计

– (1)精确的模型 – 1、SPICE模型 器件中原来的二级效应成为一级效应。 一维模型成为二、三维模型。 不同几何尺寸器件的电学特性也不同。

2013-8-7

上海大学《数字集成电路设计》

HSPICE支持的主要模型

其中BSIM短沟绝缘栅场效应晶体管(Berkeley Shortchannel IGFET Model)被工业界广泛采用,成为事实 上的工业标准。 模拟电路特别是射频电路用的精确模型更加复杂。

– 60至70年代:微处理器、存储器、逻辑IC标准化导致 系统公司与IC公司分离 – 80至90年代:ASIC设计技术观念变革导致专职设计的 Fabless-IC公司与专职加工的Foundry-IC公司分离 – 21世纪:随着IC向IS转变,芯片系统(SOC)成为方 向。它强调基于IP核的设计,导致专职IP开发的 Chipless-IC公司的兴起

第4章 数字集成电路的基本单元电路1

VIH + VIL = VDD

具有相等的噪声 容限: NML= NMH

üVin= VDD,NMOS导通,PMOS截止 , 稳态Vout=0;

VDD

Vin = VDD

V out = 0

CMOS反相器的工作特点:

ü Vout=Vin; ü 稳态单管导通,没有直 通电流

反相器中 MOSFET的 工作 区域

Vout

N- O P-L N-S P-L N-L P-S

二、CMOS反相器的直流特性

低电平信号的噪声容限NML: NML= VIL- VOL

NM L

噪声影响下的数字信号传播

设在无噪声条件下,输入电压和输出电压间的关系为 VOUT = f (VIN ) 如果输入信号由于噪声而偏离额定值,则输出电压也会偏离 原先的额定值

' VOUT = f (VIN ) +

dVOUT ∆VIN + 高阶项(忽略) dVIN

1 Wp 2 µ pCox 2 (VIN − VDD − VTp ) (VOUT − VDD ) − (VOUT − VDD ) 2 Lp

K n (VIL − VTn ) = K p ( 2VOUT − VIL + VTp − VDD )

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

8008 4004

0.1 1971 1974 1978 Year 1985 1992 2000

主流处理器功耗持续增加(CMOS工艺的采用出现短暂下降)

EE141 © Digital Integrated

Circuits2nd

Courtesy, Intel

Introduction

23

Power will be a major problem

EE141 © Digital Integrated Circuits2nd

The First Transistor

•1947年 Bell Lab的 布拉顿和巴 丁发明了第 一只晶体管 •1948年 Bell Lab的 肖克利发明 了现代晶体 管的始祖— —结型晶体 管

9

EE141 © Digital Integrated

Circuits2nd Introduction

3

EE141 © Digital Integrated

Class Material

Textbook: “Digital Integrated Circuits – A Design Perspective,” 2nd Edition, by J.Rabaey, A. Chandrakasan, and B. Nikolic

1959 1960 1961 1962 1963 1964 1965 1966 1967 1968 1969 1970 1971 1972 1973 1974 1975

Circuits2nd Introduction

17

Evolution in Complexity

EE141 © Digital Integrated

Circuits2nd

Introduction

18

Transistor Counts

K 1,000,000 100,000 10,000 1,000 100 10

8086

Source: Intel

1 Billion Transistors

Pentium® III Pentium® II Pentium® Pro Pentium®

EE141 © Digital Integrated

Circuits2nd

Introduction

2

What is this Course all about?

Introduction to digital integrated circuits.

manufacturing CMOS devices Wire CMOS inverters Static/Dynamic CMOS gates Sequential circuits Interconnect Arithmetic memories

Circuits2nd

Introduction

11

The First MOS Device

1957年仙童半导体公司成 功地制造出金属氧化物半 导体(MOS)器件 1958年美国仙童电子公司 赫尔尼等人发明了一整套 制作微型晶体管的新工艺 ──“平面工艺“被移用到 集成电路的制作中,使集 成电路很快从实验室研制 试验阶段转入工业生产阶 段。

8086 10 4004 Hot Plate P6 8008 8085 Pentium® proc 386 286 486 8080 1 1970 1980 1990 2000 2010 Year

功率密度太大,以至于无法降低结温

EE141 © Digital Integrated

Circuits2nd

EE141 © Digital Integrated

Circuits2nd

Introduction

15

Moore’s Law

1965年,

Gordon Moore 预测 :

单芯片的晶体管数以每18个月~24个 月翻倍.

EE141 © Digital Integrated

Circuits2nd

Introduction

EE141 © Digital Integrated

Circuits2nd

Introduction

6

The First Vaccum Tube

1904年英国电气工程师弗 莱明发明第一只真空二极 管 1906年美国科学家德· 福雷 斯特发明第一只具有放大 作用的真空三极管 电子管产生后,计算机便 跨入电子纪元 左下图是现在使用的电子 管

EE141 © Digital Integrated

Circuits2nd

Introduction

5

The First Computer

•1834年 Babbage发明 •差动引擎机械计算装置 (Difference Engine) •25,000 各机械部件 •成本为 £17,470

特点: •十进制系统 •可执行加减乘除运算 •基本概念与现代计算机 很相似 •设计复杂 •成本高昂

22

EE141 © Digital Integrated

Circuits2nd

Courtesy, Intel

Introduction

Power Dissipation

100 P6 Pentium ® proc 10 8086 286 1 8085 8080 486 386 Power (Watts)

Units

48M 86M 162M 260M 435M

Analog Baseband

Digital Baseband (DSP + MCU)

(data from Texas Instruments)

EE141 © Digital Integrated

Circuits2nd

Introduction

26

16

EE141 © Digital Integrated

LO G 2 O F THE NUM BER OF COM PONENTS PER INTEGRATED FUNCTION

16 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

Moore’s Law

Electronics, April 19, 1965.

Challenges in Digital Design

DSM

“Microscopic Problems”

• Ultra-high speed design • Interconnect • Noise, Crosstalk • Reliability, Manufacturability • Power Dissipation • Clock distribution. Everything Looks a Little Different

EE141 © Digital Integrated

Circuits2nd

Introduction

12

Intel 4004 Micro-Processor

1971年 仅用NMOS 2250 个晶体管 3x4mm2 108kHz 时钟速率 历史 CMOS PMOS NMOS CMOS

主流的单片处理器晶体管数约每2年翻倍

EE141 © Digital Integrated

Circuits2nd

Introduction

20

Die Size Growth

100 Die size (mm)

10 8080 8008 4004 1 1970 8086 8085 286

386

P6 Pentium ® proc 486

Courtesy, Intel

Introduction

25

Not Only Microprocessors

Cell Phone

Small Signal RF Power RF

Digital Cellular Market (Phones Shipped)

Power Management

1996 1997 1998 1999 2000

Circuits2nd

Introduction

TRADIC - The first full-transisitor computer (1955)

贝尔实验室研制出 世界上第一台全晶 体管计算机 TRADIC, 装有 800只晶体管,仅 100瓦功率,体积3 立方英尺。

EE141 © Digital Integrated

i486 i386 80286

1 1975 1980 1985 1990 1995 2000 2005 2010

Projected

EE141 © Digital Integrated

Circuits2nd

Courtesy, Intel

Introduction

19

Moore’s law in Microprocessors

EE141 © Digitation

13

Intel Pentium (IV) microprocessor

EE141 © Digital Integrated

Circuits2nd

Introduction

14

目录

历史回顾 数字IC设计中的问题 数字设计的质量评价

Circuits2nd

Introduction

10

The First Integrated Circuits

1958年TI的Jack Kilby 制成了世界 上第一块集成电 路。使用半导体 单晶硅制成了相 移振荡器,其中 的每个元器件已 不需要用金属导 线相连。

EE141 © Digital Integrated

EE141 © Digital Integrated