北大数字集成电路课件--7_verilog的基本单元.ppt

合集下载

《数字集成电路》课件

1 滤波

去除噪声、增强信号的关键技术。

2 变换

将信号在时域与频域之间转换的方法。

3 压缩

减少数据量,方便存储和传输。

数字信号处理中的滤波器设计

FIR滤波器

时域响应仅有有限个点,稳定性好。

IIR滤波器

时域响应呈指数衰减,延时较小。

模拟/数字混合信号集成电路

1

基础理论

混合信号电路设计所需的模拟电路与数字电路基础知识。

时序逻辑电路

触发器与锁存器

用于存储时钟信号冲突消除和数 据暂存。

计数器

移位寄存器

用于计算和记录触发事件的数量。

用于数据移位操作,实现数据的 串行传输。

数字信号处理技术

数字信号处理(DSP)是用数字计算机或数字信号处理器对原始信号进行处理、分析和存储的一 种技术。它在通信、音频处理和图像处理等领域具有广泛应用。

《数字集成电路》PPT课 件

数字集成电路PPT课件大纲: 1. 什么是数字集成电路 2. 数字集成电路的分类和结构

数字电路设计的流程

1

需求分析

确定数字电路的功能与性能要求,并定义输入输出及约束条件。

2

电路设计

利用逻辑门、触发器等基本组件进行数字电路设计。

3

电路仿真

使用仿真软件验证数字电路中的电气特性和功能。

2 低功耗设计

3 增强型通信

减少功耗,延长电池寿命。

提升通信性能和速度。

2

模拟数字转换

模拟和数字信号之间的转换方法和技术。

3

功耗与噪声

如何平衡功耗Βιβλιοθήκη 噪声性能。电路模拟与仿真SPICE仿真

使用电路仿真软件模拟电路 的工作状态。

参数提取与建模

Verilog语法基础PPT教案学习

#10 num <= rega << 5 ; // num =

01_1000_0000

#10 regb <= rega << 5 ; // regb =

1000_0000

#20 num <= rega >> 3; // num =

00_0000_0001

#20 regb <= rega >> 3 ; // regb =

x

to b");

x

else $display(" a is not

equal to b");

a = 2'b1x;

z

b = 2'b1x;

0

if (a === b)

0

$display(" a is

0

identical to b");

1

else

$display(" a is not

Case等只i能d用e于nt行i为ca描l述t,o不b能"用);于RTL描述。

regc; reg val;

initial begin rega = 4'b0011; regb = 4'b1010; regc = 4'b1x10;

end initial fork

#10 val = rega == regb ; // val = 0

#20 val = rega != regc; // val = 1

第9页/共72页

注意逻辑等与 case等的差别 2‘b1x==2’b0x

值为0,因为不相等 2‘b1x==2’b1x

值为x,因为可能不 相等,也可能相等

数字集成电路基本单元与图PPT课件

1)

顾名思义,反相输出就是内部信号经反相后

输出。这个反相器除了完成反相的功能外,另一个

主要作用是提供一定的驱动能力。

第17页/共22页

焊盘输入输出单元(I/O PAD)

2)同相输出I/O PAD

2007-2008-1

同相输出实际上就是“反相+反相”,为什么不直接从内部 电路直接输出呢?主要是驱动能力问题。利用链式结构可以大大 地减小内部负荷。即内部电路驱动一个较小尺寸的反相器,这个 反相器再驱动大的反相器,在同样的内部电路驱动能力下才能获 得较大的外部驱动。P77 第18页/共22页

逻辑图输入

逻辑模拟、时序模拟

标准单元 设计系统

布局、布线 提取布线寄生参数

生成测试向量

逻辑模拟、时序模拟

转换拓扑图为掩模版版图

生产厂家

芯片制造

第14页/共22页

单元逻辑符号库 单元电路功能库

单元拓扑库 工艺、电学参数

单元版图库

数字电路标准单元库设计简介

2007-2008-1

• 库单元设计

标准单元库中的单元电路是多样化的,通常包含 上百种单元电路,每种单元的描述内容都包括: (1)逻辑功能; (2)电路结构与电学参数;

数字集成电路的基本电路的主要性能指标是: (1)工作速度(延迟时间的长短); (2)集成度(占用面积的大小); (3)功耗(消耗的电源功率); (4)噪声容限等。

2007-2008-1

第1页/共22页

CMOS基本门电路及版图实现

• CMOS反相器

(1) CMOS反相器的具体电路如图所示,这是一种典型的 CMOS电路结构,它由一个NMOS晶体管和PMOS晶体管配对 构成,两个器件的漏极相连作为输出,栅极相连作为输入。 NMOS晶体管的衬底与它的源极相连并接地,PMOS晶体管的 衬底与它的源极相连并接电源。

Verilog的讲义52页PPT

0

0x

9

9.40ns

9

01

10

10.00ns 10

11

19

19.40ns 19

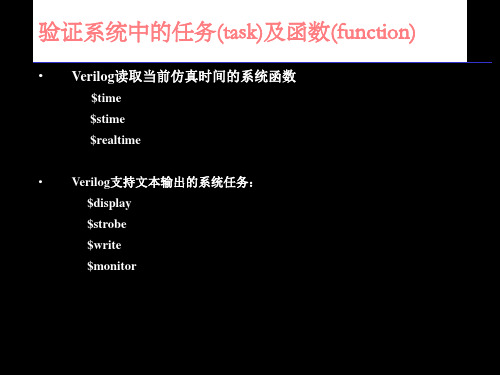

显示信号值 — $display

• $display输出参数列表中信号的当前值。 语法:$display([“ format_specifiers”,] <argument_ list>)

• $display输出时自动换行。

%m %t

hex octal decimal binary ASCII string strength module time

转义符

\t \n \\

\" \< 1-3 digit octal number> %0d

tab 换行 反斜杠 双引号 上述的ASCII表示 无前导0的十进制数

显示信号值—$write和$strobe

9.53ns

initial

10

01

begin

10 10.00ns 10

11

$display("time realtime20stime19\.t53ns

20

in1 \t o1 ");

10

$timeformat(-9, 2, "ns", 10);

$monitor("%d %t %d \t %b \t %b", $time, $realtime,

• $write与$display相同,不同的是不会自动换行。

$write($time, “%b \t %h \t %d \t %o \t”, sig1, sig2, sig3, sig4);

• $strobe与$display相同,不同的是在仿真时间前进之前的信号值。 而$display和$write立即显示信号值。也就是说$strobe显示稳定状态 信号值,而$display和$write可以显示信号的中间状态值。

《数字集成电路设计》PPT课件

② x和z值 在数字电路中,x代表不定值,z代表高阻值。 例如: 8’b1001xxxx 表示位宽8的二进制数第四位为不定值。

ⅱ. Parameter常数

在Verilog中,用parameter定义一个标识符代表一个常量,称为符 号常量。采用标识符代表一个常量可提高程序的可读性和可维护 性。其定义结构如下:

Verilog HDL程序模块包括模块名、输入输出端口说明、 内部信号说明、逻辑功能定义等几部分。

程序模板如下:

module <模块名>(<输入、输出模块列表>); /*端口描述*/ input <输入端口列表>; output <输出端口列表>;

/*内部信号说明*/ wire //nets型变量 reg //register变量 integer //常数

位运算是对两个操作数相应位进行运算操作数的位数是不变的而缩减运算时针对单个操作数先将操作数的第一位于第二位进行运算再将结果与第三位进行运算以此类推直到最后一位其结果是一个一位二进制数

数字集成电路设计

FPGA结构与设计流程

FPGA是英文Field Programmable Gate Array的缩写,即现场可编程门阵 列,是在PAL、GAL、EPLD等可编程器件的基础上进一步发展的产物。 它是作为专用集成电路(ASIC)领域中的一种半定制电路而出现的,即 解决了定制电路的不足,又克服了原有可编程器件门电路数有限的缺点。

wire[n:1] 变量名1,变量名2,……,变量名n;

ⅱ. register型变量

register型变量对应于具有状态保持作用的电路元件,如触发器,锁 存器等。它只有明确地赋值后才能对其他变量赋值,重新赋值前一 直保持原值。在设计中,此类变量必须放在块语句(always语句)中, 通过过程语句赋值。同一个register型变量只能在一个块语句中重复 赋值,而不能同时在多个块语句中重复赋值使用。register型变量包 括reg型和integer型。

《Verilog设计入门》PPT课件

精选PPT

18

3.1 组合电路的Verilog描述

3.1.2 4选1多路选择器及其case语句表述方式 6.赋值操作符 “<=”,只能用于顺序语句,不能用于assign引 导的并行语句

两种过程赋值操作: (1)阻塞式赋值“=”:语句执行结束,右侧表达式的值立刻赋给左侧 目标变量。

对于always引导的块语句中含有多条阻塞式赋值语句时,当执行某 一条语句时,其它语句不允许执行,被阻塞了,具有顺序执行的特点。

精选PPT

23

3.1 组合电路的Verilog描述

3.1.4 4选1多路选择器及其if语句描述方式

精选PPT

24

3.1 组合电路的Verilog描述

3.1.4 4选1多路选择器及其if语句描述方式 1.if_ else条件语句 if(表达式) begin 语句1;语句2;…..语句n; end else begin 语句n+1;语句n+2;…..语句n+n; end

input a,b;

output so,co;

assign so = a ^ b;

assign co = a & b;

endmodule

精选PPT

28

3.1 组合电路的Verilog描述

3.1.5 加法器及其Verilog描述

2.基于always @引导的过程语句和逻辑操作符的描述

module h_adder2(a,b,so,co);

endmodule

精选PPT

34

3.1 组合电路的Verilog描述

3.1.5 加法器及其Verilog描述 5. 全加器描述----用半加器、或门模块及例化语句描述

精选PPT

verilog数字系统设计教程PPT课件

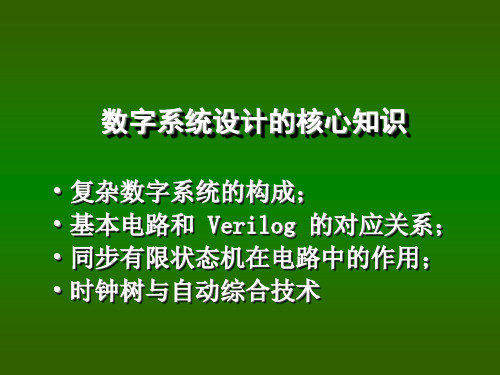

数字系统设计的核心知识

• 复杂数字系统的构成; • 基本电路和 Verilog 的对应关系; • 同步有限状态机在电路中的作用; • 时钟树与自动综合技术

数字逻辑电路的构成

- 组合逻辑:输出只是输入逻辑电平的函

数(有延时),与电路的原始状态无关。

• 时序逻辑:输出不只是输入的逻辑电

平的函数,还与电路所处的状态有关。

8 ‘ d 31

8‘d

t

out[15:0]

202

16 ‘ d

16‘ d

t

Sn 开

93

606

t 关

全局时钟网和平衡树结构

触发器1

全局时钟网络 触发器 图1 全局时钟网示意图

缓冲器

触发器n

图2 平衡树结构示意图

避免冒险和竞争

• 由于组合逻辑和布线的延迟引起

a

c

b

a

b

t

c

t

clock

避免冒险和竞争与流水线

t

t

带寄存器的八位数据通路控制器的波形

ControlSwitch

in[7]

out[7]

CLOCK

out[7]

D Q[7]

ControlSwitch

in[0]

out[0]

CLOCK

out[0]

D Q[0]

带寄存器的八位数据通路控制器的Verilog描述

`define ON 1 ‘b 1 `define OFF 1 ‘b 0 wire ControlSwitch; wire clock wire [7:0] out, in;

ControlSwitch in[7]

out[7]

…... …...

in[0]

• 复杂数字系统的构成; • 基本电路和 Verilog 的对应关系; • 同步有限状态机在电路中的作用; • 时钟树与自动综合技术

数字逻辑电路的构成

- 组合逻辑:输出只是输入逻辑电平的函

数(有延时),与电路的原始状态无关。

• 时序逻辑:输出不只是输入的逻辑电

平的函数,还与电路所处的状态有关。

8 ‘ d 31

8‘d

t

out[15:0]

202

16 ‘ d

16‘ d

t

Sn 开

93

606

t 关

全局时钟网和平衡树结构

触发器1

全局时钟网络 触发器 图1 全局时钟网示意图

缓冲器

触发器n

图2 平衡树结构示意图

避免冒险和竞争

• 由于组合逻辑和布线的延迟引起

a

c

b

a

b

t

c

t

clock

避免冒险和竞争与流水线

t

t

带寄存器的八位数据通路控制器的波形

ControlSwitch

in[7]

out[7]

CLOCK

out[7]

D Q[7]

ControlSwitch

in[0]

out[0]

CLOCK

out[0]

D Q[0]

带寄存器的八位数据通路控制器的Verilog描述

`define ON 1 ‘b 1 `define OFF 1 ‘b 0 wire ControlSwitch; wire clock wire [7:0] out, in;

ControlSwitch in[7]

out[7]

…... …...

in[0]

《数字集成电路设计》课件

加法器和减法器

深入研究加法器和减法器的原理,了解如何进行数字的加法和减法运算。

贝叶斯定理在电路设计中的应 用

介绍贝叶斯定理在电路设计中的应用场景,讲解如何利用先验知识和观测结 果进行后验概率的计算。

层级与模块化设计

层级设计

了解层级设计的原理和方法,掌握如何将复杂的电 路分解为多个模块进行设计和测试。

仿真实例

通过案例分析和实际仿真实例,加深对 电路仿真工具和流程的理解和应用。

计算机辅助设计方法与工具介 绍

介绍计算机辅助设计的基本原理和方法,以及常用的电路设计工具,包括EDA 软件和硬件描述语言。

引言

数字集成电路设计是现代信息技术的关键领域,本课程将深入探讨数字电路 设计的理论和实践,为学生打下坚实的基础。

逻辑门与布尔代数

了解常用逻辑门的工作原理,掌握布尔代数的基本概念和运算规则,为后续的电路设计奠定基础。

时序逻辑电路设计基础

1

触发器和计数器

2

深入研究各种触发器和计数器的原理和

应用,掌握时序逻辑电路的设计技巧。

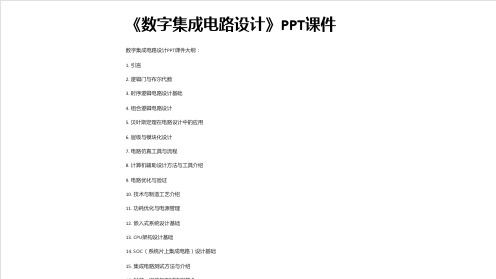

《数字集成电路设计》PPT课件

数字集成电路设计PPT课件大纲: 1. 引言 2. 逻辑门与布尔代数 3. 时序逻辑电路设计基础 4. 组合逻辑电路设计 5. 贝叶斯定理在电路设计中的应用 6. 层级与模块化设计 7. 电路仿真工具与流程 8. 计算机辅助设计方法与工具介绍 9. 电路优化与验证 10. 技术与制造工艺介绍 11. 功耗优化与电源管理 12. 嵌入式系统设计基础 13. CPU架构设计基础 14. SOC(系统片上集成电路)设计基础 15. 集成电路测试方法与介绍

模块化设计

学习模块化设计的思想和技术,掌握如何将多个模 块进行组合,实现复杂功能的集成电路设计。

深入研究加法器和减法器的原理,了解如何进行数字的加法和减法运算。

贝叶斯定理在电路设计中的应 用

介绍贝叶斯定理在电路设计中的应用场景,讲解如何利用先验知识和观测结 果进行后验概率的计算。

层级与模块化设计

层级设计

了解层级设计的原理和方法,掌握如何将复杂的电 路分解为多个模块进行设计和测试。

仿真实例

通过案例分析和实际仿真实例,加深对 电路仿真工具和流程的理解和应用。

计算机辅助设计方法与工具介 绍

介绍计算机辅助设计的基本原理和方法,以及常用的电路设计工具,包括EDA 软件和硬件描述语言。

引言

数字集成电路设计是现代信息技术的关键领域,本课程将深入探讨数字电路 设计的理论和实践,为学生打下坚实的基础。

逻辑门与布尔代数

了解常用逻辑门的工作原理,掌握布尔代数的基本概念和运算规则,为后续的电路设计奠定基础。

时序逻辑电路设计基础

1

触发器和计数器

2

深入研究各种触发器和计数器的原理和

应用,掌握时序逻辑电路的设计技巧。

《数字集成电路设计》PPT课件

数字集成电路设计PPT课件大纲: 1. 引言 2. 逻辑门与布尔代数 3. 时序逻辑电路设计基础 4. 组合逻辑电路设计 5. 贝叶斯定理在电路设计中的应用 6. 层级与模块化设计 7. 电路仿真工具与流程 8. 计算机辅助设计方法与工具介绍 9. 电路优化与验证 10. 技术与制造工艺介绍 11. 功耗优化与电源管理 12. 嵌入式系统设计基础 13. CPU架构设计基础 14. SOC(系统片上集成电路)设计基础 15. 集成电路测试方法与介绍

模块化设计

学习模块化设计的思想和技术,掌握如何将多个模 块进行组合,实现复杂功能的集成电路设计。

第四章 Verilog基本语法(一)PPT教学课件

16

2020/12/11

玉溪师范学院

参数

➢ 参数是一个常量。用parameter定义一个标识符来代表 一个常量。参数经常用于定义时延和变量的宽度。

格式: parameter param1 = const_expr1,

param2 = const_expr2,

…,

paramN = const_exprN;

assign #XOR_DELAY S=A^B;

assign #AND_DELAY C=A&B;

endmodule

19

TOP HA

2020/12/11

玉溪师范学院

参数值的模块引用

module TOP3(NewA,NewB,NewS,NewC); input NewA, NewB; output NewS,NewC; HA #(5,2) Ha1 (NewA, NewB, NewS, NewC);ut

selb

26

2020/12/11

玉溪师范学院

reg型

寄存器是数据存储单元的抽象 reg型数据常用来表示always块内的指定信号,常代表触

发器 reg型数据用initial或者always块中指定信号 reg型数据的缺省值是x。可以被赋正值或者负值。当它作

为一个表达式中的操作数时候,作为无符号数。 reg数据类型定义格式为

2.0 ; -0.1等

科学记数法,例如:

235.1e2 等于23510.0

234_12e2

等于2341200.0

实数小数通过四舍五入被隐式地转换为最相近的整数。例如:

42.446, 42.45 转换为整数42

92.5, 92.699 转换为整数93

-5.62 转换为整数-6

2020/12/11

玉溪师范学院

参数

➢ 参数是一个常量。用parameter定义一个标识符来代表 一个常量。参数经常用于定义时延和变量的宽度。

格式: parameter param1 = const_expr1,

param2 = const_expr2,

…,

paramN = const_exprN;

assign #XOR_DELAY S=A^B;

assign #AND_DELAY C=A&B;

endmodule

19

TOP HA

2020/12/11

玉溪师范学院

参数值的模块引用

module TOP3(NewA,NewB,NewS,NewC); input NewA, NewB; output NewS,NewC; HA #(5,2) Ha1 (NewA, NewB, NewS, NewC);ut

selb

26

2020/12/11

玉溪师范学院

reg型

寄存器是数据存储单元的抽象 reg型数据常用来表示always块内的指定信号,常代表触

发器 reg型数据用initial或者always块中指定信号 reg型数据的缺省值是x。可以被赋正值或者负值。当它作

为一个表达式中的操作数时候,作为无符号数。 reg数据类型定义格式为

2.0 ; -0.1等

科学记数法,例如:

235.1e2 等于23510.0

234_12e2

等于2341200.0

实数小数通过四舍五入被隐式地转换为最相近的整数。例如:

42.446, 42.45 转换为整数42

92.5, 92.699 转换为整数93

-5.62 转换为整数-6

北航夏宇闻verilog讲稿ppt语法入门.pptx

目的:

▪ 通过简单的例子了解Verilog模块的基本构成 ▪ 了解Verilog模块的层次结构和行为模块 ▪ 了解Verilog模块的测试

简单的 Verilog HDL 模块

下面先介绍几个简单的Verilog HDL程序,然后从中分 析Verilog HDL程序的特性。

例[2.1.1]: module adder ( count,sum,a,b,cin ); input [2:0] a,b; input cin; output count; output [2:0] sum; assign {count,sum}=a+b+cin; endmodule

转换为门级电路互连的电路结构(综合)。 ▪ 需要对已经转换为门级电路结构的逻辑

进行测试(门级电路仿真)。 ▪ 需要对布局布线后的电路结构进行测试。

(布局布线后仿真)。

模块的测试

激励和控 制信号

被测模块

输出响应 和验证

பைடு நூலகம்

模块的测试

测试模块常见的形式:

module t; reg …; //被测模块输入/输出变量类型定义 wire…; //被测模块输入/输出变量类型定义 initial begin …; …; …; end … …//产生测试信号 always #delay begin …; end … …//产生测试信号

endmodule

简单的 Verilog HDL 模块

上述程序例子通过另一种方法描述了一个三态 门。

在这个例子中存在着两个模块:模块trist1 调用模块 mytri 的实例元件 tri_inst。

模块 trist1 是上层模块。模块 mytri 则被称 为子模块。

通过这种结构性模块构造可构成特大型模块。

▪ 通过简单的例子了解Verilog模块的基本构成 ▪ 了解Verilog模块的层次结构和行为模块 ▪ 了解Verilog模块的测试

简单的 Verilog HDL 模块

下面先介绍几个简单的Verilog HDL程序,然后从中分 析Verilog HDL程序的特性。

例[2.1.1]: module adder ( count,sum,a,b,cin ); input [2:0] a,b; input cin; output count; output [2:0] sum; assign {count,sum}=a+b+cin; endmodule

转换为门级电路互连的电路结构(综合)。 ▪ 需要对已经转换为门级电路结构的逻辑

进行测试(门级电路仿真)。 ▪ 需要对布局布线后的电路结构进行测试。

(布局布线后仿真)。

模块的测试

激励和控 制信号

被测模块

输出响应 和验证

பைடு நூலகம்

模块的测试

测试模块常见的形式:

module t; reg …; //被测模块输入/输出变量类型定义 wire…; //被测模块输入/输出变量类型定义 initial begin …; …; …; end … …//产生测试信号 always #delay begin …; end … …//产生测试信号

endmodule

简单的 Verilog HDL 模块

上述程序例子通过另一种方法描述了一个三态 门。

在这个例子中存在着两个模块:模块trist1 调用模块 mytri 的实例元件 tri_inst。

模块 trist1 是上层模块。模块 mytri 则被称 为子模块。

通过这种结构性模块构造可构成特大型模块。

数字系统设计与verilog HDL 第7章PPT课件

1) 顺序块

由关键词begin开始,end结束 顺序块中的语句是一条一条执行,只有前面的语句执行完后, 后面的语句才能执行(内嵌套延迟和非阻塞赋值除外)。

如果语句中包含有延迟或事件控制,那么延迟总是相对于上 一条语句完成的时间的。

[例] begin

b=a; c=b;

end

[例] begin

b=a; #10 c=b;

//当信号a或信号b的值发生改变

@(posedge clock)

//当clock 的上升沿到来时

@(negedge clock)

//当clock 的下降沿到来时

@(posedge clk or negedge reset)

//当clk的上升沿到来或reset信号的下降沿到来

敏感信号列表举例(4选1数据选择器)

可综合性

√ √

√ √ √ √ √

√ √ √

7.1 过程语句

initial always 在一个模块(module)中,使用initial和always语句的 次数是不受限制的。initial语句常用于仿真中的初始化 ,initial过程块中的语句仅执行一次;always块内的语句 则是不断重复执行的。

第7章 Verilog行为语句

主要内容

◆ 过程语句(initial、always) ◆ 块语句(begin-end、fork-join) ◆ 赋值语句(assign、=、<=) ◆ 条件语句(if-else、case、casez、casex) ◆ 循环语句(for、forever、repeat、while) ◆ 编 译 指 示 语 句 ( ` define、`include、`ifdef、 `else、`endif) ◆ 任务(task)与 函数(function) ◆ 顺序执行与并发执行

由关键词begin开始,end结束 顺序块中的语句是一条一条执行,只有前面的语句执行完后, 后面的语句才能执行(内嵌套延迟和非阻塞赋值除外)。

如果语句中包含有延迟或事件控制,那么延迟总是相对于上 一条语句完成的时间的。

[例] begin

b=a; c=b;

end

[例] begin

b=a; #10 c=b;

//当信号a或信号b的值发生改变

@(posedge clock)

//当clock 的上升沿到来时

@(negedge clock)

//当clock 的下降沿到来时

@(posedge clk or negedge reset)

//当clk的上升沿到来或reset信号的下降沿到来

敏感信号列表举例(4选1数据选择器)

可综合性

√ √

√ √ √ √ √

√ √ √

7.1 过程语句

initial always 在一个模块(module)中,使用initial和always语句的 次数是不受限制的。initial语句常用于仿真中的初始化 ,initial过程块中的语句仅执行一次;always块内的语句 则是不断重复执行的。

第7章 Verilog行为语句

主要内容

◆ 过程语句(initial、always) ◆ 块语句(begin-end、fork-join) ◆ 赋值语句(assign、=、<=) ◆ 条件语句(if-else、case、casez、casex) ◆ 循环语句(for、forever、repeat、while) ◆ 编 译 指 示 语 句 ( ` define、`include、`ifdef、 `else、`endif) ◆ 任务(task)与 函数(function) ◆ 顺序执行与并发执行

VerilogHDL语言基础幻灯片PPT

Verilog HDL硬件描述语言功能

4.提供显式语言结构指定设计中的端口到端口的时 延及路径时延和设计的时序检查。

5.可采用三种不同方式或混合方式对设计建模。这 些方式包括:

➢ 行为描述方式—使用过程化结构建模; ➢ 数据流方式—使用连续赋值语句方式建模; ➢ 结构化方式—使用门和模块实例语句描述建模。

15.Verilog HDL能够监控模拟验证的执行,即模拟验 证执行过程中设计的值能够被监控和显示。这些值也能够 用于与期望值比较,在不匹配的情况下,打印报告消息。

16.在行为级描述中,Verilog HDL不仅能够在RTL级 上进行设计描述,而且能够在体系结构级描述及其算法级 行为上进行设计描述。

module 模块名(端口列表); 端口定义 input输入端口 output输出端口 inout输入/输出端口

数据类型说明 wire reg parameter、、、

逻辑功能定义 Assign连续赋值语句 Initial、Always过程语句 Function、Task调用 元件、模块调用 …...

Verilog HDL语言基础--本章概述

✓ Verilog的门级描述语句; ✓ Verilog编译指示语句; ✓ Verilog系统任务和函数; ✓ Verilog用户定义任务和函数和Verilog语言模块描 述方式。

本章内容对于初步掌握Verilog语言规则非常重 要。

--Verilog语言概述

17.能够使用门和模块实例化语句在结构级进行结构 描述。

Verilog程序结构

一个复杂电路系统的完整Verilog HDL模型是由若 干个Verilog HDL模块构成的,每一个模块又可以由若干 个子模块构成。Verilog使用大约100个预定义的关键词定 义该语言的结构。