数字电路简介,课件.

《数字电路说课》课件

数字电路设计方法

单击此处添加文本具体内容

GENERAL WORK REPORT FOR FOREIGN

硬件描述语言

硬件描述语言(HDL)是一种用于描述数字电 路和系统的语言,它能够描述电路的结构、行 为和功能。常见的硬件描述语言包括Verilog 和VHDL。

HDL的主要优点是能够在高抽象层次上描述电 路,使得设计者能够更加关注电路的逻辑和行 为,而不是具体的实现细节。这有助于提高设 计的可重用性和可维护性。

数字电路说课

单击此处添加文本具体内容

GENERAL WORK REPORT FOR FOREIGN

CONTENTS

目录

1

WORKREVIEW

数字电路概述

2

UNDERWORK

数字电路基础知识

4

FUTUREOUTLOO K

数字电路的实现与 测试

5

Байду номын сангаас

UNDERWORK

数字电路的故障诊 断与排除

3

WORKHARVEST

数字电路基础知识

单击此处添加文本具体内容

GENERAL WORK REPORT FOR FOREIGN

逻辑门电路

总结词

逻辑门电路是数字电路的基本组成部 分,用于实现逻辑运算。

详细描述

逻辑门电路有与门、或门、非门等基本 类型,它们通过输入和输出的逻辑关系 实现逻辑运算,是构成复杂数字电路的 基础。

03

随着数字电路功能的日益复杂,设计与验证的难度越来越大,

需要更高效的设计与验证方法。

数字电路的未来展望

数字电路将继续在材料、工艺、设计方 法等方面取得创新突破,推动集成电路 技术的不断发展。

阎石第五版数字电路技术课件

数字电路基础

触发器概述

触发器的分类

触发器的工作原理

触发器的应用

01

02

03

04

触发器是一种具有记忆功能的电路,能够存储二进制信息。

根据工作原理的不同,触发器可以分为RS触发器、D触发器、JK触发器和T触发器等。

触发器通过接收输入信号,根据不同的工作模式,将存储的信息保持或翻转。

触发器广泛应用于数字系统的设计和实现,如寄存器、计数器等。

详细描述

总结词

数字电路技术的发展历程

详细描述

数字电路技术自20世纪40年代诞生以来,经历了从小规模到大规模,再到超大规模集成电路的发展历程。随着半导体工艺的不断进步,数字电路技术的集成度越来越高,性能越来越强大,应用领域也越来越广泛。

总结词

数字电路技术的应用领域

详细描述

数字电路技术广泛应用于计算机、通信、控制、测量仪器、航空航天、军事等领域。在计算机领域,数字电路技术用于构建中央处理器、存储器、输入输出接口等关键部件。在通信领域,数字电路技术用于信号传输、调制解调、信道编码等。在控制领域,数字电路技术用于实现各种控制算法和控制系统。在测量仪器领域,数字电路技术用于提高测量精度和自动化程度。在航空航天和军事领域,数字电路技术用于实现高速数据处理和精确控制系统。

数字电路的分析与设计

根据逻辑函数表达式或真值表,设计实现特定逻辑功能的组合逻辑电路。

组合逻辑电路设计

根据给定的逻辑函数和触发器类型,设计实现特定功能的时序逻辑电路。

时序逻辑电路设计

利用可编程逻辑器件的资源和编程语言,设计实现各种数字电路和系统。

可编程逻辑器件设计

使用硬件描述语言(如Verilog或VHDL)进行数字电路和系统的设计和仿真。

数字电路基础课件ppt

详细描述

首先,需要明确数字逻辑功能,并选择合适的硬件描述语言(如VHDL或Verilog)编写程序。然后,使用EDA工具进行综合和布局布线,生成可编程的配置文件。最后,将配置文件下载到FPGA或CPLD中实现设计的逻辑功能。

05

数字电路的测试与调试

输入输出测试

时序测试

负载测试

仿真测试

01

02

03

04

检查电路的输入和输出是否符合设计要求,验证电路的功能是否正常。

测试电路中各个逻辑门之间的信号传输是否符合时序要求,确保电路的时序逻辑正确。

测试电路在不同负载条件下的性能表现,验证电路的稳定性和可靠性。

利用仿真软件模拟电路的工作过程,发现潜在的设计缺陷和错误。

将电路划分为若干个部分,分别进行调试,逐步排查问题所在。

总结词

应用领域与趋势

详细描述

数字电路广泛应用于计算机、通信、控制等领域。随着技术的发展,数字电路的设计和制造工艺不断进步,集成电路的规模越来越大,数字电路的应用前景十分广阔。

总结词:差异比较

详细描述:数字电路和模拟电路在处理信号的方式、电路结构和功能等方面存在显著差异。模拟电路处理的是连续变化的信号,而数字电路处理的是离散的二进制信号。此外,数字电路具有更高的抗干扰能力和稳定性。

数字电路设计基础

总结词

详细描述

总结词ቤተ መጻሕፍቲ ባይዱ

详细描述

组合逻辑电路是数字电路中最基本的电路,其设计主要基于逻辑代数和真值表。

组合逻辑电路由逻辑门电路组成,其输出仅取决于当前输入,不涉及任何记忆元件。常见的组合逻辑电路有加法器、比较器、编码器、译码器等。

组合逻辑电路的设计步骤包括定义逻辑问题、列出真值表、化简表达式、选择合适的门电路实现等。

数字电子电路第二版电子课件第一章数字电路基础

§1—1 数字信号与数字电路

4

第一章 数字电路基础

当人们在超市购物结账付款时,收银员只要把条形码扫描器对准货物上 的条形码一扫,计算机屏幕上立刻就会显示该物品的价格。这是因为条形 码经扫描器扫描后,会产生相应的“数字信号”,经计算机处理后就可以 显示为货物的名称及价格等信息,进而可刷卡付款,打印付款收据。超市 自动收款设备如图所示。

非逻辑开关电路

44

第一章 数字电路基础

图所示为非门逻辑符号。非门真值表见表。 非门的逻辑功能可概括为“有0出1,有1出0”。非门的逻辑表达式为:

该表达式读作Y等于A非。

非门真值表

非门逻辑符号

45

28

第一章 数字电路基础

几种常见的BCD码

29

第一章 数字电路基础

(1)8421BCD码 最常用的BCD码是8421BCD码。 (2)5421BCD码 5421BCD码也是一种有权码,从高位到低位分别是5、4、2、1。 (3)2421BCD码 2421BCD码也是一种有权码,从高位到低位的权分别是2、4、2、1。 (4)余3码 这是一种无权码,它是在相应的8421BCD码上加0011(3)得到的。

15

第一章 数字电路基础

用数字电路测量电动机转速的原理框图

16

第一章 数字电路基础

2. 四人抢答器 四人抢答器原理框图如图所示。

四人抢答器原理框图

17

第一章 数字电路基础

从以上两个电路的工作过程可以看出,数字电路大致包含数字信号的产 生与整形、编码、寄存、译码、显示等典型单元数字电路。

此外,为了将传感器转换而来的模拟信号转换成控制系统所需要的数字 信号,必须采用模数转换器(A/D Converter)。数字信号被处理后,通常 还要经过数模转换器(D/A Converter)恢复成模拟信号,去驱动执行元件, 如图所示。

数字电路ppt课件

目录

• 数字电路概述 • 数字电路基础知识 • 数字电路设计 • 数字电路的测试与验证 • 数字电路的优化与改进 • 数字电路的未来发展

01

数字电路概述

定义与特点

定义

数字电路是处理离散的二进制信 号的电路,这些信号通常表示为 高电平(逻辑1)和低电平(逻辑 0)。

特点

数字电路具有高可靠性、高稳定 性、易于大规模集成等优点,广 泛应用于计算机、通信、控制等 领域。

光数字电路的发展需要解决光子器件 的集成度和可靠性问题,以及光信号 的稳定性和可控制性问题。

光数字电路利用光波导、光调制器和 光探测器等光子器件实现信号的传输 和处理,可应用于高速通信、并行计 算等领域。

THANKS

感谢观看

确保其正常工作。

故障诊断

故障定位

通过测试和分析,确定故障发生的位置和原 因。

故障排除

针对故障模式,采取相应的措施排除故障, 恢复数字电路的正常工作。

故障模式识别

根据故障的表现形式,识别出故障的模式。

故障预防

通过分析和总结,预防类似故障的再次发生 。

可靠性分析

可靠性评估

对数字电路的可靠性进行评估,包括 平均无故障时间、失效率等指标。

02

数字电路基础知识

逻辑门电路

与门

实现逻辑与运算,当输入都为 高电平时,输出为高电平。

或门

实现逻辑或运算,当输入中至 少有一个为高电平时,输出为 高电平。

非门

实现逻辑非运算,当输入为高 电平时,输出为低电平;当输 入为低电平时,输出为高电平 。

异或门

当两个输入不同时,输出为高 电平;当两个输入相同时,输

可重构电路设计

《数字电路业务介绍》课件

随着环保意识的提高,数字电路业务 需要满足更低的功耗需求,以降低能 源消耗和减少环境污染。

VS

解决方案:采用低功耗的数字电路设 计,优化电源管理和节能技术,降低 数字电路的功耗。

安全与可靠性问题

数字电路业务涉及到信息安全和产品可靠性等问题,需要采取有效的安全措施和可靠性保障。

解决方案:加强安全防护和可靠性设计,采用加密技术和故障检测与恢复等技术,提高数字电路的安 全性和可靠性。

工业控制领域

数字电路在工业控制领域中广泛应用 于自动化生产线的控制、监测和调节 等方面。

数字电路能够实现精确的控制和快速 的响应,提高生产效率和产品质量。

智能家居领域

数字电路在智能家居领域中应用于智能家电、智能照明、智 能安防等方面的控制和管理。

数字电路能够实现家庭设备的互联互通,提高家居生活的便 利性和舒适性。

《数字电路业务介绍》 ppt课件

contents

目录

• 数字电路业务概述 • 数字电路业务的核心技术 • 数字电路的应用领域 • 数字电路业务的挑战与解决方案 • 数字电路业务的市场前景

01

数字电路业务概述

定义与特点

安全性

数字电路采用加密技术,保障了通信内容 的安全性。

定义

数字电路业务是一种基于数字技术的电路 交换业务,通过数字信号传输实现语音、 数据和多媒体通信。

医疗电子领域

数字电路在医疗电子领域中应用于医疗设备的数字化改造 和智能化升级,如医学影像设备、诊断仪器等。

数字电路能够提高医疗设备的准确性和可靠性,为医疗技 术的发展提供有力支持。

04

数字电路业务的挑战与解决方案

技术更新换代快

数字电路技术发展迅速,不断有新技术涌现,使得数字电路业务面临不断更新的 挑战。

数字电路基础(全部课件)

则该数的权展开式为: (M)2 = an-1×Nn-1 + an-2 ×Nn-2 + … +a1×N1+ a0 ×N0

+a-1 ×N-1+a-2 ×N-2+… +a-m×N-m ③由权展开式很容易将一个N进制数转换为十进制数。

事物往往存在两种对立的状态,在逻辑代数中可以抽 象地表示为 0 和 1 ,称为逻辑0状态和逻辑1状态。

逻辑代数中的变量称为逻辑变量,用大写字母表示。 逻辑变量的取值只有两种,即逻辑0和逻辑1,0 和 1 称为 逻辑常量,并不表示数量的大小,而是表示两种对立的逻 辑状态。

1.3.1 基本逻辑运算

1、与逻辑(与运算)

2、二进制

数码为:0、1;基数是2。 运算规律:逢二进一,即:1+1=10。 二进制数的权展开式: 如:(101.01)2= 1×22 +0×21+1×20+0×2-1+1 ×2

-2 =(5.25)10

各数位的权是2的幂

二进制数只有0和1两个数码,它的每一位都可以用电子元 件来实现,且运算规则简单,相应的运算电路也容易实现。

(3)对组成数字电路的元器件的精度要求不高, 只要在工作时能够可靠地区分0和1两种状态即可。

2、数字电路的分类

(1)按集成度分类:数字电路可分为小规模(SSI,每 片数十器件)、中规模(MSI,每片数百器件)、大规模 (LSI,每片数千器件)和超大规模(VLSI,每片器件数 目大于1万)数字集成电路。集成电路从应用的角度又可 分为通用型和专用型两大类型。

A

B

B

E

Y

E

Y

A接通、B断开,灯亮。

A、B都接通,灯亮。

数字逻辑电路大全PPT课件(2024版)

第6页/共48页

Rb1 4kΩ

Rc 2 1.6kΩ

Vc 2

1

+VCC( +5V) Rc4 130Ω

3

T2 4

1

3

A

31

2T2

D Vo

B

T1

C

Ve 2

1

3

2T 3

Re2

1kΩ

输入级

中间级

输出级

第7页/共48页

2.TTL与非门的逻辑关系

(1)输入全为高电平3.6V时。

T2、T3导通,VB1=0.7×3=2.1(V ),

列。 6 . 74AS 系 列 —— 为 先 进 肖 特 基 系

列, 它是74S系列的后继产品。 7.74ALS系列——为先进低 功耗肖特基系列, 是74LS系列的后继产品。

第30页/共48页

2.3

一、 NMOS门电路 1.NMOS非门

MOS逻辑门电路

VDD (+12V)

VDD (+12V)

VDD (+12V)

0.4V

高 电 平 噪 声 容 限 第1V5页NH/共=48V页OH ( min ) - VON = 2.4V-2.0V =

四、TTL与非门的带负载能力

1.输入低电平电流IIL与输入高电平电流IIH (1)输入低电平电流IIL——是指当门电路的输入端

接低电平时,从门电路输入端流出的电流。

& Vo G0

呈 现 高 阻 , 称 为 高 阻 态 , 或 禁 止 态+V。CC

Rc2

Rc4

Rb1

Vc2 1

3

T2 4

A

&

B

L

EN

数字电路经典课件 (20)

1 74LS163

CP

74LS138

LD

STA

Y0

Y0

CR

STB

Y1

Y1

CTT

STC

Y2

Y2

CTP

Y3

Y3

Y4

Y4

Q0

Y5

Y5

D0

Q1

Y6

Y6

D1

Q2

Y7

Y7

D2

Q3

D3

CO

计数器

译码器

16输出脉冲分配器

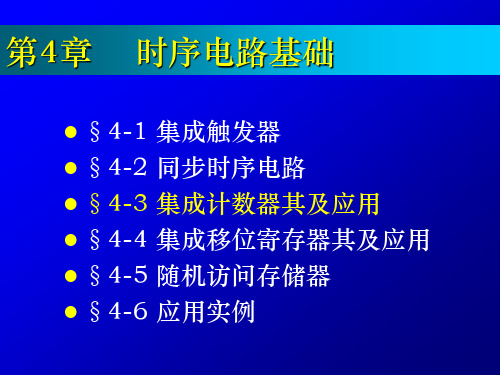

§4-3 集成计数器其及应用

§4-3-1 集成计数器74163 §4-3-2 计数器74163的扩展 §4-3-3 集成计数器的应用举例 §4-3-4 74192 双时钟模10加/减计数器

大的状态返回置数,预

0100

置数输入端为最小状态

0101

值。

N=最大状态 − 预置数+1

0110

0111

例3:用预置端和进位端构成模6计数器

用同步置数端时,N = 16-预置数

§4-3 集成计数器其及应用

§4-3-1 集成计数器74163 §4-3-2 计数器74163的扩展 §4-3-3 集成计数器的应用举例 §4-3-4 74192 双时钟模10加/减计数器

例2:用计数器和数据选择器构成序列信号发生器

设计长度为P的序列信号发生器,可以先设计一个 模P的计数器,再加一个数据选择器,计数器的输出接 在MUX的地址端,序列数据接在MUX的数据端。

例2:01100011序列信号发生器

例3:设计一个011001序列信号发生器

3. 构成脉冲分配器

在数字电路中,能按一定时间、一定顺序轮流输

例5:74192构成的模6计数器的设计(用预置端)

数字电路全套课件

4

5 6 7

4

5 6 7

12

13 14 15

1100

1101 1110 1111

14

15 16 17

C

D E F

(二) 不同数制间的转换

1. 各种进制转化为十进制 (1101.11)2=1x23+1x22+0x21+1x20+1x2-1+1x2-2 =8+4+0+1+0.5+0.25=(13.75)10 (132.04)8=1x82+3x81+2x80+0x8-1+4x8-2 =64+24+2+0. 5=(90.0625)10 (2C5 )16=2X162+12X161+5X160 =512+192+5=(709)10

(xxx)2 或 (xxx)B

数码:0、1 例如 (1011.11)2 或 (1011.11)B 进位规律:逢二进一,借一当二 例如 0 + 1 = 1 1 + 1 = 10 11 + 1 = 100 10 – 1 = 1

权:2i 基数:2 系数:0、1

按权展开式表示 (1011.11)2 = 1×23 + 0×22 + 1×21 + 1×20 + 1×2-1 + 1×2-2 将按权展开式按照十进制规律相加,即得对应十进制数。 (1011.11)2 = 1×23 + 0×22 + 1×21 + 1×20 + 1×2-1 + 1×2-2 = 8 + 0 + 2 + 1 + 0.5 + 0.25 = 11.75 (1011.11)2 = (11.75)10

数字电路数字量输入输出课件

形状

7段码 .gfedcba

符号

形状

7段码 .gfedcba

’0’

00111111

’8’

01111111

’1’

00000110

’9’

01100111

’2’

01011011

’A’

01110111

’3’

01001111

’B’

01111100

’4’

01100110

’C’

00111001

’5’

01101101

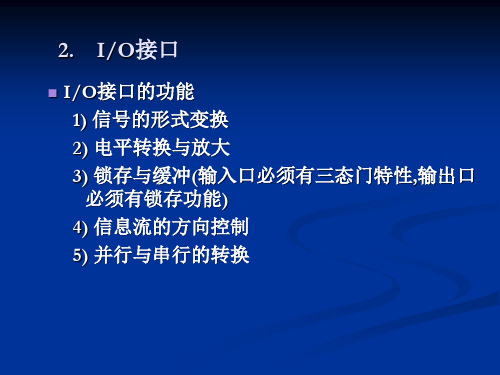

5.2.3 总线信号与接口的连接

数据信号的连接 地址信号的连接:译码信号 控制信号的连接

例1、简单的输入接口举例

常用芯片:74LS244 应用例子:开关接口

&

≥1

≥1

+5V

例2、 简单的输出接口举例

输出端口应具备锁存器功能. 常用芯片:74LS273 74LS374(具有三态输出的锁存器) 应用例子:发光二极管接口

a b c d e f g DP

7406

反相器

74LS273

Rx8

≥1

74LS138

D0~D7

IOW#

IOR#

Y0

Y1

F0H = 0000 0000 1111 0000 F1H = 0000 0000 1111 0001

&

≥1

A7~A4

A15~A8

A3

A2

A1

A0

D0

D1

D2

查询方式传送

适用于外设并不总是准备好,而且对传送速率、传送效率要求不高的场合。 CPU在与外设交换数据前必须询问外设状态—— “你准备好没有?” 对外设的要求:应提供设备状态信息 对接口的要求:需要提供状态端口 优点:软件比较简单 缺点:CPU效率低,数据传送的实时性差,速度较慢

数字电路经典课件 (11)

一、集成电路的生产工艺

TTL:晶体管-晶体管逻辑 ,速度快。 (标准,S,LS,AS,ALS,F)

MOS:金属-氧化物-半导体逻辑,功耗低。 (PMOS,NMOS,CMOS) (HC,AHC,AC,HCT,ACT,AHCT,LV,LVC)

ECL: 发射极偶合逻辑,速度更快。 系列:74系列、54系列、4000系列等。 命名:如SN74LS00。

3.1.2 三极管的开关特性

三极管的基本结构是两个反向连结的PN结面,可有 pnp和npn 两种组合。

三个接出来的端点依序称为发射极(emitter,E)、基 极(base,B)和集电极(collector,C)。

pnp与npn三极管的电路符号:

✓ 发射极特别被标出,箭号所指的极为n型半导体, 和二极管 的符号一致。

4、平均传输延时时间— 输出由高变低、由低变高的平均延时时间

tr:上升时间; tf:下降时间; tpdL: 输出由高电平到低电平的传输延迟时间;

tpdH: 输出由低电平到高电平的传输延迟时间。

vi

VIM 0.5VIM

vi 5V

&

vo

vo

tpdL

0.9VOM 0.5VOM 0.1VOM

tf

t tpdH

扇出系数:可以驱动同类门的最大个数, IOH/IIH 或者IOL/IIL,

74LS00: IOH=400uA

IIH=20uA

IOL=8mA

IIL=0.4mA

注意: 1. 前级IOL不小于后级IIL之和, 前级IOH不小于后级IIH之和

2. 一般门电路, IOH/IIH 与IOL/IIL可能不同,扇 出系数为其中较小的一个。

传输门

三态门逻辑符号

数字电路完整课件讲解

2.1.4 MOS 管的开关特性 1、 MOS管的工作原理

③ NMOS、PMOS管的符号:

NMOS加正电源,uGS>0,uDS>0 PMOS加正电源,uGS<0,uDS<0

2.1.4 MOS 管的开关特性

2、NMOS管的几个主要参数

①开启电压VT:形成导电沟道所需的最小电压uGS

VTN=+2V,VTP=-2V ②跨导gm:gm表明MOS管的输入电压控制电流的能力。

• 栅极电容的电荷不易泄漏掉,容易由于外界静电感 应积累电荷,在栅极产生较高的电压,造成栅极氧 化层击穿,损坏MOS管。

2.1.4 MOS 管的开关特性

• 在数字集成电路中,一般都 在输入端加上保护电路。如图 在GS间加保护二极管DZ,当静 电压超过一定限度后,二极管 击穿导通,使静电荷泄放保护 氧化层不被击穿。

例2:与门:Y=AB 先画出与非,再非。

三、 CMOS 传输门、三态门和漏极开路门

(一)CMOS传输(TG 门 — Transmission Gate)

门1. 电路组成:

C TP

uI / uO

+VDD

uO / uI

uI / uO

C

TG

uO / uI

TN

C

VSS

2. 工作原理:

导关通断电电阻阻小大 C (几( ≥百1欧09姆))

• 输入端电压高于VDD+uDF或低于-uDF 输入电容。 时,保护二极管就会导通,TN、TP栅极 电位限制在-uDF~VDD+uDF之间。

(二)CMOS反相器的静态特

性1、输入特性:iI f (uI )

• 正常工作电压情况下,由于 MOS管输入电阻很高,iI≈0;

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

第11章数字电路11.1 数字电路的基本知识11.2 逻辑门电路11.3 触发器11.4 计数器11.5 寄存器11.6 译码器与显示器件11.7 集成555定时器及应用11.8 数/模与模/数转换器的概念11.1 数字电路的基本知识11.1.1 数字电路概述电信号分为模拟信号与数字信号两类。

模拟信号:时间上和幅度上都是连续变化的信号。

数字信号:时间和幅度上都是离散的信号。

模拟电路:处理模拟信号的电路;数字电路:研究数字信号的产生、变换、传输、储存、控制、运算等的电路。

数字电路的输出与输入间有一定的逻辑关系,因此数字电路也称为逻辑电路。

数字电路分类组合逻辑电路:电路任意时刻的输出信号仅取决于该时刻的输入信号,与信号作用前电路原来的状态无关。

时序逻辑电路:电路任意时刻的输出信号不仅取决于该时刻的输入信号,而且还取决于信号作用前电路原来的状态。

即,时序逻辑电路具有记忆。

数字电路的特点信号为二值量信号。

可用电平的高低或脉冲的有无来表示,因此基本单元电路结构简单、抗干扰能力强。

11.1.2 数制和码制1. 数制常用的数值有十进制和二进制。

人们日常生活中使用十进制;数字电路中使用二进制。

(1) 十进制有 0 ~ 9 十个数码,基数为十,“逢十进一”;低位到高位各位的“权”依次为 100、101、102 、···;[例]:[1851]10 = 1×103 + 8×102 + 5×101 + 1×100任意一个十进制数可展开为: ∑=110-ii K D(2) 二进制有 0 、1 两个数码,基数为二,“逢二进一”;低位到高位各位的“权”依次为 20、21、22 、···例:[1001]2 = 1 ⨯ 23 + 0 ⨯ 22 + 0 ⨯ 21 + 1 ⨯ 20任意一个二进制正整数可展开为: ∑=1-2i i K D (3) 二-十进制数的相互转换二进制数转换为十进制数:按权展开后相加。

例:[1001]2 = 1 ⨯ 23 + 0 ⨯ 22 + 0 ⨯ 21 + 1 ⨯ 20 = 8 + 0 + 0 + 1 = [ 9 ]10十进制数转换为二进制数:除 2 取余,倒排列。

例:[13]10 = 13 2 2 2 2 6 ······ 余1······ 余03 1 0 ······ 余1 ······ 余1 [1101 ]22. 码制编码:用二进制数码表示文字、符号或其它特定对象的过程。

BCD码:用 4 位二进制数码表示 1 位十进制数码。

8421 BCD码编码表十进制数码二进制数码位权8 位权4 位权2 位权10 1 2 3 4 5 6 7 8 9 011111111111111111.2 逻辑门电路逻辑门:能实现一定因果逻辑关系的单元电路。

三种基本逻辑关系:与逻辑、或逻辑、非逻辑。

三种基本逻辑门电路:与门、或门、非门。

11.2.1 与逻辑及与门1. 与逻辑决定一事件的所有条件都具备时,该事件才会发生。

[例] 只有当开关A与B都闭合,灯Y才会亮。

若以“1” 表示灯亮、开关闭合;“0” 表示灯暗、开关断开,可得到逻辑真值表。

真值表:将输入变量可能的取值组合状态及其对应的输出状态列成的表格。

与门真值表A B Y0 0 0 0 1 0 111 1与逻辑表达式: Y = A · B结论:与逻辑关系为全 1 出 1,有 0 出 0 2. 与门 实现与逻辑运算的电路与门符号:与门电路在不同输入逻辑变量时对应输出的逻辑函数波形图:A BY11.2.2 或逻辑及或门2. 或逻辑在决定一事件的几个条件中,只要有一个或几个条件具备,该事件就会发生。

只要开关A 与B 有一个闭合,灯Y 就会亮。

[例]:或门真值表A B Y0 0 00 1 11 0 1 1 1 1或逻辑表达式:Y = A + B结论:或逻辑关系为全 0 出0,有 1 出 1。

或门符号:或门实现或逻辑运算的电路11.2.3 非逻辑及非门非逻辑就是否定。

[例]:开关断开时,灯亮;闭合时反而不亮。

非门真值表A Y0 11 0 非逻辑表达式:非门符号:Y非门实现非逻辑运算的电路。

11.2.4 复合逻辑门1. 与非门符号与非门真值表A B Y 0 0 1 0 1 1 1 0 1 11逻辑表达式: ABY 集成与非门 T4000(74LS00)的外引线排列图:与非逻辑关系:有 0 出 1,全 1 出 0。

2. 或非门符号或非门真值表A B Y0 0 10 1 01 0 0 1 1 0 逻辑表达式:BAY+=或非逻辑关系:有 1 出 0,全 0 出 1。

11.3 触发器触发器:具有记忆功能的逻辑部件,有两种相反的稳定输出状态。

11.3.1 R -S 触发器1. 基本 R -S 触发器(1) 电路组成将两个集成与非门的输出端和输入端交叉反馈相接。

;D D S R 、两个输入端(2) 符号逻辑状态相反、两个输出端Q Q”状态。

时,称触发器为“、当”状态;时,称触发器为“、当0 10 1 01 ====Q Q Q Q 定义 Q 端的状态为触发器的状态。

(3) 逻辑功能, 0 , 1 D D 时当==S R 触发器状态为 1; , 1 , 0 D D 时当==S R 触发器状态为 0; ,1 , 1 D D 时当==S R 触发器保持原状态不变;触发器的状态不定。

信号同时撤除后、当这是不稳定状态时当 , , , 1 , 0 , 0 D D D D R S Q Q S R ====D R D S 1 0 1 110 DRDS 1 1 11 D R DS 1 1 D R D S 0 0(4) 逻辑状态表应禁止不定 0 0 保 持 原状态 1 1 置 1 1 0 1 置 0 0 1 0 逻辑功能 Q D R D S (5) 结论基本 R -S 触发器为负脉冲触发有效。

因而逻辑符号中输入端靠近方框处有小圆圈。

负脉冲触发2. 同步 R -S 触发器触发器的翻转时刻受时钟脉冲 CP 控制,翻转到什么状态,仍由输入 R 、S 决定。

(1) 电路组成一个基本 R -S 触发器; 一个控制门(G 3、G 4)不用时接高电平或悬空端直接置端直接置, 1 , 0 D D S R(2) 逻辑符号CP 端及输入端R、S 无小圆圈――正脉冲触发有效。

(3) 工作原理CP = 0 时,G3、G4 输出为 1,触发器维持原态;CP = 1 时,触发器状态由R、S 决定(见逻辑状态表)。

(4) 逻辑状态表(5) 工作波形CP R S Q 逻辑功能0 任意任意原状态保持1 0 0 原状态保持1 0 1 1 置11 1 0 0 置01 1 1 不定应禁止存在问题:在CP = 1 期间,如果输入信号发生多次变化,触发器的输出可能发生多次翻转——空翻。

11.3.2 主从 J-K 触发器1. 电路组成 3. 工作原理当 CP = 1 时,主触发器的状态由输入信号 J 、K 和触发器的原状态决定;由两个同步 R-S 触发器构成,从触发器的状态为触发器的状态。

触发器的状态不变。

因而主从 不变 原状态从触发器被封锁而保持 此时 , , 0 , K J CP - 2. 逻辑符号当 CP 由 1 变为 0 时,主触发器被封锁,状态不变;触发器状态一致。

主从 的状态传送到从触发器 主触发器将保存从触发器打开 此时 J-K CP , , , 1 , 4. 结论主从 J -K 触发器在 CP = 1时,接收输入信号;在 CP 下降沿输出相应的状态。

符号中 CP 端的小圆圈表示同步脉冲的下降沿触发。

下降沿触发5. 逻辑状态表6. 工作波形翻转11置 1 00 1 置0 1 1 0 保持原状态逻辑功能 Q K J Q当 J = K = 1 时,触发器工作在计数状态。

符号:CP 处不加小圆圈,表明触发器是由CP 脉冲的上升沿触发。

CP 脉冲上升沿到来后触发器的状态,等于上升沿到来之前输入端D 的状态。

工作波形:逻辑状态表:D Q 逻辑功能0 0 置 01 1 置 1符号: 由 CP 脉冲的下降沿触发。

T 等于 0 时,触发器保持原状态不变;T 等于 1 时,触发器翻转。

逻辑状态表:工作波形:翻转1 保持 原状态 0 逻辑功能 Q T Q11.4 计数器计数器:对输入脉冲的个数进行计数的电路。

由具有记忆功能的触发器组成。

一个触发器可以计 1 位二进制数,n个触发器可计n位二进制数。

同步计数器:计数脉冲同时加到计数器中各个触发器的时钟脉冲端;异步计数器:计数脉冲不是同时加到计数器中各个触发器的时钟脉冲端,各触发器翻转有先有后。

11.4.1 异步二进制加法计数器工作原理: 触发器 J 、K 端悬空,工作于计数状态。

计数脉冲作为触发器 FF1 的 CP 脉冲,每当 CP 脉冲下降沿到来时,触发器状态翻转一次;每当 Q 1下降沿到来时,触发器 FF2 翻转一次;每当 Q 2下降沿到来时,触发器 FF3 翻转一次;发器初始状态均为零。

触端加一清零负脉冲,各D可见:各触发器的状态,代表了输入计数脉冲的个数。

10 1 00 1 2 3 01 1 7 1 1 1 80 0 3 位二进制计数器状态表计数脉冲 触发器状态 十进制数CPQ 3 Q 2 Q 10 0 0 0 0 10 0 1 1 2 0 1 0 2 3 0 1 1 3 4 1 0 0 4 51 0 1 5 6 1 1 0 6 7 11178 0 0 0 0由波形可见,Q 1 端的波形为二分频; Q 2 端的波形为四分频等。

所以计数器也可作为分频器。

11.4.2 十进制计数器十进制有十个状态,需用四个触发器。

采用 8421BCD 编码方式,十进制加法计数器的状态表如下:十进制计数器状态表计数脉冲触发器状态十进制数 CP Q 4 Q 3 Q 2 Q 1 0 0 0 0 0 0 1 0 0 0 1 1 2 0 0 1 0 2 3 0 0 1 1 3 4 0 1 0 0 4 51156 0 1 1 0 67 0 1 1 1 78 1 0 0 0 0 911910 0 0 0 0 0使用集成计数器可以方便地构成任意进制计数器。

11.4.3 集成计数器集成计数器种类繁多,功能完善,可扩展性、通用性较强。

T210 是集成异步二-五-十进制计数器。

外引线排列图逻辑符号R 0(1)、R 0(2)是复位端;S 9(1)、S 9(2)是置位端;Q 3、Q 2、Q 1、Q 0 是输出端;CP 0、CP 1 是脉冲输入端;U CC 接 + 5 V 电源;GND 接地。