组成试卷A卷_答案

2022年南昌大学软件工程专业《计算机组成原理》科目期末试卷A(有答案)

2022年南昌大学软件工程专业《计算机组成原理》科目期末试卷A(有答案)一、选择题1、主存储器主要性能指标有()。

1.存储周期Ⅱ.存储容量Ⅲ.存取时间Ⅳ.存储器带宽A.I、IⅡB.I、IⅡ、IVC. I、Ⅲ、lVD.全部都是2、某机器字长32位,存储容量64MB,若按字编址,它的寻址范围是()。

A.8MB.16MBC.16MD.8MB3、完整的计算机系统应该包括()。

A.运算器、存储器、控制器B.外部设备和主机C.主机和应用程序D.主机、外部设备、配套的软件系统4、下列关于计算机操作的单位时间的关系中,正确的是()。

A.时钟周期>指令周期>CPU周期B.指令周期CPU周期>时钟周期C.CPU周期>指令周期>时钟周期D.CPU周期>时钟周期>指令周期5、()可区分存储单元中在放的是指令还是数据。

A.存储器B.运算C.用户D.控制器6、某总线共有88根信号线,其中数据总线为32根,地址总线为20根,控制总线36根,总线工作频率为66MHz、则总线宽度为(),传输速率为()A.32bit 264MB/sB.20bit 254MB/sC.20bit 264MB/sD.32bit 254MB/s7、总线的半同步通信方式是()。

A.既不采用时钟信号,也不采用握手信号B.只采用时钟信号,不采用握手信号C.不采用时钟信号,只采用握手信号D.既采用时钟信号,又采用握手信号8、某计算机的指令流水线由4个功能段组成,指令流经各功能段的时间(忽略各功能段之间的缓存时间)分别为90ns,80ns、70ns和60ns,则该计算机的CPU时钟周期至少是)()。

A.90nsB.80nsC.70nsD.60ns9、同步控制是()。

A.只适用于CPU控制的方式B.由统一时序信号控制的方式C.所有指令执行时问都相同的方式D.不强调统一时序信号控制的方式10、下列选项中,用于设备和设备控制器(I/O接口)之间互连的接口标准是()。

消防设施操作员之消防设备中级技能能力测试试卷A卷附答案

2023年消防设施操作员之消防设备中级技能能力测试试卷A卷附答案单选题(共100题)1、消防设备末端配电装置的清扫和检修一般(),其内容除清扫和摇测绝缘外,还应检查各部连接点和接地处的紧固状况。

A.每月至少一次B.每季至少一次C.每半年至少一次D.每年至少一次【答案】 D2、防火阀安装在什么位置。

A.防火阀安装在机械排烟系统管道上B.防火阀安装在防排烟系统管道上C.防火阀安装在机械正压送风系统管道上D.防火阀安装在管道上【答案】 C3、以下不属于防火门自检的有()。

A.防火门的释放器是否灵敏B.防火门下是否有堆积物,影响开启C.看防火门关闭时,是否按照顺序进行关闭D.防火门关闭后的密封性E.分别触发两个相关的火灾探测器,查看电动防火门的关闭效果及反馈信号【答案】 B4、下列关于收到报警按钮的安装说法正确的是()。

A.每个防火分区应至少设置一只,应设在明显和便于操作的部位B.从一个防火分区内的任何位置到最邻近的手动火灾报警按钮的步行距离不应大于25mC.手动火灾报警按钮宜设置在疏散通道或出入口处D.当采用壁挂方式安装时,其底边距地高度宜为1.3-1.5m,且应有明显标识【答案】 A5、火灾自动报警系统的触发器件包括:火灾探测器和()。

A.火灾显示盘B.手动报警按钮C.火灾警报器D.声光显示器【答案】 B6、钢制双片防火卷帘的耐火极限是()。

A.不小于2hB.不小于3hC.不小于4hD.36-72h【答案】 A7、火灾报警控制器在自动联动状态下,对信息特征描述不正确的是()。

A.启动灯亮B.液晶显示启动设备参数和部位C.记录启动时间D.记录启动设备总数【答案】 B8、二氧化碳灭火器喷嘴形状是()。

A.大喇叭口B.小喇叭口C.尖嘴【答案】 A9、对灭火器进行水压试验压力应按灭火器铭牌标志上规定的水压试验压力值进行,保压()min。

A.1B.2C.3D.4【答案】 A10、下列不属于电气火灾监控器保养项目的是()。

2022年武汉轻工大学计算机科学与技术专业《计算机组成原理》科目期末试卷A(有答案)

2022年武汉轻工大学计算机科学与技术专业《计算机组成原理》科目期末试卷A(有答案)一、选择题1、Cache用组相联映射,一块大小为128B,Cache共64块,4块分一组,主存有4096块,主存地址共需()位。

A.19B.18C.17D.162、某C语言程序段如下:for(i=0;i<9;i++){temp=1;for(j=0;j<=i;j++)temp+=a[J];sum+=temp;}下列关于数组a的访问局部性的描述中,正确的是()。

A.时间局部性和空间局部性皆有B.无时间局部性,有空间局部性C.有时间局部性,无空间局部性D.时间局部性和空间局部性皆无3、关于浮点数在IEEE754标准中的规定,下列说法中错误的是()。

I.浮点数可以表示正无穷大和负无穷大两个值Ⅱ.如果需要,也允许使用非格式化的浮点数Ⅲ.对任何形式的浮点数都要求使用隐藏位技术IⅣ.对32位浮点数的阶码采用了偏移值为l27的移码表示,尾数用原码表示4、下列关于各种移位的说法中正确的是()。

I.假设机器数采用反码表示,当机器数为负时,左移时最高数位丢0,结果出错;右移时最低数位丢0,影响精度Ⅱ在算术移位的情况下,补码左移的前提条件是其原最高有效位与原符号位要相同Ⅲ.在算术移位的情况下,双符号位的移位操作中只有低符号位需要参加移位操作()A. Ⅲ、ⅡB.只有ⅡC.只有ⅢD.全错5、下列为8位移码机器数[x]移,当求[-x]移时,()将会发生溢出。

A.11111111B.00000000C.10000000D.011l1l116、关于同步控制说法正确的是()。

A.采用握手信号B.由统一时序电路控制的方式C.允许速度差别较大的设备一起接入工作D.B和C7、在集中式总线控制中,响应时间最快的是()。

A.链式查询B.计数器定时查询C.独立请求D.分组链式查询8、某计算机主频为1.2GHz,其指令分为4类,它们在基准程序中所占比例及CPI如下表所示。

大学英语(四)A-卷【考试试卷答案】

大学英语(四)课程考试A 卷 适用于;考试日期:; 试卷所需时间:120分钟 闭卷;试卷A 总分:100分。

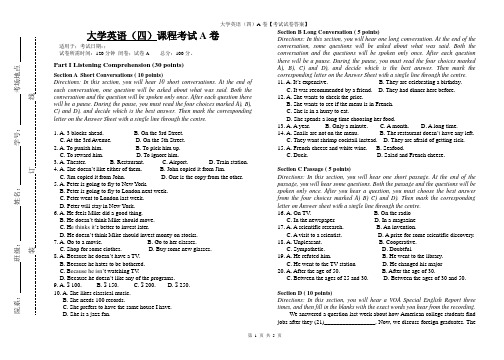

Part I Listening Comprehension (30 points) Section A Short Conversations ( 10 points) Directions: In this section, you will hear 10 short conversations. At the end of each conversation, one question will be asked about what was said. Both the conversation and the question will be spoken only once. After each question there will be a pause. During the pause, you must read the four choices marked A), B), C) and D), and decide which is the best answer. Then mark the corresponding letter on the Answer Sheet with a single line through the centre. 1. A. 3 blocks ahead. B. On the 3rd Street. C. At the 3rd Avenue. D. On the 5th Street. 2. A. To punish him. B. To pick him up. C. To reward him. D. To ignore him. 3. A. Theater. B. Restaurant. C. Airport. D. Train station. 4. A. She doesn ’t like either of them. B. John copied it from Jim. C. Jim copied it from John. D. One is the copy from the other. 5. A. Peter is going to fly to New York. B. Peter is going to fly to London next week. C. Peter went to London last week. D. Peter will stay in New York. 6. A. He feels Mike did a good thing. B. He doesn ’t think Mike should move. C. H e thinks it’s better to invest later. D. He doesn ’t think Mike should invest money on stocks. 7. A. Go to a movie. B. Go to her classes. C. Shop for some clothes. D. Buy some new glasses. 8. A. Because he doesn ’t have a TV . B. Because he hates to be bothered. C. B ecause he isn’t watching TV . D. Because he doesn ’t like any of the programs. 9. A. $ 100. B. $ 150. C. $ 200. D. $ 250. 10. A. She likes classical music. B. She needs 100 records. C. She prefers to have the same house I have. D. She is a jazz fan. Section B Long Conversation ( 5 points) Directions: In this section, you will hear one long conversation. At the end of the conversation, some questions will be asked about what was said. Both the conversation and the questions will be spoken only once. After each question there will be a pause. During the pause, you must read the four choices marked A), B), C) and D), and decide which is the best answer. Then mark the corresponding letter on the Answer Sheet with a single line through the centre. 11. A. It ’s expensive. B. They are celebrating a birthday. C. It was recommended by a friend. D. They had dinner here before. 12. A. She wants to check the price. B. She wants to see if the menu is in French. C. She is in a hurry to eat. D. She spends a long time choosing her food. 13. A. A year. B. Only a minute. C. A month. D. A long time. 14. A. Snails are not on the menu. B. The restaurant doesn ’t have any left. C. They want shrimp cocktail instead. D. They are afraid of getting sick. 15. A. French cheese and white wine. B. Seafood. C. Duck. D. Salad and French cheese. Section C Passage ( 5 points) Directions: In this section, you will hear one short passage. At the end of the passage, you will hear some questions. Both the passage and the questions will be spoken only once. After you hear a question, you must choose the best answer from the four choices marked A) B) C) and D). Then mark the corresponding letter on Answer sheet with a single line through the centre. 16. A. On TV . B. On the radio C. In the newspaper. D. In a magazine 17. A. A scientific research. B. An invention. C. A visit to a scientist. D. A prize for some scientific discovery.18. A. Unpleasant. B. Cooperative. C. Sympathetic. D. Doubtful. 19. A. He refuted him. B. He went to the library. C. He went to the TV station D. He changed his major 20. A. After the age of 50. B. After the age of 30. C. Between the ages of 25 and 30. D. Between the ages of 30 and 50. Section D ( 10 points) Directions: In this section, you will hear a VOA Special English Report three times, and then fill in the blanks with the exact words you hear from the recording. We answered a question last week about how American college students findjobs after they (21)_________________. Now, we discuss foreign graduates. The院系: 班级: 姓名:学号:考场地点装订线(22)________________ for employing foreign workers in the United States is long. It involves different government agencies. It also involves (23)_____________________________________. For example, the American Recovery and Reinvestment Act that President Obama signed into law in February dealt with this issue. It included conditions against foreign workers displacing qualified Americans at companies that (24)________________________________. Job (25)______________ have slowed in some industries. But the economic downturn has cost millions of jobs and recovery will take some time. Foreign graduates need a job (26)________________ to get an H-1B visa. This is a (27)_________________ visa for work in the person’s area of specialty. The employer is the one who (28)_______________ for it. The visa is good for 3 years and may be extended for another 3 years. Cheryl Gilman directs visa services at the University of Southern California in Los Angeles. She noted that H-1B visas were still (29)_________________ for next year. This tells her that the recession is preventing employers from (30)_________________ as many foreign nationals as they have in the past. Part II Reading Comprehension (30 points) Section A Directions: There are two passages in this part. Each passage is followed by some questions or unfinished statements. For each of them there are four choices marked A) , B) , C) and D). You should decide on the best choice and mark the corresponding letter on the Answer Sheet with a single line through the center. Passage One As people generally use the word “honor ” they do not do so in the context of thinking about moral virtue. As a result they often confuse honor with fame. A virtuous person is an honorable person, a person who ought to be honored by the community in which he or she lives. But the virtuous person does not seek honor, being secure in his or her own self-respect. Lack of honor does not detract from the efficacy of moral virtue as an operative factor in the pursuit of happiness —as a means to leading a good human life. Virtuous persons may be considered fortunate if their virtue is recognized and publicly applauded. Persons lacking moral virtue can achieve fame as readily as, or perhaps more easily than, those who have a high degree of moral virtue. Fame belongs to the great, the outstanding, and the exceptional, without regard to their virtue or lack of it. Infamy is fame, no less than popularity. The great scoundrel can be as famous as the great hero. There can be famous villains as well as famous saints. Existing in the reputation a person has, regardless of his or her accomplishments, fame does not tarnish as honor does when it is unmerited. We normally desire the esteem of our fellow human beings, but is not this wish for the esteem of others a desire for fame rather than for honor? A virtuous person will not seek fame or be unhappy for lack of it. For fame can be enjoyed by bad men and women, as well as good. When it is enjoyed by virtuous persons without being sought by them, it is not distinguishable from honor, for then it is deserved. 31. What does this passage mainly talk about? A. A virtuous person achieves both honor and fame. B. A virtuous person does not seek honor or fame. C. Honor and fame are different concepts. D. Honor and fame are not distinguishable. 32. A virtuous person leads a good human life by means of _________. A. presuming happiness B. achieving moral virtue C. seeking honor D. seeking fame 33. What tends to tarnish with time? A. The reputation a person has. B. A high degree of moral virtue. C. A person ’s accomplishments. D. Honor that is undeserved. 34. Fame differs from honor in that _______. A. bad men and women can enjoy fame B. the great people can enjoy fame C. fame can fade in color D. virtuous persons will not seek fame 35. Which of the following statements is TURE? A. A virtuous person deserves honor. B. A famous person deserves honor. C. A virtuous person is publicly identified. D. A famous person has great accomplishments. Passage Two If you want to teach your children how to say sorry, you must be good at saying it yourself, especially to your own children. But how you say it can be quite tricky. If you s ay to your children “I’m sorry I got angry with you, but …”, what follows that “but” can render the apology ineffective: “I had a bad day” or “your noise was giving me a headache ” leaves the person who has been injured feeling that he should be apologizing for his bad behavior in expecting an apology. Another method by which people appear to apologize without actually doing so is to say “I’m sorry you’re upset”; this suggests that you are somehow at fault for allowing yourself to get upset by what the other person has done.院系:班级: 姓名:学号:考场地点装订线Then there is the general, all covering apology, which avoids the necessity of identifying a specific act that was particularly hurtful or insulting, and which the person who is apologizing should promise never to do again. Saying “I’m useless as a parent” does not commit a person to any specific improvement. These pseudo-apologies are used by people who believe saying sorry shows weakness. Parents who wish to teach their children to apologize should see it as a sign of strength, and therefore not resort to these pseudo-apologies. But even when presented with examples of genuine contrition, children still need help to become aware of the complexities of saying sorry. A three-year-old might need help in understanding that other children feel pain just as he does, and that hitting a playmate over the head with a heavy toy requires an apology. A six-year-old might need reminding that spoiling other children’s expectations can require an apology. A 12-year-old might need to be shown that raiding the biscuit tin without asking permission is acceptable, but that borrowing a parent’s clothes without permission is not. 36. If a mother adds “but” to an apology, _______. A. she doesn’t feel that she should have apologized B. she does not realize that the child has been hurt C. the child may find the apology easier to accept D. the child may feel that he owes her an apology 37. According to the author, saying “I’m sorry you’re upset” most probably means “_______”. A. You have good reason to get upset B. I’m aware you’re upset, but I’m not to blame C. I apologize for hurting your feelings D. I’m at fault for making you upset 38. It is not advisable to use the general, all-covering apology because _______. A. it gets one into the habit of making empty promises B. it may make the other person feel guilty C. it is vague and ineffective D. it is hurtful and insulting 39. We learn from the last paragraph that in teaching children to say sorry _______. A. the complexities involved should be ignored B. their ages should be taken into account C. parents need to set them a good example D. parents should be patient and tolerant 40. It can be inferred from the passage that apologizing properly is _______. A. a social issue calling for immediate attention B. not necessary among family membersC. a sign of social progressD. not as simple as it seems Section B: Directions: In this section, there is a passage with ten blanks. You are required to select one word for each blank from a list of choices given in a word bank following the passage. Read the passage through carefully before making your choices. Each choice in the blank is identified by a letter. You may not use any of the words in the bank more than once. Blanks 41 to 50 are based on the following passage. There are two factors which determine an individual ’s intelligence. The first is the sort of brain he is born with. Human brains differ 41 , some being more capable than others. But no matter how good a brain he has to begin with, a (an)42 will have a low intelligence unless he has opportunities to learn. So the second factor in what happens to the individual is the sort of environment in which he is 43 . If an individual is handicapped environmentally, it is likely that his brain will fail to develop. And he will never 44 the level of intelligence of which he is capable. The importance of environment in determining an individual ’s intelligence can be 45 by the case history of the identical twins, Peter and Mark. Being identical, the twins had identical brain at birth, and their growth processes were the same. When the twins were three months old, their parents died, and they were placed in 46 foster homes. Peter was reared by parents of low intelligence in an isolated community with poor 47 opportunities. Mark was reared in the home of well-to-do parents who had been to college. He was read to as a child, sent to good schools, and given every opportunity to be 48 intellectually. This environmental difference continued until the twins were in their late teens, when they were given tests to 49 their intelligence. Mark ’s I.Q. was 125, twenty-five points higher than the 50 , and fully forty points higher than his identical brother. Given equal opportunities, the twins, having identical brains, would have scored at roughly the same level.院系: 班级: 姓名:学号:考场地点装订线Part III Vocabulary and Structure (10 points) Directions: There are 20 incomplete sentences in this part. For each sentence there are four choices marked A, B, C and D. Choose the One answer that best completes the sentence. 51. The boy wanted to ride his bicycle in the street, but his mother told him ____. A. not to B. not to do C. not do it D. do not to 52. Would you like a cup of coffee ____shall we get down to business right away? A. and B. then C. or D. otherwise 53. Not until all the fish died in the river ____how serious the pollution was. A. did the villagers realize B. the villagers realized C. the villagers did realize D. didn't the villagers realize 54. I ____that we would be able to leave tomorrow, but it's beginning to look difficult. A. hoped B. was hoping C. had hoped D. am hoping 55. A study shows that students living in non-smoking dorms are less likely to ____the habit of smoking. A. make up B. turn up C. draw up D. pick up 56. Many personnel managers say it is getting harder and harder to____honest applicants from the growing number of dishonest ones. A. distinguish B. disguise C. dissolve D. discount 57. According to the key witnesses, a peculiarly big nose is the criminal's most memorable facial____. A. feature B. hint C. spot D. signature 58. It's good to know that quite a few popular English expressions actually ____from the Bible. A. acquire B. obtain C. derive D. result 59. After working all day, he was so tired that he was in no____ to go to the party with us. A. taste B. mood C. sense D. emotion 60. There is already clear ____to show that plants and animals are being affected by climate change. A. witness B. certification C. identity D. evidence 61. Last year the advertising rate ____ by 20 percent. A. raised B. aroused C. arose D. rose 62. The student was just about to ______ the question, when suddenly he found the answer. A. arrive at B. submit to C. give in D. work out 63. Suddenly she grabbed her stomach and ______. A. threw away B. threw in C. threw up D. threw off 64. They have brought her out of the operating room, but she ’s not fully ____ yet. A. cautious B. conscience C. conscious D. confused 65. He _____ the job because it involved too much traveling. A. turns in B. turns out C. turns over D. turns down 66.To some _______, Mary still does not understand this unit. But she herself does not believe so. A. extend B. part C. extent D. content 67. He checked carefully to _______ the possible errors in his design. A. eliminate B. exceed C. enlarge D. vibrate 68. What we need to learn is how to put theory into _______ when we begin our fieldwork here. A. appearance B. application C. accomplish D. achievement 69. Jack is _______ of stealing the books from the library. A. accused B. witnessed C. strained D. found 70. The Foreign Minister made an excellent _______ on the current international situation. A. committee B. command C. comment D. commission Part IV Translation (15 points) Translate the following sentences into English. 71. 我从未受过正式培训,我只是边干边学. 72. 随着年龄越来越大,你应该考虑未来的计划。

计算机专业《计算机组成原理》试卷A参考答案

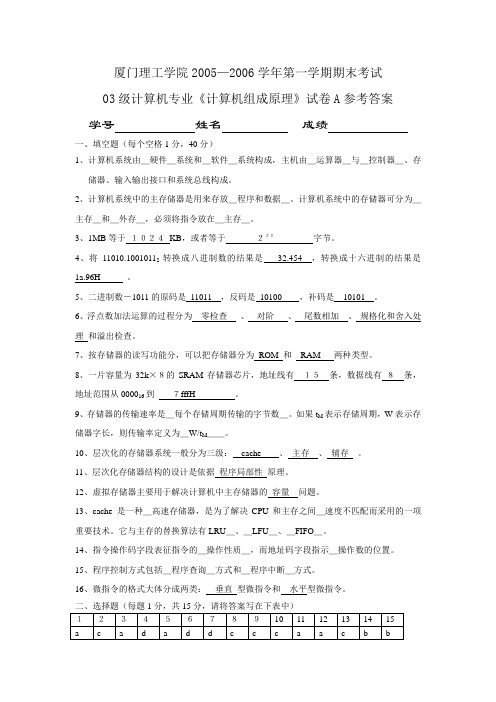

厦门理工学院2005—2006学年第一学期期末考试03级计算机专业《计算机组成原理》试卷A参考答案学号姓名成绩一、填空题(每个空格1分,40分)1、计算机系统由_硬件_系统和_软件_系统构成,主机由_运算器_与_控制器_、存储器、输入输出接口和系统总线构成。

2、计算机系统中的主存储器是用来存放_程序和数据_。

计算机系统中的存储器可分为_主存_和_外存_,必须将指令放在_主存_。

3、1MB等于1024KB,或者等于220字节。

4、将11010.10010112转换成八进制数的结果是32.454 ,转换成十六进制的结果是1a.96H 。

5、二进制数-1011的原码是11011 ,反码是10100 ,补码是10101 。

6、浮点数加法运算的过程分为零检查、对阶、尾数相加、规格化和舍入处理和溢出检查。

7、按存储器的读写功能分,可以把存储器分为ROM 和RAM 两种类型。

8、一片容量为32k×8的SRAM存储器芯片,地址线有15条,数据线有8条,地址范围从000016到7fffH 。

9、存储器的传输速率是_每个存储周期传输的字节数_。

如果t M表示存储周期,W表示存储器字长,则传输率定义为_W/t M__。

10、层次化的存储器系统一般分为三级:cache 、主存、辅存。

11、层次化存储器结构的设计是依据程序局部性原理。

12、虚拟存储器主要用于解决计算机中主存储器的容量问题。

13、cache 是一种_高速存储器,是为了解决CPU和主存之间_速度不匹配而采用的一项重要技术。

它与主存的替换算法有LRU_、_LFU_、_FIFO_。

14、指令操作码字段表征指令的_操作性质_,而地址码字段指示_操作数的位置。

15、程序控制方式包括_程序查询_方式和_程序中断_方式。

16、微指令的格式大体分成两类:垂直型微指令和水平型微指令。

二、选择题(每题1分,共15分,请将答案写在下表中)三、应用题(共45分)1、用已知x=0.101001, y=0.111 采用不恢复余数除法求x÷y。

《英语(一)》期末考试试卷【 A卷】和答案

1《英语(一)》期末考试试卷【A卷】(学年第一学期)注意:1.本试卷共 3 页;2.考试时间: 90 分钟Section A (1×15=15分)Directions: Choose the appropriate letters A—D to complete the following statements.1. I knew a new classmate Ann today. She is _______ America.A. forB. inC. toD. from2. All of his friends came to the airport to______ him____ .A. send…downB. see…offC. send…downD. se e…awa y3. It is of _______for us to get everything read before the party.A. greatly importantB. great importantC. great importanceD. greatly importance4. S1: Can you spare some time for me next week?S2: ______________.A. I’m really very busy now.B. OK. What can I do for you?C. I usually go out seeing movies in my spare time.D. My family will go traveling this evening.5. Would you _____to join us for dessert and coffee?A mind B. please C. like D. care6. I would___ for daily necessities tomorrow. Will you go with me?A. go to shopB. make shoppingC. go shoppingD. buy7. Chinese people have a special way to celebrate the Mid-autumn _______. .A. HolidayB. VacationC. EventD. Festival8. Jack is _______ about stamp collecting. In fact, he is willing to give everything for a rare stamp.A. interestedB. illC. crazyD. sick9. Two hundred people are expected to _______ the meeting.A. attendB. haveC. takeD. go10. Please us at campuslife@ if you need detailed information.A. touchB. contactC. searchD. tell11. Will it be _________ for you to start work tomorrow.A. convenientB. convenienceC. convenientlyD. conveniences12. It is overclouding in the sky and it _____like rain.A. isB. seemsC. seemD. be13. Passengers to pay duty on overweighed luggage.A. requireB. requiredC. are requiredD. were required14. Supermarkets usually provide a(n) Lane for customers with a purchase less than 8 items.A. ExpressB. Hurry-upC. Speed-upD. Fast15. It is difficult for me to __________ the twins ________.A. tel l…fromB. tel l…apartC. tel l…betweenD. tel l…amongSection B (1×10=10分)Directions: Complete each statement with the proper form of the word given in the brackets.16. Jackie Chan is admired by millions as an excellent (act).17. He was about the same (high) as his wife.18. there are as many as 30 different (nation) in this school.19. Tom falls in love with the most (attract) girl in his class.20. Our house was built in a (tradition) Chinese style.21. Many animals have (good) hearing than we do.22. Coin (collect) is one of Jim’s hobbies.23. Sam used to (keep) a pet ,when he was young.24. It’s my pleasure to (introduction) tonight’s speakers.25. He is a very (talk ) child.Part II Reading ComprehensionTask1 (2×5=10分)Directions: Read the passage and choose the appropriate letters A—D to answer each question.Perhaps the best way to think about making friends is to decide what makes a friend. I asked a group of 13 year old boys and girls to come up with a list of what they liked about their friends. They said that good friends: show an interest in what people dogo around with a pleasant expression on their facelaugh at people’s jokesare kindoffer to help others with work or carry thingsinvite people to do somethingare good at thinking of something interesting to doare willing to shareare humorous and tell jokesare fair26. According to the author, what is the best way to make friends?A) The best way is to talk to everyone.B) The best way is to do everything to make the person happy.C) The best way is to think everyone is good.D) The best way is to know what a good friend is.27. How did the author get the list?A) He thought it out.B) He copied it from a book.C) He summed up the ideas of a group of children.D) He made friends with a group of children.28. How many good qualities should a good friend have?A) 6. B) 7. C) 9. D) 10.29. Which of the following is NOT true?A) A good friend should have a sense of humor.B) A good friend should be able to tell jokes and enjoy others’ jokes.C) A good friend should always keep from getting into groups.D) A good friend should enjoy sharing things with others.30. Which of the following is the best title for this passage?A) What Makes a Good FriendB) The Best Way to Make FriendsC) The Results of a SurveyD) How to Make FriendsTask 2 (2×5=10分)Directions: Read the passage and choose the appropriate letters A—D to answer each question.Banks safeguard money and valuables and provide loans, credit, and payment services, such as checking accounts, money orders, and cashier’s checks. Banks may also offer investment and insurance products, which they were once prohibited from selling.As many models for cooperation and integration among finance industries have appeared, some of the traditional differences between banks, insurance companies, and securities firms have disappeared. In spite of these changes, banks continue to maintain and perform their primary role—accepting deposits and lending funds from these deposits.Commercial banks, which dominate the bank industry, offer a full range of services for individuals, businesses, and governments.31. What is the first paragraph mainly about?A. It introduces the types of banks.B. It introduces the functions of banks.C. It explains the traditional functions of banks.D. It discusses the business of banks.32. What are the traditional functions of a bank?A. It safeguards money and valuables.B. It provides loans, credit, and payment services.C. It safeguards money and valuables and provides loans, credit, and payment services.D. It sells investment and insurance products.33. Which of the following statements is not true?A. Banks also play the role of insurance companies.B. Banks safeguard money and valuables like securities firms do.C. Insurance companies cannot play the role of banks.D. The primary functions of banks will always be there. 34. What is the basic role of banks?A. Accept customer’s deposits.B. Back individuals or firms by lending funds.C. Provide firms with investments.D. Accept customer’s deposits and invest the deposits as funds.35. Which of the following is the best title for this passage?A. Nature of Bank IndustryB. Types of BanksC. Changes in Bank IndustryD. Functions of BanksTask 3 (1×5=5分)Directions: Read an ad. Fill in the blanks with Not More Than 3 words in the table below.Shaw’s SupermarketEarn up to $100 from your Shaw’s Osco Pharmacy.Click here for more information.Click here for new dinner ideas from Shaw’s and Swift Premium.Fresh Meal Solutions for Your Family!Click here for detailsAt Shaw’s, we offer you all the attention you could ever want, both online and in your neighborhood store.From pharmacy prescriptions to our in-store CoinStar service. From photo processing to great gift ideas like Gift Cards, prepaid calling cards and cellular programs. From Shaw’s.Task 4 (1×10=10分)Directions: Choose the appropriate letters A—Q to translate the Chinese expressions in the table. A………………………………………………golf course B………………………………………………swimming pool C………………………………………………invitation D…………………………………………credit card E………………………………………………online bank F………………………………………………a deposit form G………………………………………………get-together H………………………………………………going-away party I………………………………………………..family album23J ………………………………………………..instant message service K ………………………………………………withdraw L ………………………………………………check-out desk M ………………………………………………post card N ………………………………………………cashO ………………………………………………international campus P ………………………………………………celebration Q ………………………………………………great grandparentsTask 5 (1×5=5分)Directions: Read the invitation card and answer the questions.46. Whose birthday is it?It is . 47. How old is she going to be?She is going to be . 48. When is her birthday?It ’s on . 49. Where is the party going to be ?I t’s going to be held at . 50. What kind of card is it?It is .Part III TranslationDirections: Each of the four sentences (NO. 51 to NO. 54) is followed by four choices of suggested translationmarked A, B, C and D. Make the best choice and put the paragraph (No.65) into Chinese. (51-54:3×4=12分; 55: 8×1=12分)51. Chess must be one of the oldest games in the world. A. 象棋必须是世界上最古老的游戏之一。

2022年河南工程学院软件工程专业《计算机组成原理》科目期末试卷A(有答案)

2022年河南工程学院软件工程专业《计算机组成原理》科目期末试卷A(有答案)一、选择题1、地址线A15~A0(低),若选取用16K×1位存储芯片构成64KB存储器,则应由地址码()译码产生片选信号。

A.A15,A14B.A0,AlC.A14,A13D.A1,A22、对36位虚拟地址的页式虚拟存储系统,每页8KB,每个页表项为32位,页表的总容量为()。

A.1MBB.4MBC.8MBD.32MB3、计算机硬件能够直接执行的是()。

1.机器语言程序IⅡ.汇编语言程序Ⅲ.硬件描述语言程序入A.仅IB.仅I、ⅡC.仅I、ⅢD. I、Ⅱ 、Ⅲ4、下列关于配备32位微处理器的计算机的说法中,正确的是()。

该机器的通用寄存器一般为32位Ⅱ.该机器的地址总线宽度为32位Ⅲ.该机器能支持64位操作系统IV.一般来说,64位微处理器的性能比32位微处理器的高A.I、ⅡB.I、ⅢC.I、ⅣD.I、IⅡ、Ⅳ5、指令寄存器的位数取决()。

A.存储器的容量B.指令字长C.机器字长人D.存储字长6、下列关于总线仲裁方式的说法中,正确的有()。

I.独立请求方式响应时间最快,是以增加处理器开销和增加控制线数为代价的II.计数器定时查询方式下,有,根总线请求(BR)线和一根设备地址线,若每次计数都从0开始,则设备号小的优先级高III.链式查询方式对电路故障最敏感IV.分布式仲裁控制逻辑分散在总线各部件中,不需要中央仲裁器A.III,IVB. I,III,IVC. I,II,IVD.II,III,IV7、在下面描述的PCI总线的基本概念中,不正确的表述是()。

A.PCI总线支持即插即用B.PCI总线可对传输信息进行奇偶校验C.系统中允许有多条PCI总线D.PCI设备一定是主设备8、指令从流水线开始建立时执行,设指令由取指、分析、执行3个子部件完成,并且,每个子部件的时间均为At,若采用常规标量单流水线处理器(即处理器的度为1),连续执行12条指令,共需()。

2022年沈阳理工大学计算机科学与技术专业《计算机组成原理》科目期末试卷A(有答案)

2022年沈阳理工大学计算机科学与技术专业《计算机组成原理》科目期末试卷A(有答案)一、选择题1、下列关于Cache和虚拟存储器的说法中,错误的有()。

I.当Cache失效(即不命中)时,处理器将会切换进程,以更新Cache中的内容II.当虚拟存储器失效(如缺页)时,处理器将会切换进程,以更新主存中的内容III.Cache 和虚拟存储器由硬件和OS共同实现,对应用程序员均是透明的IV.虚拟存储器的容量等于主存和辅存的容量之和A.I、IⅣB.Ⅲ、VC. I、Ⅱ、ⅢD. I、Ⅲ、Ⅳ2、主存与Cache间采用全相联映射方式,Cache容量4MB,分为4块,每块lMB,主存容量256MB。

若主存读/写时间为30ms,Cache的读/写时间为3ns,平均读/写时间为3.27ms,则Cache的命中率为()。

A.90%B.95%C.97%D.99%3、加法器采用先行进位的根本目的是()。

A.优化加法器的结构B.快速传递进位信号C.增强加法器的功能D.以上都不是4、在补码加减交替除法中,参加操作的数和商符分别是()。

A.绝对值的补码在形成商值的过程中自动形成B.补码在形成商值的过程中自动形成C.补码由两数符号位“异或”形成D.绝对值的补码由两数符号位“异或”形成5、假设在网络中传送采用偶校验码,当收到的数据位为10101010时,则可以得出结论()A.传送过程中未出错B.出现偶数位错C.出现奇数位错D.未出错或出现偶数位错6、下列关于总线仲裁方式的说法中,正确的有()。

I.独立请求方式响应时间最快,是以增加处理器开销和增加控制线数为代价的II.计数器定时查询方式下,有,根总线请求(BR)线和一根设备地址线,若每次计数都从0开始,则设备号小的优先级高III.链式查询方式对电路故障最敏感IV.分布式仲裁控制逻辑分散在总线各部件中,不需要中央仲裁器A.III,IVB. I,III,IVC. I,II,IVD.II,III,IV7、下列关于总线说法中,正确的是()I.使用总线结构减少了信息传输量II.使用总线的优点是数据信息和地址信息可以同时传送III.使用总结结构可以提高信息的传输速度IV.使用总线结构可以减少信息传输线的条数A.I,II,IIIB.II,III,IVC.III,IVD.只有I8、CPU中不包括()。

财务管理试卷(A卷)附答案

财务管理试卷(A卷)一、单项选择题(每题1.5分,共15分)1、现代财务管理理论普遍公认的财务目标是()A、利润最大化B、每股盈余最大化发展C、股东财富最大化D、风险最小化2、已知某企业股票价格为20元,预计下一年的股利为1元,并且该股票以大约10%的速度持续增长,则该股票的期望报酬率为()A、10%B、30%C、25%D、15%3、某企业按照利率10%向银行借款200万元,银行要求维持贷款限额20%的补偿性余额,则企业可以实际使用的借款额为()A、180万元B、20万元C、160万元D、40万元4、下列属于盈利能力比率指标的有()A、已获利息倍数B、权益净利率C、产权比率D、资产负债率5、欲建立一奖学金,每年计划颁发50000元的奖金,若利率为5%,则现在应当存入()A、500元B、50000元C、10000元D、1000000元6、已知甲公司2017年的销售额为200万元,预计2018年外部融资的销售增长率为0.26,预计2018年销售额增长率为5%。

则预计2004年甲公司对外融资额为()A、2.6万元B、52万元C、10万元D、3.6万元7、根据一定的目标资本结构,测算出投资所需要的权益资本,先从盈余当中留用,然后将剩余的盈余作为股利予以分配的是()A、剩余股利政策B、固定股利政策C、固定股利比例政策D、低正常股利加额外股利政策8、某企业每年消耗的某材料5000吨,该材料单位成本为20元,单位储存成本为2元,一次订货成本为50元,则每年最优订货次数为()A、10B、30C、20D、159、下列各项不属于折现分析方法的有()A、现值指数法B、会计收益率法C、内含报酬率法D、净现值法10、甲公司无优先股,去年每股盈余为4元,每股发放股利2元,保留盈余在过去一年增加了500万元。

年底每股账面价值为30元,负债总额为5000万元,则该公司年底资产总额为()A、10000万元B、11000万元C、11500万元D、12500万元二、多项选择题(每题2分,共20分)1、在财务管理中,资金利率的组成部分通常有()A、风险报酬率B、通货膨胀补偿率C、套算利率D、纯利率2、对于上市公司来说,最重要的财务指标是()A、每股收益B、每股净资产C、每股股利D、净资产收益率3、企业持有现金的动机有()A、预防动机B、交易动机C、投资动机D、投机动机4、财务管理的风险按形成的原因,可以分为()A、系统风险B、财务风险C、经营风险D、非系统风险5、下列说法正确的有()A、进行财务管理时应考虑风险B、资产负债率越大,财务风险越大C、速动比率能反映盈利能力D、投资中,净现值法考虑了风险6、债券筹资的优点有()A、筹资成本高B、筹资风险低C、保证控制权D、充分发挥财务杠杆作用7、融资租赁租金的构成有()A、租赁资产的成本B、租赁资产的成本利息C、计提的折旧D、租赁手续费8、下列哪种股利政策有利于股东安排收入和支出()A、剩余股利政策B、固定或持续增长的股利政策C、固定股利支付率政策D、低正常股利加额外股利政策9、如果一个项目投资可行,则()A、净现值大于零B、现值指数大于1C、内含报酬率大于资本成本率D、现值指数小于110、固定资产的计价方法有()A、原始价值B、重置价值C、折余价值D、残值价值三、判断题(每题1.5分,共15分)1、资金的筹集属于企业的财务活动()2、纯粹利率是指无通货膨胀、无风险情况下的利率()3、流动比率可以反映企业的资产管理能力()4、权益净利率 = 总资产净利率×销售净利率×权益乘数()5、销售预测是财务预测的起点()6、风险和报酬率的基本关系是风险越大,获得的报酬率就越高()7、在进行项目投资时,若其收益率超过资本成本,则企业的价值就增加()8、在进行企业存货管理时,要充分考虑存货的储存成本()9、财务杠杆系数 + 经营杠杆系数 = 1()10、产权比率属于企业的长期偿债能力指标()四、计算分析题(50分)1、某公司拟购置一房地产,房主提出两种付款方案:(1)从第五年开始,每年年初支付25万元,连续支付10次,共250万元;(2)从现在起,每年年初支付20万元,连续支付10次,共200万元;若资金成本率为10%,则应该选择哪一个方案?已知:(P/A,10%,9)=5.7590,(P/A,10%,10)=6.1446,(P/F,10%,3)=0.7516 (本题共10分)2、某企业2017年资产总额为1000万元,资产负债率为40%,负债平均利息率为5%,实现的销售收入为1000万元,全部的固定成本和费用为220万元,变动成本率为30%。

2021年清华大学计算机科学与技术专业《计算机组成原理》科目期末试卷A(有答案)

2021年清华大学计算机科学与技术专业《计算机组成原理》科目期末试卷A(有答案)一、选择题1、下列关于一地址指令的说法正确的是()。

A.只有一个操作数B.一定有两个操作数,其中一个是隐含的,完成功能(A)OP(ACC)C.如果有两个操作数,则两个操作数相同,完成功能(A)OP(A)D.可能有两个操作数,也可能只有一个操作数2、寄存器间接寻址方式中,操作数在()中。

A.通用寄存器B.堆栈C.主存单元D.指令本身3、一个浮点数N可以用下式表示:N=mr me,其中,e=rc g;m:尾数的值,包括尾数采用的码制和数制:e:阶码的值,一般采用移码或补码,整数;Tm:尾数的基;re:阶码的基;p:尾数长度,这里的p不是指尾数的:进制位数,当ra=16时,每4个二进制位表示一位尾数;q:阶码长度,由于阶码的基通常为2,因此,在一般情况下,q就是阶码部分的二进制位数。

研究浮点数表示方式的主要目的是用尽量短的字长(主要是阶码字长q和尾数字长的和)实现尽可能大的表述范围和尽可能高的表数精度。

根据这一目的,上述6个参数中只有3个参数是浮点数表示方式要研究的对象,它们是()。

A.m、e、rmB. rm、e、rmC.re、p、qD. rm、p、q4、某数采用IEEE754标准中的单精度浮点数格式表示为C6400000H,则该数的值是()。

A.-1.5×213B.-1.5×212C.-0.5×213D.-0.5×2125、下列为8位移码机器数[x]移,当求[-x]移时,()将会发生溢出。

A.11111111B.00000000C.10000000D.011l1l116、某机器字长32位,存储容量64MB,若按字编址,它的寻址范围是()。

A.8MB.16MBC.16MD.8MB7、关于LRU算法,以下论述正确的是()。

A.LRU算法替换掉那些在Cache中驻留时间最长且未被引用的块B.LRU算法替换掉那些在Cache中驻留时间最短且未被引用的块C.LRU算法替换掉那些在Cache中驻留时间最长且仍在引用的块D.LRU算法替换掉那些在Cache中驻留时间最短且仍在引用的块8、CPU中不包括()。

2022年郑州航空工业管理学院软件工程专业《计算机组成原理》科目期末试卷A(有答案)

2022年郑州航空工业管理学院软件工程专业《计算机组成原理》科目期末试卷A(有答案)一、选择题1、某存储器容量为64KB,按字节编址,地址4000H~5FFFH为ROM区,其余为RAM 区。

若采用8K×4位的SRAM芯片进行设计,则需要该芯片的数量是()。

A.7B.8C.14D.162、某SRAM芯片,其容量为512×8位,除电源和接地端外,该芯片引出线的最小数目应该是()。

A.23B.25C.50D.193、下列描述中,正确的是()。

A.控制器能理解、解释并执行所有指令以及存储结果B.所有数据运算都在CPU的控制器中完成C.ALU可存放运算结果D.输入、输出装置以及外界的辅助存储器称为外部设备4、假定编译器对高级语言的某条语句可以编译生成两种不同的指令序列,A、B和C三类指令的CPl和执行两种不同序列所含的三类指令条数见下表。

则以下结论错误的是()。

I.序列一比序列二少l条指令Ⅱ.序列一比序列二的执行速度快Ⅲ.序列一的总时钟周期数比序列二多1个Ⅳ.序列一的CPI比序列二的CPI大A.I、llB.1、ⅢC. ll、1VD.Ⅱ5、假定机器M的时钟频率为200MHz,程序P在机器M上的执行时间为12s。

对P优化时,将其所有乘4指令都换成了一条左移两位的指令,得到优化后的程序P。

若在M上乘法指令的CPl为102,左移指令的CPl为z,P的执行时间是P”执行时间的1.2倍,则P中的乘法指令条数为()。

A.200万B.400万C.800万D.1600万6、总线的数据传输速率可按公式Q=Wf/N计算,其中Q为总线数据传输速率,W为总线数据宽度(总线位宽/8),f为总线时钟频率,N为完成一次数据传送所需的总线时钟周期个数。

若总线位宽为16位,总线时钟频率为8MHz,完成一次数据传送需2个总线时钟周期,则总线数据传输速率Q为()。

A.16Mbit/sB.8Mbit/sC.16MB/sD.8MB/s7、在异步通信方式中,一个总线传输周期的过程是()。

建筑结构试卷试题A参考(附答案)

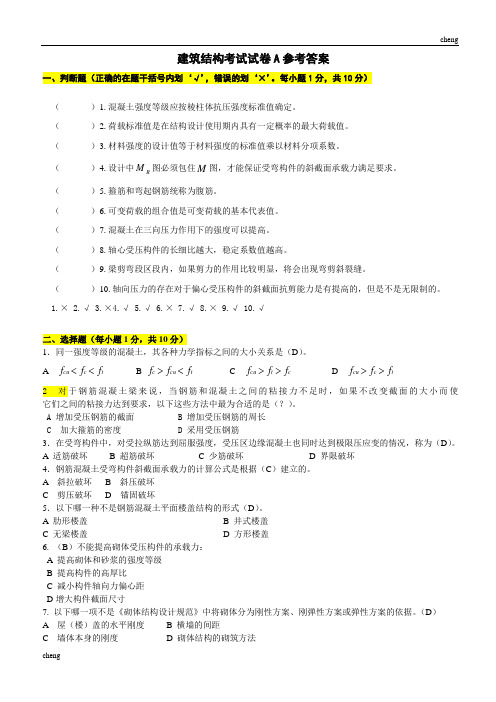

建筑结构考试试卷A 参考答案一、判断题(正确的在题干括号内划‘√’,错误的划‘×’。

每小题1分,共10分)( )1.混凝土强度等级应按棱柱体抗压强度标准值确定。

( )2.荷载标准值是在结构设计使用期内具有一定概率的最大荷载值。

( )3.材料强度的设计值等于材料强度的标准值乘以材料分项系数。

( )4.设计中R M 图必须包住M 图,才能保证受弯构件的斜截面承载力满足要求。

( )5.箍筋和弯起钢筋统称为腹筋。

( )6.可变荷载的组合值是可变荷载的基本代表值。

( )7.混凝土在三向压力作用下的强度可以提高。

( )8.轴心受压构件的长细比越大,稳定系数值越高。

( )9.梁剪弯段区段内,如果剪力的作用比较明显,将会出现弯剪斜裂缝。

( )10.轴向压力的存在对于偏心受压构件的斜截面抗剪能力是有提高的,但是不是无限制的。

1.×2.√3.×4.√5.√6.×7.√8.×9.√ 10.√二、选择题(每小题1分,共10分)1.同一强度等级的混凝土,其各种力学指标之间的大小关系是(D )。

A t c cu f f f <<B t cu c f f f <>C c t cu f f f >>D t c cu f f f >>2 对于钢筋混凝土梁来说,当钢筋和混凝土之间的粘接力不足时,如果不改变截面的大小而使 它们之间的粘接力达到要求,以下这些方法中最为合适的是(?)。

A 增加受压钢筋的截面B 增加受压钢筋的周长C 加大箍筋的密度D 采用受压钢筋3.在受弯构件中,对受拉纵筋达到屈服强度,受压区边缘混凝土也同时达到极限压应变的情况,称为(D )。

A 适筋破坏B 超筋破坏C 少筋破坏D 界限破坏4.钢筋混凝土受弯构件斜截面承载力的计算公式是根据(C )建立的。

A 斜拉破坏B 斜压破坏C 剪压破坏D 锚固破坏5.以下哪一种不是钢筋混凝土平面楼盖结构的形式(D )。

试卷(A)答案及评分标准

Contests试卷(A) (1)试卷(A)答案及评分标准 (5)试卷(B) (8)试卷(B)答案及评分标准 (13)试卷(A )(答案一律写在答题纸上,在本试卷上做无效)一、单项选择题(每题2分,共30分) 1、对于内能的描述,正确的是( )A.状态一定,内能一定B.某一状态对应的内能可以直接测定C.某一状态对应的内能值可以有2个或2个以上D.状态改变,内能一定改变 2、C 2H 5OH(l)+3O 2(g)=2CO 2(g)+3H 2O(g)的反应热为△rHm ,若△Cp>0,则( ) A.△rHm 为C 2H 5OH(l)的△cHm B. 反应热等于反应内能变化值 C.反应热小于0 D.反应热不与温度有关 3、同一温度下,同一理想气体的Cp 与Cv 的关系是( ) A.Cp>Cv B.Cp<Cv C.Cp=Cv D.不能确定 4、恒压条件下,G 随T 的升高而( )A.升高B.降低C.不变D.无法判断5、1mol 理想气体的=⎪⎭⎫ ⎝⎛∂∂TV S ( ) A.-R/V B.R/P C.P/T D.R/V 2 6、水蒸气冷凝成水,则系统的熵变ΔS ( ) A. >0 B. <0 C. = 0 D.无法判断 7、下列关于热力学第三定律,说法正确的是( ) A.在0K 时,任何物质的完美晶体的熵值为0 B.在0K 时,任何纯物质的晶体的熵值为0 C.在0℃时,任何纯物质的完美晶体的熵值为0D.在0K 时,任何纯物质的完美晶体的熵值为08、从热力学基本方程可导出S PH)(∂∂等于( ) A.T P G )(∂∂ B.V S U )(∂∂ C.T V A )(∂∂ D.P T G)(∂∂ 9、既是化学势又是偏摩尔量的是( )A.B A n P T B n U ≠∂∂,,)(B.B A n V S B n A ≠∂∂,,)(C.B A n P S B n H ≠∂∂,,)(D.B A n P T Bn G ≠∂∂,,)(10、298K, P θ压力下的两瓶水溶液A 、B ,A 的渗透压比B 低,当A 、B 间隔一半透膜(只允许水分子通过),这时水的渗透方向是( ) A.A→ B B.B→ A C .无渗透 D.无法判断11、在温度为T ,压力为p 时,反应3O 2(g )=2O 3(g )的Kp 与Ky 比值为( ) A.RT B.p C.(RT )-1 D.p -112、PCl 5的分解反应是PCl 5 (g) = PCl 3 (g) + Cl 2 (g),在473K 达到平衡时,PCl 5 (g)有48.5%分解;在573K 达到平衡时,有97%分解,则此反应为( ) A.放热反应 B.吸热反应C.既不是放热反应也不吸热反应D.这两个温度下的平衡常数相等 13、下列叙述中错误的是( ) A.水的三相点f=0,而冰点f=1 B.水的三相点温度是0℃,压力是610.62PaC.三相点的温度和压力仅由系统决定,不能任意改变D.水的冰点是0℃,压力是101325Pa14、下列电解质中,离子平均活度系数最小的是(设浓度均为0.01mol·㎏-1)( ) A.ZnSO 4 B.CaCl 2 C.KCl Cl 315、已知25ºC 时,1/2CaSO 4,CaCl 2与NaCl 的∞Λ,m 分别为a ,b ,c ,(单位为S·m 2·mol -1),则∞Λ,m (Na 2SO 4)为( )A.c +a -bB.2a -b +2cC.2c -2a +bD.2a -b +c 二、填空题(每题2分,共20分)1、物理量Q 、W 、U 、H 、V 、T 、P 属于状态函数的有_____,状态函数中属于强度性质的有_____,属于广度性质的有_____。

西安交通大学组成原理13年试卷

共 6 页

第 2 页

二、简答题: (每小题 5 分,共 15 分)

1、设磁盘存储器有 6 个记录扇面,共有 100 道题,分 8 个扇区,每扇区存 储 1K 字节,转速为 7200 转/分,则该扇面存储器的总容量是多少字节?数据传 输率是多少(Bps)?平均等待时间又是多少? 2、请列出补码一位乘比较法中每部部分积运算的运算规则表,并分析移位 次数、运算次数等规则。 3、在微指令格式设计中,微地址的形成方法有哪几种?请简述它们获得后 继微地址的方法。假设某机有 100 条指令,平均每条指令由 5 条伪指令编制的 微程序实现,其中有一条取指伪指令是所有指令公用的。已知微指令长度为 32 位,则控制存储器容量至少需要多大?

三、指令系统设计: (15 分)

某 32 位计算机,CPU 中有 32 个通用寄存器,主存容量为 4GB。指令字 节等于机器字长,若该机指令系统课完成 138 种操作,操作码位数固定,且具 有立即寻址、直接寻址、间接寻址、寄存器间接寻址、变址寻址(通用寄存器 作为变址寄存器)、基址寻址(通用寄存器作为基址寄存器)和相对寻址 7 中 方式。 试回答:(要求:答案中数据用 2 的幂形式表示) (1)画出一地址指令格式,并指出各字段的位数及作用; (2)直接寻址的最大范围; (3)变址寻址的范围; (4)基址寻址的位移量范围; (5)相对寻址的位移量范围。

西安交通大学考试题 A 卷

课 程 计算机组成原理 A

系 别 考 试 日 期

成绩

2013 年 1 月 18 日

专业班号 姓 名 学 号 期中 期末 √

一、多选一填空:

(答案请直接填在空中)

(10 分)

1、某机指令字长 20 位,每个操作数的地址码为 8 位,指令分别为零地址、 一地址和二地址 3 种格式。分别采用定长操作码和变长操作码方案时,二地址 指令的最多条数是 。 A.14 条,15 条 B.15 条,16 条 C.16 条,15 条 D.15 条,14 条 2、下列有关存储系统的叙述中,错误的是 。 A.Cache-主存之间的信息调度功能全部由硬件技术实现 B.主存-辅存层次的主要作用是为程序员提供交大的访存空间 C.Cache-主存层次在提高 CPU 访存速度的同时增加了存储器的容量 D.主存-辅存之间的信息调度功能通过软硬件结合的技术实现 3、用 64K×1 位的 DRAM 芯片构成 1M×16 位的主存储器,芯片内部存储元排 列成正方形整列,其刷新最大时间间隔为 4ms。则采用异步刷新时,两次刷新 操作的最大时间间隔为 。 A.18μs B.17μs C.16μs D.15μs 4、 某 CRT 显示器, 采用逐行光栅扫描方式, 其帧频为 50Hz, 行频为 30KHz, 点频为 24MHz,那么该显示器的分辨率为 。 A.800×600 B.1024×728 C.1024×1024 D.1280×720

2023年试验检测师之道路工程自我检测试卷A卷附答案

2023年试验检测师之道路工程自我检测试卷A卷附答案单选题(共40题)1、下列沥青混凝土面层实测项目中属于关键项目的是()。

A.平整度B.弯沉C.压实度D.摩擦系数【答案】 C2、以下无机结合料稳定土中需要控制延迟时间的有()①石灰稳定细粒土②水泥稳定细粒土③石灰水泥稳定细粒土④石灰粉煤灰稳定细粒土⑤水泥粉煤灰稳定细粒土⑥石灰稳定粗粒土A.①③⑤B.②③⑥C.②③⑤D.①②③④⑤⑥【答案】 C3、现行规程规定,采用维卡仪法测定水泥标准稠度用水量,以试杆距底板的距离为()作为水泥达到标准稠度的判定标准。

A.3mm±1mmB.4mm±1mmC.5mm±1mmD.6mm±1mm【答案】 D4、路基、沥青路面弯沉代表值的单位是()。

A.0.1B.0.01C.0.1mmD.0.01mm【答案】 D5、饱和度是用来评价沥青混合料()的指标。

A.高温稳定性B.低温抗裂性C.耐久性D.抗滑性【答案】 C6、用连续平整度仪测定平整度评定工程质量时,所选取的测定位置应距车道标线()。

A.20-30cmB.30-50cmC.50-80cmD.80-100cm【答案】 D7、当水泥细度检验采用负压筛法和水筛法得到的结果发生争视时,应以()为准。

A.负压筛法B.水筛法C.两种方法的算术平均值D.结果较小的方法【答案】 A8、土的常用物理性质指标有:土粒比重Gs、天然密度p、干密度pd、含水率w、饱和密度psat、浮密度p′、孔隙比e、孔隙率n、饱和度Sr,请回答以下问题。

(3)假设土的总体积V,固体颗粒体积Vs,水体积Vw,由(V—Vw一Vs)/V计算得到的是()。

(2013助理真题)A.nB.eC.SrD.以上都不是【答案】 D9、沥青的针入度表示沥青的()。

A.动力黏度B.绝对黏度C.条件黏度D.动黏度【答案】 C10、《公路工程质量检验评定标准》要求。

用3m直尺测定路面平整度时要求每200米测()处,每处()尺。

五邑大学2018计算机组成原理试卷A含答案

五邑大学试卷参考答案及评分标准(A卷)学期: 2018 至 2019学年度第 1 学期课程:计算机组成原理课程代号: 0800200使用班级: 2017级计算机专业各班一、正误判断题(10小题,每小题1分,共10分)1.×加法器采用先行进位(并行进位)的目的是增加加法器的功能。

2.√指令译码器对指令中的操作码字段进行译码。

3.×计算机在运算过程中最高位产生了进位或借位称为溢出。

4.×SRAM和DRAM都可以用作Cache。

5.×计算机操作的最小时间单位是机器周期。

6.√计算机硬件能直接执行的语言是机器语言。

7.√机器的减法运算是补码加法实现的。

8.×在机器浮点加法运算中,为了保证精度,大阶码向小阶码对齐。

9.√在微指令编码表示法中,只有相斥的微命令才能放在同一分组中。

10.×在计算机系统中表征系统运行状态的部件是程序计数器。

二、单项选择题(10小题,每小题2分,共20分)1. 定点16位字长的字,采用补码形式表示时,一个字所能表示的整数范围是 A 。

A.-215~ +(215-1) B.-(215-1)~ +(215-1) C.-(215+1)~ +215D.-215~ +215 2.如果X为补码,由[X]补求[-X]补是将 B 。

A.[X]补符号位变反,其它各位不变B.[X]补连同符号位一起各位变反,末位加1C.[X]补除符号位外,各位变反,末位加1 D.[X]补各位值保持不变3.主存贮器和CPU之间增加cache的目的是_ A 。

A 解决CPU和主存之间的速度匹配问题B 扩大主存容量C 扩大CPU中通用寄存器的数量D 既扩大主存容量,又扩大通用寄存器的数量4. 关于静态存储器、动态存储器,下面叙述中正确的是 C 。

A.动态存储器依靠双稳态电路的两个稳定状态来分别存储0和1B.静态存储器速度较慢,但集成度稍高。

动态存储器速度稍快,但集成度低。

《计算机组成原理》试卷A与参考答案

有一个64K×16位的存储器, 由16K×1位的DRAM芯片(芯片内是128×128结构)构成,存储器读/写周期为500ns。试问:

(1)(3分)需要多少DRAM芯片?

(2)(3分)采用异步刷新方式,如果单元刷新间隔不超过2ms,则刷新信号周期是多少?

(3)(3分)如果采用集中式刷新,存储器刷新一遍最少要用多少时间?

18.已知X为整数,且[X]补= 10011011,则X的十进制数值是。

A +155 B–101 C–155 D +101

19.主存储器是计算机系统的记忆设备,它主要用来。

A存放数据B存放程序C存放数据和程序D存放微程序

20.指令系统采用不同寻址方式的目的是。

A实现存贮程序和程序控制;B缩短指令长度,扩大寻址空间,提高编程灵活性; 。

C变址寄存器内容加上形式地址 (位移量)D程序记数器内容加上形式地址 (位移量)

4.计算机系统中的存贮器系统是指。

A RAM存贮器B ROM存贮器

C主存贮器D cache、主存贮器和外存贮器

5.若浮点数用补码表示,则判断运算结果是否为规格化数的方法是。

A阶符与数符相同为规格化数B阶符与数符相异为规格化数

A主存地址寄存器B程序计数器C指令寄存器D状态条件寄存器

16.微型计算机系统中 ,操作系统保存在硬盘上,其主存储器应该采用。

A RAM B ROM C RAM和ROM D CCP

17.至今为止,计算机中的所有信息仍以二进制方式表示的理由是。

A.节约元件;B运算速度快;C物理器件的性能决定 ;D信息处理方便;

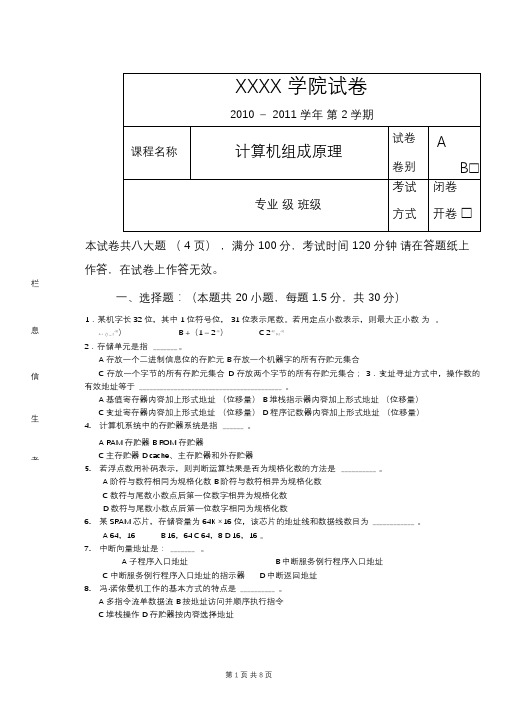

XXXX学院试卷

2010-2011学年 第2学期

课程名称

计算机组成原理

2023年护师类之妇产护理主管护师真题练习试卷A卷附答案

2023年护师类之妇产护理主管护师真题练习试卷A卷附答案单选题(共30题)1、患者李某,剖宫产术后30天,突然阴道大出血3小时。

入院时血压70/60mmHg,心率130次/分,血红蛋白60g/L。

首先给予患者的处理是A.建立有效的静脉通道,大量补液、输血B.应用缩宫素C.抗生素防治感染D.清宫术E.B超【答案】 A2、初产妇,29岁,孕2产0,现妊娠35周,既往曾孕24周脊柱裂胎儿而行引产一次。

此次妊娠早期经过顺利。

妊娠32周时超声检查发现羊水偏多,胎儿大于妊娠周数,未见明显畸形。

孕妇体态肥胖,近期有多饮、多食及多尿症状。

下列并发症中首选考虑哪项诊断A.胎盘早期剥离B.胎儿消化道发育异常C.母儿血型不合D.妊娠期糖尿病E.风疹病毒感染【答案】 D3、34岁女性,葡萄胎2次清宫后,阴道不规则流血持续存在,尿HCG(+)。

首选的辅助检查是A.血β-HCCB.X线检查C.B超检查D.盆腔检查E.诊刮【答案】 C4、李女士,35岁,孕2产1,平素月经规律,经期无不适。

近4个月阴道分泌物增多伴外阴瘙痒。

该女士正确的做法是A.每天用温开水洗外阴部B.自己去药房买药局部用药治疗C.及时去医院检查D.每天用盐开水坐浴E.采用酸性溶液坐浴【答案】 C5、张女士,30岁,目前采用短效口服避孕药避孕,在白天服药后有反应,第二天下午前来就诊。

短效口服避孕药的主要避孕机制是A.子宫内的无菌性反应B.子宫液组成改变C.抑制排卵D.异物反应致子宫内膜产生前列腺素E.受精卵的运行与子宫内膜发育不同步【答案】 C6、某孕妇,35岁,孕2产1,现妊娠35+5周,既往健康,一年前因妊娠7个月死胎而行引产术。

本次妊娠早期产前各项化验指标均正常。

入院检查:血压17.96/10.64kPa(135/80mmHg),体温36.8℃,宫底高度36cm,胎心率正常,空腹血糖7mmol/L,尿糖(++),尿白细胞2~4个/HP。

入院后经控制饮食治疗1周,空腹血糖为6.2mmol/L,NST发现为无反应型,胎心率每分钟114~123次。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

(3)(6 分)模型机的某条指令的微程序流程图如图 2 所示,写出该条指令的功能、寻址方式、指

令第二字的含义。

指令的功能:JMP 指令,(PC)+DISP→PC

寻址方式:相对寻址

指令第二字的含义:相对偏移量 (4)(6 分)写出上述 SUB DR,[SI+ADDR]指令的微程序流程图。

④ (7 分)求 [X*Y](要求阶码用补码计算,尾数用补码 BOOTH 算法计算,列出计算过程和算式)。

四.综合设计题(47 分)

1. (20 分)某机字长 8 位,CPU 地址总线 16 位,数据总线 8 位,存储器按字节编址,CPU

的控制信号线有:MREQ#(存储器访问请求,低电平有效),R/W#(读写控制,低电平 为写信号,高电平为读信号)。试问:

尾数(5 位)

则按上述浮点数的格式:

① (2 分)若数 Z 的浮点数的 16 进制形式为 1ABH,求 Z 的十进制的真值。 [Z]浮=0,0110 1.01011 Z=-0.10101×2+6=-101010 Z=-42 ② (4 分)若(X)10 =15/32,(Y)10= -1.25,则求 X 和 Y 的规格化浮点数表示形式。 X=0.01111 X=0.11110×2-1 【X】浮=1,1111 0.11110 Y=-1.01 Y=-0.10100×2+1 【Y】浮=0,0001 1.01100 ③ (5 分)求(要求用补码计算,列出计算步骤)。

(1) (2 分)若该机主存采用 16K×1 位的 DRAM 芯片(内部为 128×128 阵列)构成最大主存空间, 则共需 32 个芯片。若采用异步刷新方式,单元刷新周期为 2ms,则刷新信号的周期

为 1/64 ms。 (2) (4 分)若为该机配备 2K×8 位的 Cache,每字块 4 字节,采用 4 路组相联映象,则主存地址

MOV1 R1,23H ADD R1, [[12H]] SUB R1, [SI+01H] HALT

立即数

――

23H

(R1)=23H

间接寻址 变址寻址

――

(12H)= (10H)=

10H

80H

(SI)+01H (11H)=

=11H

90H

――

――

(R1)=23H+80H =0A3H

(R1)=0A3H-90H =13H ――

1. 控制器中有若干个专用寄存器,__IR _寄存器用来存放指令,CM) 。

2. 半导体 RAM 通常分为 SRAM 和 DRAM,主要区别在于:前者是用 双稳态触发器

来

存储信息的,而后者是用 极间电容 来存储信息的,前者与后者相比,速度快,价格高。

20H

若(PC)=20H,变址寄存器(SI)=10H,则此时启动程序执行,问执行了几条指令程序停止?

写出每条指令的助记符、寻址方式、EA、操作数和执行结果。

单元地 指令

助记符

寻址方式

EA

址

码

操作数

执行结果

20H 01H 21H 23H 22H 81H 23H 12H 24H 91H 25H 01H 26H F0H

输入输出线、地址线、数据线、控制线及其连接)。

(5) (27 分)设某 8 位计算机指令格式如下:

OP(4 位) SR(2 位) DR(2 位)

A DDR/ DATA / DISP

注意:除了 HALT 指令为单字指令外,其他指令均为双字指令;其中, SR 为源寄存器号, DR 为 目的寄存器号,指令第二字为地址、数据或偏移量。模型机结构如图 1:

3. 从 主存 取出一条指令并执行完这条指令的时间,称为指令周期。指令系统是指 一台计算机中所有机器指令的集合 。

4. 在微程序控制器中,指令译码器的作用是 产生指令的微程序入口地址 。

5. 控制器由专用寄存器、指令译码器、 时序系统 、 操作控制器 构成,控制器的功能是 取

指令 、 分析指令 、 执行指令 、处理特殊请求和异常情况。

中字段块内地址 2 位,字段 Cache 组地址 7 位,字段高位标记 7 位。若主存地址为 1234H,则该地址映象到的 Cache 的第 24H 组。

(3) (4 分)若 CPU 执行一段时间时,Cache 完成存取的次数为 2400 次,主存完成的存取次数为

100 次,已知 cache 的存储周期为 20ns,主存的存储周期为 100ns。则 Cache/主存系统的平均访 问时间为 23.2 或 24 ns,Cache/主存系统的效率为 86.2%或 83.3% 。

(4) (10 分)若用若干个 8K×4 位的 SRAM 芯片形成 24K×8 位的 RAM 存储区域,起始地址为 2000H, 假设 SRAM 芯片有 CS#(片选,低电平有效)和 WE#(写使能,低电平有效)信号控制端;试

写出 RAM 的地址范围,并画出 SRAM 与 CPU 的连接图(请标明 SRAM 芯片个数、译码器的

(1)(9 分)下面是该模型机的指令系统的一部分:

指令助记符

功能

OP

MOV1 DR,DATA

DATA→DR

0000

MOV2 [ADDR],SR

SR→ADDR

0001

ADD

DR,[[ADDR]]

SUB DR,[SI+ADDR]

JMP DISP

(DR)+((ADDR))→DR (DR)-((SI)+ADDR)→DR

(2)(6 分)该微程序控制器有 28 种微操作命令,采用直接控制法,有 4 个转移控制状态,采用

译码形式编码,微指令格式中的下址字段 8 位,微指令格式如下,则操作控制字段和判别测试 字段各有几位?控存的容量为多少(字数×字长)?

控制字段

判别测试字段

下址字段

28 位

2位

8位

控存的容量:256×38 位

组成 A 卷_答案

杭州电子科技大学学生考试卷(A)卷答案

一.单项选择题(20 分,每题 1 分)

1.D

2. C

3. C

4. D

5. C

6. D

7. A

8. D

9. B

10. D

11.B

12. D

13. A

14. B

15. C

16.C

17. B

18. A

19. A

20. D

二.填空题(15 分,每空 1 分)

6. 微指令的格式可以分为 水平型 微指令和 垂直型 微指令,前者并行处理能力强,但微指令

字长 长 。

三.计算题(18 分) 1. (18 分)设浮点数的格式为:阶码 5 位,包含一位符号位,尾数 5 位,包含一位符号位,阶码和

尾数均用补码表示,排列顺序为:

阶符(1 位)

阶码(4 位) 数符(1 位)

(PC)+DISP→PC

1000 1001 1100

…… HALT 内存地址的部分单元内容如下:

…… 停机

…… 1111

单元地址 内容 单元地址 内容 单元地址 内容

10H

80H

20H

01H

24H

91H

11H

90H

21H

23H

25H

01H

12H

10H

22H

81H

26H

F0H

13H

11H

23H

12H

27H