40种封装技术

电子元件封装大全及封装常识

修改者:林子木电子元件封装大全及封装常识一、什么叫封装封装,就是指把硅片上的电路管脚,用导线接引到外部接头处,以便与其它器件连接.封装形式是指安装半导体集成电路芯片用的外壳。

它不仅起着安装、固定、密封、保护芯片及增强电热性能等方面的作用,而且还通过芯片上的接点用导线连接到封装外壳的引脚上,这些引脚又通过印刷电路板上的导线与其他器件相连接,从而实现内部芯片与外部电路的连接。

因为芯片必须与外界隔离,以防止空气中的杂质对芯片电路的腐蚀而造成电气性能下降。

另一方面,封装后的芯片也更便于安装和运输。

由于封装技术的好坏还直接影响到芯片自身性能的发挥和与之连接的PCB(印制电路板)的设计和制造,因此它是至关重要的。

衡量一个芯片封装技术先进与否的重要指标是芯片面积与封装面积之比,这个比值越接近1 越好。

封装时主要考虑的因素:1、芯片面积与封装面积之比为提高封装效率,尽量接近1:1;2、引脚要尽量短以减少延迟,引脚间的距离尽量远,以保证互不干扰,提高性能;3、基于散热的要求,封装越薄越好。

封装主要分为DIP 双列直插和SMD 贴片封装两种。

从结构方面,封装经历了最早期的晶体管TO(如TO-89、TO92)封装发展到了双列直插封装,随后由PHILIP公司开发出了SOP 小外型封装,以后逐渐派生出SOJ(J 型引脚小外形封装)、TSOP(薄小外形封装)、VSOP(甚小外形封装)、SSOP(缩小型SOP)、TSSOP(薄的缩小型SOP)及SOT(小外形晶体管)、SOIC(小外形集成电路)等。

从材料介质方面,包括金属、陶瓷、塑料、塑料,目前很多高强度工作条件需求的电路如军工和宇航级别仍有大量的金属封装。

封装大致经过了如下发展进程:结构方面:TO->DIP->PLCC->QFP->BGA ->CSP;材料方面:金属、陶瓷->陶瓷、塑料->塑料;引脚形状:长引线直插->短引线或无引线贴装->球状凸点;装配方式:通孔插装->表面组装->直接安装二、具体的封装形式1、SOP/SOIC 封装SOP 是英文Small Outline Package 的缩写,即小外形封装。

芯片封装类型图鉴

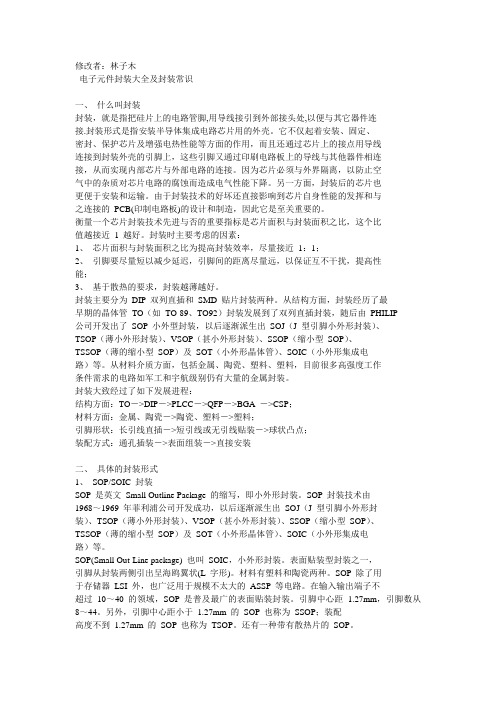

一.TO 晶体管外形封装TO〔Transistor Out-line〕的中文意思是“晶体管外形〞。

这是早期的封装规格,例如TO-92,TO-92L,TO-220,TO-252等等都是插入式封装设计。

近年来外表贴装市场需求量增大,TO封装也进展到外表贴装式封装。

TO252和TO263就是外表贴装封装。

其中TO-252又称之为D-PAK,TO-263又称之为D2PAK。

D-PAK封装的MOSFET有3个电极,栅极〔G〕、漏极〔D〕、源极〔S〕。

其中漏极〔D〕的引脚被剪断不用,而是使用背面的散热板作漏极〔D〕,直接焊接在PCB上,一方面用于输出大电流,一方面通过PCB散热。

所以PCB的D-PAK焊盘有三处,漏极〔D〕焊盘较大。

二. DIP 双列直插式封装DIP(DualIn-line Package)是指采用双列直插形式封装的集成电路芯片,绝大多数中小规模集成电路(IC)均采用这种封装形式,其引脚数一般不超过100个。

封装材料有塑料和陶瓷两种。

采用DIP封装的CPU芯片有两排引脚,使用时,需要插入到具有DIP结构的芯片插座上。

当然,也可以直接插在有一样焊孔数和几何排列的电路板上进展焊接。

DIP封装结构形式有:多层陶瓷双列直插式DIP,单层陶瓷双列直插式DIP,引线框架式DIP〔含玻璃陶瓷封接式,塑料包封结构式,陶瓷低熔玻璃封装式〕等。

DIP封装具有以下特点:1.适合在PCB (印刷电路板)上穿孔焊接,操作方便。

2.比TO型封装易于对PCB布线。

3.芯片面积与封装面积之间的比值较大,故体积也较大。

以采用40根I/O引脚塑料双列直插式封装(PDIP)的CPU为例,其芯片面积/封装面积=(3×3)/(15.24×50)=1:86,离1相差很远。

〔PS:衡量一个芯片封装技术先进与否的重要指标是芯片面积与封装面积之比,这个比值越接近1越好。

如果封装尺寸远比芯片大,说明封装效率很低,占去了很多有效安装面积。

ic的封装类型

ic的封装类型IC的封装类型IC(Integrated Circuit)是集成电路的简称,它是由大量电子元件(如晶体管、电阻、电容等)及其连接电路组成的微小芯片。

为了保护IC芯片不受外界环境和物理损伤的影响,同时方便电路的连接和安装,IC芯片通常需要进行封装。

封装是将芯片封装在外壳中,以保护芯片并方便与外部电路的连接。

IC封装的类型繁多,常见的有DIP、SOP、QFN、BGA等。

不同封装类型具有不同的特点和应用范围,下面将逐一介绍这些封装类型。

DIP(Dual In-line Package)双列直插式封装是IC封装中最早应用的一种类型。

DIP封装的引脚呈现两列直插排列,便于插入插座或焊接到电路板上,因此广泛应用于各种电子设备中。

DIP封装具有易于焊接、维修和更换的优点,但其尺寸较大,无法满足高密度集成电路的需求。

SOP(Small Outline Package)小外形封装是一种体积较小的IC封装类型,它在DIP封装的基础上进行了改进。

SOP封装的引脚仍然是双列直插排列,但引脚间距更小,体积更小,适用于高密度集成电路。

SOP封装广泛应用于计算机、通信设备以及消费电子产品中。

QFN(Quad Flat No-leads)四方无引脚封装是一种无引脚封装类型,它的引脚位于芯片的底部,通过焊盘与电路板连接。

QFN封装具有体积小、引脚密度高、散热性好等优点,适用于要求小型化和散热性能的电子设备。

QFN封装常用于无线通信、汽车电子和工业控制等领域。

BGA(Ball Grid Array)球栅阵列封装是一种高密度封装类型。

BGA 封装的芯片底部有密集的焊球,通过焊球与电路板上的焊盘连接。

BGA封装具有引脚密度高、散热性能好、可靠性高等优点,广泛应用于高性能计算机、网络设备和手机等领域。

BGA封装的缺点是焊接难度较大,维修和更换困难。

除了以上常见的封装类型外,还有PLCC、SOIC、TSOP等多种封装类型,它们在不同的应用领域具有各自的优势。

LED封装的100多种结构形式区分大全

LED封装的100多种结构形式区分大全LED封装技术的要素有三点:封装结构设计、选用合适封装材料和工艺水平。

目前LED封装结构形式有100多种,主要的封装类型有Lamp系列40多种、SMD(chip LED和TOP LED)系列30多种、COB系列30多种、PLCC、大功率封装、光集成封装和模块化封装等,封装技术的发展要紧跟和满足LED应用产品发展的需要。

LED封装技术的基本内容LED封装技术的基本要求是:提高出光效率、高光色性能及器件可靠性。

(1)提高出光效率LED封装的出光效率一般可达80~90%。

①选用透明度更好的封装材料:透明度≥95%(1mm厚度),折射率大于1.5等。

②选用高激发效率、高显性的荧光粉,颗粒大小适当。

③装片基板(反射杯)要有高反射率,出光率高的光学设计外形。

④选用合适的封装工艺,特别是涂覆工艺。

(2)高光色性能LED主要的光色技术参数有:高度、眩光、色温、显色性、色容差、光闪烁等。

显色指数CRI≥70(室外)、≥80(室外)、≥90(美术馆等)。

色容差≤3 SDCM≤5 SDCM(全寿命期间)封装上要采用多基色组合来实现,重点改善LED辐射的光谱量分布SPD,向太阳光的光谱量分布靠近。

要重视量子点荧光粉的开发和应用,来实现更好的光色质量。

(3)LED器件可靠性LED可靠性包含在不同条件下LED器件性能变化及各种失效模式机理(LED封装材料退化、综合应力的影响等),这是主要提到可靠性的表征值—寿命,目前LED器件寿命一般为3~5小时,可达5~10万小时。

①选用合适的封装材料:结合力要大、应力小、匹配好、气密性好、耐温、耐湿(低吸水性)、抗紫外光等。

②封装散热材料:高导热率和高导电率的基板,高导热率、高导电率和高强度的固晶材料,应力要小。

③合适的封装工艺:装片、压焊、封装等结合力强,应力要小,结合要匹配。

LED光集成封装技术LED光集成封装结构现有30多种类型,正逐步走向系统集成封装,是未来封装技术的发展方向。

封装标准介绍(简化版)

芯片的封装技术已经历了好几代的变迁,从DIP、QFP、PGA、BGA到CSP再到MCM,技术指标一代比一代先进,包括芯片面积与封装面积之比越来越接近于1,适用频率越来越高,耐温性能越来越好,引脚数增多,引脚间距减小,重量减小,可靠性提高,使用更加方便等等。

下面将对具体的封装形式作详细说明。

封装形式塑封体尺寸mm*mm*mm引线间距mm/mil跨度mm/milDIP8L9.25*6.35*3.32.54/1007.62/300DIP14L19.1*6.35*3.32.54/1007.62/300DIP16L19.1*6.35*3.32.54/1007.62/300DIP18L22.9*6.5*3.32.54/1007.62/300DIP20L26.23*6.55*3.32.54/1007.62/300DIP24L31.76*13.8*3.852.54/10015.24/600DIP28L37.05*13.8*3.8515.24/600DIP40L52.25*13.8*3.85 2.54/10015.24/600DIP42L52.25*13.8*3.85 2.54/10015.24/600HDIP12L19.1*6.35*3.3 2.54/1007.62/300SDIP24L22.9*6.55*3.3 1.778/707.62/300SDIP28L25.6*8.8*3.3 1.778/7010.16/400SIP8L19.2*6.5*2.8 2.54/100___SIP9L22.3*5.6*3.2 2.54/100___SIP10L24.2*6.7*3.25 2.54/100___HSIP12L2.54/100___ZIP16L24.2*6.7*3.25 1.50/59___SOP8L4.9*3.9*1.38 1.27/505.72/225SOP14L8.65*3.9*1.38 1.27/505.72/225SOP16L9.9*3.9*1.38 1.27/505.72/225SOP16L(W) 10.3*7.5*2.3 1.27/509.53/375SOP20L12.8*7.5*2.3 1.27/509.53/375SOP24L15.4*7.5*2.3 1.27/509.53/375SOP28L18.09*7.5*2.3 1.27/509.53/37519*7.6*2.3 1.27/509.53/375HSOP28L 18.9*7.5*2.3 0.8/31.59.53/375SSOP10L(1) 4.9*3.9*1.38 1/39.33.9/153.5SSOP16L6.2*5.3*1.5 0.62/25.65.3/209SSOP20L7.2*5.3*1.5 0.62/25.65.3/209SSOP24L8.2*5.3*1.5 0.62/25.65.3/209SSOP24L(1) 13*6*1.81/39.36/236SSOP28L 10.2*5.3*1.75 0.62/25.65.3/209TSOP44L 18.44*10.16*1 0.8/31.510.16/400TSOP54L22.2*10.16*10.8/31.510.16/400QFP44L10*10*2.10.8/31.5_____LQFP64L14*14*1.40.8/31.5_____TO251(5L)6.5*5.5*2.31.27/50_____TO252(5L)6.5*5.5*2.31.27/50_____SOT89(3L)4.5*2.5*1.51.5/59_____SOT223(3L)6.5*3.5*1.652.3/91_____一、DIP PGA封装DIP,引脚少于等于24,一般主体宽度为300mil(窄体).多于24脚,多为600mil(宽体)。

封装技术

41

二、封装工艺和控制

2、工艺过程和作用

K、出货(SHIPPING) 按客户要求进行外包装后发往客

户指定地点.

42

二、封装工艺和控制

3、工艺优化方法 A、对分法 B、0.618法.适用于单因素. C、DOE正交试验法,适用于多因素多条件

超级连接1 优选法 正交实验设计(1).doc

缺角

24

擦伤 厚度

划片 装片 键合 塑封 去飞边

电镀 打印 切筋

划偏

缺角

擦伤

沾污

断丝

塌丝

未充填 麻点/气孔

引线框变 飞边残留 形

未镀上 污染

白板

沾污

断筋

弯脚

擦伤 掉片 内外/脱 偏心 塑封体 打毛 变色 倾斜 偏心

沾污 倾斜 强度 溢料

镀层不足 印记错误 缺角

超 级

46

三、封装失效和可靠性

2、封装失效及比例

插装式的结构便于自动化安装和高的可靠 性焊接,体积大。

表面安装式结构引线密度高,体积小, 焊接要求高。

6

一、封装基础知识

4、半导体器件分类

双极型集成电路:

以双极型晶体管为基本有源器件构成的单片集成电路,特点:电路速度 高、阀值电压低、稳定性好负载能力强,但工艺复杂。

MOS集成电路:

以MOS晶体管为基本有源器件构成的单片集成电路,特点:工艺简单、 集成度高、输入阻抗高、功耗小。

Chip Carrier 塑料有引线芯

片载体

9

一、封装基础知识

B、封装形式命名

CLCC Ceramic Leaded Chip Carrier 塑料无引线 芯片载体

芯片封装类型图解

集成电路封装形式介绍(图解)BGA BGFP132 CLCCCPGA DIP EBGA 680LFBGA FDIP FQFP 100LJLCC BGA160L LCCLDCC LGA LQFPLQFP100L Metal Qual100L PBGA217LPCDIP PLCC PPGAPQFP QFP SBA 192LTQFP100L TSBGA217L TSOPCSPSIP:单列直插式封装.该类型的引脚在芯片单侧排列,引脚节距等特征和DIP基本相同.ZIP:Z型引脚直插式封装.该类型的引脚也在芯片单侧排列,只是引脚比SIP粗短些,节距等特征也和DIP基本相同.S-DIP:收缩双列直插式封装.该类型的引脚在芯片两侧排列,引脚节距为1.778mm,芯片集成度高于DIP.SK-DIP:窄型双列直插式封装.除了芯片的宽度是DIP的1/2以外,其它特征和DIP相同.PGA:针栅阵列插入式封装.封装底面垂直阵列布置引脚插脚,如同针栅.插脚节距为2.54mm或1.27mm,插脚数可多达数百脚.用于高速的且大规模和超大规模集成电路.SOP:小外型封装.表面贴装型封装的一种,引脚端子从封装的两个侧面引出,字母L状.引脚节距为1.27mm.MSP:微方型封装.表面贴装型封装的一种,又叫QFI等,引脚端子从封装的四个侧面引出,呈I字形向下方延伸,没有向外突出的部分,实装占用面积小,引脚节距为1.27mm.QFP:四方扁平封装.表面贴装型封装的一种,引脚端子从封装的两个侧面引出,呈L字形,引脚节距为1.0mm,0.8mm,0.65mm,0.5mm,0.4mm,0.3mm,引脚可达300脚以上.SVP:表面安装型垂直封装.表面贴装型封装的一种,引脚端子从封装的一个侧面引出,引脚在中间部位弯成直角,弯曲引脚的端部和PCB键合,为垂直安装的封装.实装占有面积很小.引脚节距为0.65mm,0.5mm.LCCC:无引线陶瓷封装载体.在陶瓷基板的四个侧面都设有电极焊盘而无引脚的表面贴装型封装.用于高速,高频集成电路封装.PLCC:无引线塑料封装载体.一种塑料封装的LCC.也用于高速,高频集成电路封装.SOJ:小外形J引脚封装.表面贴装型封装的一种,引脚端子从封装的两个侧面引出,呈J字形,引脚节距为1.27mm.BGA:球栅阵列封装.表面贴装型封装的一种,在PCB的背面布置二维阵列的球形端子,而不采用针脚引脚.焊球的节距通常为1.5mm,1.0mm,0.8mm,和PGA相比,不会出现针脚变形问题.CSP:芯片级封装.一种超小型表面贴装型封装,其引脚也是球形端子,节距为0.8mm,0.65mm,0.5mm等.TCP:带载封装.在形成布线的绝缘带上搭载裸芯片,并和布线相连接的封装.和其他表面贴装型封装相比,芯片更薄,引脚节距更小,达0.25mm,而引脚数可达500针以上.介绍:1 基本元件类型Basic Component Type盒形片状元件(电阻和电容)Box Type Solder ComponentResistor and Capacitor小型晶体管三极管及二极管SOTSmall Outline TransistorTransistor and Diodeelf类元件Melf type Component [Cylinder]Sop元件Small outline package小外形封装TSop元件Thin Sop薄形封装SOJ元件Small Outline J-lead Package 具有丁形引线的小外形封装QFP元件Quad Flat Package方形扁平封装PLCC元件Plastic Leaded Chip Carrier 塑料有引线芯片载体BGABall Grid Array 球脚陈列封装球栅陈列封装CSPChip Size Package芯片尺寸封装2特殊元件类型Special Component Type钽电容( Tantalium Capacitor)铝电解电容(Aalminum Electrolytic Capacitor )可变电阻( Variable Resistor )针栅陈列封装BGABin Grid Array连接器ConnectorIC卡连接器IC Card Connector附BGA 封装的种类APBGAPlastic BGA塑料BGABCBGACeramic BGA陶瓷BGACCCGACeramic Column Grid Array陶瓷柱栅陈列DTBGATape Automated BGA载带自动键合BGAEMBGA微小BGA注芯片的封装技术已经历了好几代的变迁从DIPQFPPGABGA到CSP再到MCM技术指标一代比一代先进包括芯片面积和封装面积之比越来越接近于1适用频率越来越高耐温性能越来越好引脚数增多引脚间距减少重量减少可靠性提高使用更加方便等(MCMMulti Chip Model 多芯片组件)英汉缩语对照SMTSurface Mount Technology 表面贴装技术SMDSurface Mounting Devices 表面安装器件SMBSurface Mounting Printed Circuit Board 表面安装印刷板DIP Dual-In-Line Package 双列直插式组件THTThough Hole Mounting Technology插装技术PCB Printed Circuit Board 印刷电路板SMC Surface Mounting Components表面安装零件PQFP Plastic Quad Flat Package 塑料方形扁平封装SOIC Small Scale Integrated Circuit小外形集成电路LSI Large Scale Integration 大规模集成注意芯片封装图鉴封装大致经过了如下发展进程:结构方面:DIP封装(70年代)->SMT工艺(80年代 LCCC/PLCC/SOP/QFP)->BGA封装(90年代)->面向未来的工艺(CSP/MCM)材料方面:金属、陶瓷->陶瓷、塑料->塑料;引脚形状:长引线直插->短引线或无引线贴装->球状凸点;装配方式:通孔插装->表面组装->直接安装一.TO 晶体管外形封装TO(Transistor Out-line)的中文意思是“晶体管外形”。

半导体封装工艺介绍

FOL– Die Attach 芯片粘接

Epoxy Write: Coverage >75%;

Die Attach: Placement<0.05mm;

FOL– Epoxy Cure 银浆固化

Die Attach质量检查: 银浆固化: 175°C,1个小时; N2环境,防止氧化: Die Shear(芯片剪切力)

Raw Material in Assembly(封装 原材料)

【Mold Compound】塑封料/环氧树脂

主要成分为:环氧树脂及各种添加剂(固化剂,改性剂,脱 模剂,染色剂,阻燃剂等); 主要功能为:在熔融状态下将Die和Lead Frame包裹起来, 提供物理和电气保护,防止外界干扰; 存放条件:零下5°保存,常温下需回温24小时;

FOL– Wafer Saw晶圆切割

Wafer Mount 晶圆安装 Wafer Saw 晶圆切割 Wafer Wash 清洗

将晶圆粘贴在蓝膜(Mylar)上,使得即使被切割开后,不会散落;

通过Saw Blade将整片Wafer切割成一个个独立的Dice,方便后面的 Die Attach等工序;

• QFN—Quad Flat No-lead Package 四方无引脚扁平封装 • SOIC—Small Outline IC 小外形IC封装 • TSSOP—Thin Small Shrink Outline Package 薄小外形封装 • QFP—Quad Flat Package 四方引脚扁平式封装 • BGA—Ball Grid Array Package 球栅阵列式封装 • CSP—Chip Scale Package 芯片尺寸级封装

FOL– Wire Bonding 引线焊接

SMD常见封装类型

SMD常见封装类型1、BGA(ball grid array)球形触点陈列,表面贴装型封装之一。

在印刷基板的背面按陈列方式制作出球形凸点用以代替引脚,在印刷基板的正面装配L SI 芯片,然后用模压树脂或灌封方法进行密封。

也称为凸点陈列载体(PAC)。

引脚可超过200,是多引脚LS I 用的一种封装。

封装本体也可做得比QF P(四侧引脚扁平封装)小。

例如,引脚中心距为1.5mm 的360 引脚BGA仅为31mm见方;而引脚中心距为0.5mm 的304 引脚QFP为40mm见方。

而且BGA不用担心QF P 那样的引脚变形问题。

该封装是美国Motor ola 公司开发的,首先在便携式电话等设备中被采用,今后在美国有可能在个人计算机中普及。

最初,BGA 的引脚(凸点)中心距为1.5mm,引脚数为225。

现在也有一些LSI 厂家正在开发500 引脚的BGA。

BGA 的问题是回流焊后的外观检查。

现在尚不清楚是否有效的外观检查方法。

有的认为,由于焊接的中心距较大,连接可以看作是稳定的,只能通过功能检查来处理。

美国Moto rola公司把用模压树脂密封的封装称为O MPAC,而把灌封方法密封的封装称为GPAC(见OMPAC和GPAC)。

2、BQFP(quad flat packag e with bumper)带缓冲垫的四侧引脚扁平封装。

QFP 封装之一,在封装本体的四个角设置突起(缓冲垫)以防止在运送过程中引脚发生弯曲变形。

美国半导体厂家主要在微处理器和A SIC 等电路中采用此封装。

引脚中心距0.635mm,引脚数从84到196 左右(见QFP)。

3、碰焊PGA(butt jointpin grid array)表面贴装型P GA 的别称(见表面贴装型PGA)。

半导体集成电路常见封装缩写(精)

半导体集成电路常见封装缩写解释1. DIP(dual in-line PACkage)双列直插式封装。

插装型封装之一,引脚从封装两侧引出,封装材料有塑料和陶瓷两种。

DIP 是最普及的插装型封装,应用范围包括标准逻辑IC,存贮器LSI,微机电路等。

引脚中心距2.54mm,引脚数从6 到64。

封装宽度通常为15.2mm。

有的把宽度为7.52mm和10.16mm 的封装分别称为skinny DIP 和slim DIP(窄体型DIP)。

但多数情况下并不加区分,只简单地统称为DIP。

另外,用低熔点玻璃密封的陶瓷DIP 也称为Cerdip(见C erdip)。

BGA是英文Ball Grid Array Package的缩写,即球栅阵列封装。

SOP小型外引脚封装Small Outline Package ro0c[hi^M 4srs?}JSSOP收缩型小外形封装Shrink Small Outline Package P-pBI%{p)与SOP的区别:近似小外形封装,但宽度要比小外形封装更窄,可节省组装面积的新型封装。

2. DIP(dual tape carrier PACkage)同上。

日本电子机械工业会标准对DTCP 的命名(见DTCP)。

QTCP(quad tape carrier PACkage)四侧引脚带载封装。

TCP 封装之一,在绝缘带上形成引脚并从封装四个侧面引出。

是利用TAB 技术的薄型封装(见TAB、TCP)。

COB(chip on board)板上芯片封装,是裸芯片贴装技术之一,半导体芯片交接贴装在印刷线路板上,芯片与基板的电气连接用引线缝合方法实现,芯片与基板的电气连接用引线缝合方法实现,并用树脂覆盖以确保可靠性。

虽然COB 是最简单的裸芯片贴装技术,但它的封装密度远不如TAB 和倒片焊技术。

JLCC(J-leaded chip carrier)J 形引脚芯片载体。

指带窗口CLCC 和带窗口的陶瓷QFJ 的别称(见CLCC 和QFJ)。

芯片封装分类

芯⽚封装分类芯⽚封装分类⼤全【1】双列直插封装(DIP)20世纪60年代,由于IC集成度的提⾼,电路引脚数不断增加,有了数⼗个I/O引脚的中、⼩规模集成电路(MSI、SSI),相应的封装形式为双列直插(DIP)型,并成为那个时期的主导产品形式。

70年代,芯⽚封装流⾏的是双列直插封装(DIP)、单列直插封装(SIP)、针栅阵列封装(PGA)等都属于通孔插装式安装器件。

通孔插装式安装器件的代表当属双列直插封装,简称DIP(Dualln-LinePackage)。

这类DIP从封装结构形式上可以分为两种:其⼀,军品或要求⽓密封装的采⽤陶瓷双例直插DIP;其⼆,由于塑料封装具有低成本、性价⽐优越等特点,因此,封装形式⼤多数采⽤塑料直插式PDIP。

塑料双便直插封装(PDIP)是上世纪80年代普遍使⽤的封装形式,它有⼀个矩形的塑封体,在矩形塑封体⽐较长的两侧⾯有双列管脚,两相邻管脚之间的节距是2.54mm,引线数为6-84,厚度约为2.0~3.6,如表2所⽰。

两边平等排列管脚的跨距较⼤,它的直插式管脚结构使塑封电路可以装在塑料管内运输,不⽤接触管脚,管脚从塑封体两⾯弯曲⼀个⼩⾓度⽤于插孔式安装,也便于测试或器件的升级和更换。

这种封装形式,⽐较适合印制电路板(PCB)的穿孔安装,具有⽐50年代的TO型圆形⾦属封装,更易于对PCB布线以及操作较为⽅便等特点。

这种封装适合于⼤批量低成本⽣产,便于⾃动化的线路板安装及提供⾼的可靠性焊接。

同时,塑料封装器件在尺⼨、重量、性能、成本、可靠性及实⽤性⽅⾯也优于⽓密性封装。

⼤部分塑封器件重量⼤约只是陶瓷封装的⼀半。

例如:14脚双列直插封装(DIP)重量⼤约为1g,⽽14脚陶瓷封装重2g。

但是双列直插封装(DIP)效率较低,⼤约只有2%,并占去了⼤量有效安装⾯积。

我们知道,衡量⼀个芯⽚封装技术先进与否的重要指标是芯⽚⾯积与封装⾯积之⽐,这个⽐值越接近1越好。

【2】四边引线扁平封装(QFP)20世纪80年代,随着计算机、通讯设备、家⽤电器向便携式、⾼性能⽅向的发展;随着集成电路技术的进步,⼤规模集成电路(LSI)I/O引脚数已达数百个,与之相适应的,为了缩⼩PCB板的体积进⽽缩⼩各种系统及电器的体积,解决⾼密度封装技术及所需⾼密度引线框架的开发,满⾜电⼦整机⼩型化,要求集成电路封装在更⼩的单位⾯积⾥引出更多的器件引脚和信号,向轻、薄、短、⼩⽅向发展。

【知识】元器件封装知识

1文档来源为:从网络收集整理.word 版本可编辑.【关键字】知识贴片式元件表面组装技术(surface Mount Technology 简称SMT) 表面贴装 (Surface Mounted Devices 简称SMD) 一、表面贴片组件(形状和封装的规格)表面贴片技术由1960年代开始发展,在1980年代逐渐广泛采用,至现在已发展多种类SMD 组件,优点是体积较小,适合自动化生产而使用在线路更密集的底板上。

SMD 组件封装的形装和尺寸的规格都已标准化,由JEDEC 标准机构统一,以下是SMD 组件封装的命名:1. 二个焊接端的封装形式:矩形封装:通常有片式电阻(Chip-R)/ 片式电容(Chip-C)/ 片式磁珠 (Chip Bead),常以它们的外形尺寸(英制)的长和宽命名,来标志它们的大小,以英制(inch) 或 公制(mm)为单位, 1inch=25.4mm ,如外形尺寸为0.12in×0,06in ,记为1206,公制记为3.2mm×1.6mm 。

常用的尺寸规格见下表:(一般长度误差值为±10%)NO 英制名称 长(L) "X 宽(W) " 公制(M)名称 长(L)X 宽(W) mm 1 01005 0.016" × 0.008" 0402M 0.4 × 0.2 mm 2 0201 0.024” × 0.012" 0603M 0.6 × 0.3 mm 3 0402 0.04” × 0.02" 1005M 1.0 × 0.5mm 4 0603 0.063" × 0.031" 1608M 1.6 × 0.8 mm 5 0805 0.08" × 0.05" 2012M 2.0 × 1.25 mm 6 1206 0.126" × 0.063" 3216M 3.2 × 1.6 mm 7 1210 0.126" × 0.10" 3225M 3.2 × 2.5 mm 8 1808 0.18" × 0.08" 4520M 4.5 × 2.0 mm 9 1812 0.18" × 0.12" 4532M 4.5 × 3.2 mm 10 2010 0.20" × 0.10" 5025M 5..0 × 2.5 mm 1125120.25" × 0.12" 6330M 6.3 × 3.0 mm 较特别尺寸如下: NO 英制名称 长(L) "X 宽(W) " 公制(M)名称 长(L)X 宽(W) mm 1 0306 0.031" × 0.063" 0816M 0.8 ×1.6 mm 2 0508 0.05" × 0.08" 0508M 1.25 × 2.0mm 3 0612 0.063" ×0.12"0612M1.6 × 3.0 mmMELF 封装:MELF(是Metal Electrical Face 的简称) 圆柱体的封装形式,通常有晶圆电阻(Melf-R) /贴式电感(Melf Inductors) /贴式二极管(Melp Diodes ):NO 工业命名 公制(M)名称 长(L)X 直径(D) mm 101022211M2.2 × 1.1 mm片式电阻(Chip-R ) 片式磁珠 (Chip Bead )片式电容(Chip Cap )2 0204 3715M 3.6 × 1.4 mm3 0207 6123M 5.8 × 2.2 mm4 0309 8734M 8.5 × 3.2 mmSOD封装:专为小型二极管设计的一种封装。

第13章-先进封装技术

图 CBGA结构图

4.载带球栅阵列(TBGA)

也称为阵列载带自动键合(Array Tape Automated Bonding,ATAB),是一种相对新 颖的BGA封装。

TBGA优点:

比其它BGA封装轻、小; 电性能优良; 装配的PCB上,封装效率高。

13.2 CSP技术

刚性基板封装

3、引线框架式CSP封装(Custom Lead Frame)

由日本Fujitsu公司开发的此类CSP封装基本 结构如下页图所示。它分为Tape-LOC和MFLOC 两种形式,将芯片安装在引线框架上, 引线框架作为外引脚,因此不需要制作焊料 凸点,可实现芯片与外部的互连。它通常分 为Tape-LOC和MF-LOC 两种形式。

世界上首款BGA封装的主板芯片组i850

1.塑料球栅阵列(PBGA)工艺流程

PBGA(Plastic Ball Grid Array) PBGA的载体用材料:FR-4环氧树脂,与PCB用材

料相同; 芯片通过引线键合技术连接到载体上表面; 采用塑封进行载体塑模; 采用阵列式低共熔点37Pb/63Sn焊料(约在183℃

引线框架式CSP

4、圆片级CSP封装(Wafer-Level Package)

封装见下页图。它是在圆片前道工序完成后,直接 对圆片利用半导体工艺进行后续组件封装,利用划 片槽构造周边互连,再切割分离成单个器件。

WLP主要包括两项关键技术即再分布技术和凸焊点 制作技术。

它有以下特点:

①相当于裸片大小的小型组件(在最后工序切割分片); ②以圆片为单位的加工成本(圆片成本率同步成本); ③加工精度高(由于圆片的平坦性、精度的稳定性)。

BGA定义:

40种常用的芯片封装技术

40种常用的芯片封装技术封装,Package,是把集成电路装配为芯片最终产品的过程,简单地说,就是把Foundry生产出来的集成电路裸片(Die)放在一块起到承载作用的基板上,把管脚引出来,然后固定包装成为一个整体。

作为动词,“封装”强调的是安放、固定、密封、引线的过程和动作;作为名词,“封装”主要关注封装的形式、类别,基底和外壳、引线的材料,强调其保护芯片、增强电热性能、方便整机装配的重要作用。

1、芯片面积与封装面积之比为提高封装效率,尽量接近1:1;2、引脚要尽量短以减少延迟,引脚间的距离尽量远,以保证互不干扰,提高性能;3、基于散热的要求,封装越薄越好。

封装主要分为DIP双列直插和SMD贴片封装两种。

从结构方面,封装经历了最早期的晶体管TO(如TO-89、TO92)封装发展到了双列直插封装,随后由PHILIP公司开发出了SOP小外型封装,以后逐渐派生出SOJ(J型引脚小外形封装)、TSOP(薄小外形封装)、VSOP(甚小外形封装)、SSOP(缩小型SOP)、TSSOP(薄的缩小型SOP)及SOT(小外形晶体管)、SOIC(小外形集成电路)等。

从材料介质方面,包括金属、陶瓷、塑料,很多高强度工作条件需求的电路如军工和宇航级别仍有大量的金属封装。

1、BGA 封装(ball grid array)球形触点陈列,表面贴装型封装之一。

在印刷基板的背面按陈列方式制作出球形凸点用以代替引脚,在印刷基板的正面装配LSI 芯片,然后用模压树脂或灌封方法进行密封。

也称为凸点陈列载体(PAC)。

引脚可超过200,是多引脚LSI 用的一种封装。

封装本体也可做得比QFP(四侧引脚扁平封装)小。

例如,引脚中心距为1.5mm 的360引脚BGA 仅为31mm 见方;而引脚中心距为0.5mm 的304 引脚QFP 为40mm 见方。

而且BGA。

集成电路封装介绍

由陶瓷封装向塑料封装发展

在陶瓷封装向高密度 ,多引线和低功耗展的同时 , 多引线和低功耗展的同时 越来越多的领域正在由塑料封装所取代。 越来越多的领域正在由塑料封装所取代。而且 , ,目前以PQFP和 目前以PQFP 新的塑料封装形式层出不穷 ,目前以PQFP和 PBGA为主 全部用于表面安装 这些塑料封装 PBGA为主 ,全部用于表面安装 ,这些塑料封装 占领着 90 %以上的市场 以上的市场

半导体制造装备概述

芯片制造(前道) 芯片制造(前道)

单晶硅拉制、切片、表面处理、光刻、减薄、 单晶硅拉制、切片、表面处理、光刻、减薄、 划片

芯片封装(后道) 芯片封装(后道)

测试、 滴胶、 测试、 滴胶、Die bonding、Wire bonding、 、 、 压模

Y

Y

Y

Y

封装类型 无引线(面) 栅阵列 小外形或小外 形IC 小外形J形引 线 载带自动焊 列直插封装 单列直插封装 单边交叉双列 直插封装 四边单列直插 封装 单列直插存储 器模块

缩写词 LGA SO或SOIC SOJ TAB SIP ZIP QUIP

SMTPGA TAB

60年代

70年代

80年代

90年代 Y Y Y

Y Y Y Y Y Y Y

Y Y Y Y Y

多芯片模块 MCM针栅阵列 缩小的DIP 多I/O引脚数SIMM

MCM MCMPG A

SIMM (SIP)

微电子封装一般可分为 4级 ,如图 所示 ,即 : 级 如图 即 0级封装 级封装———芯片上器件本体的互连 级封装 芯片上器件本体的互连 1级封装 级封装———芯片 (1个或多个 )上的输入 / 级封装 芯片 个或多个 上的输入 输出与基板互连 2级封装 级封装———将封装好的元器件或多芯片 级封装 将封装好的元器件或多芯片 PWB)组装成电 组件用多层互连布线板 (PWB 组装成电 PWB 子部件 ,插件或小整机 插件或小整机 3级封装 级封装———用插件或小整机组装成机柜 级封装 用插件或小整机组装成机柜 整机系统

pcb元器件最全的封装详细介绍

史上最全的芯片封装介绍芯片封装,简单点来讲就是把Foundry生产出来的集成电路裸片(Die)放到一块起承载作用的基板上,再把管脚引出来,然后固定包装成为一个整体。

它可以起到保护芯片的作用,相当于是芯片的外壳,不仅能固定、密封芯片,还能增强其电热性能。

因此,封装对CPU和其他LSI集成电路而言,非常重要。

封装的类型,大致可以分为DIP双列直插和SMD贴片封装两种。

从结构方面,封装经历了最早期的晶体管TO(如TO-89、TO92)封装发展到了双列直插封装,随后由PHILIP公司开发出了SOP小外型封装,以后逐渐派生出SOJ (J型引脚小外形封装)、TSOP(薄小外形封装)、VSOP(甚小外形封装)、 SSOP (缩小型SOP)、TSSOP(薄的缩小型SOP)及SOT(小外形晶体管)、SOIC(小外形集成电路)等。

从材料介质方面,包括金属、陶瓷、塑料、塑料,很多高强度工作条件需求的电路如军工和宇航级别仍有大量的金属封装。

以下为小编整理的主流封装类型:常见的10大芯片封装类型1、DIP双列直插式封装DIP是指采用双列直插形式封装的集成电路芯片,绝大多数中小规模集成电路(IC)均采用这种封装形式,其引脚数一般不超过100个。

采用DIP封装的IC有两排引脚,需要插入到具有DIP结构的芯片插座上。

当然,也可以直接插在有相同焊孔数和几何排列的电路板上进行焊接。

DIP封装的芯片在从芯片插座上插拔时应特别小心,以免损坏引脚。

DIP封装图DIP封装具有以下特点:1、适合在PCB(印刷电路板)上穿孔焊接,操作方便。

2、芯片面积与封装面积之间的比值较大,故体积也较大。

DIP是最普及的插装型封装,应用范围包括标准逻辑IC,存储器和微机电路等。

2、QFP/ PFP类型封装QFP/PFP封装的芯片引脚之间距离很小,管脚很细,一般大规模或超大型集成电路都采用这种封装形式。

用这种形式封装的芯片必须采用SMD(表面安装设备技术)将芯片与主板焊接起来。

各封装的区别

1、BGA(ball grid array)球形触点陈列,表面贴装型封装之一。

在印刷基板的背面按陈列方式制作出球形凸点用以代替引脚,在印刷基板的正面装配LSI芯片,然后用模压树脂或灌封方法进行密封。

也称为凸点陈列载体(PAC)。

引脚可超过200,是多引脚LSI用的一种封装。

封装本体也可做得比QFP(四侧引脚扁平封装)小。

例如,引脚中心距为1.5mm的360引脚BGA仅为31mm见方;而引脚中心距为0.5mm的304引脚QFP为40mm见方。

而且BGA不用担心QFP那样的引脚变形问题。

该封装是美国Motorola公司开发的,首先在便携式电话等设备中被采用,今后在美国有可能在个人计算机中普及。

最初,BGA的引脚(凸点)中心距为1.5mm,引脚数为225。

现在也有一些LSI厂家正在开发500引脚的BGA。

BGA的问题是回流焊后的外观检查。

现在尚不清楚是否有效的外观检查方法。

有的认为,由于焊接的中心距较大,连接可以看作是稳定的,只能通过功能检查来处理。

美国Motorola公司把用模压树脂密封的封装称为OMPAC,而把灌封方法密封的封装称为GPAC(见OMPAC和GPAC)。

2、BQFP(quad flat package with bumper)带缓冲垫的四侧引脚扁平封装。

QFP封装之一,在封装本体的四个角设置突起(缓冲垫)以防止在运送过程中引脚发生弯曲变形。

美国半导体厂家主要在微处理器和ASIC等电路中采用此封装。

引脚中心距0.635mm,引脚数从84到196左右(见QFP)。

3、碰焊PGA(butt joint pin grid array)表面贴装型PGA的别称(见表面贴装型PGA)。

4、C-(ceramic)表示陶瓷封装的记号。

例如,CDIP表示的是陶瓷DIP。

是在实际中经常使用的记号。

5、Cerdip用玻璃密封的陶瓷双列直插式封装,用于ECL RAM,DSP(数字信号处理器)等电路。

带有玻璃窗口的Cerdip用于紫外线擦除型EPROM以及内部带有EPROM的微机电路等。

大功率芯片封装

大功率芯片一般需要进行封装,以便实现电路板的组装和应用。

常见的大功率芯片封装方式有以下几种:

1. QFP封装:QFP(Quad Flat Package)封装是一种面积较小、引脚数较多的表面贴装封装。

QFP封装可以承载较高功率,适合于功率密度较高的应用场合。

2. BGA封装:BGA(Ball Grid Array)封装是一种球形网格阵列封装,其引脚通过焊接在基板的底部,可以使得芯片上的引脚数量更多,适用于功率密度较高的大功率芯片。

3. DIP封装:DIP(Dual In-line Package)封装是一种双行直插式封装,被广泛用于早期的芯片封装。

DIP封装在功率密度较低的情况下,仍可用于大功率芯片。

4. LGA封装:LGA(Land Grid Array)封装是一种与BGA类似的焊盘封装。

它的主要优点是可以提供更高的连接密度,以及更好的导热性。

5. TO封装:TO(Transistor Outline)封装是一种晶体管外形封装,适合于功率密度较低的大功率芯片。

6. COB封装:COB(Chip on Board)封装是一种将芯片直接粘贴在基板上的封装方式。

它可以显著减小芯片与基板之间的导通电阻,提高芯片的可靠性和导热性。

在选择大功率芯片封装方式时,需要考虑功率密度、散热、可靠性、成本等因素,并根据具体应用需求进行选择。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

1、BGA 封装(ball grid array)球形触点陈列,表面贴装型封装之一。

在印刷基板的背面按陈列方式制作出球形凸点用以代替引脚,在印刷基板的正面装配LSI 芯片,然后用模压树脂或灌封方法进行密封。

也称为凸点陈列载体(PAC)。

引脚可超过200,是多引脚LSI 用的一种封装。

封装本体也可做得比QFP(四侧引脚扁平封装)小。

例如,引脚中心距为1.5mm 的360 引脚BGA 仅为31mm 见方;而引脚中心距为0.5mm 的304 引脚QFP 为40mm 见方。

而且BGA 不用担心QFP 那样的引脚变形问题。

该封装是美国Motorola 公司开发的,首先在便携式电话等设备中被采用,今后在美国有可能在个人计算机中普及。

最初,BGA 的引脚(凸点)中心距为1.5mm,引脚数为225。

现在也有一些LSI 厂家正在开发500 引脚的BGA。

BGA 的问题是回流焊后的外观检查。

现在尚不清楚是否有效的外观检查方法。

有的认为,由于焊接的中心距较大,连接可以看作是稳定的,只能通过功能检查来处理。

美国Motorola 公司把用模压树脂密封的封装称为OMPAC,而把灌封方法密封的封装称为GPAC(见OMPAC 和GPAC)。

2、BQFP 封装(quad flat package with bumper)带缓冲垫的四侧引脚扁平封装。

QFP 封装之一,在封装本体的四个角设置突起(缓冲垫) 以防止在运送过程中引脚发生弯曲变形。

美国半导体厂家主要在微处理器和ASIC 等电路中采用此封装。

引脚中心距0.635mm,引脚数从84 到196 左右(见QFP)。

3、碰焊PGA 封装(butt joint pin grid array)表面贴装型PGA 的别称(见表面贴装型PGA)。

4、C-(ceramic) 封装表示陶瓷封装的记号。

例如,CDIP 表示的是陶瓷DIP。

是在实际中经常使用的记号。

5、Cerdip 封装用玻璃密封的陶瓷双列直插式封装,用于ECL RAM,DSP(数字信号处理器)等电路。

带有玻璃窗口的Cerdip用于紫外线擦除型EPROM 以及内部带有EPROM 的微机电路等。

引脚中心距2.54mm,引脚数从8 到42。

在日本,此封装表示为DIP-G(G 即玻璃密封的意思)。

6、Cerquad 封装表面贴装型封装之一,即用下密封的陶瓷QFP,用于封装DSP 等的逻辑LSI 电路。

带有窗口的Cerquad用于封装EPROM 电路。

散热性比塑料QFP 好,在自然空冷条件下可容许1. 5~2W 的功率。

但封装成本比塑料QFP 高3~5 倍。

引脚中心距有1.27mm、0.8mm、0.65mm、0.5mm、0.4mm 等多种规格。

引脚数从32 到368。

带引脚的陶瓷芯片载体,表面贴装型封装之一,引脚从封装的四个侧面引出,呈丁字形。

带有窗口的用于封装紫外线擦除型EPROM 以及带有EPROM 的微机电路等。

此封装也称为QFJ、QFJ-G(见QFJ)。

7、CLCC 封装(ceramic leaded chip carrier)带引脚的陶瓷芯片载体,表面贴装型封装之一,引脚从封装的四个侧面引出,呈丁字形。

带有窗口的用于封装紫外线擦除型EPROM 以及带有EPROM 的微机电路等。

此封装也称为QFJ、QFJ-G(见QFJ)。

8、COB 封装(chip on board)板上芯片封装,是裸芯片贴装技术之一,半导体芯片交接贴装在印刷线路板上,芯片与基板的电气连接用引线缝合方法实现,芯片与基板的电气连接用引线缝合方法实现,并用树脂覆盖以确保可*性。

虽然COB 是最简单的裸芯片贴装技术,但它的封装密度远不如TAB 和倒片焊技术。

9、DFP(dual flat package)双侧引脚扁平封装。

是SOP 的别称(见SOP)。

以前曾有此称法,现在已基本上不用。

陶瓷DIP(含玻璃密封)的别称(见DIP).11、DIL(dual in-line) DIP 的别称(见DIP)。

欧洲半导体厂家多用此名称。

12、DIP(dual in-line package) 双列直插式封装。

插装型封装之一,引脚从封装两侧引出,封装材料有塑料和陶瓷两种。

DIP 是最普及的插装型封装,应用范围包括标准逻辑IC,存贮器LSI,微机电路等。

引脚中心距2.54mm,引脚数从6 到64。

封装宽度通常为15.2mm。

有的把宽度为7.52mm 和10.16mm 的封装分别称为skinny DIP 和slim DIP(窄体型DIP)。

但多数情况下并不加区分,只简单地统称为DIP。

另外,用低熔点玻璃密封的陶瓷DIP 也称为cerdip(见cerdip)。

13、DSO(dual small out-lint)双侧引脚小外形封装。

SOP 的别称(见SOP)。

部分半导体厂家采用此名称。

双侧引脚带载封装。

TCP(带载封装)之一。

引脚制作在绝缘带上并从封装两侧引出。

由于利用的是TAB(自动带载焊接)技术,封装外形非常薄。

常用于液晶显示驱动LSI,但多数为定制品。

另外,0.5mm 厚的存储器LSI簿形封装正处于开发阶段。

在日本,按照EIAJ(日本电子机械工业)会标准规定,将DICP 命名为DTP。

15、DIP(dual tape carrier package)同上。

日本电子机械工业会标准对DTCP 的命名(见DTCP)。

16、FP(flat package)扁平封装。

表面贴装型封装之一。

QFP 或SOP(见QFP 和SOP)的别称。

部分半导体厂家采用此名称。

17、Flip-chip倒焊芯片。

裸芯片封装技术之一,在LSI 芯片的电极区制作好金属凸点,然后把金属凸点与印刷基板上的电极区进行压焊连接。

封装的占有面积基本上与芯片尺寸相同。

是所有封装技术中体积最小、最薄的一种。

但如果基板的热膨胀系数与LSI 芯片不同,就会在接合处产生反应,从而影响连接的可靠性。

因此必须用树脂来加固LSI 芯片,并使用热膨胀系数基本相同的基板材料。

其中SiS 756北桥芯片采用最新的Flip-chip封装,全面支持AMDAthlon 64/FX中央处理器。

支持PCI Express X16接口,提供显卡最高8GB/s双向传输带宽。

支持最高HyperTransport Technology,最高2000MT/s MHz的传输带宽。

内建矽统科技独家Advanced HyperStreaming Technology,MuTIOL 1G Technology。

18、FQFP(fine pitch quad flat package)小引脚中心距QFP。

通常指引脚中心距小于0.65mm 的QFP(见QFP)。

部分导导体厂家采用此名称。

塑料四边引出扁平封装PQFP(Plastic Quad Flat Package)PQFP 的封装形式最为普遍。

其芯片引脚之间距离很小,引脚很细,很多大规模或超大集成电路都采用这种封装形式,引脚数量一般都在100个以上。

Intel 系列CPU 中80286、80386和某些486主板芯片采用这种封装形式。

此种封装形式的芯片必须采用SMT 技术(表面安装设备)将芯片与电路板焊接起来。

采用SMT 技术安装的芯片不必在电路板上打孔,一般在电路板表面上有设计好的相应引脚的焊点。

将芯片各脚对准相应的焊点,即可实现与主板的焊接。

用这种方法焊上去的芯片,如果不用专用工具是很难拆卸下来的。

SMT 技术也被广泛的使用在芯片焊接领域,此后很多高级的封装技术都需要使用SMT 焊接。

以下是一颗AMD 的QFP 封装的286处理器芯片。

0.5mm 焊区中心距,208根I/O 引脚,外形尺寸28×28mm,芯片尺寸10×10mm,则芯片面积/封装面积=10×10/28×28=1:7.8,由此可见QFP 比DIP 的封装尺寸大大减小了。

PQFP 封装的主板声卡芯片19、CPAC(globe top pad array carrier)美国Motorola 公司对BGA 的别称(见BGA)。

20、CQFP 軍用晶片陶瓷平版封裝(Ceramic Quad Flat-pack Package)右邊這顆晶片為一種軍用晶片封裝(CQFP),這是封裝還沒被放入晶體以前的樣子。

這種封裝在軍用品以及航太工業用晶片才有機會見到。

晶片槽旁邊有厚厚的黃金隔層(有高起來,照片上不明顯)用來防止輻射及其他干擾。

外圍有螺絲孔可以將晶片牢牢固定在主機板上。

而最有趣的就是四周的鍍金針腳,這種設計可以大大減少晶片封裝的厚度並提供極佳的散熱。

21、H-(with heat sink)表示带散热器的标记。

例如,HSOP 表示带散热器的SOP。

22、Pin Grid Array(Surface Mount Type)表面贴装型PGA。

通常PGA 为插装型封装,引脚长约3.4mm。

表面贴装型PGA 在封装的底面有陈列状的引脚,其长度从1.5mm 到2.0mm。

贴装采用与印刷基板碰焊的方法,因而也称为碰焊PGA。

因为引脚中心距只有1.27mm,比插装型PGA 小一半,所以封装本体可制作得不怎么大,而引脚数比插装型多(250~528),是大规模逻辑LSI 用的封装。

封装的基材有多层陶瓷基板和玻璃环氧树脂印刷基数。

以多层陶瓷基材制作封装已经实用化。

PGA 封装威刚迷你DDR333本内存23、JLCC 封装(J-leaded chip carrier)J 形引脚芯片载体。

指带窗口CLCC 和带窗口的陶瓷QFJ 的别称(见CLCC 和QFJ)。

部分半导体厂家采用的名称。

24、LCC 封装(Leadless chip carrier)无引脚芯片载体。

指陶瓷基板的四个侧面只有电极接触而无引脚的表面贴装型封装。

是高速和高频IC 用封装,也称为陶瓷QFN 或QFN-C(见QFN)。

25、LGA 封装(land grid array)触点陈列封装。

即在底面制作有阵列状态坦电极触点的封装。

装配时插入插座即可。

现已实用的有227 触点(1.27mm 中心距)和447 触点(2.54mm 中心距)的陶瓷LGA,应用于高速逻辑LSI 电路。

LGA 与QFP 相比,能够以比较小的封装容纳更多的输入输出引脚。

另外,由于引线的阻抗小,对于高速LSI 是很适用的。

但由于插座制作复杂,成本高,现在基本上不怎么使用。

预计今后对其需求会有所增加。

AMD 的2.66GHz 双核心的Opteron F 的Santa Rosa 平台26、LOC 封装(lead on chip)芯片上引线封装。

LSI 封装技术之一,引线框架的前端处于芯片上方的一种结构,芯片的中心附近制作有凸焊点,用引线缝合进行电气连接。

与原来把引线框架布置在芯片侧面附近的结构相比,在相同大小的封装中容纳的芯片达1mm 左右宽度。