四路抢答器 (完整版)

四路抢答器完整版.docx

华北科技学院课程设计说明书班级:电子 B071姓名:郭亚立设计题目:四路智能抢答器设计时间:2010.1.9至 2010.1.22学号:200703014138指导教师:杜志伟评语:评阅成绩:评阅老师:华北科技学院课程设计报告四路抢答器设计报告目录一、设计任务和要求: ...................................................................................................................- 3 -1.1设计任务 ..................................................................................................................................- 3 -1.2设计要求 ..................................................................................................................................- 3 -二、设计方案的选择与论证...........................................................................................................- 4 -2.1方案的选择、论证 ..................................................................................................................- 4 -2.2设计总方案 ..............................................................................................................................- 4 -三、电路设计计算与分析.................................................................................................................- 5 -3.1抢答器控制电路设计 ..............................................................................................................- 5 -3.1.1优先编码器 74LS148 .....................................................................................................- 7 -3.1.2锁存器 74LS279 ............................................................................................................- 9 -3.1.374LS121 单稳态触发器: (10)3.2定时时间电路的设计 (10)3.2.1计数器 74LS192 (12)3.3控制电路和报警电路 (13)3.3.1振荡电路 (17)华北科技学院课程设计报告3.4整体仿真 (19)四、总结及心得 (20)五、附录 (22)5.1主要元器件列表 (22)5.2总原理图 (23)六、参考文献 (24)一、设计任务和要求:1.1设计任务设计一台可供 4 名选手参加比赛的智力竞赛抢答器。

四路抢答器电路组成及工作原理(含电路图)

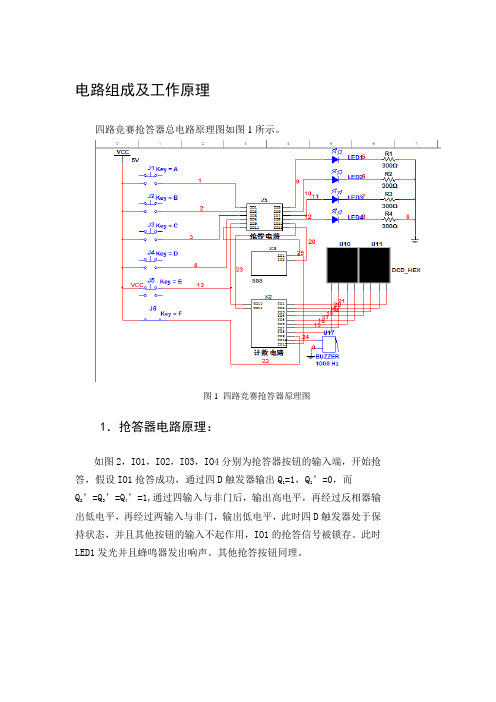

电路组成及工作原理四路竞赛抢答器总电路原理图如图1所示。

图1 四路竞赛抢答器原理图1.抢答器电路原理:如图2,IO1,IO2,IO3,IO4分别为抢答器按钮的输入端,开始抢答,假设IO1抢答成功,通过四D触发器输出Q1=1,Q1’=0,而Q 2’=Q3’=Q4’=1,通过四输入与非门后,输出高电平,再经过反相器输出低电平,再经过两输入与非门,输出低电平,此时四D触发器处于保持状态,并且其他按钮的输入不起作用,IO1的抢答信号被锁存。

此时LED1发光并且蜂鸣器发出响声。

其他抢答按钮同理。

图2 抢答器部分电路图2.计时电路原理:计时电路为两片74LS160用置数法构成的31进制计数器,因为可以为了让答题者直观的看到30S这个时间点,所以设置了31进制的计数器。

两片的四个输入端均接低电平,两片的输出端分别接七段译码管直接显示数字,高位的74LS160芯片的Q1Q2接到一个二输入的与非门(U8A)输出到计数器的LD端、三输入与非门端、反相器端。

输出到LD端是为了构成31进制计数器,当高位变为3时,计数器置0。

输出到三输入与非门(U9A)和时钟脉冲、开关的电平信号一起输入到与非门中,这就是为什么能控制计时的开始与暂停了,当开关输入低电平时,无论是否有时钟信号,时钟均不发生改变,此时时钟信号为无效信号;而当开关输入高电平时,U8A输出也为高,因此,时钟信号为有效信号,因此,凭借这样的类似锁存的电路,就可以控制计时的开始与暂停。

而当时间到了30s时,U8A输出为低电平,时钟信号又成为无效信号,时间被停止在30s,此时将U8A信号通过一个反相器输出到蜂鸣器,蜂鸣器发出响声。

图3 计时器电路3.555函数发生器:输出高电平时间:T1=(R1+R2)Cln2输出低电平时间:T2=R2Cln2振荡周期:T=(R1+2R2)Cln2图4 555函数发生器。

四路抢答器(完整版)

华北科技学院课程设计说明书班级:电子B071 :郭亚立设计题目:四路智能抢答器设计时间: 2010.1.9 至 2010.1.22 学号: 8指导教师:杜志伟评语:评阅成绩:评阅老师:四路抢答器设计报告目录一、设计任务和要求:...................................................... - 3 -1.1设计任务 (3)1.2设计要求 (3)二、设计方案的选择与论证.................................................. - 4 -2.1方案的选择、论证 (4)2.2设计总方案 (4)三、电路设计计算与分析..................................................... - 5 -3.1抢答器控制电路设计 (5)3.1.1 优先编码器 74LS148................................................ - 7 -3.1.2 锁存器74LS279.................................................... - 9 -3.1.3 74LS121单稳态触发器:.......................................... - 10 -3.2定时时间电路的设计 (10)3.2.1 计数器74LS192................................................... - 12 -3.3控制电路和报警电路 (13)3.3.1 振荡电路......................................................... - 17 -3.4整体仿真 (19)四、总结及心得 ............................................................- 20 -五、附录 .................................................................- 22 -5.1主要元器件列表 (22)5.2总原理图 (23)六、参考文献 ..............................................................- 24 -一、设计任务和要求:1.1设计任务设计一台可供4名选手参加比赛的智力竞赛抢答器。

单片机课程设计四路抢答器

xxxxxx大学课程设计报告课程设计名称:单片机系统综合课程设计课程设计题目:四路抢答器院(系):专业:班级:学号:姓名:指导教师:完成日期:xxxxxx大学课程设计报告目录第1章总体设计方案 (1)1.1课程设计的内容和要求 (1)1.2课程设计原理 (1)1.3课程设计思路 (2)1.4实验环境 (2)第2章详细设计方案 (3)2.1硬件电路设计 (3)2.2主程序设计 (4)2.3功能模块的设计与实现独立式按键功能模块 (4)第3章调试及结果分析 (7)3.1调试步骤及方法 (7)3.2实验结果及分析 (7)参考文献 (8)附录一(源程序) (9)附录二(原理图) (13)附录三(元器件清单) (14)第1章总体设计方案1.1课程设计的内容和要求(1)课程设计内容:使用51单片机制作抢答器功能如下:①常规模式主持人按下抢答开始开关,数码管从10S开始倒计时,此时选手可以抢答,若有选手抢答,相应LED亮,单数码管显示其选手号,双数码管从30S开始进行答题倒计时,答题时间到则单数码管闪烁显示选手号5次,再回到初始状态,若时间到但没有人抢答则回到初始状态(所有灯灭,检测主持键是否按下)②违规模式主持人尚在念题还未按下抢答开始开关,某选手违规抢答,则单数码管闪烁显示其选手号5次后回到初始状态。

(2)课程设计要求:①认真完成课程设计任务;②通过老师现场验收;③交出完整的课程设计报告。

1.2 课程设计原理根据题目要求,设计中采用8031芯片、LED灯、数码管和一些独立式按键构成一个简易四路抢答器。

设计中由于数码管扫描延时比较长,采用单片机的内部定时器进行定时,并采用中断方式。

整个抢答器的工作原理是:在正常的供电状态下,开始抢答时利用单片机倒计时,并由单片机将所需要显示的数据送到LED显示器的输入口,当有键按下时则执行相应的键功能程序。

1.3 课程设计思路(1)提出方案根据设计要求,系统采用个独立式开关作为按键,通过单片机不停地扫描P1口来控制LED数码管的显示,当按下启动按键后,经单片机处理,输出控制信号,数码管从10开始进入减计时并在数码管上显示剩余时间,在有选手按下按键时,就会有对应于这个按键的编码在数码管上显示,同时蜂鸣器给出声响来提示主持人和选手;如果在10秒内没有选手抢答,则本次抢答无效,系统封锁输入电路,禁止选手超时抢答。

四路抢答器电路图及说明

作业上交

时间:6月15日截止 上交内容: ①电路板实物 ②电子版Protel图

评分标准

原理图:10% PCB图:40% 电路板制作:50% ☆注: 1. 每组自己绘图,不得互相抄袭。 2. 电路板必须用自己绘制的PCB图进行制作, 不得用别组的图制作。

期终练习

实用电路板的绘制与制作—— 四路抢答器

原理图

功能简介

该抢答器电路可以同时进行四路抢答。按 键按下后,蜂鸣器发声,同时数码管显示 优先抢答者的号数。抢答成功后,再按按 键,显示不会改变,除非按复位键。

复位后,显示清零,可继续抢答,S1—S4为 抢答键,S5为复位键。

元件清单

序号 1 2 3 4 元件名称 集成电路芯片 IC座 数码管 二极管 规格型号 CD4511 16Pin 0.56寸共阴极 N4148 15 数量 1 1 DS1 D1—D7 元件标识 U2

8. 给焊盘补泪滴。

9. 绘制完成后,进行DRC校验。校验无误后,再对照原理 图对每个网络和引脚的连线进行仔细检查。

10. 制作电路板。

包括:打印PCB图,PCB图的热转印,腐蚀,打磨,打孔, 焊接。

11. 电路板测试。

注意事项: 1. 本板电源电压为:直流电5—6V,接电时注意区 分正负极,切不可超出电压范围。 2. 请不要在带电状态下插拔芯片CD4511,插拔该 芯片时注意芯片的方向。

5

6

三极管

电阻

9013

330Ω 2.2KΩ

1

7 1

Q1

R7—R13 R6

10KΩ

100KΩ 7 8 电解电容 5V有源蜂鸣器 10uF 直径12mm

四路竞赛抢答器设计·PPT

RS触发器分三种:基本RS触发器、 同步RS触发器、主从RS触发器。 74ls279是四个基本RS触发器,输入 的是R非、S非。当S非端输入0,R 非端输入0,则Q为1。当S非端输入 0,R非端输入1,则Q为1。当S非端 输入1,R非端输入0,则Q为0。S非 端输入1,当R非端输入1,则Q为保 持。

单稳态触发器 无触发信号时电路工作在稳定 状态,当UI受到下降脉冲时, 触发器由0变为1,但此状态不 稳定,会根据电阻与电容的大 小回复稳定状态。根据此特点 来作为此电路中的定时器。

多谐振荡器 在电容UC充电与放电的过程与 比较器C1在1、0之间跳变的过 程的作用下,电路会在两个暂稳 态之间来回翻转—振荡,因此产 生矩形脉冲。根据此特点为此电 路产生秒脉冲。

四路竞赛抢答器设计

设计人:杨翔 樊明 班级:162903

设计要求

• 该电路的根本任务是准确的判断出第一抢答者 的信号并将其锁存。实现这一功能可用触发器 和锁存器等。在得到第一信号后应立即将电路 的输入封锁,即使其他组再次发出抢答信号也 无效。同时还必须注意,第一抢答信号应该在 主持人发出抢答命令之后才有效。当电路形成 第一抢答信号之后,用编码、译码及数码显示 电路显示出抢答者的组别,也可以用发光二级 管直接指示出组别。

编号显示器 显示抢答选 手编号

倒计时器控式开 关 由主持人控制

七段数码管译码器驱动 器74LS48

同步十进制可逆计数器 74LS192

555构成的多谐振荡器, 用来产生秒脉冲

74LS192具有:双时钟十进制可逆计数功能;并具有清除 和置数等功能。 A—D :并行数据输入端 QA— QD :数据输出端 UP:加法计数器脉冲输入端 DOWN:减法计数脉冲输入端 CLR:异步置0端(高电平有效) ~LOAD:置数控制端(低电平有效) ~CO:加法计数时,进位输出端(低电平有效) ~BO:减法计数时,借位输出端(低电平有效)

4路抢答器

目录1.绪论 12.电路设计方案及功能分析 2 2.1 设计目的 2 2.2 设计要求 2 2.3 系统基本方案 2 2.4电路详解32.4.1、51系列单片机最小系统 32.4.2、时钟电路 (3)2.4.3、复位电路 4 2.4.4、EA/VPP(31 脚)的功能和接法42.4.5、P0 口外接上拉电阻 (4)2.4.6、上拉电阻 (5)2.4.7、LED驱动电路 62.4.8、数码管 6 2.5电路分析92.6供电模块选择113.系统设计12 3.1 系统框图 (12)3.2 系统原理图 (13)3.3 Proteus 仿真134.系统调试及结果分析 (15)5.总结和体会156.遇到问题 (15)7.参考文献 (15)8.附录 (16)8.1 元件清单..................................... 错误!未定义书签。

8.2 程序161.绪论由于单片机技术在各个领域正得到越来越广泛的应用,世界上许多集成电路生产厂家相继推出了各种类型的单片机,在单片机家族的众多成员中MCS-52系列单片机以其优越的性能、成熟的技术及高可靠性和高性能价格比,迅速占领了工业测控和自动化工程应用的主要市场,成为国内单片机应用领域中的主流。

目前,可用于MCS-52系列单片机开发的硬件越来越多,与其配套的各类开发系统、各种软件也日趋完善,因此,可以极方便地利用现有资源,开发出用于不同目的的各类应用系统。

单片机最小系统是在以MCS-52单片机为基础上扩展,使其能更方便地运用于测试系统中,不仅具有控制方便、组态简单和灵活性大等优点,而且可以大幅度提高被测试的技术指标,从而能够大大提高产品的质量和数量。

单片机以其功能强、体积小、可靠性高、造价低和开发周期短等优点,称为在实时检测和自动控制领域中广泛应用的器件,在工业生产中称为必不可少的器件,尤其是在日常生活中发挥的作用也越来越大。

本毕业设计主要在STC89C52RC单片机上扩展I/O 口,复位电路,晶振电路,LED显示电路,数码管显示电路,蜂鸣器电路。

《简易四路抢答器》

;实战四《简易四路抢答器》;该抢答器供不多于4个参赛队或者个人的抢答比赛场合使用。

每个参赛队的座位前;安装1只抢答按钮开关(用板上的S9、S10、S11、S12)和一个信号灯(D4、D5、D6、D7)。

;主持人座位前装一只复原开关(板上S3)、1只蜂鸣器(板上BUZ1)和一个抢答器工作状态;指示灯(D10),每当主持人口头发出号令之后.哪个队先按下座位上的按钮开关,该座位的信;号灯就先被点亮,同时封锁其他按钮开关的活动.并且熄灭主持人座位上的状态指示灯和发出;三声类似于电话振铃的提示声,以声明此次抢答动作已经完成.在主持人确认后,按下复原按钮;,状态指示灯重新点亮,并且同时发出"笛-笛-"声,为下一次抢答作好准备.;PIC单片机学习网陈学乾 ;程序文件名:"MCD-INTBUZ.ASM";******************************************************************** *;程序清单;******************************************************************** *tmr0 equ 1h ;定义定时器/计数器0寄存器地址status equ 3h ;定义状态寄存器地址option_reg equ 81h ;定义选项寄存器地址option_temp equ 0a6h ;(在BACK1)定义选项寄存器的备份寄存器的地址intcon equ 0bh ;定义中断控制寄存器地址portc equ 7h ;定义端口RC的数据寄存器地址trisc equ 87h ;定义端口RC的方向控制寄存器地址portb equ 06h ;定义端口RB的数据寄存器地址trisb equ 86h ;定义端口RB的方向控制寄存器地址c equ 0 ;定义进位标志位的位地址z equ 2 ;定义0标志位的位地址w equ 0 ;定义传送目标寄存器为W的指示位f equ 1 ;定义传送目标寄存器为RAM的指示位t0if equ 2 ;定义TMR0中断标志位的位地址t0ie equ 5 ;定义TMR0中断使能位的位地址inte equ 4 ;定义外部中断使能位的位地址intf equ 1 ;定义外部中断标志位的位地址count equ 20h ;定义一个计数器变量count1 equ 24h ;定义一个计数器变量count2 equ 25h ;定义一个计数器变量count3 equ 27h ;定义一个计数器变量count4 equ 28h ;定义一个计数器变量portb_b equ 21h ;为PORTC定义一个备份寄存器w_temp equ 7fh ;为W在体0和体1定义2个备份寄存器;w_temp equ 0ffh ;(若是16F873/4,则需保留FFH单元)status_temp equ 23h ;为STATUS定义一个备份寄存器rp0 equ 5h ;定义状态寄存器中的页选位RP0;******************复位向量和中断向量***********************org 000h ;nop ;设置一条ICD必须的空操作指令goto main ;org 0004h ;goto serv ;跳转到中断服务子程序;*******************主程序************************************mainbsf status,rp0 ;movlw 0 ;movwf trisc ;设置RC口全部为输出movlw 0ffh ;movwf trisb ;设置RB口全部为输入movlw 02h ;设置选项寄存器:上拉电阻启用;INT下降沿触发movwf option_reg ;分频器给TMR0;分频比1:8bcf status,rp0 ;movlw 90h ;movwf intcon ;开发INT中断clrf portc ;RC口灯全灭loopmovf portb,w ;读取RB口数据iorlw b'11100001' ;送RB口的数到备份寄存器并将除S9、S10、S11、S12以外的位全部送1movwf portb_b ;xorlw 0ffh ;没有键按下转LOOP继续检测btfsc status,z ;goto loop ;call delay10ms ;防抖动廷时movf portb,w ;iorlw b'11100001' ;xorwf portb_b,0 ;再次读取RB口的数据,与前一次读的数相同则键值有效btfsc status,z ;goto loop ;comf portb_b,w ;取反以便使被按下按键的位为1,其它位为0movwf portc ;送RC口显示call tone3t ;调用发声三次子程序loop1comf portb,w ;检测按键是否有松开andlw b'00011110' ;btfsc status,z ;goto loop ;松开了返回goto loop1 ;没松开继续检测;*********************中断服务子程序***************************** serv;********************保存护现场部分*******************************movwf w_temp ;保护Wswapf status,w ;保护STATUSclrf status ;选择体0movwf status_temp ;将STATUS存入体0的备份寄存器;********************* 调查中断源********************************** btfsc intcon,intf ;检查不是INT中断,返回goto intserv ;是!转到INT中断处理部分goto retfie0 ;;*********************INT中断处理部分****************************** intservclrf portc ;令全部灯熄灭bsf portc,7 ;点亮D10,表示就绪call tone630 ;调用高音子程序call delay ;调用1S廷时子程序call tone630 ;调用低音子程序bcf intcon,intf ;清除INT中断标志位;*************************恢复现场部分***************************** retfie0swapf status_temp,w ;恢复STATUSmovwf status ;swapf w_temp,f ;恢复Wswapf w_temp,w ;retfie ;中断返加;*************************低音调发生子程序(500HZ/50MS)************* tone500movlw .50 ;循环次数寄存器赋初值movwf count ;50=500HZx0.05Sx2t5lopbcf intcon,t0if ;清除TRM0溢出中断标志位movlw .131 ;给TMR0装入初值256-125=131movwf tmr0 ;启动定时器t5herebtfss intcon,t0if ;定时器溢出否goto t5here ;否!循环栓测movlw b'01000000' ;只将BIT6置位xorwf portc,f ;只将RC6(BUZ)脚电平反转,其余不变decfsz count,f ;循环次数递减,为0,跳一步goto t5lop ;不为0,跳回return ;返回;**************************高音调发生子程序(630HZ/50MS)*****************tone630movlw .63 ;循环次数寄存器赋初值movwf count1 ;63=630HZx0.05Sx2t6lopbcf intcon,t0if ;清除TRM0溢出中断标志位movlw .157 ;给TMR0装入初值157=256-99movwf tmr0 ;启动定时器t6herebtfss intcon,t0if ;定时器溢出否goto t6here ;否!循环栓测movlw b'01000000' ;只将BIT6置位xorwf portc,f ;只将RC6(BUZ)脚电平反转,其余不变decfsz count1,f ;循环次数递减,为0,跳一步goto t6lop ;不为0,跳回return ;返回;*********************发声1S子程序(1S=10x(50ms+50ms)*********** tonelsmovlw .10 ;循环次数寄存器赋初值movwf count2 ;t1lopcall tone500 ;调用低音子程序call tone630 ;调用高音子程序decfsz count2,f ;循环次数递减,为0,跳一步goto t1lop ;不为0,跳回return ;返回;*********************TMR0廷时子程序1S(1S=16x256x(256-12)US)******** delaybsf status,rp0 ;设置文件寄存器体1movf option_reg,w ;保护选项寄存器内容movwf option_temp ;movlw 07h ;重设选项寄存器;上拉电阻启用,INT 下降沿触发movwf option_reg ;分频器给TRM0;分频比值设为1:256 bcf status,rp0 ;恢复到文件寄存器体0movlw .16 ;循环利用TMROP定时16次movwf count3 ;溢出次数寄存器d1lopbcf intcon,t0if ;清除TMR0溢出中断标志位bcf intcon,t0ie ;清除TMR0溢出中断使能位movlw .12 ;给TMR0装入初值12=256-244movwf tmr0 ;启动定时器herebtfss intcon,t0if ;用查询法检测TMR0溢出否goto here ;否!返回decfsz count3,f ;是!溢出次数减1,为0,跳一步goto d1lop ;否!循环利用TMR0bsf status,rp0 ;设置文件寄存器体1movf option_temp,w ;恢复选项寄存器内容movwf option_reg ;bcf status,rp0 ;恢复到文件寄存器体0return ;返回;*************************断续发声3次报警子程序***********************tone3tmovlw .3 ;循环次数寄存器赋初值movwf count4 ;t3lopcall tonels ;调用发声1S子程序call delay ;调用廷时1S子程序decfsz count4,f ;循环次数递减,为0,跳一步goto t3lop ;不为0,跳回return ;返回;**************************软件廷时10MS子程序****************************delay10msmovlw .13 ;将外层循环参数值送到30Hmovwf 30h ;lp0movlw 0ffh ;将内层循环参数值送到31Hmovwf 31h ;lp1decfsz 31h,1 ;变量31H内容递减,若为0则跳跃 goto lp1 ;跳转到LP1decfsz 30h,1 ;变量30H内容递减,若为0则跳跃 goto lp0 ;跳转到LP0return ;返回主程序end ;源程序结束;***************************************************; 进入该实战演练的工序流程如下:; 1.创建源文件和编辑源文件;在此介绍一种不同于前面讲的创建源文件的方法,用Windows附件中的”记事本”; 这个为大家所熟知和好用的文件编辑器,并且可以方便的加入中文注释.不过有两点需要注意,一是注释前面的; 分号”;”必须用西文半角输入;二是必须用”.asm”扩展名存储到事先建立的一个专用子目录下.; 2.打开MPLAB集成开发环境:首先在WINDOWS环境下,选用开始>程序>Microchip MPLAB>MPLAB命令,启动MPLAB; 并进入MPLAB的桌面.; 3.创建项目:选用菜单File>New或Project>New Project,在事先建立的一个专用子目录下创建一个新项目,将; 用记事本创建的源文件加入到该项目中.; 4.建立项目中的目标文件:选择菜单Project >Build All(项目>建立所有文件),MPLAB将自动调用MPASM将项目; 文件管理下的源文件(.asm)汇编成十六进制的目标文件(.hex).; 5.ICD参数设置:通过菜单命令Project>Edit Project或者Option>Development Mode,将开发模式设置为; ”MPLAB ICD Debugger”,点击OK按钮,打开ICD的工作窗口,在调试阶段,可以按照说明书图2-10设置各项,但需注意; OSCILLATOR应设置为XT方式,尤其需要说明的是,选中“Enable Debug Mode”(使能调试模式)选项,在向目; 标单片机烧写机器码程序时,会将调试临控程序同时写入单片机的指定程序存储器区域,然后才允许用ICD方式调试。

四路抢答器

摘要:本文主要介绍了多路智力竞赛抢答器。

它是由主体电路和扩展电路组成。

主体电路由抢答电路、定时电路组成。

优先编码电路、锁存器、译码电路将各输入信号在显示器上输出,用控制电路和主持人开关启动报警电路,以上为主体电路工作原理。

通过译码电路将秒脉冲信号在显示器上输出实现计时功能,构成扩展电路。

数电课程设计的编写是以实际动手研究为主线,以科学研究所研究到的所应用的实际技术为主要内容。

培养学生掌握电子技术的科学规律、技术,测量技术等研究方法使其具有独立动手研究的能力,以便在未来的工作中开拓创新。

抢答器是一种能使任何比赛及竞争性的游戏体现公平、公正的电子装备。

在比赛中为了准确、公正、直观地判断出第一抢答者,所设计的抢答器通常由数码显示指示出第一抢答者。

同时还应设计记分、犯规和奖惩记录等多种功能。

为了全面运用科学动手研究的技术方法,在加强的直接动手方法的同时,力求让我们在短时间里得以掌握先进科学技术:如本设计中所使用到的Protel99等技术手段,新工具。

也培养了自己理论联系实际、设计电路的能力及正确的的处理数据、分析。

本文主要介绍了数字电子技术是一门应用性很强的专业基础课,主要任务是在传授有关数字电子技术基本知识的基础上,培训分析和设计数字电路的能力。

为了更好地把理论教学和实践有机地结合在一起,让我们进一步的掌握数字电子技术的知识、提高电子电路设计、分析、制作和调试的基本技能,在课程中特意安排了数字电子技术实习。

关键词抢答器、锁存电路、编码电路、译码电路、数码显示目录一、设计任务及要求 (3)1.1任务 (3)1.2要求 (3)1.2. 1基本要求 (3)1.2.2扩展要求 (3)二、设计方案 (3)2.1电路的设计 (2)三、设计原理及实现 (4)3.1元器件清单 (4)3.2 电路的工作工程及其原理图 (4)3.3主要芯片的功能和工作原理 (5)四、电路制作与调试 (6)4.1电路制作及其PCB图 (6)4.2 电路调试 (7)五、设计结论及体会 (8)参考文献 (8)一、设计任务及要求1.1、任务:用元器件及印刷电路板设计并制作一个多路智力竞赛抢答器。

基于MCS51单片机的四路抢答器课件

程序流程图如下

电路原理图及PCB制版图

四路智力抢答器电路原理图

四路智力抢答器PCB模块

程序设计

▪ 抢答器工作过程如下

▪ · 首先主持人选定倒计时时间,单片机扫描U3以 获取此信息。如果没有人为设置,默认为10s。

▪ · 在按下抢答按键之前,3个数码管全部显示“0”。

▪ · 按下抢答按键之后,蜂鸣器响一声,单片机开 始倒计时,数码管U6和U7显示倒计时时间,数 码管U8显示“0”。

▪ void send_data(uchar);

▪ uchar set_time(void); 时时间

▪ bit control_key(void); 是否按键

▪ uchar get_key_num(void); 个参赛者按键

▪ void display_time(void); 时剩余时间

//初始化MAX7219 //向控制寄存器写数

▪ 完成上述功能的电路包括时间设定开关、声光显 示、按键控制以及按键锁存等部分

各模块功能

▪ 单片机部分 ▪ 时间设定模块 ▪ 按键模块 ▪ 数码管显示模块 ▪ 蜂鸣器模块

单片机部分

▪ 通过读取P3.7~P3.3 的状态决定倒计时时 间;通过读取P1.3~ P1.0的状态读取按键 情况;通过P2.4~ P2.2控制显示模块以 显示按键者的号码和 倒计时所剩时间;通 过P0.1控制蜂鸣器

key_flg=1;

//设置有人按键答题标志

TR0=0;

//停止T0运行

}

else

//否则循环检测

{

display_time();

//并显示剩余时间

continue;

}

}

if(key_flg==1)

四路抢答器(详图)

目录一、实验目的 (3)二、设计要求与内容 (3)三、设计原理3.1总体设计方案 (3)3.1.1设计思路 (3)3.1.2总电路框图 (3)3.2各模块设计方案及原理3.2.1抢答器 (3)3.2.2计时器 (5)四、电路仿真4.1倒计时电路 (6)4.2抢答器 (6)五、实验结果与析 (7)六、主要元器件 (8)七、实习总结 (9)四路数字抢答器一、实验目的结合我们所学的有关电子线路课程,综合实现四路抢答器的设计。

二、设计要求与内容(1)要求实现ABCD四路抢答器的设计,每一组都具有独立的抢答按键,要求某路抢答后,其他三路抢答无效;(2)某路抢答信号到达后,指示该路已抢答的独立灯发光,发出提示音,并用数码管显示抢答的组号(以ABCD表示);(3)裁判桌上的公共通道号显示(以ABCD表示);(4)抢答时间的定时与报警,具体实现可自拟。

扩展内容:①记录某路的抢答次数或抢到得次数;②记录某路的分数;③路数的扩展。

三、设计原理及过程3.1总体设计方案3.1.1设计思路①要准确判断出第一抢答者的信号并将其锁存,实现这一功能可选择使用触发器或锁存器等。

得到第一信号后其他组的抢答信号无效,并且第一信号在主持人发出抢答命令后才有效。

②第一信号发出后,用编码、译码及数码显示电路显示抢答者的组别,发光二极管亮。

③主持人按下抢答按钮后,开始30秒倒计时,在此时间内抢答有效,若30秒内无人抢答,主持人清零后开始新一轮抢答。

3.1.2总电路框图3.2各模块设计方案及原理3.2.1抢答电路抢答电路实现选手抢答并锁存,同时发光二极管发光,数码显示。

使用优先编码器74LS148和锁存器74LS279来完成。

该电路主要完成两个功能:一是分辨出选手按键的先后,并锁存优先抢答者的编号,同时译码显示电路显示编号(采用七段数字数码显示管);二是禁止其他选手按键,其按键无效。

工作过程:开关S 处于清除端时,RS 触发器R 、S 端均为0,使译码器74LS48的优先编码工作标志端位0,处于工作状态。

四路抢答器(完全版)

华北科技学院课程设计说明书班级:电子B071 姓名:郭亚立设计题目:四路智能抢答器设计时间:2010.1.9 至2010.1.22 学号:200703014138指导教师:杜志伟评语:评阅成绩:评阅老师:四路抢答器设计报告目录一、设计任务和要求:.................................................................................................... - 4 -1.1设计任务 (4)1.2设计要求 (4)二、设计方案的选择与论证............................................................................................. - 5 -2.1方案的选择、论证 (5)2.2设计总方案 (5)三、电路设计计算与分析.................................................................................................. - 6 -3.1抢答器控制电路设计 (6)3.1.1 优先编码器74LS148 ..................................................................................................... - 9 -3.1.2 锁存器74LS279............................................................................................................. - 10 -3.1.3 74LS121单稳态触发器:.......................................................................................... - 11 -3.2定时时间电路的设计.. (11)3.2.1 计数器74LS192............................................................................................................. - 14 -3.3控制电路和报警电路.. (15)3.3.1 振荡电路.......................................................................................................................... - 19 -3.4整体仿真 (21)四、总结及心得............................................................................................................. - 22 -五、附录...................................................................................................................... - 24 -5.1主要元器件列表 (24)5.2总原理图 (25)六、参考文献 ................................................................................................................ - 26 -一、设计任务和要求:1.1设计任务设计一台可供4名选手参加比赛的智力竞赛抢答器。

四路抢答器报告(最终版)

设计报告课程名称 EDA技术实用教程任课教师黄慧设计题目数字式竞赛抢答器班级 12自动化卓越班姓名学号李思聪 1205032033郭一鸣 1205031020孔德利 1205031026 日期 2014年11月11日一、设计目的1、学习使用实验箱中数码管显示、按键控制。

2、熟悉抢答器的工作原理。

3、了解数字系统设计,调试及故障排除方法。

二、设计要求1、四组参赛者进行抢答,当抢答组按下抢答按钮时,抢答器能准确的判断出抢答者。

2、抢答器可以容纳4组参赛者同时抢答,每组设置1个按钮供抢答者使用。

设置抢答使能信号,当此信号有效时,若参赛者按下抢答开关,则抢答器能判断出第一抢答者并指示该组抢答成功,其他组参赛者的抢答开关不起作用,若提前抢答则对相应的参赛者发出警报。

3、系统具有清零功能。

当清零信号有效时,抢答器对前一轮抢答的第一抢答者判断结果进行清零,恢复为初始状态。

4、数字式竞赛抢答器电路还具有计分功能。

如果抢答成功的参赛者满足得分条件则增加相应的分数,答错不扣分。

三、电路的总体方案及工作原理1、总体方案(1)方案一系统由三个主要模块组成,分别为第一判别电路、计分电路、显示电路。

其中第一判断电路主要完成最快抢答者的判断功能;计分电路则存储每组的分数,显示电路则显示抢答者的状态和各组的分数。

因此数字竞赛抢答器的输入信号包括复位信号CLR、抢答器使能信号EN、4级参赛者抢答按钮A\B\C\D及加分信号ADD,输出信号包括4组参赛者的状态显示LEDx(x表示参赛者编号)及其对应的得分SCOREx、抢答器抢答成功的组别显示等。

(2)方案二抢答电路选用优先编码器 74LS148 和锁存器 74LS297 来完成。

该电路主要完成两个功能:一是分辨出选手按键的先后,并锁存优先抢答者的编号,同时译码显示电路显示编号(显示电路采用七段数字数码显示管);二是禁止其他选手按键,其按键操作无效。

定时电路原理及设计:该部分主要由555定时器秒脉冲产生电路、十进制同步加减计数器74LS192减法计数电路、74LS48译码电路和1个7段数码管即相关电路组成。

四路抢答器——精选推荐

四路抢答器电子技术课程设计一.设计任务与要求3 目录二.四人抢答电路构成框图3三.选择器件及器件介绍4四.功能模块7五.设计电路图10六.心得体会12四人抢答电路一.设计任务与要求:设计一个4路抢答电路。

具体要求如下:1用JK触发器和门电路设计一个四路抢答电路。

2每个参赛者控制一个按钮,用按动按钮发出抢答信号。

3裁判有一个总按钮开关,用于将抢答器清零复位。

4竞赛开始后,先按动按钮者将对应的一个发光二极管点亮,此后其他三人再按动按钮对电路不起作用。

二.总体框图:这里组合逻辑电路用JK触发器,并将JK端接高电平,使之成为T触发器,选手通过控制开关可以将时钟信号加到JK触发器的时钟信号端,JK触发器的输出端连小灯泡,当有信号时,使灯亮,达到抢答效果。

主持人控制各JK触发器的异步清零端,可以将小灯泡熄灭。

附加右侧门电路,使一旦有灯亮,就封锁所有触发器的时钟信号,使其余的灯泡不再亮,从而实现一个选手率先按下开关后这个选手对应的灯亮,其他人再按按钮,对电路没有影响,即满足“竞赛开始后,先按动按钮者将对应的一个发光二极管点亮,此后其他两人再按动按钮对电路不起作用”的要求。

三.选择器件及器件介绍:(一)所选器件(表一)(二)器件介绍:(1) JK触发器:1.凡在时钟信号作用下逻辑功能符合如下特性表所规定的逻辑功能者,无论其触发方式如何,均称为JK触发器。

(表二)2.JK触发器的特性方程:3.JK触发器的状态转换图:4.主从JK触发器,是为了解决主从RS触发器中R,S之间有约束的问题而设计的.图(a)所示是主从JK触发器的逻辑电路图,是在主从RS触发器基础上,把..引回到门..的输入端,把Q引回到门..的输入端得到的.原来的S 变成为J,R变成为K,由于主从结构的电路形式未变,而输入信号变成了J和K,故名主从JK触发器.(a)(b) (c)(a)逻辑电路图(b)曾用符号(c)国标符号图(b)是人们曾用的逻辑符号,CP端的小圆圈表示只有当CP下降沿到来时,触发器的Q端和..才会改变状态.图(c)所示是国家标准规定的逻辑符号,方框内的符号..表示延迟,因图(a)所示主从JK触发器在时钟脉冲上升沿时刻就把输入信号接收进去,但是直至CP下降沿到来时,Q端和..端才会改变状态.5.JK触发器工作原理:下面分四种情况来分析主从型JK触发器的逻辑功能。

四路抢答器电路组成及工作原理(含电路图)

62电路组成及工作原理图l 四路竞赛抢答器原理图1.抢答器电路原理:如图2, 101, 102, 103, 104分别为抢答器按钮的输入端,开始抢 答,假设101抢答成功,通过四D 触发器输出QE ,QUO,而 Q2,=Q3=Q 『4通过四输入与非门后,输出高电平,再经过反相器输出 低电平,再经过两输入与非门,输出低电平,此时四D 触发器处于保 持状态,并且其他按钮的输入不起作用,101的抢答信号被锁存。

此 时LED1发光并且蜂鸣器发出响声。

其他抢答按钮同理。

J3 Key = CJ4 Key = D士BUZZER____ mnc 4 1000 Hz四路竞赛抢答器总电路原理图如图1所示。

I RR15Key = A30 OGKey = B30 OGVCCLlJGtwR3 A^Ar- 30 OCY OR1 VW- 300C-计教电珞22HEX图2抢答器部分电路图2 •计时电路原理:计时电路为两片74LS160用置数法构成的31进制计数器,因为可以 为了让答题者直观的看到30S 这个时间点,所以设置了 31进制的计数 器。

两片的四个输入端均接低电平,两片的输出端分别接七段译码管 直接显示数字,高位的74LS160芯片的QiQ 接到一个二输入的与非门(U8A)输出到计数器的LD 端、三输入与非门端、反相器端。

输出到 LD端是为了构成31进制计数器,当高位变为3时,计数器置0。

输出到三:::R5: r —^r^ :Ui6A74LS86D1mQ—W/—1 ::M :: :::R7:::—W _i?必務箝嗪曲o1011:□VCC..U19A..IE上174HC0BNJ105 :啤 -Tior. lezl 715^DC DHEX 741SQ0D二二 UiX [—[_•> ::迪妙贰P- • - •••2U13A输入与非门(U9A)和时钟脉冲、开关的电平信号一起输入到与非门中,这就是为什么能控制计时的开始与暂停了,当开关输入低电 平时,无论是否有时钟信号,时钟均不发生改变,此时时钟信号为无 效信号;而当开关输入高电平时,U8A 输出也为高,因此,时钟信号 为有效信号,因此,凭借这样的类似锁存的电路,就可以控制计时的 开始与暂停。

智能四路抢答器(完)讲解

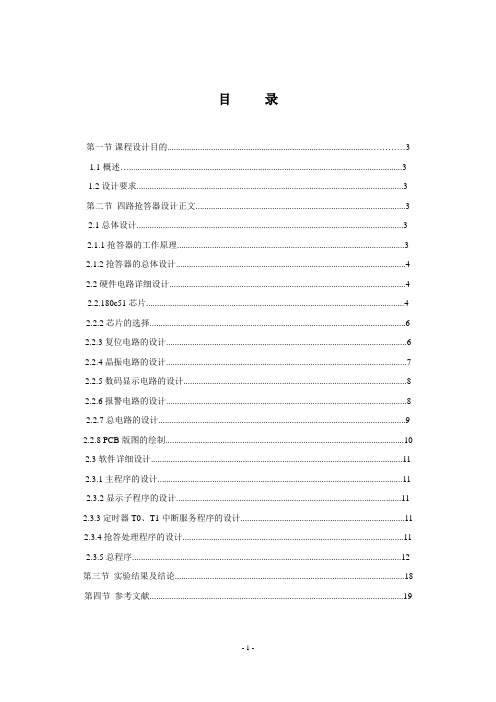

目录第一节课程设计目的 (3)1.1概述 (3)1.2设计要求 (3)第二节四路抢答器设计正文 (3)2.1总体设计 (3)2.1.1抢答器的工作原理 (3)2.1.2抢答器的总体设计 (4)2.2硬件电路详细设计 (4)2.2.180c51芯片 (4)2.2.2芯片的选择 (6)2.2.3复位电路的设计 (6)2.2.4晶振电路的设计 (7)2.2.5数码显示电路的设计 (8)2.2.6报警电路的设计 (8)2.2.7总电路的设计 (9)2.2.8 PCB版图的绘制 (10)2.3软件详细设计 (11)2.3.1主程序的设计 (11)2.3.2显示子程序的设计 (11)2.3.3定时器T0、T1中断服务程序的设计 (11)2.3.4抢答处理程序的设计 (11)2.3.5总程序 (12)第三节实验结果及结论 (18)第四节参考文献 (19)第一节课程设计目的1.1概述单片机原理及应用课程设计是学生综合运用所学知识,全面掌握单片微型计算机及其接口的工作原理、编程和使用方法的重要实践环节。

通过独立或协作提出并论证设计方案,进行软、硬件调试,最后获得正确的运行结果,可以加深和巩固对理论教学和实验教学内容的掌握,进一步建立计算机应用系统整体概念,初步掌握单片机软、硬件开发方法,为以后进行实际单片机软、硬件应用开发奠定良好的基础。

课程设计的主要内容:根据单片机原理及应用课程的要求,主要进行两个方面的设计,即单片机最小系统和接口技术应用设计。

其中,单片机最小系统主要要求学生熟悉单片机的内部结构和引脚功能、引脚的使用、复位电路、时钟电路、4个并行接口和一个串行接口的实际应用,从而可构成最小应用系统,并编程进行简单使用。

接口技术应用设计主要要求学生能综合运用单片机、存储器、常用接口芯片构成单片机应用系统,有针对性地进行软、硬件设计与开发。

1.2 设计要求:1、设置4个抢答台和四个抢答成功指示灯,1个比赛主持人开始按键和1个抢答指示灯及1个LED显示器。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

华北科技学院课程设计说明书班级:电子B071 姓名:郭亚立设计题目:四路智能抢答器设计时间: 2010.1.9 至 2010.1.22 学号: ************ 指导教师:***评语:评阅成绩:评阅老师:四路抢答器设计报告目录一、设计任务和要求: ................................................................................................................... - 3 -1.1设计任务 (3)1.2设计要求 (3)二、设计方案的选择与论证 ........................................................................................................... - 4 -2.1方案的选择、论证 (4)2.2设计总方案 (4)三、电路设计计算与分析 ................................................................................................................. - 5 -3.1抢答器控制电路设计 (5)3.1.1 优先编码器74LS148 ..................................................................................................... - 7 -3.1.2 锁存器74LS279 ............................................................................................................ - 9 -3.1.3 74LS121单稳态触发器:.......................................................................................... - 10 -3.2定时时间电路的设计 (10)3.2.1 计数器74LS192 ............................................................................................................ - 12 -3.3控制电路和报警电路 (13)3.3.1 振荡电路....................................................................................................................... - 17 -3.4整体仿真 (19)四、总结及心得............................................................................................................................... - 20 -五、附录......................................................................................................................................... - 22 -5.1主要元器件列表 (22)5.2总原理图 (23)六、参考文献................................................................................................................................... - 24 -一、设计任务和要求:1.1设计任务设计一台可供4名选手参加比赛的智力竞赛抢答器。

用数字显示抢答倒计时间,由“9”倒计到“0”时,无人抢答,蜂鸣器鸣响。

选手抢答时,数码显示选手组号,同时蜂鸣器鸣响,倒计时停止。

1.2设计要求1)4名选手编号为:1,2,3,4。

各有一个抢答按钮,按钮的编号与选手的编号对应,也分别为1,2,3,4。

2)给主持人设置一个控制按钮,用来控制系统清零(抢答显示数码管灭灯)和抢答的开始。

3)抢答器具有数据锁存和显示的功能。

抢答开始后,若有选手按动抢答按钮,该选手编号立即锁存,并在抢答显示器上显示该编号,同时扬声器给出音响提示,封锁输入编码电路,禁止其他选手抢答。

抢答选手的编号一直保持到主持人将系统清零为止。

抢答器具有定时(15秒)抢答的功能。

4)当主持人按下开始按钮后,定时器开始倒计时,定时显示器显示倒计时间,若无人抢答,倒计时结束时,扬声器响。

参赛选手在设定时间(15秒)内抢答有效,抢答成功,扬声器响,同时定时器停止倒计时,抢答显示器上显示选手的编号,定时显示器上显示剩余抢答时间,并保持到主持人将系统清零为止。

5)如果抢答定时已到,却没有选手抢答时,本次抢答无效。

系统扬声器报警,并封锁输入编码电路,禁止选手超时后抢答,时间显示器显示0。

6)用石英晶体振荡器产生频率为1Hz的脉冲信号,作为定时计数器的CP信号。

二、设计方案的选择与论证2.1方案的选择、论证方案一:用一片四D触发器74LS175和四输入2或非门CD4002实现。

四D 触发器输出经四输入或非门到四路抢答按键开关,加到触发器的四个输入端,同时经四输入或非门和反相器作为四D触发器的时钟信号,四D触发器清零端经上拉电阻接电源,同时经过清零控制开关到地。

电路简单成本低,稍加扩展就能达到实用化。

方案二:用一片八线-三线优先编码器74LS148、四RS触发器74LS279和七段译码器74LS48实现数显四路(八路)抢答器,电路稍显复杂,但功能较完善。

方案一电路简单能够满足要求,但是由于需要4个4D触发器,接线繁琐,增加了电路设计与仿真的难度,方案二用集成器件,电路减小了体积,提高了稳定性,并且可以应用EDA软件仿真、调试,易于进行功能扩展。

故采用方案二设计。

2.2设计总方案本设计电路主要由控制电路、脉冲产生电路、锁存电路、编码及译码显示电路、倒计时电路和报警产生电路组成。

如图1所示为总体方框图。

其工作原理为:接通电源后,主持人将开关拨到"清零"状态,抢答器处于禁止状态,编号显示器灭灯,定时器显示设定时间;主持人将开关置;开始"状态,宣布"开始"抢答器工作。

定时器倒计时。

选手在定时时间内抢答时,抢答器完成:优先判断、编号锁存、编号显示。

当一轮抢答之后,定时器停止、禁止二次抢答、定时器显示剩余时间。

如果再次抢答必须由主持人再次操作"清除"和"开始"状态开关。

图1.四人智力竞赛抢答器框图三、电路设计计算与分析3.1抢答器控制电路设计设计电路见图2所示。

电路选用优先编码器 74LS148 和锁存器 74LS279 来完成。

抢答器控制电路是抢答器设计的关键,它要完成以下三项功能:1)当参赛选手按动抢答键时,扬声器发声,抢答电路和定时电路停止工作,同时译码显示电路显示编号(显示电路采用七段数字数码管显示)。

2)当设定的抢答时间到,无人抢答时,扬声器发声,同时抢答电路和定时电路停止工作。

3)当主持人清零后,可再次进行抢答。

工作过程:开关J5置于“清除”端时,RS触发器的 R、S端均为0,4个触发器输出置0,使74LS148的优先编码工作标志端(图中5号端)=0,使之处于工作状态。

当开关J5断开,J6置于“开始”时,抢答器处于等待工作状态,当有选手将抢答按键按下时(如按下J2),74LS148的输出经RS锁存后,CTR = 1,RBO(图中4端) =1,七段显示电路74LS48处于工作状态,4Q3Q2Q = 010,经译码显示为“2”。

此外,CTR=1,使74LS148 优先编码工作标志端(图中2号端)=1,处于禁止状态,封锁其他按键的输入。

当按键松开即按下时,74LS148的此时由于仍为CTR=1,使优先编码工作标志端为1,所以74LS148仍处于禁止状态,确保不会出二次按键时输入信号,保证了抢答者的优先性。

如有再次抢答需由主持人将J5开关重新置“清除”然后才可能进行。

仿真结果3.1.1优先编码器74L S14874LS148为8线-3线优先编码器,表3.1.1为其真值表,下图为其管脚图。

Y 1Y 2Y EXY s Y 97614154801234567874LS148161514131211109I 4I 5I 6I 7S (E )Y 2Y 1GN D V CC Y S Y EX I 3I 2I 1I 0Y 0(b )74LS148管脚图表3.1.1 74LS148 8线—3线二进制编码器真值表74LS148工作原理如下:该编码器有8个信号输入端,3个二进制码输出端。

此外,电路还设置了输入使能端EI ,输出使能端EO 和优先编码工作状态标志GS 。

当EI=0时,编码器工作;而当EI=1时,则不论8个输入端为何种状态,3个输出端均为高电平,且优先标志端和输出使能端均为高电平,编码器处于非工作状态。

这种情况被称为输入低电平有效,输出也为低电来有效的情况。

当EI 为0,且至少有一个输入端有编码请求信号(逻辑0)时,优先编码工作状态标志GS 为0。

表明编码器处于工作状态,否则为1。

由功能表可知,在8个输入端均无低电平输入信号和只有输入0端(优先级别最低位)有低电平输入时,A2A1A0均为111,出现了输入条件不同而输出代码相同的情况,这可由GS的状态加以区别,当GS=1时,表示8个输入端均无低电平输入,此时A2A1A0=111为非编码输出;GS=0时,A2A1A0=111表示响应输入0端为低电平时的输出代码(编码输出)。

EO只有在EI为0,且所有输入端都为1时,输出为0,它可与另一片同样器件的EI连接,以便组成更多输入端的优先编码器。

从功能表不难看出,输入优先级别的次为7,6,……,0。

输入有效信号为低电平,当某一输入端有低电平输入,且比它优先级别高的输入端无低电平输入时,输出端才输出相对应的输入端的代码。

例如5为0。

且优先级别比它高的输入6和输入7均为1时,输出代码为010,这就是优先编码器的工作原理。

3.1.2锁存器74L S279原理:在74ls279中,由于4回路中2回路置位端子为两个,所以使用其一时,整理两个置位输入作为1个使用,或将另一个输入固定为“H”使用。