CD4060秒脉冲的产生电路

CD4060

(一)秒时钟信号的产生1.振荡器1) 晶体振荡器晶体振荡器电路给数字钟提供一个频率稳定准确的32768Hz的方波信号,可保证数字钟的走时准确及稳定。

晶体振荡器是构成数字式时钟的核心,它保证了时钟的走时准确及稳定。

数字钟的精度主要取决于时间标准信号的频率及其稳定度。

晶体具有较高的频率稳定性及准确性,从而保证了输出频率的稳定和准确因此,一般采用石英晶体振荡器经过分频得到这一信号。

2) 振荡电路如图2所示电路通过CMOS非门构成的输出为方波的数字式晶体振荡电路。

这个电路中,CMOS非门U1与晶体、电容和电阻构成晶体振荡器电路,U2实现整形功能,将振荡器输出的近似于正弦波的波形转换为较理想的方波。

输出反馈电阻R1为非门提供偏置,使电路工作于放大区域,即非门的功能近似于一个高增益的反相放大器。

电容C1、C2与晶体构成一个谐振型网络,完成对振荡频率的控制功能,同时提供了一个180度相移,从而和非门构成一个正反馈网络,实现了振荡器的功能。

晶体XTAL的频率选为32768Hz。

该元件专为数字钟电路而设计,其频率较低,有利于减少分频器级数。

图2 晶体振荡电路框图2.分频器电路1) 分频器通常,数字钟的晶体振荡器输出频率较高,为了得到1Hz的秒信号输入,需要对振荡器的输出信号进行分频.时间标准信号的频率很高,要得到秒脉冲,需要分频电路。

分频器实际上也就是计数器,为此电路输送一秒脉冲。

2) 分频器电路电路通常实现分频器的电路是计数器电路,一般采用多级2进制计数器来实现.例如,将32768Hz的振荡信号分频为1HZ的分频倍数为32768(),即实现该分频功能的计数器相当于15级2进制计数器. 这里用一个14级2进制计数器和一个1级2进制计数器。

本次设计是运用了CD4060分频器进行分频,分频电路可提供512HZ和1024HZ的频率,在经CD4027分频器进行一分频,为此电路输送一秒脉冲。

本设计中采用CD4060来构成14级分频电路。

CD4060最全中文参考资料 引脚定义、电路连接之欧阳引擎创编

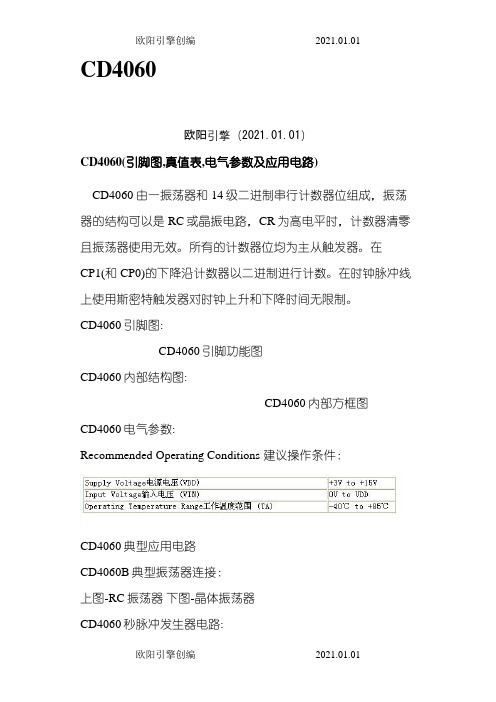

CD4060欧阳引擎(2021.01.01)CD4060(引脚图,真值表,电气参数及应用电路)CD4060由一振荡器和14级二进制串行计数器位组成,振荡器的结构可以是RC或晶振电路,CR为高电平时,计数器清零且振荡器使用无效。

所有的计数器位均为主从触发器。

在CP1(和CP0)的下降沿计数器以二进制进行计数。

在时钟脉冲线上使用斯密特触发器对时钟上升和下降时间无限制。

CD4060引脚图:CD4060引脚功能图CD4060内部结构图:CD4060内部方框图CD4060电气参数:Recommended Operating Conditions 建议操作条件:CD4060典型应用电路CD4060B典型振荡器连接:上图-RC振荡器下图-晶体振荡器CD4060秒脉冲发生器电路:图2 CD4060秒脉冲发生器脉冲发生器是数字钟的核心部分,它的精度和稳定度决定了数字钟的质量,通常用晶体振荡器发出的脉冲经过整形、分频获得1Hz的秒脉冲。

如晶振为32768 Hz,通过15次二分频后可获得1Hz的脉冲输出,电路图如图2所示。

CD4060定时电路由CD4060和CD4027构成的50Hz振荡器电路本振荡器能产生交变的50Hz脉冲方波,其占空比为50%.可供某些反相器电路应用。

该方波发生器由14级计数、振荡器(CD4060)。

双J-K触发器(CD4027);运算放大器(LM324)和少量的分立元件等组成。

电路的振荡由CD4060(IC1)外加晶振3.2768MHz完成,用电阻R1限制振荡回路功耗,R2是偏置电阻。

为了启动和维持电路的振荡,用电阻R1提供必需的最小值跨导。

振荡的频率经"14"级分频,得到200Hz,再由CD4060的第③脚输出。

200tHz频率又由双J-K触发器进一步"4分频,获得50Hz 信号。

该50Hz由CDD4027的15出,同时在14脚还产生与15脚的互补(相位差180.)频率信号。

秒信号发生器电路图两个

秒信号发生器电路图两个秒信号发生器:下面介绍的秒信号发生器可用在LED数字钟中,为数字钟提供秒基准信号。

字串7附图1电路由14位二进制串行计数器/分频器和振荡器CD4060、BCD同步加法计数器CD4518构成的秒信号发生器。

电路中利用CD4060组成两部分电路。

一部分是14级分频器,其最高分频数为16384;另一部分是由外接电子表用石英晶体、电阻及电容构成振荡频率为32768Hz的振荡器。

震荡器输出经14级分频后在输出端Q14上得到1/2秒脉冲并送入由1/2 CD4518构成的二分频器,分频后在输出断Q1上得到秒基准脉冲。

检验电路是否工作,可测量CD4060的9脚有无振荡信号输出。

调整微调电容可校准振荡频率。

附图2是另一款秒信号发生器电路。

它由双BCD同步加计数器CD4518、四输入端与非门CD4011和四2输入端或非门CD4001等构成。

电路中利用CD4060组成两部分电路。

一部分是14级分频器,其最高分频数为16384;另一部分是由外接电子表用石英晶体、电阻及电容构成振荡频率为32768Hz的振荡器。

震荡器输出经14级分频后在输出端Q14上得到1/2秒脉冲并送入由1/2 CD4518构成的二分频器,分频后在输出断Q1上得到秒基准脉冲。

检验电路是否工作,可测量CD4060的9脚有无振荡信号输出。

调整微调电容可校准振荡频率。

电路中,由CD4011门I构成晶体振荡电路产生的1MHz脉冲信号,经反相器门II送至由CD4518构成的多级计数分频器。

其中第一级10分频后输出为100KHz,第二级输出为10KHz,第三级输出为1000Hz,第四级输出为100Hz、第6级输出为1Hz。

由CD4011的门III、IV构成R-S触发器和CD4001的一个门组成了秒信号控制门。

单允许工作开关K3置“开”位置时,允许输出秒信号;置“关”位置时,禁止输出秒信号。

走时、校准开关K2置“走时”位置时,输出秒信号;置“校准”位置时,输出校准信号。

CD4060秒脉冲产生电路

脉冲发生器要想构成数字钟,首先应选择一个脉冲源——能自动地产生稳定的标准时间脉冲信号。

而脉冲源产生的脉冲信号的频率较高,因此,需要进行分频,使高频脉冲信号变成适合于计时的低频脉冲信号,即“秒脉冲信号”(频率为1HZ)。

经过分频器输出的秒脉冲信号到计数器中进行计数。

将标准秒信号送入“秒计数器”,“秒计数器”采用60进制计数器,每累计60秒发一个“分脉冲”信号,该信号将作为“分计数器”的时钟脉冲。

“分计数器”也采用60进制计数器,每累计60分钟,发出一个“时脉冲”信号,该信号将被送到“时计数器”。

“时计数器”采用24进制计时器,可实现对一天24小时的累计。

此时需要分别设计60进制,24进制计数器,各计数器输出信号经译码器到数字显示器,使“时”、“分”、“秒”得以数字显示出来。

值得注意的是:任何计时装置都有误差,因此应考虑校准时间电路。

校时电路一般采用手动调整。

手动调整可利用手动的节拍调准显示时间。

C D4060由一振荡器和14级二进制串行计数器位组成,振荡器的结构可以是RC或晶振电路,CR为高电平时,计数器清零且振荡器使用无效。

所有的计数器位均为主从触发器。

在CP1(和CP0)的下降沿计数器以二进制进行计数。

在时钟脉冲线上使用斯密特触发器对时钟上升和下降时间无限制。

CD4060引角图CD4060内部方框图CD4060B典型振荡器连接上图-RC振荡器下图-晶体振荡器RC振荡器中T=2.2R1C,R2=2*R1~10*R1脉冲发生器是数字钟的核心部分,它的精度和稳定度决定了数字钟的质量,通常用晶体振荡器发出的脉冲经过整形、分频获得1Hz的秒脉冲。

如晶振为32768 Hz,通过15次二分频后可获得1Hz的脉冲输出CD4060秒脉冲发生器电路-----精心整理,希望对您有所帮助!。

CD4060中文资料

CD4020 CD4040 CD4060中文资料CD4020 CD4040 CD4060中文资料时间:2009-07-19 15:15:06 来源:资料室作者:编号:5912 更新日期20110701 065429 CD4020是14位二进制串行计数器。

所有的计数器为主从触发器。

计数器在时钟下降沿进行计数,CR为高电平时,对计数器进行清零。

由于在时钟输入端使用斯密特触发器,对脉冲上升和下降时间无限制,所有输入和输出均经过缓冲。

cW8838电子-技术资料-电子元件-电路图-技术应用网站-基本知识-原理-维修-作用-参数-电子元器件符号cW8838电子-技术资料-电子元件-电路图-技术应用网站-基本知识-原理-维修-作用-参数-电子元器件符号CD4040是12位二进制串行计数器,所有计数器位为主从触发器。

计数器在时钟下降沿进行计数,CR为高电平时,对计数器进行清零。

由于在时钟输入端使用斯密特触发器,对脉冲上升和下降时间无限制。

所有输入和输出均经过缓冲。

cW8838电子-技术资料-电子元件-电路图-技术应用网站-基本知识-原理-维修-作用-参数-电子元器件符号cW8838电子-技术资料-电子元件-电路图-技术应用网站-基本知识-原理-维修-作用-参数-电子元器件符号CD4060由一振荡器和14级二进制串行计数器位组成,振荡器的结构可以是RC或晶振电路,CR为高电平时,计数器清零且振荡器使用无效。

所有的计数器位均为主从触发器。

在CP1(和CP0)的下降沿计数器以二进制进行计数。

在时钟脉冲线上使用斯密特触发器对时钟上升和下降时间无限制。

cW8838电子-技术资料-电子元件-电路图-技术应用网站-基本知识-原理-维修-作用-参数-电子元器件符号cW8838电子-技术资料-电子元件-电路图-技术应用网站-基本知识-原理-维修-作用-参数-电子元器件符号CD4020引脚功能图cW8838电子-技术资料-电子元件-电路图-技术应用网站-基本知识-原理-维修-作用-参数-电子元器件符号cW8838电子-技术资料-电子元件-电路图-技术应用网站-基本知识-原理-维修-作用-参数-电子元器件符号CD4040引脚图cW8838电子-技术资料-电子元件-电路图-技术应用网站-基本知识-原理-维修-作用-参数-电子元器件符号cW8838电子-技术资料-电子元件-电路图-技术应用网站-基本知识-原理-维修-作用-参数-电子元器件符号CD4060引脚功能图cW8838电子-技术资料-电子元件-电路图-技术应用网站-基本知识-原理-维修-作用-参数-电子元器件符号cW8838电子-技术资料-电子元件-电路图-技术应用网站-基本知识-原理-维修-作用-参数-电子元器件符号cW8838电子-技术资料-电子元件-电路图-技术应用网站-基本知识-原理-维修-作用-参数-电子元器件符号CD4020内部方框图cW8838电子-技术资料-电子元件-电路图-技术应用网站-基本知识-原理-维修-作用-参数-电子元器件符号cW8838电子-技术资料-电子元件-电路图-技术应用网站-基本知识-原理-维修-作用-参数-电子元器件符号CD4040内部方框图cW8838电子-技术资料-电子元件-电路图-技术应用网站-基本知识-原理-维修-作用-参数-电子元器件符号cW8838电子-技术资料-电子元件-电路图-技术应用网站-基本知识-原理-维修-作用-参数-电子元器件符号CD4060内部方框图cW8838电子-技术资料-电子元件-电路图-技术应用网站-基本知识-原理-维修-作用-参数-电子元器件符号CD4060B典型振荡器连接:上图-RC振荡器下图-晶体振荡器cW8838电子-技术资料-电子元件-电路图-技术应用网站-基本知识-原理-维修-作用-参数-电子元器件符号Absolute Maximum Ratings 绝对最大额定值:Supply Voltage电源电压(VDD) -0.5V to +18VInput V oltage输入电压(VIN) -0.5V to VDD +0.5VStorage Temperature Range储存温度范围(TS) -65℃to +150℃Package Dissipation (PD)Dual-In-Line 普通双列封装700 mWSmall Outline 小外形封装500 mWLead Temperature 焊接温度(TL)Soldering, 10 seconds)(焊接10秒)260℃cW8838电子-技术资料-电子元件-电路图-技术应用网站-基本知识-原理-维修-作用-参数-电子元器件符号Recommended Operating Conditions 建议操作条件:Supply Voltage电源电压(VDD) +3V to +15VInput V oltage输入电压(VIN) 0V to VDDOperating Temperature Range工作温度范围(TA) -40℃to +85℃cW8838电子-技术资料-电子元件-电路图-技术应用网站-基本知识-原理-维修-作用-参数-电子元器件符号DC Electrical Characteristics 直流电气特性:Symbol符号cW8838电子-技术资料-电子元件-电路图-技术应用网站-基本知识-原理-维修-作用-参数-电子元器件符号Parameter参数cW8838电子-技术资料-电子元件-电路图-技术应用网站-基本知识-原理-维修-作用-参数-电子元器件符号Conditions 测试条件-40°C cW8838电子-技术资料-电子元件-电路图-技术应用网站-基本知识-原理-维修-作用-参数-电子元器件符号+25°C cW8838电子-技术资料-电子元件-电路图-技术应用网站-基本知识-原理-维修-作用-参数-电子元器件符号+85°C cW8838电子-技术资料-电子元件-电路图-技术应用网站-基本知识-原理-维修-作用-参数-电子元器件符号Units 单位cW8838电子-技术资料-电子元件-电路图-技术应用网站-基本知识-原理-维修-作用-参数-电子元器件符号最小最大最小典型最大最小最大IDD Quiescent Device Current静态电流VDD=5V,VIN = VDD or VSS cW8838电子-技术资料-电子元件-电路图-技术应用网站-基本知识-原理-维修-作用-参数-电子元器件符号20 cW8838电子-技术资料-电子元件-电路图-技术应用网站-基本知识-原理-维修-作用-参数-电子元器件符号cW8838电子-技术资料-电子元件-电路图-技术应用网站-基本知识-原理-维修-作用-参数-电子元器件符号cW8838电子-技术资料-电子元件-电路图-技术应用网站-基本知识-原理-维修-作用-参数-电子元器件符号20 cW8838电子-技术资料-电子元件-电路图-技术应用网站-基本知识-原理-维修-作用-参数-电子元器件符号cW8838电子-技术资料-电子元件-电路图-技术应用网站-基本知识-原理-维修-作用-参数-电子元器件符号150 cW8838电子-技术资料-电子元件-电路图-技术应用网站-基本知识-原理-维修-作用-参数-电子元器件符号μAcW8838电子-技术资料-电子元件-电路图-技术应用网站-基本知识-原理-维修-作用-参数-电子元器件符号VDD=10V,VIN = VDD or VSS cW8838电子-技术资料-电子元件-电路图-技术应用网站-基本知识-原理-维修-作用-参数-电子元器件符号40 cW8838电子-技术资料-电子元件-电路图-技术应用网站-基本知识-原理-维修-作用-参数-电子元器件符号cW8838电子-技术资料-电子元件-电路图-技术应用网站-基本知识-原理-维修-作用-参数-电子元器件符号cW8838电子-技术资料-电子元件-电路图-技术应用网站-基本知识-原理-维修-作用-参数-电子元器件符号40 cW8838电子-技术资料-电子元件-电路图-技术应用网站-基本知识-原理-维修-作用-参数-电子元器件符号cW8838电子-技术资料-电子元件-电路图-技术应用网站-基本知识-原理-维修-作用-参数-电子元器件符号300 cW8838电子-技术资料-电子元件-电路图-技术应用网站-基本知识-原理-维修-作用-参数-电子元器件符号VDD=15V,VIN= VDD or VSS cW8838电子-技术资料-电子元件-电路图-技术应用网站-基本知识-原理-维修-作用-参数-电子元器件符号80 cW8838电子-技术资料-电子元件-电路图-技术应用网站-基本知识-原理-维修-作用-参数-电子元器件符号cW8838电子-技术资料-电子元件-电路图-技术应用网站-基本知识-原理-维修-作用-参数-电子元器件符号cW8838电子-技术资料-电子元件-电路图-技术应用网站-基本知识-原理-维修-作用-参数-电子元器件符号80 cW8838电子-技术资料-电子元件-电路图-技术应用网站-基本知识-原理-维修-作用-参数-电子元器件符号cW8838电子-技术资料-电子元件-电路图-技术应用网站-基本知识-原理-维修-作用-参数-电子元器件符号600 cW8838电子-技术资料-电子元件-电路图-技术应用网站-基本知识-原理-维修-作用-参数-电子元器件符号VOL LOW Level Output V oltage 输出低电平电压VDD = 5V cW8838电子-技术资料-电子元件-电路图-技术应用网站-基本知识-原理-维修-作用-参数-电子元器件符号0.05 cW8838电子-技术资料-电子元件-电路图-技术应用网站-基本知识-原理-维修-作用-参数-电子元器件符号cW8838电子-技术资料-电子元件-电路图-技术应用网站-基本知识-原理-维修-作用-参数-电子元器件符号0 cW8838电子-技术资料-电子元件-电路图-技术应用网站-基本知识-原理-维修-作用-参数-电子元器件符号0.05 cW8838电子-技术资料-电子元件-电路图-技术应用网站-基本知识-原理-维修-作用-参数-电子元器件符号cW8838电子-技术资料-电子元件-电路图-技术应用网站-基本知识-原理-维修-作用-参数-电子元器件符号0.05 cW8838电子-技术资料-电子元件-电路图-技术应用网站-基本知识-原理-维修-作用-参数-电子元器件符号V cW8838电子-技术资料-电子元件-电路图-技术应用网站-基本知识-原理-维修-作用-参数-电子元器件符号VDD = 10V cW8838电子-技术资料-电子元件-电路图-技术应用网站-基本知识-原理-维修-作用-参数-电子元器件符号0.05 cW8838电子-技术资料-电子元件-电路图-技术应用网站-基本知识-原理-维修-作用-参数-电子元器件符号cW8838电子-技术资料-电子元件-电路图-技术应用网站-基本知识-原理-维修-作用-参数-电子元器件符号0 cW8838电子-技术资料-电子元件-电路图-技术应用网站-基本知识-原理-维修-作用-参数-电子元器件符号0.05 cW8838电子-技术资料-电子元件-电路图-技术应用网站-基本知识-原理-维修-作用-参数-电子元器件符号cW8838电子-技术资料-电子元件-电路图-技术应用网站-基本知识-原理-维修-作用-参数-电子元器件符号0.05 cW8838电子-技术资料-电子元件-电路图-技术应用网站-基本知识-原理-维修-作用-参数-电子元器件符号VDD = 15V cW8838电子-技术资料-电子元件-电路图-技术应用网站-基本知识-原理-维修-作用-参数-电子元器件符号0.05 cW8838电子-技术资料-电子元件-电路图-技术应用网站-基本知识-原理-维修-作用-参数-电子元器件符号cW8838电子-技术资料-电子元件-电路图-技术应用网站-基本知识-原理-维修-作用-参数-电子元器件符号0 cW8838电子-技术资料-电子元件-电路图-技术应用网站-基本知识-原理-维修-作用-参数-电子元器件符号0.05 cW8838电子-技术资料-电子元件-电路图-技术应用网站-基本知识-原理-维修-作用-参数-电子元器件符号cW8838电子-技术资料-电子元件-电路图-技术应用网站-基本知识-原理-维修-作用-参数-电子元器件符号0.05 cW8838电子-技术资料-电子元件-电路图-技术应用网站-基本知识-原理-维修-作用-参数-电子元器件符号VOH HIGH Level Output V oltage 输出高电平电压VDD = 5V 4.95 cW8838电子-技术资料-电子元件-电路图-技术应用网站-基本知识-原理-维修-作用-参数-电子元器件符号cW8838电子-技术资料-电子元件-电路图-技术应用网站-基本知识-原理-维修-作用-参数-电子元器件符号4.95 cW8838电子-技术资料-电子元件-电路图-技术应用网站-基本知识-原理-维修-作用-参数-电子元器件符号5 cW8838电子-技术资料-电子元件-电路图-技术应用网站-基本知识-原理-维修-作用-参数-电子元器件符号cW8838电子-技术资料-电子元件-电路图-技术应用网站-基本知识-原理-维修-作用-参数-电子元器件符号4.95 cW8838电子-技术资料-电子元件-电路图-技术应用网站-基本知识-原理-维修-作用-参数-电子元器件符号cW8838电子-技术资料-电子元件-电路图-技术应用网站-基本知识-原理-维修-作用-参数-电子元器件符号V cW8838电子-技术资料-电子元件-电路图-技术应用网站-基本知识-原理-维修-作用-参数-电子元器件符号VDD = 10V 9.95 cW8838电子-技术资料-电子元件-电路图-技术应用网站-基本知识-原理-维修-作用-参数-电子元器件符号cW8838电子-技术资料-电子元件-电路图-技术应用网站-基本知识-原理-维修-作用-参数-电子元器件符号9.95 cW8838电子-技术资料-电子元件-电路图-技术应用网站-基本知识-原理-维修-作用-参数-电子元器件符号10 cW8838电子-技术资料-电子元件-电路图-技术应用网站-基本知识-原理-维修-作用-参数-电子元器件符号cW8838电子-技术资料-电子元件-电路图-技术应用网站-基本知识-原理-维修-作用-参数-电子元器件符号9.95 cW8838电子-技术资料-电子元件-电路图-技术应用网站-基本知识-原理-维修-作用-参数-电子元器件符号cW8838电子-技术资料-电子元件-电路图-技术应用网站-基本知识-原理-维修-作用-参数-电子元器件符号VDD = 15V 14.95 cW8838电子-技术资料-电子元件-电路图-技术应用网站-基本知识-原理-维修-作用-参数-电子元器件符号cW8838电子-技术资料-电子元件-电路图-技术应用网站-基本知识-原理-维修-作用-参数-电子元器件符号14.95 cW8838电子-技术资料-电子元件-电路图-技术应用网站-基本知识-原理-维修-作用-参数-电子元器件符号15 cW8838电子-技术资料-电子元件-电路图-技术应用网站-基本知识-原理-维修-作用-参数-电子元器件符号cW8838电子-技术资料-电子元件-电路图-技术应用网站-基本知识-原理-维修-作用-参数-电子元器件符号14.95 cW8838电子-技术资料-电子元件-电路图-技术应用网站-基本知识-原理-维修-作用-参数-电子元器件符号cW8838电子-技术资料-电子元件-电路图-技术应用网站-基本知识-原理-维修-作用-参数-电子元器件符号VIL LOW Level Input V oltage 输入低电平电压VDD=5V,VO=0.5V or 4.5V cW8838电子-技术资料-电子元件-电路图-技术应用网站-基本知识-原理-维修-作用-参数-电子元器件符号1.5 cW8838电子-技术资料-电子元件-电路图-技术应用网站-基本知识-原理-维修-作用-参数-电子元器件符号cW8838电子-技术资料-电子元件-电路图-技术应用网站-基本知识-原理-维修-作用-参数-电子元器件符号2 cW8838电子-技术资料-电子元件-电路图-技术应用网站-基本知识-原理-维修-作用-参数-电子元器件符号1.5 cW8838电子-技术资料-电子元件-电路图-技术应用网站-基本知识-原理-维修-作用-参数-电子元器件符号cW8838电子-技术资料-电子元件-电路图-技术应用网站-基本知识-原理-维修-作用-参数-电子元器件符号1.5 cW8838电子-技术资料-电子元件-电路图-技术应用网站-基本知识-原理-维修-作用-参数-电子元器件符号电子元器件符号VDD=10V,VO=1.0V or 9.0V cW8838电子-技术资料-电子元件-电路图-技术应用网站-基本知识-原理-维修-作用-参数-电子元器件符号3.0 cW8838电子-技术资料-电子元件-电路图-技术应用网站-基本知识-原理-维修-作用-参数-电子元器件符号cW8838电子-技术资料-电子元件-电路图-技术应用网站-基本知识-原理-维修-作用-参数-电子元器件符号4 cW8838电子-技术资料-电子元件-电路图-技术应用网站-基本知识-原理-维修-作用-参数-电子元器件符号3.0 cW8838电子-技术资料-电子元件-电路图-技术应用网站-基本知识-原理-维修-作用-参数-电子元器件符号cW8838电子-技术资料-电子元件-电路图-技术应用网站-基本知识-原理-维修-作用-参数-电子元器件符号3.0 cW8838电子-技术资料-电子元件-电路图-技术应用网站-基本知识-原理-维修-作用-参数-电子元器件符号VDD=15V,VO=1.5V or 13.5V cW8838电子-技术资料-电子元件-电路图-技术应用网站-基本知识-原理-维修-作用-参数-电子元器件符号4.0 cW8838电子-技术资料-电子元件-电路图-技术应用网站-基本知识-原理-维修-作用-参数-电子元器件符号cW8838电子-技术资料-电子元件-电路图-技术应用网站-基本知识-原理-维修-作用-参数-电子元器件符号6 cW8838电子-技术资料-电子元件-电路图-技术应用网站-基本知识-原理-维修-作用-参数-电子元器件符号4.0 cW8838电子-技术资料-电子元件-电路图-技术应用网站-基本知识-原理-维修-作用-参数-电子元器件符号cW8838电子-技术资料-电子元件-电路图-技术应用网站-基本知识-原理-维修-作用-参数-电子元器件符号4.0 cW8838电子-技术资料-电子元件-电路图-技术应用网站-基本知识-原理-维修-作用-参数-电子元器件符号VIH HIGH Level Input V oltage 输入高电平电压VDD=5V,VO=0.5V or 4.5V 3.5 cW8838电子-技术资料-电子元件-电路图-技术应用网站-基本知识-原理-维修-作用-参数-电子元器件符号cW8838电子-技术资料-电子元件-电路图-技术应用网站-基本知识-原理-维修-作用-参数-电子元器件符号3.5 cW8838电子-技术资料-电子元件-电路图-技术应用网站-基本知识-原理-维修-作用-参数-电子元器件符号3 cW8838电子-技术资料-电子元件-电路图-技术应用网站-基本知识-原理-维修-作用-参数-电子元器件符号cW8838电子-技术资料-电子元件-电路图-技术应用网站-基本知识-原理-维修-作用-参数-电子元器件符号-电子元器件符号cW8838电子-技术资料-电子元件-电路图-技术应用网站-基本知识-原理-维修-作用-参数-电子元器件符号V cW8838电子-技术资料-电子元件-电路图-技术应用网站-基本知识-原理-维修-作用-参数-电子元器件符号VDD=10V,VO=1.0V or 9.0V 7.0 cW8838电子-技术资料-电子元件-电路图-技术应用网站-基本知识-原理-维修-作用-参数-电子元器件符号cW8838电子-技术资料-电子元件-电路图-技术应用网站-基本知识-原理-维修-作用-参数-电子元器件符号7.0 cW8838电子-技术资料-电子元件-电路图-技术应用网站-基本知识-原理-维修-作用-参数-电子元器件符号6 cW8838电子-技术资料-电子元件-电路图-技术应用网站-基本知识-原理-维修-作用-参数-电子元器件符号cW8838电子-技术资料-电子元件-电路图-技术应用网站-基本知识-原理-维修-作用-参数-电子元器件符号7.0 cW8838电子-技术资料-电子元件-电路图-技术应用网站-基本知识-原理-维修-作用-参数-电子元器件符号cW8838电子-技术资料-电子元件-电路图-技术应用网站-基本知识-原理-维修-作用-参数-电子元器件符号VDD=15V,VO=1.5V or 13.5V 11.0 cW8838电子-技术资料-电子元件-电路图-技术应用网站-基本知识-原理-维修-作用-参数-电子元器件符号cW8838电子-技术资料-电子元件-电路图-技术应用网站-基本知识-原理-维修-作用-参数-电子元器件符号11.0 cW8838电子-技术资料-电子元件-电路图-技术应用网站-基本知识-原理-维修-作用-参数-电子元器件符号9 cW8838电子-技术资料-电子元件-电路图-技术应用网站-基本知识-原理-维修-作用-参数-电子元器件符号cW8838电子-技术资料-电子元件-电路图-技术应用网站-基本知识-原理-维修-作用-参数-电子元器件符号11.0 cW8838电子-技术资料-电子元件-电路图-技术应用网站-基本知识-原理-维修-作用-参数-电子元器件符号cW8838电子-技术资料-电子元件-电路图-技术应用网站-基本知识-原理-维修-作用-参数-电子元器件符号IOL LOW Level Output Current 输出低电平电流(Note 3) VDD = 5V, VO = 0.4V 0.52 cW8838电子-技术资料-电子元件-电路图-技术应用网站-基本知识-原理-维修-作用-参数-电子元器件符号cW8838电子-技术资料-电子元件-电路图-技术应用网站-基本知识-原理-维修-作用-参数-电子元器件符号0.44 cW8838电子-技术资料-电子元件-电路图-技术应用网站-基本知识-原理-维修-作用-参数-电子元器件符号数-电子元器件符号cW8838电子-技术资料-电子元件-电路图-技术应用网站-基本知识-原理-维修-作用-参数-电子元器件符号0.36 cW8838电子-技术资料-电子元件-电路图-技术应用网站-基本知识-原理-维修-作用-参数-电子元器件符号cW8838电子-技术资料-电子元件-电路图-技术应用网站-基本知识-原理-维修-作用-参数-电子元器件符号mA cW8838电子-技术资料-电子元件-电路图-技术应用网站-基本知识-原理-维修-作用-参数-电子元器件符号VDD = 10V, VO = 0.5V 1.3 cW8838电子-技术资料-电子元件-电路图-技术应用网站-基本知识-原理-维修-作用-参数-电子元器件符号cW8838电子-技术资料-电子元件-电路图-技术应用网站-基本知识-原理-维修-作用-参数-电子元器件符号1.1 cW8838电子-技术资料-电子元件-电路图-技术应用网站-基本知识-原理-维修-作用-参数-电子元器件符号2.25 cW8838电子-技术资料-电子元件-电路图-技术应用网站-基本知识-原理-维修-作用-参数-电子元器件符号cW8838电子-技术资料-电子元件-电路图-技术应用网站-基本知识-原理-维修-作用-参数-电子元器件符号0.9 cW8838电子-技术资料-电子元件-电路图-技术应用网站-基本知识-原理-维修-作用-参数-电子元器件符号cW8838电子-技术资料-电子元件-电路图-技术应用网站-基本知识-原理-维修-作用-参数-电子元器件符号VDD = 15V, VO = 1.5V 3.6 cW8838电子-技术资料-电子元件-电路图-技术应用网站-基本知识-原理-维修-作用-参数-电子元器件符号cW8838电子-技术资料-电子元件-电路图-技术应用网站-基本知识-原理-维修-作用-参数-电子元器件符号3.0 cW8838电子-技术资料-电子元件-电路图-技术应用网站-基本知识-原理-维修-作用-参数-电子元器件符号8.8 cW8838电子-技术资料-电子元件-电路图-技术应用网站-基本知识-原理-维修-作用-参数-电子元器件符号cW8838电子-技术资料-电子元件-电路图-技术应用网站-基本知识-原理-维修-作用-参数-电子元器件符号2.4 cW8838电子-技术资料-电子元件-电路图-技术应用网站-基本知识-原理-维修-作用-参数-电子元器件符号cW8838电子-技术资料-电子元件-电路图-技术应用网站-基本知识-原理-维修-作用-参数-电子元器件符号IOH HIGH Level Output Current 输出高电平电流(Note 3) VDD = 5V, VO = 4.6V -0.52 cW8838电子-技术资料-电子元件-电路图-技术应用网站-基本知识-原理-维修-作用-参数-电子元器件符号电子元器件符号-0.44 cW8838电子-技术资料-电子元件-电路图-技术应用网站-基本知识-原理-维修-作用-参数-电子元器件符号-0.88 cW8838电子-技术资料-电子元件-电路图-技术应用网站-基本知识-原理-维修-作用-参数-电子元器件符号cW8838电子-技术资料-电子元件-电路图-技术应用网站-基本知识-原理-维修-作用-参数-电子元器件符号-0.36 cW8838电子-技术资料-电子元件-电路图-技术应用网站-基本知识-原理-维修-作用-参数-电子元器件符号cW8838电子-技术资料-电子元件-电路图-技术应用网站-基本知识-原理-维修-作用-参数-电子元器件符号mA cW8838电子-技术资料-电子元件-电路图-技术应用网站-基本知识-原理-维修-作用-参数-电子元器件符号VDD = 10V, VO = 9.5V -1.3 cW8838电子-技术资料-电子元件-电路图-技术应用网站-基本知识-原理-维修-作用-参数-电子元器件符号cW8838电子-技术资料-电子元件-电路图-技术应用网站-基本知识-原理-维修-作用-参数-电子元器件符号-1.1 cW8838电子-技术资料-电子元件-电路图-技术应用网站-基本知识-原理-维修-作用-参数-电子元器件符号-2.25 cW8838电子-技术资料-电子元件-电路图-技术应用网站-基本知识-原理-维修-作用-参数-电子元器件符号cW8838电子-技术资料-电子元件-电路图-技术应用网站-基本知识-原理-维修-作用-参数-电子元器件符号-0.9 cW8838电子-技术资料-电子元件-电路图-技术应用网站-基本知识-原理-维修-作用-参数-电子元器件符号cW8838电子-技术资料-电子元件-电路图-技术应用网站-基本知识-原理-维修-作用-参数-电子元器件符号VDD = 15V, VO = 13.5V -3.6 cW8838电子-技术资料-电子元件-电路图-技术应用网站-基本知识-原理-维修-作用-参数-电子元器件符号cW8838电子-技术资料-电子元件-电路图-技术应用网站-基本知识-原理-维修-作用-参数-电子元器件符号-3.0 cW8838电子-技术资料-电子元件-电路图-技术应用网站-基本知识-原理-维修-作用-参数-电子元器件符号-8.8 cW8838电子-技术资料-电子元件-电路图-技术应用网站-基本知识-原理-维修-作用-参数-电子元器件符号cW8838电子-技术资料-电子元件-电路图-技术应用网站-基本知识-原理-维修-作用-参数-电子元器件符号-2.4 cW8838电子-技术资料-电子元件-电路图-技术应用网站-基本知识-原理-维修-作用-参数-电子元器件符号cW8838电子-技术资料-电子元件-电路图-技术应用网站-基本知识-原理-维修-作用-参数-电子元器件符号。

CD4060内部结构及典型应用电路

电平

电压 VDD = 15V

0

.

0.0

0.0

0

0

5

5

5

0

.

0.0

0.0

0

0

5

5

5

0

.

0.0

0.0

0

0

5

5

5

HIGH VDD = 5V

4.

4.

4.9

9

5

9

Level

5

5

5

Output

9.

9.

VO Voltag

9.9

VDD = 10V

9

10

9

H e输

5

5

5

出高

电平

1

1

14.

电压 VDD = 15V

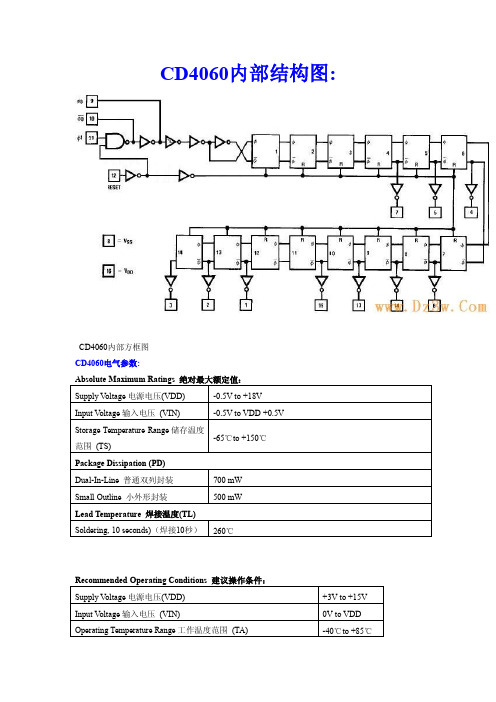

CD4060内部结构图:

CD4060内部方框图

CD4060电气参数:

Absolute Maximum Ratings 绝对最大额定值:

Supply Voltage 电源电压(VDD)

-0.5V to +18V

Input Voltage 输入电压 (VIN)

-0.5V to VDD +0.5V

Storage Temperature Range 储存温度 -65℃to +150℃

CD4060定时电路

. 电压 V or 13.5V

0

6 4.0

4.0

HIGH VDD=5V,VO=0.5V 3.

3.

3.5 3LevBiblioteka l or 4.5V55

Input VDD=10V,VO=1.0 7.

7.

一种60Hz脉冲发生电路

一种60Hz脉冲发生电路60Hz脉冲信号是时钟电路常用到的信号。

本文介绍一种60Hz脉冲信号发生电路,分析其存在的误差,并给出减少误差的改进电路。

电路组成图1示出的60Hz脉冲信号发生电路,由石英晶体多谐振荡器和分频器两部分电路组成,其中IC1为“非”门电路CD4069,IC2为分频集成电路CD4040,JT为32768Hz石英晶体。

石英晶体、“非”门1和“非”门2组成石英晶体多谐振荡器,晶体JT和电容C1在电路中形成正反馈。

晶体在它的固有串联谐振频率点f0的等效阻抗最小,所以电路的振荡频率就取决于晶体的固有串联谐振频率,与外接电阻R1、电容C1的参数无关。

由于石英晶体的频率稳定度可达10-10~10-11,所以可获得频率非常稳定的振荡信号。

IC2、“非”门3、“非”门4和D1、D2组成分频电路,它对石英晶体振荡器所产生的32768Hz的脉冲信号进行分频,在输出端Q10或Q9可获取60Hz的脉冲信号。

分频比及频率误差CD4040是一片12级脉动进位二进制计数分频电路,它在时钟的下降沿进行计数,其复位端输入高电平时,可取得与时钟输入无关的直接复位。

由于石英晶体的固有谐振频率f0=32768Hz,从Q9端输出的信号是f0的29分频,其数值是64Hz,所以不采取一定的措施是不能获得60Hz的信号的。

所采取的措施是,把CD4040的Q10输出端通过R2、“非”门3和“非”门4连接到它的复位端,同时通过D1、D2分别连接到它的Q2和Q6输出端,即D1、D2、“非”门3和“非”门4组成复位控制电路,让Q10、Q6、Q2的输出共同控制CD4040的复位。

Q10端输出的信号是振荡频率的210分频,该信号的一个周期为振荡脉冲信号的1024个周期时间,低电平和高电平时间各为振荡脉冲的512个周期时间。

同理,Q6端输出信号一个周期的高、低电平各为振荡脉冲的32个周期时间,Q2端输出信号一个周期的高、低电平时间各为振荡脉冲的2个周期时间。

CD4060最全中文参考资料 引脚定义、电路连接

CD4060之欧侯瑞魂创作创作时间:二零二一年六月三十日CD4060(引脚图,真值表,电气参数及应用电路)CD4060由一振荡器和14级二进制串行计数器位组成,振荡器的结构可以是RC或晶振电路,CR为高电平时,计数器清零且振荡器使用无效.所有的计数器位均为主从触发器.在CP1(和CP0)的下降沿计数器以二进制进行计数.在时钟脉冲线上使用斯密特触发器对时钟上升和下降时间无限制.CD4060引脚图:CD4060引脚功能图CD4060内部结构图:CD4060内部方框图CD4060电气参数:Recommended Operating Conditions 建议把持条件:CD4 060典范应用电路CD4060B典范振荡器连接:上图-RC振荡器下图-晶体振荡器CD4060秒脉冲发生器电路:图2 CD4060秒脉冲发生器脉冲发生器是数字钟的核心部份,它的精度和稳定度决定了数字钟的质量,通经常使用晶体振荡器发出的脉冲经过整形、分频获得1Hz的秒脉冲.如晶振为32768 Hz,通过15次二分频后可获得1Hz 的脉冲输出,电路图如图2所示.CD4060按时电路由CD4060和CD4027构成的50Hz振荡器电路本振荡器能发生交变的50Hz脉冲方波,其占空比为50%.可供某些反相器电路应用.该方波发生器由14级计数、振荡器(CD4060).双J-K触发器(CD4027);运算放年夜器(LM324)和少量的分立元件等组成.电路的振荡由CD4060(IC1)外加晶振完成,用电阻R1限制振荡回路功耗,R2是偏置电阻.为了启动和维持电路的振荡,用电阻R1提供必需的最小值跨导.振荡的频率经"14"级分频,获得200Hz,再由CD4060的第③脚输出.200tHz频率又由双J-K触发器进一步"4分频,获得50Hz信号.该50Hz由CDD4027的15出,同时在14脚还发生与15脚的互补(相位差180.)频率信号.频率的占空比仍是50%.50Hz的方波由运算放年夜器LM324的A1、A2进行缓冲处置,在其①脚和⑦脚获得相位相反的方波输出,可供一些反相器电路应用.。

cd060最全中文参考资料 引脚定义、电路连接

CD4060CD4060(引脚图,真值表,电气参数及应用电路)??? CD4060由一振荡器和14级二进制串行计数器位组成,振荡器的结构可以是RC或晶振电路,CR为高电平时,计数器清零且振荡器使用无效。

所有的计数器位均为主从触发器。

在CP1(和CP0)的下降沿计数器以二进制进行计数。

在时钟脉冲线上使用斯密特触发器对时钟上升和下降时间无限制。

CD4060引脚图:????????????????????????? CD4060引脚功能图CD4060内部结构图: ???????????????????????????????????????????????????????????? CD4060内部方框图CD4060电气参数:Recommended Operating Conditions 建议操作条件:CD4060典型应用电路CD4060B典型振荡器连接:上图-RC振荡器下图-晶体振荡器CD4060秒脉冲发生器电路: ????????????????????????????????? 图2? CD4060秒脉冲发生器脉冲发生器是数字钟的核心部分,它的精度和稳定度决定了数字钟的质量,通常用晶体振荡器发出的脉冲经过整形、分频获得1Hz的秒脉冲。

如晶振为32768 Hz,通过15次二分频后可获得1Hz的脉冲输出,电路图如图2所示。

?CD4060定时电路由CD4060和CD4027构成的50Hz振荡器电路本振荡器能产生交变的50Hz脉冲方波,其占空比为50%.可供某些反相器电路应用。

该方波发生器由14级计数、振荡器(CD4060)。

双J-K触发器(CD4027);运算放大器(LM324)和少量的分立元件等组成。

电路的振荡由CD4060(IC1)外加晶振3.2768MHz完成,用电阻R1限制振荡回路功耗,R2是偏置电阻。

为了启动和维持电路的振荡,用电阻R1提供必需的最小值跨导。

振荡的频率经"14"级分频,得到200Hz,再由CD4060的第③脚输出。

cd4060时基电路工作原理

cd4060时基电路工作原理

CD4060是一款由NXP公司生产的CMOS集成电路,它包含一个振荡器与计数器、一个可编程分频器以及一个输出控制模块。

这款集成电路常被用于产生精确的定时信号,以及在微处理器系统中作为时钟源。

1. 振荡器与计数器:

CD4060的振荡器部分由一个反相放大器构成,可以用于产生一个频率可调的正弦波或方波信号。

该信号的频率由外部电阻和电容的值决定。

然后,这个振荡信号被送入计数器部分。

计数器部分是一个14位的二进制计数器,它可以在接收到振荡器的时钟信号后,对输入的二进制数据进行逐位计数。

当计数器的值达到最大值(即11111111111111,也就是2的14次方减1),计数器就会溢出,并将这个溢出信号送入分频器部分。

2. 分频器:

分频器是一个可编程的分频器,它可以根据输入的二进制数据来改变输出的频率。

这个分频比是由连接到CD4060的外部电阻和电容的值决定的。

当计数器溢出时,分频器会对振荡器的输出信号进行分频,然后将分频后的信号送入输出控制部分。

3. 输出控制:

输出控制部分是一个集电极开路的晶体管输出,它可以控制外部设备的开关。

当分频器的输出信号到达一定的阈值时,输出控制部分就会导通,从而驱动外部设备。

同时,输出控制部分还可以通过集电极开路的方式,将输出信号与地线隔离,以实现对外部设备的有效控制。

总的来说,CD4060时基电路通过振荡器与计数器产生原始的时钟信号,然后通过分频器对时钟信号进行分频,最后通过输出控制部分实现对外部设备的开关控制。

其产生的时钟信号具有精度高、稳定性好等特点,因此在许多微处理器系统中被用作时钟源。

cd4060分频工作原理

cd4060分频工作原理

CD4060是一款集成电路,常用于频率分频应用。

其工作原理是基于二进制计数器和分频器的组合,能够将输入信号的频率降低到更低的频率。

CD4060的工作原理可以分为三个部分:计数器、分频器和输出控制。

CD4060内部集成了一个14位二进制计数器。

这个计数器可以通过外部时钟信号进行驱动,每收到一个时钟脉冲,计数器的值就会加1。

当计数器的值达到最大值时,会自动清零,重新从0开始计数。

CD4060还包含一组分频器。

这些分频器可以将输入时钟信号的频率分频为2、4、8、16等倍数。

具体的分频比由引脚上的接线决定。

例如,如果将引脚Q4连接到引脚CLK(时钟输入),那么输入信号的频率将被分频为输入频率的16倍。

CD4060还有一个输出控制功能。

通过设置引脚上的接线,可以选择输出的位数。

例如,如果将引脚Q5连接到引脚RESET(复位),那么当计数器的值达到32时,输出会被清零。

这样可以实现更高精度的频率分频。

CD4060的分频功能非常灵活,适用于各种需要将信号频率降低的

应用场景。

例如,在无线通信系统中,CD4060可以将高频信号分频为低频信号,用于时钟同步和数据处理。

在音频设备中,CD4060可以将高采样率的音频信号分频为低采样率,以便进行数字信号处理。

总结起来,CD4060是一款基于二进制计数器和分频器的集成电路,能够将输入信号的频率降低到更低的频率。

通过设置引脚上的接线,可以选择分频比和输出位数,实现不同精度的频率分频。

CD4060的分频功能非常灵活,适用于各种需要降低信号频率的应用场景。

cd4060应用电路图汇总(分频定时CD4060时间控制器)

cd4060应用电路图汇总(分频定时CD4060时间控制器)CD4060是由一振荡器和14级二进制串行计数器位组成,振荡器的结构可以是RC或晶振电路,CR为高电平时,计数器清零且振荡器使用无效。

所有的计数器位均为主从触发器。

在CP1(和CP0)的下降沿计数器以二进制进行计数。

在时钟脉冲线上使用斯密特触发器对时钟上升和下降时间限制。

cd4060应用电路图(一)采用CD4060分频器的定时通电控制器电路:本例介绍一款采用CD4060分频器集成电路制作的定时通电控制器,能按设定的开、停时间比来控制电器,使之间歇工作,可用于控制使用交流220 V电源的小功率喷雾设施或加湿器、换气扇等。

该定时通电控制器电路由电源电路、多谐振荡器电路、开/停时间选择电路和控制电路组成,如下图所示。

电路中,电源电路由电源开关S、熔断器FU、工作状态选择开关S2、电源变压器T、整流二极管VD1、VD2、滤波电容C3~C5、三端稳压集成电路IC3、限流电阻R4和电源指示发光二极管VL组成;多谐振荡器电路由内置振荡器的分频集成电路IC1和电阻R1*、R2、电容C1组成;启/停时间选择电路由计数/脉冲分配器集成电路IC2和启/停时间比较选择开关S3组成;控制电路由电阻R3、R5、晶体管V、光耦合器VLC和压敏电阻RV组成。

交流220 V电压经T降压、VD1和VD2整流及C5滤波后,一路经R5供给VLC内部的发光二极管;另一路经IC3稳压为+9V,作为IC1和IC2的工作电源,同时经R4将VL点亮。

RV为过压保护元件,可防止VLC内部的光控晶闸管被浪涌电流或尖峰电压击穿。

多谐振荡器通电工作后,从IC1的3脚(Q14端)输出周期为1 min的方波脉冲信号,作为IC2,第14脚(CP端)的计数脉冲,102的3脚每10 min输出一个高电平或每6 min输出一个高电平(将S3置于“1”位置时,受控电器每10 min工作1 min;将S3置于“2”位置时,受控电器每6 min工作1min)。

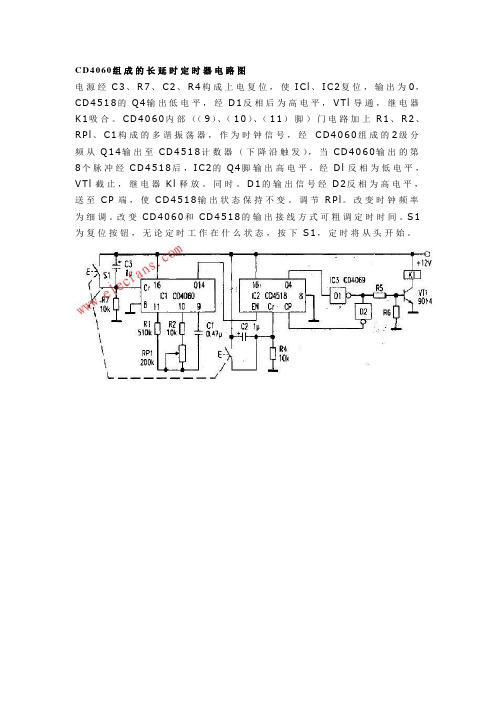

CD4060组成的长延时定时器电路图

C D4060组成的长延时定时器电路图

电源经C3、R7、C2、R4构成上电复位,使I C l、I C2复位,输出为0,C D4518的Q4输出低电平,经D1反相后为高电平,V T l导通,继电器K1吸合。

C D4060内部((9)、(10)、(11)脚)门电路加上R1、R2、R P l、C1构成的多谐振荡器,作为时钟信号,经C D4060组成的2级分频从Q14输出至C D4518计数器(下降沿触发),当C D4060输出的第8个脉冲经C D4518后,I C2的Q4脚输出高电平,经D l反相为低电平,V T l截止,继电器K l释放。

同时。

D1的输出信号经D2反相为高电平,送至C P端,使C D4518输出状态保持不变。

调节R P l。

改变时钟频率为细调。

改变C D4060和C D4518的输出接线方式可粗调定时时间。

S1为复位按钮,无论定时工作在什么状态,按下S1,定时将从头开始。

CD4060最全中文参考资料 引脚定义、电路连接

CD4060之迟辟智美创作CD4060(引脚图,真值表,电气参数及应用电路)CD4060由一振荡器和14级二进制串行计数器位组成,振荡器的结构可以是RC或晶振电路,CR为高电平时,计数器清零且振荡器使用无效.所有的计数器位均为主从触发器.在CP1(和CP0)的下降沿计数器以二进制进行计数.在时钟脉冲线上使用斯密特触发器对时钟上升和下降时间无限制.CD4060引脚图:CD4060引脚功能图CD4060内部结构图:CD4060内部方框图CD4060电气参数:Recommended Operating Conditions 建议把持条件:CD 4060典范应用电路CD4060B典范振荡器连接:上图-RC振荡器下图-晶体振荡器CD4060秒脉冲发生器电路:图2 CD4060秒脉冲发生器脉冲发生器是数字钟的核心部份,它的精度和稳定度决定了数字钟的质量,通经常使用晶体振荡器发出的脉冲经过整形、分频获得1Hz的秒脉冲.如晶振为32768 Hz,通过15次二分频后可获得1Hz的脉冲输出,电路图如图2所示.CD4060按时电路由CD4060和CD4027构成的50Hz振荡器电路本振荡器能发生交变的50Hz脉冲方波,其占空比为50%.可供某些反相器电路应用.该方波发生器由14级计数、振荡器(CD4060).双J-K触发器(CD4027);运算放年夜器(LM324)和少量的分立元件等组成.电路的振荡由CD4060(IC1)外加晶振完成,用电阻R1限制振荡回路功耗,R2是偏置电阻.为了启动和维持电路的振荡,用电阻R1提供必需的最小值跨导.振荡的频率经"14"级分频,获得200Hz,再由CD4060的第③脚输出.200tHz频率又由双J-K触发器进一步"4分频,获得50Hz信号.该50Hz由CDD4027的15出,同时在14脚还发生与15脚的互补(相位差180.)频率信号.频率的占空比仍是50%.50Hz的方波由运算放年夜器LM324的A1、A2进行缓冲处置,在其①脚和⑦脚获得相位相反的方波输出,可供一些反相器电路应用.。

采用CD4060的长延时定时器

采用CD4060的长延时定时器(二)本例介绍采用CD406o数字集成电路制作的长延时定时器(二),该定时器利用CD4W组成定时器的时基电路,由电路产生的定时时基脉冲,通过内部分频器分频后输出时基信号。

再通过外设的分频电路的分频,取得所需要的定时控制时间。

工作原理采用CD4060数字集成电路制作的长延时定时器(二)电路原理图如图所示。

该电路由CD4060与外接阻容元件组成高频振荡器,由(Rz+R1)C,决定与振荡器的振荡频率,通过RP调节振荡频率范围。

由CD4518双二一十进制计数器中的一个计数器组成分频器,其分频系数最大为10,本电路用它的输出端甲作为定时输出端。

由CD4518的工作原理和引脚功能可知,当仍输出高电平时,恰好是十进制数中的10,CD406 9六反相器中的两个门D1、D2和晶体管VT与继电器K组成输出与控制电路。

电路中,C3, R6组成Ic1的开机复位电路,C2、R3组成IC2的开机复位电路。

接通电源后,通过开机复位电路使ici、IC2自动复位。

SB1、SB2分别为Ic1、IC2的人工复位按键,当需要时按下该键使相应电路复位。

开机后,时基振荡器振荡经过分频后向外输出时基信号。

作为分频器的IC2开始计数分频。

当计数到10时,Q4输出高电平,该高电平经D1友相变为低电平使VT截止,继电器断电释放,切断被控电路工作电源。

与此同时,D1输出的低电平经D2反相为高电平后加至IC2的CP端,使输出端输出的高电平保持。

电路通电使Ic1、IC2复位后,IC2的四个输出端,均为低电平。

而娜输出的低电平经DI反相变为高电平,通过R4使VT导通,继电器通电吸合。

这种工作状态为开机接通、定时断开状态。

如果要改变为开机断开、定时接通状态,可在输出端DI和VT之间加人一级反相器。

定时时间的长短,可通过RP来调整,也可根据二一十进制编码的对应关系,通过对IC2的输出端的连接来改变。

本例电路定时范围为3min一1h.元器件选择Ic1选用CD406014位串行二进制计数/分频/振荡器数字集成电路;IC2选用双二一十进制计数器数字集成电路;IC3选用CD4069六反相器。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

CD4060秒脉冲产生电路

一摘要

数字钟是一种用数字电路技术实现时、分、秒计时的装置,与机械式时钟相比具有更高的准确性和直观性,且无机械装置,具有更更长的使用寿命,因此得到了广泛的使用。

诸如按时自动打铃,时间程序自动控制,定时启闭路灯,定时开关烘箱,通断动力设备,甚至各种定时电气的的自动启用等。

这些都是以数字时钟作为时钟源的。

数字钟从原理上讲是一种典型的数字电路,其中包括了组合逻辑电路和时序电路。

目前,数字钟的功能越来越强,并且有多种专门的大规模集成电路可供选择。

经过了数字电路设计这门课程的系统学习,特别经过了关于组合逻辑电路与时序逻辑电路部分的学习,我们已经具备了设计小规模集成电路的能力,借由本次设计的机会,充分将所学的知识运用到实际中去。

二主要技术指标

1.设计一个有时、分、秒(23小时59分59秒)显示的电子钟

2.该电子钟具有手动校时功能

三方案论证与选择

要想构成数字钟,首先应选择一个脉冲源——能自动地产生稳定的标准时间脉冲信号。

而脉冲源产生的脉冲信号的频率较高,因此,需要进行分频,使高频脉冲信号变成适合于计时的低频脉冲信号,即“秒脉冲信号”(频率为1HZ)。

经过分频器输出的秒脉冲信号到计数器中进行计数。

将标准秒信号送入“秒计数器”,“秒计数器”采用60进制计数器,每累计60秒发一个“分脉冲”信号,该信号将作为“分计数器”的时钟脉冲。

“分计数器”也采用60进制计数器,每累计60分钟,发出一个“时脉冲”信号,该信号将被送到“时计数器”。

“时计数器”采用24进制计时器,可实现对一天24小时的累计。

此时需要分别设计60进制,24进制计数器,各计数器输出信号经译码器到数字显示器,使“时”、“分”、“秒”得以数字显示出来。

值得注意的是:任何计时装置都有误差,因此应考虑校准时间电路。

校时电路一般采用手动调整。

手动调整可利用手动的节拍调准显示时间。

CD4060由一振荡器和14级二进制串行计数

器位组成,振荡器的结构可以是RC或晶振电路,CR为高电平时,计数器清零且振荡器使用无效。

所有的计数器位均为主从触发器。

在CP1(和CP0)的下降沿计数器以二进制进行计数。

在时钟脉冲线上使用斯密特触发器对时钟上升和下降时间无限制。

CD4060引脚图:

CD4060引脚功能图CD4060内部结构图:

CD4060内部方框图

CD4060电气参数:

Recommended Operating Conditions 建议操作条件:

CD4060典型应用电路

CD4060B典型振荡器连接:

上图-RC振荡器下图-晶体振荡器

RC振荡器中T=2.2R1C,R2=2*R1~10*R1

CD4060秒脉冲发生器电路:

图2 CD4060秒脉冲发生器

脉冲发生器是数字钟的核心部分,它的精度和稳定度决定了数字钟的质量,通常用晶体振荡器发出的脉冲经过整形、分频获得1Hz的秒脉冲。

如晶振为32768 Hz,通过15次二分频后可获得1Hz的脉冲输出,电路图如图2所示。