卷积码的仿真

44—RS和卷积编码Matlab仿真

RS编码clc; clear;m = 8; % Number of bits per symboln = 2^m-1; k = 223; % Word lengths for codedata = ceil(255*rand(20, 223)); % 构建20个随机生成的数据包msg = gf(data,m); % 生成伽罗华域,Three rows of m-bit symbolscode = rsenc(msg,n,k); % use RS encoder% 构建20个随机生成的错误,第i个包有i个错误,RS(255,223)可以纠正(n-k)/2=16个连续错误errs = tril(ones(20,20),0);errs = ceil(255*rand(20, 20).*errs);errs = [errs zeros(20,235)];errors = gf(errs,m);noisycode = code + errors; % 二进制模2加[dec,cnumerr] = rsdec(noisycode,n,k); % use RS decodercnumerrfor i=1:20if code(i)==dec(i)disp([num2str(i),' th message is decoded right']);elsedisp([num2str(i),' th message is decoded wrong']);endendMatlab输出:cnumerr =12345678910111213141516 ‐1 ‐1‐1‐11 th message is decoded right2 th message is decoded right3 th message is decoded right4 th message is decoded right5 th message is decoded right6 th message is decoded right7 th message is decoded right8 th message is decoded right9 th message is decoded right10 th message is decoded right11 th message is decoded right12 th message is decoded right13 th message is decoded right14 th message is decoded right15 th message is decoded right16 th message is decoded right17 th message is decoded wrong18 th message is decoded wrong 19 th message is decoded wrong20 th message is decoded wrong卷积编码:clc; clear;len = 1000;msg = randint(2*len,1); % Random binary message of 2-bit symbolstrel = poly2trellis([5 4],[23 35 0;0 5 13]); % Trelliscode = convenc(msg,trel); % Encode the message.ncode = rem(code + randerr(3*len,1,[0 1;.96 .04]),2); % Add noise.decoded = vitdec(ncode,trel,34,'cont','hard'); % Decode.[number,ratio] = biterr(decoded(68+1:end),msg(1:end-68));上图所示的结构,输入是1bit,输出是2bit,所以是一个1/2卷积编码器。

卷积码的编解码Matlab仿真与模拟讲解

卷积码的编解码Matlab仿真摘要卷积码是一种性能优越的信道编码。

它的编码器和译码器都比较容易实现,同时它具有较强的纠错能力。

随着纠错编码理论研究的不断深入,卷积码的实际应用越来越广泛。

本文简明地介绍了卷积码的编码原理和译码原理。

并在SIMULINK模块设计中,完成了对卷积码的编码和译码以及误比特统计整个过程的模块仿真。

最后,通过在仿真过程中分别改变卷积码的重要参数来加深理解卷积码的这些参数对卷积码的误码性能的影响。

经过仿真和实测,并对测试结果作了分析。

得出了以下三个结论:(1)当改变卷积码的码率时,系统的误码性能也将随之发生变化。

(2)对于码率一定的卷积码,当约束长度N 发生变化时,系统的误码性能也会随之发生变化。

(3)回溯长度也会不同程度上地影响误码性能。

关键词:卷积码;码率;约束长度;回溯长度目录论文总页数:21页1 引言 (1)1.1 课题背景 (1)1.2 国内外研究现状 (1)1.3 本课题的意义 (1)1.4 本课题的研究方法 (1)2 卷积码的基本概念 (2)2.1 信道 (2)2.2 纠错编码 (2)2.3 卷积码的基本概念 (2)2.4 卷积码编码的概念 (2)2.4.1 卷积编码 (2)2.4.2 卷积码的树状图 (3)2.4.3 卷积码的网格图 (4)2.4.4 卷积码的解析表示 (5)3 卷积码的译码 (6)3.1 卷积码译码的概述 (6)3.2 卷积码的最大似然译码 (6)3.3 VITEBI 译码的关键步骤 (7)3.3.1 输入与同步单元 (7)3.3.2 支路量度计算 (7)3.3.3 路径量度的存储与更新 (7)3.3.4 信息序列的存储与更新 (8)3.3.5 判决与输出单元 (8)4 结论 (9)4.1 卷积码的仿真 (9)4.1.1 SIMULINK仿真模块的参数设置以及重要参数的意义 (9)4.2 改变卷积码的参数仿真以及结论 (12)4.2.1 不同回溯长度对卷积码性能的影响 (12)4.2.2 不同码率对卷积码误码性能的响 (14)4.2.3 不同约束长度对卷积码的误码性能影响 (15)结论 (17)参考文献 (18)致谢.................................................... 错误!未定义书签。

通信综合课程设计 卷积码的实现与仿真

文章标题:深度解析通信综合课程设计中卷积码的实现与仿真引言:通信综合课程设计是通信工程领域的重要教育环节,而卷积码作为其中的重要内容之一,其实现与仿真更是学生们需要深入了解和掌握的技能。

本文将从简到繁地讨论通信综合课程设计中卷积码的实现与仿真,帮助读者更好地理解和掌握这一重要内容。

第一部分:通信综合课程设计概述1.1 通信综合课程设计的重要性在通信工程领域,通信综合课程设计是学生将在实际工作中常常用到的实践环节,通过这一环节,学生们可以将所学的理论知识应用到实际项目中,提高实践能力和解决问题的能力。

1.2 通信综合课程设计的内容概述通信综合课程设计内容丰富多样,包括调制解调、信道编码、卷积码、纠错码等多个主题,而卷积码的实现与仿真是其中的重要部分之一。

第二部分:卷积码的基本原理2.1 卷积码的定义卷积码是一种线性时不变系统(LTI)编码器,在通信系统中起到纠错码的作用。

2.2 卷积码的编码和解码原理通过引入时延、存储元素和加法器,实现对输入序列进行编码;而解码过程则是通过译码器进行,根据输入序列和已知的编码规则进行解码。

第三部分:通信综合课程设计中卷积码的实现3.1 卷积码的软件实现在通信综合课程设计中,学生们可以利用MATLAB等软件工具,编写程序实现卷积码的编码和解码过程,从而加深对卷积码原理的理解。

3.2 卷积码的硬件实现除了软件实现,通信综合课程设计中也常常涉及到卷积码的硬件实现,学生们可以通过FPGA等硬件开发评台,实现卷积码的编码和解码过程。

第四部分:通信综合课程设计中卷积码的仿真4.1 仿真环境的建立在通信综合课程设计中,学生们需要建立仿真环境,包括信道模型、信号源、噪声源等,以便对卷积码的性能进行评估。

4.2 仿真结果的分析通过仿真实验,学生们可以得到卷积码在不同信噪比下的误码率曲线等性能参数,从而对卷积码的性能有更深入的了解。

结论:通过本文的深入讨论,相信读者已经对通信综合课程设计中卷积码的实现与仿真有了更深入的理解。

通信原理课程设计卷积码过失操纵系统的仿真

《移动通信》课程设计报告课程设计题目:卷积码过失操纵系统的仿真系:三系学生姓名:张欣班级:通信工程(1)班学号: 117成绩:指导教师:马英辉开课时刻: 2021—2021 学年 2 学期目录第一章引言.................................................... - 0 - 题目...................................................... - 0 - 课程设计目的............................................. - 0 - 课程设计的要紧内容和要求.............................. - 0 - 第二章原理.................................................... - 1 - 卷积码.................................................... - 1 - 卷积码的算法............................................. - 1 - 维特比译码原理:........................................... - 3 - 第三章仿真进程................................................ - 6 - 仿真模拟框图........................................... - 6 - 各部件的配置........................................... - 7 - 结论......................................................... - 11 - 心得体会...................................................... - 12 - 参考文献...................................................... - 13 - 附录......................................................... - 14 -第一章引言题目卷积码过失操纵系统的仿真课程设计目的移动通信也是一门实践性超级强的课程,实验教学在整个课程的教学中占据了超级重要的地位。

卷积码(或者Turbo码)的交织与解交织的仿真编程和仿真实验

卷积码(或者Turbo码)的交织与解交织的仿真编程和仿真实验一、实验目的实现卷积码(或者Turbo码)的交织与解交织的仿真编程和仿真实验,观察交织编码分别在白噪声信道和衰落信道下系统误码率的影响,分析原因。

二、实验原理信道编码中采用交织技术,可打乱码字比特之间的相关性,将信道中传输过程中的成群突发错误转换为随机错误,从而提高整个通信系统的可靠性。

交织编码根据交织方式的不同,可分为线性交织、卷积交织和伪随机交织。

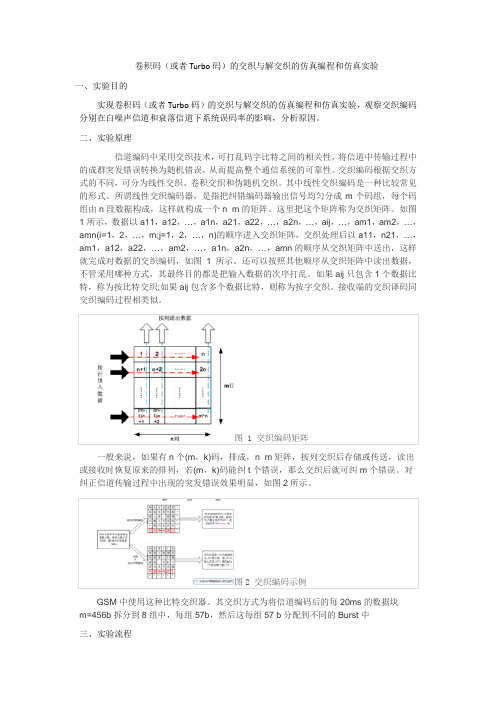

其中线性交织编码是一种比较常见的形式。

所谓线性交织编码器,是指把纠错编码器输出信号均匀分成m个码组,每个码组由n段数据构成,这样就构成一个n×m的矩阵。

这里把这个矩阵称为交织矩阵。

如图1所示,数据以a11,a12,…,a1n,a21,a22,…,a2n,…,aij,…,am1,am2,…,amn(i=1,2,…,m;j=1,2,…,n)的顺序进入交织矩阵,交织处理后以a11,n21,…,am1,a12,a22,…,am2,…,a1n,a2n,…,amn的顺序从交织矩阵中送出,这样就完成对数据的交织编码,如图1所示。

还可以按照其他顺序从交织矩阵中读出数据,不管采用哪种方式,其最终目的都是把输入数据的次序打乱。

如果aij只包含1个数据比特,称为按比特交织;如果aij包含多个数据比特,则称为按字交织。

接收端的交织译码同交织编码过程相类似。

图 1 交织编码矩阵一般来说,如果有n个(m,k)码,排成,n×m矩阵,按列交织后存储或传送,读出或接收时恢复原来的排列,若(m,k)码能纠t个错误,那么交织后就可纠m个错误。

对纠正信道传输过程中出现的突发错误效果明显,如图2所示。

图2 交织编码示例GSM中使用这种比特交织器。

其交织方式为将信道编码后的每20ms的数据块m=456b拆分到8组中,每组57b,然后这每组57 b分配到不同的Burst中三、实验流程卷积交织解卷积交织四、源程序1、交织程序1)卷积交织function [aa]=jiaozhi(bb,n)%jiaozhi.m 卷积交织函数n=28; %分组长度%bb 卷积交织前原分组序列%aa 卷积交织后分组序列%序号重排方式:cc=[ 1 23 17 11 5 17 21; 8 2 24 18 12 6 28; 15 9 3 25 19 13 7; 22 16 10 4 26 20 14 ];%交织矩阵bb=[ 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 25 26 27 28];for i=1:naa(i)=bb(cc(i));end(2)循环等差交织function [aa]=jiaozhi_nocnv(bb,n)%jiaozhi_nocnv.m 循环等差交织函数n=28; %分组长度%bb 循环等差交织前原分组序列%aa 循环等差交织后还原分组序列%序号重排方式:bb=[ 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 25 26 27 28 ]; j=1;for i=1:nj=rem(j+5-1,n)+1; %序号重排方式迭代算法aa(n+1-i)=bb(j);end2、解交织程序(1)解卷积交织function [bb]=jiejiaozhi(aa,n)%jiejiaozhi.m 解卷积交织函数n=28;% 分组长度%aa 解卷积交织前原分组序列%bb 解卷积交织后分组序列%序号重排方式:cc=[ 1 23 17 11 5 27 21; 8 2 24 18 12 6 28; 15 9 3 25 19 13 7 ;22 16 10 4 26 20 14 ]; aa=[ 1 8 15 22 23 2 9 16 17 24 3 10 11 18 25 4 5 12 19 26 27 6 13 20 21 28 7 14 ]; for i=1:nbb(cc(i))=aa(i);end(2)解循环等差交织function [bb]=jiejiaozhi_nocnv(aa,n)%jiaozhi_nocnv.m 解循环等差交织函数n=28;% 分组长度%aa 解循环等差交织前原分组序列%bb 解循环等差交织后还原分组序列%序号重排方式:aa=[ 1 24 19 14 9 4 27 22 17 12 7 2 25 20 15 10 5 28 23 18 13 8 3 26 21 16 11 6];j=1;for i=1:nj=rem(j+5-1,n)+1; %序号重排方式迭代算法bb(j)=aa(n+1-i);End交织码通常表示为(M,N),分组长度L=MN,交织方式用M行N列的交织矩阵表示。

卷积码的维特比译码原理及仿真

卷积码的维特比译码原理及仿真摘 要 本课程设计主要解决对一个卷积码序列进行维特比(Viterbi)译码输出,并通过Matlab 软件进行设计与仿真,并进行误码率分析。

实验原理QPSK :QPSK 是英文QuadraturePhaseShiftKeying 的缩略语简称,意为正交相移键控,是一种数字调制方式。

四相相移键控信号简称“QPSK ”。

它分为绝对相移和相对相移两种。

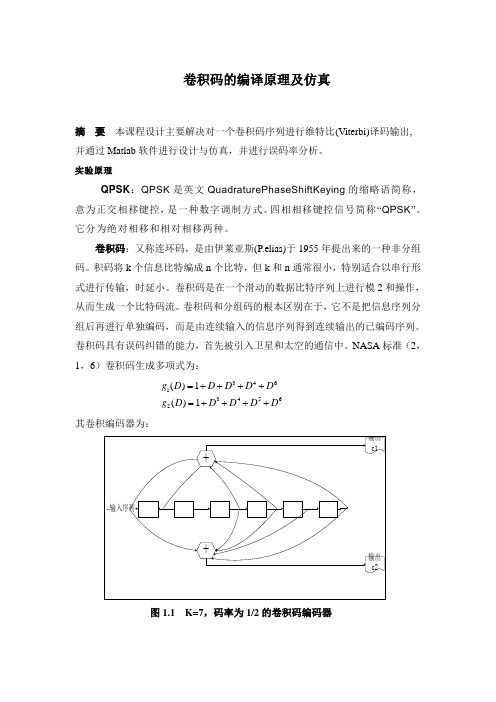

卷积码:又称连环码,是由伊莱亚斯(P.elias)于1955年提出来的一种非分组码。

积码将k 个信息比特编成n 个比特,但k 和n 通常很小,特别适合以串行形式进行传输,时延小。

卷积码是在一个滑动的数据比特序列上进行模2和操作,从而生成一个比特码流。

卷积码和分组码的根本区别在于,它不是把信息序列分组后再进行单独编码,而是由连续输入的信息序列得到连续输出的已编码序列。

卷积码具有误码纠错的能力,首先被引入卫星和太空的通信中。

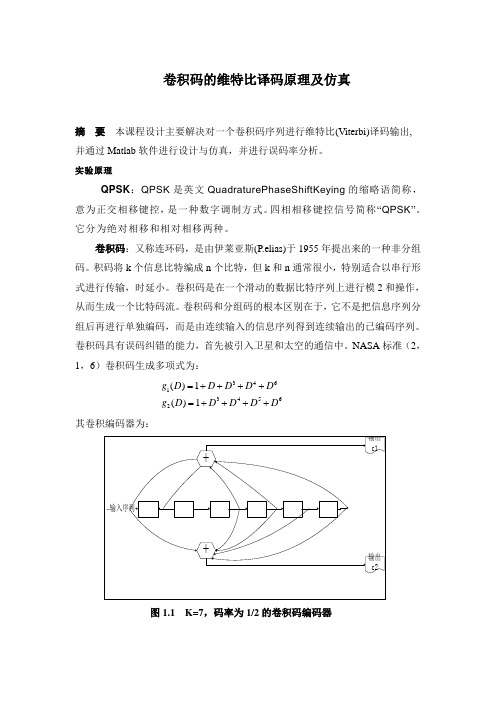

NASA 标准(2,1,6)卷积码生成多项式为: 346134562()1()1g D D D D D g D D D D D=++++=++++其卷积编码器为:图1.1 K=7,码率为1/2的卷积码编码器维特比译码:采用概率译码的基本思想是:把已接收序列与所有可能的发送序列做比较,选择其中码距最小的一个序列作为发送序列。

如果接收到L 组信息比特,每个符号包括v 个比特。

接收到的Lv 比特序列与2L 条路径进行比较,汉明距离最近的那一条路径被选择为最有可能被传输的路劲。

当L 较大时,使得译码器难以实现。

维特比算法则对上述概率译码做了简化,以至成为了一种实用化的概率算法。

它并不是在网格图上一次比较所有可能的2kL 条路径(序列),而是接收一段,计算和比较一段,选择一段最大似然可能的码段,从而达到整个码序列是一个最大似然值得序列。

下面以图2.1的(2,1,3)卷积码编码器所编出的码为例,来说明维特比解码的方法和运作过程。

matlab(n,k,m)卷积码原理及仿真

matlab(n,k,m)卷积码原理及仿真====================卷积码是一种重要的纠错码,它在通信系统中扮演着重要的角色。

特别是在高噪环境下,卷积码具有较好的性能表现,因此被广泛用于卫星通信、光纤通信等领域。

本文将介绍Matlab中实现(n,k,m)卷积码的基本原理以及仿真过程。

一、卷积码原理-------卷积码是一种非线性编码技术,它通过将信息序列与多个冗余序列进行卷积运算,生成新的编码序列。

卷积码具有较高的编码增益,同时具有较低的编码复杂度。

在(n,k,m)卷积码中,n表示编码长度,k 表示信息比特数,m表示每个码字所包含的冗余比特数。

二、Matlab仿真环境---------Matlab是一种强大的数学计算和仿真软件,它提供了丰富的工具和函数库,可以方便地实现各种数字通信系统。

在Matlab中,我们可以利用卷积码工具箱实现(n,k,m)卷积码的编码、译码和仿真。

三、仿真步骤------1.定义系统参数:包括信息比特数k、编码长度n、冗余比特数m 等。

2.生成随机信息序列:在Matlab中,可以使用rand函数生成随机比特序列作为信息序列。

3.编码:使用卷积码工具箱中的函数实现编码过程,生成冗余比特序列。

4.添加噪声:在通信系统中,噪声是不可避免的。

为了模拟高噪环境,可以在编码后的数据上添加高斯噪声。

5.译码:使用卷积码工具箱中的函数实现译码过程,恢复原始信息序列。

6.仿真结果分析:通过比较译码结果和原始信息序列,可以评估卷积码的性能。

四、示例代码------以下是一个简单的Matlab代码示例,用于实现(7,4,3)卷积码的编码、译码和仿真:```matlab%定义系统参数k=4;%信息比特数n=7;%编码长度m=3;%冗余比特数data=randi([0k-1],n,1);%生成随机信息序列noise=sqrt(0.1)*data+sqrt(0.9)*(randn(n,1));%添加高斯噪声con_code=codegen(k,m);%编码encoded=conv_mat(data',con_code');%卷积码矩阵表示法decoded=indelcod(con_code);%译码%比较译码结果和原始信息序列ifall(decoded==data)disp('译码成功!')elsedisp('译码失败!')end```五、总结----Matlab作为一种强大的数学计算和仿真软件,提供了丰富的工具和函数库,可以方便地实现各种数字通信系统。

卷积编码设计与仿真实验报告

卷积编码设计与仿真实验报告一、实验目的了解卷积码对信号的纠错性能,掌握维特比译码算法,分析卷积码不同码率下纠错能力的强弱,深刻理解CCSDS标准、信道编译码等相关概念和算法。

二、实验内容1、自己编码实现(2,1,3)卷积码的编译码,对比不同信噪比条件下,是否采用编码对于误码率性能的影响;2、基于MATLAB自带的vitdec函数实现对(2,1,7)卷积码以及2/3、3/4码率删除码的编译码,并对于不同码率抗噪声能力的强弱;3、构造BPSK调制、加性高斯白噪声的传输环境。

三、实验原理卷积码一般表示为(n,k,N)的形式,即将k个信息比特编码为n个比特的码组,N为编码约束长度,说明编码过程中相互约束的码段个数。

卷积码编码后的n个码元不仅与当前组的k个信息比特有关,还与前N-1个输入组的信息比特有关。

编码过程中相互关联的码元有N*n个。

R=k/n是编码效率。

编码效率和约束长度是衡量卷积码的两个重要参数。

典型的卷积码一般选n,k较小,但N值可取较大(>10),以获得简单而高性能的卷积码。

1、卷积码的编码原理卷积码的编码器一般比较简单,为一个具有k个输入端,n个输出端,m 级移位寄存器的有限状态有记忆系统。

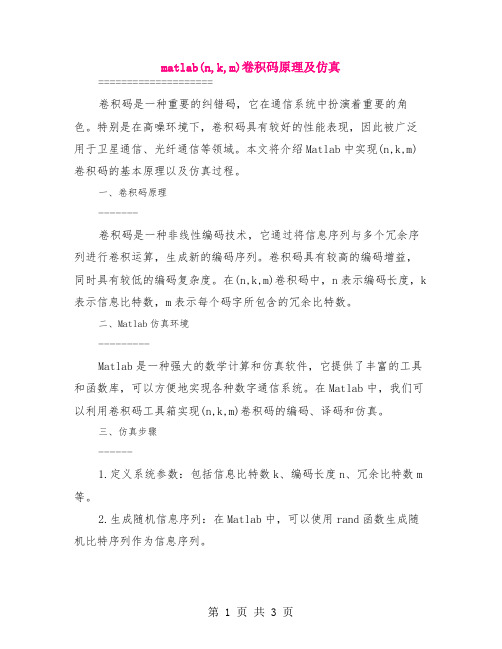

下图所示为(2,1,7)卷积码的编码器。

图1 (2,1,7)卷积码编码器若输入序列为u=(u0u1u2u3……),则对应两个码字序列 C1=(ca0ca1ca2ca3……)和C2=(cb0cb1cb2cb3……),相应的编码方程可写为 P1=u*C1,P2=u*C2,P=(P1,P2)。

“*”符号表示卷积运算,P1,P2表示编码器的两个冲激响应,即编码器的输出可以由输入序列和编码器的两个冲击响应卷积而得到,故称为卷积码。

这里的冲激响应指:当输入为[1 0 0 0 0 … … ]序列时,所观察到的两个输出序列值。

由于上图N 值为7,故冲激响应至多可持续到第7位,可写为P1=[1 1 1 1 0 0 1],P2=[1 0 1 1 0 1 1]然后将两个输出端的码字序列合并为一个码字序列为C=(ca0cb0ca1cb1ca2cb2……)。

卷积码编译码matlab仿真

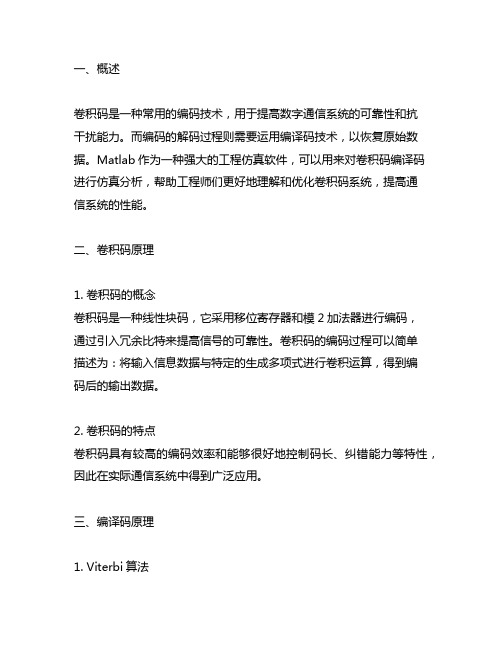

一、概述卷积码是一种常用的编码技术,用于提高数字通信系统的可靠性和抗干扰能力。

而编码的解码过程则需要运用编译码技术,以恢复原始数据。

Matlab作为一种强大的工程仿真软件,可以用来对卷积码编译码进行仿真分析,帮助工程师们更好地理解和优化卷积码系统,提高通信系统的性能。

二、卷积码原理1. 卷积码的概念卷积码是一种线性块码,它采用移位寄存器和模2加法器进行编码,通过引入冗余比特来提高信号的可靠性。

卷积码的编码过程可以简单描述为:将输入信息数据与特定的生成多项式进行卷积运算,得到编码后的输出数据。

2. 卷积码的特点卷积码具有较高的编码效率和能够很好地控制码长、纠错能力等特性,因此在实际通信系统中得到广泛应用。

三、编译码原理1. Viterbi算法卷积码的译码过程通常采用Viterbi算法,它是一种最大似然译码算法,通过计算最小距离路径的方式来进行译码。

Viterbi算法能够有效地对卷积码进行解码,提高译码的准确性。

2. 编译码的实现在Matlab中,编译码的实现通常是通过编写一定的程序来模拟Viterbi算法的译码过程。

通过仿真分析,可以评估不同的编码方案对通信系统性能的影响。

四、Matlab仿真环境1. Matlab的特点Matlab作为一种强大的仿真软件,具有丰富的工具和函数库,能够方便地进行数字通信系统设计与仿真分析。

Matlab提供了直观的图形界面和强大的数据处理能力,可用于展示仿真结果和进行数据分析。

2. 使用Matlab进行卷积码编译码仿真在Matlab环境中,可以编写程序来实现卷积码的编码和Viterbi算法的译码过程。

通过调用Matlab中的工具函数和绘图函数,可以直观地展示通信系统的性能指标,并对比不同编码方式的性能差异。

五、仿真实例分析1. 卷积码编码仿真我们可以编写Matlab程序,实现对卷积码的编码过程。

通过模拟不同的编码率和约束长度,可以观察到编码后的效果,并评估编码的性能。

对卷积码的编译码实现进行仿真编程和仿真实验

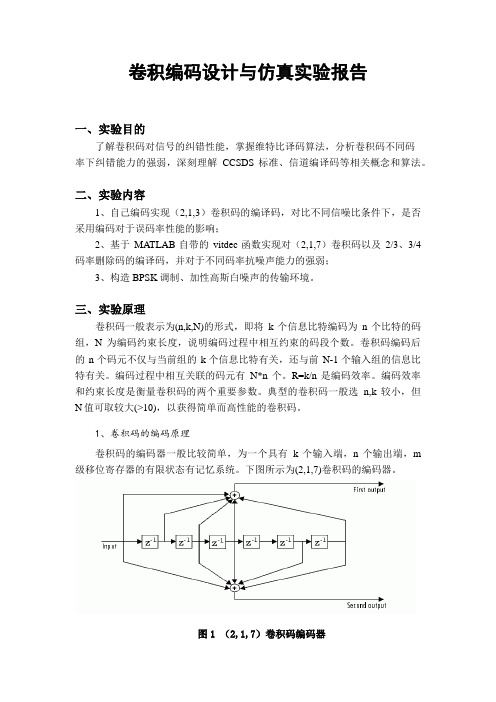

实验二:卷积码编译器1120510217 吴宏晶一、实验目的对卷积码的编译码实现进行仿真编程和仿真实验二、仿真软件LabVIEW 2013版(前面版用于数据显示,后面板为程序源代码)三、实验流程1.卷积码的编码以(3,1,2)卷积码为例,下图为LabVIEW仿真前面板每一时刻都有一个信息比特进入第一个寄存器中,如图中D1。

编码器利用D1和D2这两个寄存器来产生3比特的输出码字如图中所示C1、C2、C3。

编码的规则是C1=M1,C2=M1+D1+D2,C3=M1+D2。

定义D1和D2的状态为S1和S2,S1和S2共有四种组合状态。

描述的在不同的输入比特状态下,编码器对应的输出和下一个时刻的状态变化。

它们的转化关系如下图所示2.卷积码的译码卷积码的译码采用维特比译码法。

维特比算法的思路:在每个节点处,留下到达该节点处局部度量最大的路径,丢弃其余的局部路径,这条留下来的路径叫做幸存路径。

如果所有幸存路径在某个支路处是重合的,就可以输出这个支路上数据的译码结果。

为了避免延时,在当前局部路径中,找出局部累积量最大的,沿着这个路径回退N步会有一个分支,输出这个分支的数据。

(3,1,2)卷积码t0~t5六个时刻,第一次选取幸存路径发生在从t2到t3转移时刻。

四、实验源程序说明1.卷积码的编码程序源代码如下图所示1.坐标1处是输入码元数组,它经过一个FOR循环依次进入循环中。

2.坐标2处是D1和D2两个移位寄存器,D1的结果在一次循环过后移入D2中。

3.坐标3处表示C1的值为每次直接进来的码元值。

4.坐标4处为C2的计算值,对局部进行放大,有如下图说明:C2=D1+D2+M1(模2加法),M1为码元值。

因为没有模2加法的函数,故调用除2函数,再对余数与0进行比较是否相等,若结果为TRUE,则表明C2为2的倍数,即为0,故将0送入C2中,否则将1送入C2中。

5.坐标5处为C3的计算值,对局部进行放大,有如下图说明:C3=M1+C2,故将两数相加,再对结果与1比较,因为只有01或10相加才为1,其他值为0或者2,故若判断结果为TRUE,则将1的值赋值给C3,如上图所示。

基于EDA技术的卷积码编码器的设计与仿真

基于EDA技术的卷积码编码器的设计与仿真文章设计基于EDA技术,以(2,1,3)卷积码为例,阐述了其基本设计原理,在软件平台Quartus II上,通过电路设计和VHDL程序设计两种方式进行了设计和波形仿真。

通过验证,其运算结果与波形一致。

标签:EDA;卷积码;编码器引言卷积码是深度空间通信系统和无线通信系统中常用的一种差错控制编码。

在编码过程中,卷积码充分利用了各码字间的相关性。

在与分组码同样的码率和设备复杂性的条件下,无论从理论上还是从实践上都证明,卷积码的性能都比分组码具有优势。

而且卷积码在实现最佳译码方面也较分组码容易。

因此卷积码广泛应用于卫星通信,CDMA数字移动通信等通信系统,是很有前途的一种编码方式。

对其进行研究有很大的现实意义[1]。

同时,随着EDA技术的发展和应用领域的不断拓展与深入,EDA技术在电子信息、通信、自动控制计算机等领域的应用性越来越明显。

文章以(2,1,3)卷积码为例,介绍了卷积码编码原理和编码过程,并在EDA工具-Quartus II平台下,通过电路设计和VHDL程序设计两种方式实现卷积码编码器的设计并得出仿真结果。

1 EDA工具软件介绍EDA的工具软件依照使用功能,可分为电路设计与仿真工具、PCB设计软件、IC设计软件和CPLD/FPGA设计工具[2]。

目前被广泛使用的电路设计与仿真工具有Protel、PSPICE、multiSIM10、Matlab、Quartus II等等。

较强的实现功能使这些软件应用于多个方面,例如很多软件都可以进行电路设计与仿真,进行PCB自动布局布线,同时还能够输出多种网表文件与第三方软件接口。

本设计选用的EDA工具平台-Quartus II 是一种关于CPLD和FPGA的开发集成环境,它是由世界上最大的可编程逻辑器件公司之一的Altera提供。

Quartus II 是MAX+plusⅡ更新换代产品,使用更加方便,操作界面更加的人性化。

卷积码差错系统控制的仿真

《移动通信》课程设计报告课题题目:卷积码差错系统控制的仿真年级:通信姓名:***学号:11指导老师:2011年6月16日第一章引言 (1)1.1 课程设计的目的 (1)1.2 课程设计的要求与思路 (2)第二章原理 (3)2.1 卷积码 (3)2.2 卷积码的维特比译码 (3)第三章Matlab中卷积码译码器的设计过程与仿真 (5)3.1 仿真框图模型 (5)3.2 各部分模块参数设置 (6)第四章Matlab中卷积码译码器的误码率分析 (10)第五章总结 (12)5.1心得体会 (12)5.2参考文献 (12)卷积码差错系统控制的仿真第一章引言本课程设计主要解决对一个卷积码序列进行维特比(Viterbi)译码输出,并通过Matlab软件进行设计与仿真。

卷积码的译码有两种方法(软判决和硬判决),此课程设计采用硬判决的维特比译码。

1.1课程设计的目的1、熟悉Simulink与通信仿真;2、掌握通信系统的构成;实现信息传递所需的一切技术设备和传输媒质的总和称为通信系统。

以基本的点对点通信为例,通信系统的组成[1],如图1-1 所示。

图1-1 通信系统的的模型图中,信源(信息源,也称发终端)的作用是把待传输的消息转换成原始电信号,如电话系统中电话机可看成是信源。

信源输出的信号称为基带信号。

所谓基带信号是指没有经过调制(进行频谱搬移和变换)的原始电信号,其特点是信号频谱从零频附近开始,具有低通形式,。

根据原始电信号的特征,基带信号可分为数字基带信号和模拟基带信号,相应地,信源也分为数字信源和模拟信源。

发送设备的基本功能是将信源和信道匹配起来,即将信源产生的原始电信号(基带信号)变换成适合在信道中传输的信号。

变换方式是多种多样的,在需要频谱搬移的场合,调制是最常见的变换方式;对传输数字信号来说,发送设备又常常包含信源编码和信道编码等。

信道是指信号传输的通道,可以是有线的,也可以是无线的,甚至还可以包含某些设备。

卷积码差错控制的系统仿真

第一章引言 (1)1.1课程设计目的 (1)1.2课程设计要求 (1)第二章原理 (2)2.1卷积码 (2)2.2卷积码的算法 (2)2.3卷积码的Viterbi译码 (2)第三章Matlab中卷积码译码器的设计过程与仿真 (5)3.1 Matlab维特比译码器模块介绍 (5)3.2Matlab中卷积码维特比译码器的设计 (6)第四章Matlab中卷积码译码器的误码率分析 (10)第五章总结 (12)卷积码差错控制的系统仿真第一章引言1.1课程设计目的利用系统开发平台Windows xp,通过Matlab(7.0)软件进行设计与仿真,对一个卷积码序列进行维特比(Viterbi)译码输出,并进行误码率分析。

1.2课程设计要求1)用子系统来实现,系统包括:信源部分、信道部分、新宿部分。

2)信源部分的数据源采用随机二进制序列,并对其进行卷积码调制。

3)信道部分对调制后的信号加译。

4)信宿部分对信号调制及维比特译码。

5)编程实现波形,实现误码分析。

第二章原理2.1卷积码卷积码是1955年由爱里斯(Elias)提出的一种性能优越的信道编码。

他通常用( n,K,N)表示,他是把K个信息比特编成n个信息比特,但K和n通常很小,特别适宜于以串行方式传输信息,延时小。

N为编码约束长度,说明编码过程中互相约束的码段个数。

卷积码编码后的n个码元不仅与当前组的k个信息比特有关,而且与前N一1个输入组的信息比特有关。

编码过程中相互关联的码元有N×n个。

R=k/n.是卷积码的码率,码率和约束长度是衡量卷积码的两个重要参数。

卷积码广泛应用在无线通信标准中,如GSM,CDMA2000,IS一95中。

2.2卷积码的算法卷积码的编码描述方法有5种:冲激响应描述法、生成矩阵描述法、多项式乘积描述法、状态图描述法和网格图描述法。

图1.1卷积码编码器由于可以通过将按时间移位的脉冲进行线性叠加,或者将输入序列和编码器的脉冲响应相卷积,来产生输出编码,因此这种编码器称为卷积编码器。

卷积码的编译码原理和仿真 论文

卷积码的编译原理及仿真摘 要 本课程设计主要解决对一个卷积码序列进行维特比(Viterbi)译码输出,并通过Matlab 软件进行设计与仿真,并进行误码率分析。

实验原理QPSK :QPSK 是英文QuadraturePhaseShiftKeying 的缩略语简称,意为正交相移键控,是一种数字调制方式。

四相相移键控信号简称“QPSK ”。

它分为绝对相移和相对相移两种。

卷积码:又称连环码,是由伊莱亚斯(P.elias)于1955年提出来的一种非分组码。

积码将k 个信息比特编成n 个比特,但k 和n 通常很小,特别适合以串行形式进行传输,时延小。

卷积码是在一个滑动的数据比特序列上进行模2和操作,从而生成一个比特码流。

卷积码和分组码的根本区别在于,它不是把信息序列分组后再进行单独编码,而是由连续输入的信息序列得到连续输出的已编码序列。

卷积码具有误码纠错的能力,首先被引入卫星和太空的通信中。

NASA 标准(2,1,6)卷积码生成多项式为:346134562()1()1g D D D D Dg D D D D D=++++=++++ 其卷积编码器为:输入序列++输出c1输出c2图1.1 K=7,码率为1/2的卷积码编码器维特比译码:采用概率译码的基本思想是:把已接收序列与所有可能的发送序列做比较,选择其中码距最小的一个序列作为发送序列。

如果接收到L 组信息比特,每个符号包括v 个比特。

接收到的Lv 比特序列与2L 条路径进行比较,汉明距离最近的那一条路径被选择为最有可能被传输的路劲。

当L 较大时,使得译码器难以实现。

维特比算法则对上述概率译码做了简化,以至成为了一种实用化的概率算法。

它并不是在网格图上一次比较所有可能的2kL 条路径(序列),而是接收一段,计算和比较一段,选择一段最大似然可能的码段,从而达到整个码序列是一个最大似然值得序列。

下面以图2.1的(2,1,3)卷积码编码器所编出的码为例,来说明维特比解码的方法和运作过程。

卷积码的仿真与分析-信息论报告

三级项目报告课程名称:信息论与编码___________ 课程设计题目:卷积码的仿真与分析_______指导教师:______________系别:专业:学号:姓名: _____合作者完成时间: 2012 年 6 月 10 日至 6 月 14 日成绩:评阅人:1. 卷积码及其编译码原理概述非分组码的卷积码的编码器是在任一段规定时间内产生n 个码元,但它不仅取决于这段时间中的k 个信息位,还取决于前(K -1)段规定时间内的信息位,这K 段时间内的码元数目为K ·k ,称参数K 为卷积码的约束长度,每k 个比特输入,得到n 比特输出,编码效率为k /n ,约束长度为K 。

在k =1的条件下,移位寄存器级数m =K -1。

卷积码一般可用(n ,k ,K )来表示,其中k 为输入码元数,n 为输出码元数,而K 则为编码器的约束长度。

典型的卷积码一般选n 和k ( k < n ) 值较小,但约束长度K 可取较大值(K <10),以获得既简单又高性能的信道编码[6]。

卷积码是1955年Elias 最早提出,1957年Wozencraft 提出了序列译码。

1963年Massey 提出了一种性能稍差,但比较实用的门限译码方法。

1967年维特比(Viterbi)提出了最大似然译码。

它对存储器级数较小的卷积码的译码很容易实现,称为维特比算法或维特比译码。

图1、二进制卷积码的编码器图2给出了(3,1,2)二进制卷积码编码器。

在每一时间单位,输入一个比特信息i m,同时存贮器内的数据向右移一位,产生3个比特的输出i c ,其中一个是输入比特i m,两个是校验比特,1i p ,,2i p 。

图2由图可知: ,12,212i i i i i i i p m m p m m m ---=⊕=⊕⊕因为校验比特是输入信息元i m的模2和,它们是线性关系,所以这类卷积码是线性码。

称i c为卷积码的一个子码或码段,它不仅与当前输入信息有关,还与前2个(m )时间单位的输入信息有关,即和前2个子码有关;而且i m要经过2个时间单位才能移出存贮器,所以i c 也参与了后2个子码中的校验运算,称1N m =+为编码约束度,说明编码过程中互相约束的码段个数。

卷积码,循环码差错控制仿真

移动通信方向课程设计卷积码差错控制系统仿真学生姓名学号所在学院通信工程学院专业名称移动通信班级移动通信方向2班指导教师成绩二○一五年五月课程设计任务书卷积码差错控制系统的仿真内容摘要:卷积码(Convolution code)是由伊利亚斯(p.Elias)发明的一种非分组码。

在前向纠错系统中,卷积码在实际应用中的性能优于分组码,并且运算较简单。

维特比译码算法基本原理是:将接收到的信号序列和所有可能的发送信号序列比较,选择其中汉明距离最小的序列认为是当前发送序列。

关键词:卷积码维特比译码算法Convolution code error control system simulation Abstract:Convolution code (convolutional code) is by ilias (p.E lias) invented a kind of block code. In the forward error correction system, convolution code in the actual application performance is better than that of block codes, and the operation is relatively simple.Viterbi decoding algorithm basic principle is: will the received signal sequence and all possible signal sequence comparison, choose the hamming distance is the smallest sequence that currently sending sequence. Keywords:Convolution code Viterbi decoding algorithm目录1前言 (1)1.1题目 (1)1.2课程设计的目的 (1)1.3课程设计的主要内容和要求 (1)1.3.1课程设计的主要内容: (1)1.3.2课程设计的要求: (1)2课程设计原理 (1)2.1卷积码的定义 (1)2.2卷积码的编码原理 (2)2.3卷积码的译码过程 (2)2.4维特比译码 (2)2.4.1维特比译码原理 (2)2.4.2维特比译码过程 (3)3仿真过程 (5)3.1仿真模拟框图 (5)3.2各部件的配置 (6)4系统运行代码 (12)4.1系统运行源代码 (12)5结束语 (13)参考文献 (14)卷积码差错控制系统的仿真1前言1.1题目卷积码差错控制系统的仿真1.2课程设计的目的移动通信也是一门实践性非常强的课程,实验教学在整个课程的教学中占据了非常重要的地位。

卷积码差错控制的系统仿真

第一章引言 (1)1.1课程设计目的 (1)1.2课程设计要求 (1)第二章原理 (2)2.1卷积码 (2)2.2卷积码的算法 (2)2.3卷积码的Viterbi译码 (2)第三章Matlab中卷积码译码器的设计过程与仿真 (5)3.1 Matlab维特比译码器模块介绍 (5)3.2Matlab中卷积码维特比译码器的设计 (6)第四章Matlab中卷积码译码器的误码率分析 (10)第五章总结 (12)卷积码差错控制的系统仿真第一章引言1.1课程设计目的利用系统开发平台Windows xp,通过Matlab(7.0)软件进行设计与仿真,对一个卷积码序列进行维特比(Viterbi)译码输出,并进行误码率分析。

1.2课程设计要求1)用子系统来实现,系统包括:信源部分、信道部分、新宿部分。

2)信源部分的数据源采用随机二进制序列,并对其进行卷积码调制。

3)信道部分对调制后的信号加译。

4)信宿部分对信号调制及维比特译码。

5)编程实现波形,实现误码分析。

第二章原理2.1卷积码卷积码是1955年由爱里斯(Elias)提出的一种性能优越的信道编码。

他通常用( n,K,N)表示,他是把K个信息比特编成n个信息比特,但K和n通常很小,特别适宜于以串行方式传输信息,延时小。

N为编码约束长度,说明编码过程中互相约束的码段个数。

卷积码编码后的n个码元不仅与当前组的k个信息比特有关,而且与前N一1个输入组的信息比特有关。

编码过程中相互关联的码元有N×n个。

R=k/n.是卷积码的码率,码率和约束长度是衡量卷积码的两个重要参数。

卷积码广泛应用在无线通信标准中,如GSM,CDMA2000,IS一95中。

2.2卷积码的算法卷积码的编码描述方法有5种:冲激响应描述法、生成矩阵描述法、多项式乘积描述法、状态图描述法和网格图描述法。

图1.1卷积码编码器由于可以通过将按时间移位的脉冲进行线性叠加,或者将输入序列和编码器的脉冲响应相卷积,来产生输出编码,因此这种编码器称为卷积编码器。

卷积码的MATLAB仿真设计

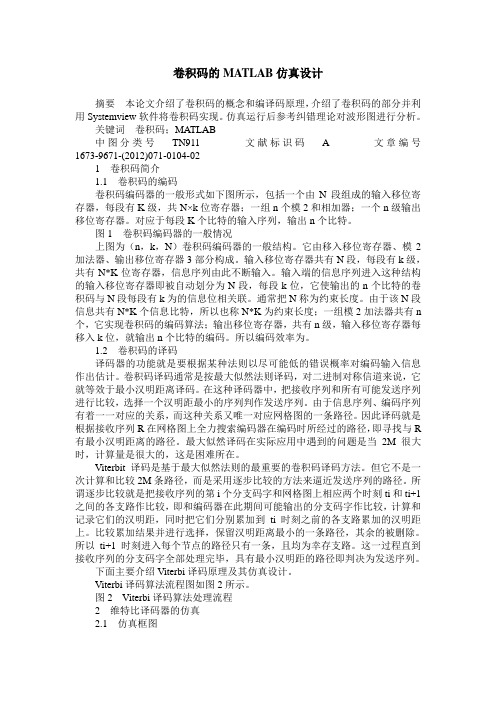

卷积码的MATLAB仿真设计摘要本论文介绍了卷积码的概念和编译码原理,介绍了卷积码的部分并利用Systemview软件将卷积码实现。

仿真运行后参考纠错理论对波形图进行分析。

关键词卷积码;MATLAB中图分类号TN911 文献标识码 A 文章编号1673-9671-(2012)071-0104-021 卷积码简介1.1 卷积码的编码卷积码编码器的一般形式如下图所示,包括一个由N段组成的输入移位寄存器,每段有K级,共N×k位寄存器;一组n个模2和相加器;一个n级输出移位寄存器。

对应于每段K个比特的输入序列,输出n个比特。

图1 卷积码编码器的一般情况上图为(n,k,N)卷积码编码器的一般结构。

它由移入移位寄存器、模2加法器、输出移位寄存器3部分构成。

输入移位寄存器共有N段,每段有k级,共有N*K位寄存器,信息序列由此不断输入。

输入端的信息序列进入这种结构的输入移位寄存器即被自动划分为N段,每段k位,它使输出的n个比特的卷积码与N段每段有k为的信息位相关联。

通常把N称为约束长度。

由于该N段信息共有N*K个信息比特,所以也称N*K为约束长度;一组模2加法器共有n 个,它实现卷积码的编码算法;输出移位寄存器,共有n级,输入移位寄存器每移入k位,就输出n个比特的编码。

所以编码效率为。

1.2 卷积码的译码译码器的功能就是要根据某种法则以尽可能低的错误概率对编码输入信息作出估计。

卷积码译码通常是按最大似然法则译码,对二进制对称信道来说,它就等效于最小汉明距离译码。

在这种译码器中,把接收序列和所有可能发送序列进行比较,选择一个汉明距最小的序列判作发送序列。

由于信息序列、编码序列有着一一对应的关系,而这种关系又唯一对应网格图的一条路径。

因此译码就是根据接收序列R在网格图上全力搜索编码器在编码时所经过的路径,即寻找与R 有最小汉明距离的路径。

最大似然译码在实际应用中遇到的问题是当2M很大时,计算量是很大的,这是困难所在。

采用8QAM调制和卷积码技术仿真

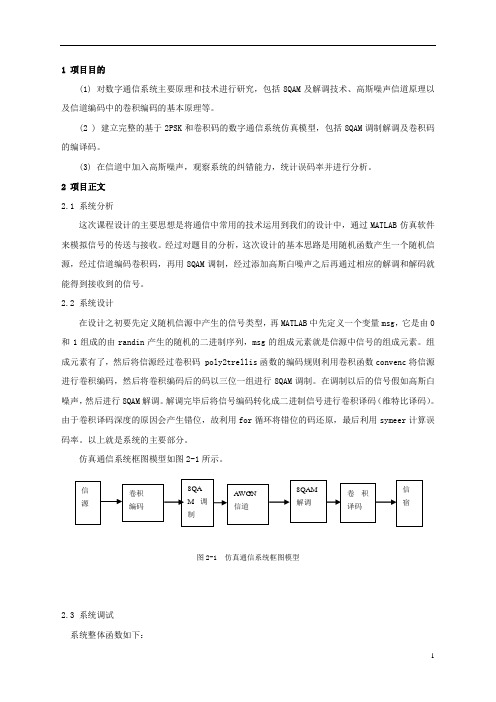

1 项目目的(1) 对数字通信系统主要原理和技术进行研究,包括8QAM 及解调技术、高斯噪声信道原理以及信道编码中的卷积编码的基本原理等。

(2 ) 建立完整的基于2PSK 和卷积码的数字通信系统仿真模型,包括8QAM 调制解调及卷积码的编译码。

(3) 在信道中加入高斯噪声,观察系统的纠错能力,统计误码率并进行分析。

2 项目正文2.1 系统分析这次课程设计的主要思想是将通信中常用的技术运用到我们的设计中,通过MATLAB 仿真软件来模拟信号的传送与接收。

经过对题目的分析,这次设计的基本思路是用随机函数产生一个随机信源,经过信道编码卷积码,再用8QAM 调制,经过添加高斯白噪声之后再通过相应的解调和解码就能得到接收到的信号。

2.2 系统设计在设计之初要先定义随机信源中产生的信号类型,再MATLAB 中先定义一个变量msg ,它是由0和1组成的由randin 产生的随机的二进制序列,msg 的组成元素就是信源中信号的组成元素。

组成元素有了,然后将信源经过卷积码 poly2trellis 函数的编码规则利用卷积函数convenc 将信源进行卷积编码,然后将卷积编码后的码以三位一组进行8QAM 调制。

在调制以后的信号假如高斯白噪声,然后进行8QAM 解调。

解调完毕后将信号编码转化成二进制信号进行卷积译码(维特比译码)。

由于卷积译码深度的原因会产生错位,故利用for 循环将错位的码还原,最后利用symeer 计算误码率。

以上就是系统的主要部分。

仿真通信系统框图模型如图2-1所示。

图2-1 仿真通信系统框图模型2.3 系统调试系统整体函数如下:信源 卷积 编码 8QAM 调制 AWGN 信道 8QAM 解调 卷积译码 信宿len = 1000;msg = randint(2*len,1); % Random binary message of 2-bit symbols trel = poly2trellis([5 4],[23 35 0;0 5 13]); % Trelliscode = convenc(msg,trel); % Encode the message.M = 8; % Alphabet sizek = log2(M);xsym = bi2de(reshape(code,k,length(code)/k).','left-msb'); %在这里left-msb的意思是二进制数据中,以左边第一位为最高位来将2进制数翻译成10进制数y = qammod(xsym,M); % Use 8-QAM modulation.ynoisy = awgn(y,17,'measured'); % Transmit signal through an AWGN channel.scatterplot(ynoisy); % Create scatter plot from noisy data.z = qamdemod(ynoisy,M); % Demodulate to recover the message.z1 = de2bi(z,'left-msb'); %将解调出来的信号进行10进制到2进制的转换z2 = reshape(z1.',prod(size(z1)),1); %再将得到的3列乘以1000行的数组转换成1列3000行的数组,decoded = vitdec(cc,trel,2,'cont','hard'); % Decode.for i=1:1996decoded(i)=decoded(i+4);end;[num,rt]= symerr(decoded,msg) % Check symbol error rate.该程序实现了从产生随机二进制信源到采用卷积码编码、8QAM调制到8QAM解调、卷积解码这一系列过程。

卷积码差错控制系统仿真

《移动通信》课程设计报告课程设计题目:卷积码差错控制系统仿真系:学生姓名:班级:学号:成绩:指导教师:开课时间:2012-2013 学年 2 学期目录第一章引言 (1)1.1 题目 (1)1.2 课程设计的目的 (1)1.3 课程设计的主要内容和要求 (1)第二章课程设计原理 (2)2.1 卷积码的定义 (2)2.2 卷积码的编码原理 (2)2.3 卷积码的译码过程 (2)2.4 维特比译码 (2)2.4.1维特比译码原理 (2)2.4.2维特比译码过程 (3)第三章仿真过程 (5)3.1 仿真模拟框图 (5)3.2 各部件的配置 (6)第四章系统运行代码 (11)4.1 系统运行源代码 (11)结论 (12)心得体会 (13)参考文献 (14)第一章引言1.1 题目卷积码差错控制系统的仿真1.2 课程设计的目的移动通信也是一门实践性非常强的课程,实验教学在整个课程的教学中占据了非常重要的地位。

在学生学习了现代通信原理、数字信号处理(DSP技术)等课程后,学生已经具有了一定的理论基础和实验技能,在此基础上本实验课程开设的主要作用和目的在于:1.帮助学生更好地理解移动通信系统,掌握各种移动通信系统的模型2.帮助学生熟悉常用的通信系统仿真平台,学习仿真模型的设计,掌握通信系统的仿真方法,学会利用仿真软件对系统性能进行评价;1.3 课程设计的主要内容和要求(1)课程设计的主要内容:1.系统包括信源部分、信道部分和信宿部分。

2.信源部分的数据源是随机的二进制序列,随机的二进制序列要经过卷积编码,经过编码的数据要进行调制。

(子系统实现)3.信道部分对调制后的信号进行加噪。

4.信宿部分完成信号的解调和译码(维特比译码)。

(子系统实现)5.对不同编码方式、不同信噪比下维特比译码的误比特率并画出图形。

(2)课程设计的要求:1.要有详细的设计过程。

即整个系统的仿真设计的选择,功能模块的设计过程和参数的选择,程序的调试过程等。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

湖南科技大学信息与电气工程学院课程设计报告课程:通信原理题目:卷积码的仿真专业:电子信息工程班级:电子二班姓名:高二奎学号: 1104030205任务书目录一、任务与要求 (4)1.1设计的目的 (4)1.2 设计的基本内容 (4)二、卷积码的介绍 (4)2.1 卷积码的介绍 (4)2.2 编码原理 (4)2.3 译码原理 (7)三、SystemView软件简介 (8)3.1 SystemView基本特点 (8)3.2 各单元模块功能介绍及电路设计 (8)3.3 各模块的原理及介绍 (10)3.4 图符库选择按钮 (10)3.5 system view 的操作步骤 (11)3.6 分析窗的接收计算器 (12)四、系统仿真和调试 (12)4.1 系统仿真 (12)4.2 调试结果 (13)五、总结 (15)5.1 设计小结 (15)5.2 心得体会 (15)参考文献 (16)一、任务与要求1.1设计的目的这次的课程设计就是基于SystemView软件的卷积码仿真设计,要学会运用SystemView,理解卷积码系统的原理,并用SystemView进行仿真设计。

1.2 设计的基本内容SystemView是一种动态系统分析软件,也是一个非常好的仿真工具。

它能按照物理概念直接建立分析和仿真,对通信技术的发展起到很大的作用。

本次课程设计就是利用软件SystemView对卷积码进行可视化仿真,对信息数据的编码,传输及译码等功能的实现,充分展示了SystemView在通信仿真中灵活的应用实例。

二、卷积码的简介2.1 卷积码介绍非分组码的卷积码的编码器是在任一段规定时间内产生n个码元,但它不仅取决于这段时间中的k个信息位,还取决于前(K-1)段规定时间内的信息位,这K段时间内的码元数目为K·k,称参数K为卷积码的约束长度,每k 个比特输入,得到n比特输出,编码效率为k/n,约束长度为K。

在k=1的条件下,移位寄存器级数m=K-1。

卷积码一般可用(n,k,K)来表示,其中k为输入码元数,n为输出码元数,而K则为编码器的约束长度。

典型的卷积码一般选n和k ( k< n ) 值较小,但约束长度K可取较大值(K<10),以获得既简单又高性能的信道编码[6]。

卷积码是1955年Elias最早提出,1957年Wozencraft提出了序列译码。

1963年Massey提出了一种性能稍差,但比较实用的门限译码方法。

1967年维特比(Viterbi)提出了最大似然译码。

它对存储器级数较小的卷积码的译码很容易实现,称为维特比算法或维特比译码。

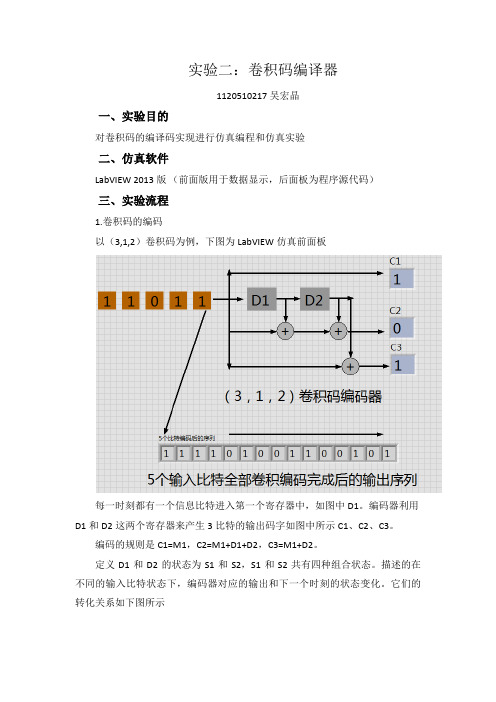

图1、二进制卷积码的编码器图2给出了(3,1,2)二进制卷积码编码器。

在每一时间单位,输入一个比特信息i m ,同时存贮器内的数据向右移一位,产生3个比特的输出i c ,其中一个是输入比特i m ,两个是校验比特,1i p ,,2i p 。

图2由图可知:,12,212i i i i i i i p m m p m m m ---=⊕=⊕⊕因为校验比特是输入信息元i m 的模2和,它们是线性关系,所以这类卷积码是线性码。

称i c 为卷积码的一个子码或码段,它不仅与当前输入信息有关,还与前2个(m )时间单位的输入信息有关,即和前2个子码有关;而且i m 要经过2个时间单位才能移出存贮器,所以i c 也参与了后2个子码中的校验运算,称1N m =+为编码约束度,说明编码过程中互相约束的码段个数。

本例的编码约束度为3。

m 或N 是表示卷积码编码器复杂性的一个重要参数。

m 或N 越大,编码器和译码器越复杂,但卷积码的纠错能力也越强。

因此这是一对矛盾,在具体设计时要根据应用要求进行折衷处理,选择适当的码型。

卷积码的描述方式为解析法和图解法两类。

解析法包括矩阵形式和生成多项式形式,图解法包括树图、状态图和网格图。

图3 卷积码的树图表示图4卷积码的网格图图5卷积码的状态图2.3 译码原理采用概率译码的基本思想是:把已接收序列与所有可能的发送序列做比较,选择其中码距最小的一个序列作为发送序列。

如果发送L组信息比特,那么对于(n,k)卷积码来说,可能发送的序列有2kL个,计算机或译码器需存储这些序列并进行比较,以找到码距最小的那个序列。

当传信率和信息组数L较大时,使得译码器难以实现。

维特比算法则对上述概率译码做了简化,以至成为了一种实用化的概率算法。

它并不是在网格图上一次比较所有可能的2kL 条路径(序列),而是接收一段,计算和比较一段,选择一段最大似然可能的码段,从而达到整个码序列是一个最大似然值得序列。

下面以图6的(2,1,3)卷积码编码器所编出的码为例,来说明维特比解码的方法和运作过程。

为了能说明解码过程,这里给出该码的状态图,如图7所示。

根据卷积码画网格的方法,我们可以画出该码的网格图,如图8所示。

该图设输入信息数目L=5,所以画L+N=8个时间单位,图中分别标以0至7。

这里设编码器从a 状态开始运作。

该网格图的每一条路径都对应着不同的输入信息序列。

由于所有可能输入信息序列共有2kL 个,因而网格图中所有可能的路径也为2kL 条。

这里节点a=00,b=01,c=10,d=11。

设输入编码器的信息序列为(11011000),则由编码器对应输出的序列为Y=(1101010001011100),编码器的状态转移路线为abdcbdca 。

若收到的序列R=(0101011001011100),对照网格图来说明维特比译码的方法。

a bc d节点号1234567图8 (2,1,3)卷积码网格图由于该卷积码的约束长度为6位,因此先选择接收序列的前6位序列R1=(010101)同到达第3时刻的可能的8个码序列(即8条路径)进行比较,并计算出码距。

该例中到达第3时刻a 点的路径序列是(000000)和(111011),他们与R1的距离分别为3和4;到达第3时刻b 点的路径序列是(000011)和(111000),他们与R1的距离分别为3和4;到达第3时刻c 点的路径序列是(001110)和(110101),他们与R1的距离分别为4和1;到达第3时刻d 点的路径序列是(001101)和(110110),他们与R1的距离分别为2和3。

上述每个节点都保留码距较小的路径作为幸存路径,所以幸存路径码序列是(000000)、(000011)、(1101001)和(001101),如图9所示。

用于上面类似的方法可以得到第4、5、6、7时刻的幸存路径。

三、SystemView 软件简介3.1 SystemView 基本特点System View 是美国ELANIX 公司推出的,基于Windows 环境下运行的用于系统仿真分析的可视化软件工具,它使用功能模块(Token)描述程序。

利用System View ,可以构造各种复杂的模拟、数字、数模混合系统和各种多速率系统,因此,它可用于各种线性或非线性控制系统的设计和仿真。

用户在进行系统设计时,只需从System View 配置的图标库中调出有关图标并进行参数设置,完成图标间的连线,然后运行仿真操作,最终以时域波形、眼图、功率谱等形式给出系统的仿真分析结果。

3.2 各单元模块功能介绍及电路设计1)系统设计窗口启动SystemView 后就会出现如图所示的系统设计窗口,它包括标题栏、菜单栏、工具条、滚动条、提示栏、图符库和设计窗工作区。

a b c d节点号 0123图9 维特比译码第3时刻幸存路径图3.1系统设计窗口系统视窗最上边一行为主菜单栏,包括:文件(File)、编辑(Edit)、参数优选(Preferences)、视窗观察(View)、便笺(NotePads)、连接(Connetions)、编译器(Compiler)、系统(System)、图符块(Tokens)、工具(Tools)和帮助(Help)共11项功能菜单。

与最初的SystemView1.8相比,SystemView3.0的操作界面和对话框布局有所改变。

2)定时窗口:图3.2 SystemView系统定时窗口设定系统定时窗口:此窗口定义系统仿真的起始和终止时间(Start Time and Stop Time)、采样率(Sample Rate)、采样间隔(Time Spacing)、采样点表(No.ofSamples)、频率分辨率(Freq.Res.)和系统的循环次数(No.of System Loops)。

系统仿真之前首先必须定义这些参数,系统定时直接控制系统的仿真。

同时系统定时的设定直接影响系统仿真的精度,所以选取参数必须十分注意,这也是我们应重点注意的内容,采样频率过高会增加仿真的时间,过低则有肯能得不到正确的仿真效果。

3.3 各模块的原理及介绍1)SystemView工具条图标介绍图3.3SystemView工具条以上工具条包括许多常用功能的图标快捷键,分别为:清除工作区、删除按钮、断开图符、间连接连接按钮、复制按钮、图符翻转、创建便笺、创建子系统、显示子系统、根轨迹、波特图、画面重画、停止仿真、开始仿真、系统定时、分析窗口。

3.4 图符库选择按钮在设计窗口中间的大片区域就是设计区域,也就是供用户搭建各种系统的地方。

在设计窗口的最上端一行是下拉式命令菜单行,通过调用这些菜单可以执行System View的各项功能;设计窗口中菜单行的下面,紧邻在设计区域上端一行是工具栏,它包含了在系统设计、仿真中可能用到的各种操作按钮;在工具栏的最右端是提示信息,当鼠标置于某一工具按钮上时,在该处会显示对该按钮的说明和提示信息;紧邻在设计区域左端是各种器件图标库,下面介绍些常用的几个库图标,如表3-1所示。

表3-1 常用图标3.5 system view 的操作步骤(一) 选择设置信号源(Source)选中该图标并按住鼠标左键将其拖至设计区内,这时所选中的图标会出现在设计区域中。

双击设计窗口中的图标后,弹出的对话框,通过Periodic Noise/PN Aperiodic和Import按钮进行分类选择和调用。

选中后单击对话框中的参数按钮Parameters,在出现的参数设置对话框中设置幅度、频率、相位。

完成后分别单击参数设置和源库对话框的按钮OK,从而完成该图标的设置。

(二)选择设置分析窗(Sink)当需要对系统中各测试点或某一图标输出进行观察时,则应放置一个分析窗(Sink)图标,一般将其设置为“Analysis”属性。

Analysis图标相当于示波器或频谱仪等仪器的作用,它是最常使用的分析型图标之一。

具体操作和信号源设置类似。

(三)系统定时(System Time)System View系统是一个离散时间系统。

在每次系统运行之前,首先需要设定一个系统频率。