AD差分输入信号

一种差分ad采样输入方案

一种差分ad采样输入方案

差分AD(模数转换器)采样输入方案是一种常见的信号采集技术,通常用于测量传感器输出或其他模拟信号。

这种方案通过测量

信号与一个已知参考信号之间的差异来实现。

下面我将从不同角度

来解释一种差分AD采样输入方案。

1. 差分输入原理,差分AD采样方案基于差分输入原理,即通

过比较两个信号的差异来获得输入信号的信息。

在这种方案中,一

个信号作为正输入,另一个信号作为负输入,通过测量它们之间的

差异来获得输入信号的数值。

2. 优点,差分AD采样方案相对于单端输入有一些优点。

首先,它可以消除共模噪声,因为共模噪声会同时影响正负输入,但通过

差分测量可以将其消除。

其次,差分输入可以提供更好的动态范围

和抗干扰能力,特别是在工业环境中,信号可能受到干扰的情况下。

3. 实现方式,实现差分AD采样方案通常需要使用差分输入的

模数转换器(ADC),这种ADC具有两个输入端,分别连接到正负输

入信号。

此外,还需要一个参考信号源,用于与输入信号进行比较。

4. 应用领域,差分AD采样方案在许多领域都有应用,特别是在需要高精度和抗干扰能力的测量和控制系统中,如工业自动化、医疗设备、通信系统等。

5. 总结,差分AD采样方案通过比较正负输入信号的差异来实现信号采集,具有消除共模噪声、提高动态范围和抗干扰能力等优点,适用于许多高要求的应用领域。

希望以上信息能够全面地回答你关于差分AD采样输入方案的问题。

如果你还有任何疑问或需要进一步了解,请随时告诉我。

AD选型指南

A/D、D/A转换器在模拟集成电路世界占有非常重要的地位,在系统中实现数据的采集与处理,完成模拟与数字相互转换。

将模拟信号转换成能进行数字处理的二进制代码的模拟集成电路称为A/D转换器,即Analog to digital converter(简称ADC),A/D转换器的输入信号为模拟信号,输出信号为数字信号,输入类型有单端输入和差分输入,输出类型有并行输出和串行输出,输出数字信号电平模式有CMOS、TTL、ECL和L VDS。

将二进制代码转换成模拟信号的集成电路称为D/A转换器,即Digital to analog converter(简称DAC),输入信号为数字信号,输出为模拟信号,输入类型有并行输入、串行输入和分段输入,输出类型有电流输出和电压输出。

选择合适的A/D、D/A转换器及应用好所选择的产品,关系到系统整体性能,下面将从系统选择和使用A/D、D/A转换器以及A/D、D/A转换器的特性等几方面进行阐述。

一、系统中A/D、D/A转换器的选择考虑的因素根据不同的系统要求,选择具体A/D、D/A转换器的产品可因人而异,但是,大体可遵循以下原则:①终端系统的要求根据对终端系统的要求分析,确定整体系统分解到A/D、D/A模块的主要指标,提出需要的产品精度(即位数或分辨率)和速度(即A/D:转换率/转换时间,D/A:转化速率/建立时间)。

②成本考虑成本与产品性能的取舍方案,确定可接受的成本范围。

③分辨率或精度根据分辨率或精度划分A/D、D/A转换器一般有:4位、6位、8位、10位、12位、14位、16位、18位、20位、22位、24位等。

④速度对于选择低速A/D转换器,则确定系统容许的转换时间,对于选择高速A/D转换器,则确定系统容许的采样频率和模拟输入信号频率。

对于选择低速D / A转换器,则确定系统容许的建立时间,对于选择高速D/A转换器,则确定系统容许的工作频率和模拟输出信号频率。

⑤性能在确定以上因素后进行产品的具体选择时,应主要考虑如下表所示的电性能参数,根据具体系统确定满足要求的产品。

单片机ad输入阻抗

单片机ad输入阻抗1.引言1.1 概述概述部分的内容是对整篇文章的主题进行简要介绍,包括单片机AD 输入阻抗的基本概念和其在电子领域中的重要性。

以下是概述部分的内容:在现代电子技术发展中,单片机(Microcontroller)作为一种重要的计算和控制设备,广泛应用于各个领域。

而单片机的模拟输入功能则是实现其应用的重要基础。

而单片机AD输入阻抗则是模拟输入功能中的重要参数。

本文主要围绕单片机AD输入阻抗展开讨论,旨在深入了解单片机AD 输入阻抗的概念、影响因素以及提高AD输入阻抗的方法等内容。

首先,我们将阐述单片机AD输入阻抗的基本概念,包括其定义和特性;其次,我们将分析单片机AD输入阻抗的影响因素,包括外界信号源阻抗、单片机内部电路和引脚设计等方面;最后,我们将探讨单片机AD输入阻抗的重要性以及提高AD输入阻抗的方法,为读者提供实际应用中的参考和指导。

通过本文的阐述,读者将对单片机AD输入阻抗有更为深入的了解,掌握其在电子设计中的关键作用,并能够在实际应用中采取合适的措施来提高AD输入阻抗。

希望本文能为读者在单片机设计和应用中提供有益的参考和指导。

1.2文章结构1.2 文章结构本文将首先概述单片机AD(模拟输入数字输出)输入阻抗的概念和重要性。

接着,将详细介绍影响单片机AD输入阻抗的因素,包括外部电路和单片机内部结构等。

在正文的第二部分,将分别探讨单片机AD输入阻抗的概念和影响因素,并阐述它们对单片机性能的影响和意义。

在结论部分,将总结单片机AD输入阻抗的重要性,并提出提高单片机AD输入阻抗的方法。

这些方法将包括在硬件设计中采用合适的电路匹配和减小电源干扰,以及在软件设计中采取有效的信号处理和滤波技术等。

通过对单片机AD输入阻抗的研究,我们可以更好地理解其对单片机性能的影响,并在实际应用中采取相应的措施来提高系统的稳定性和精确性。

本文旨在为读者提供有关单片机AD输入阻抗的全面了解,并为工程师和研究者提供一些优化AD输入阻抗的实用方法和技巧。

AD介绍

积分非线性误差(DNL) :指的是实际步宽和 1LSB 理想值之间的差值。如果 DNL 超过 了 1LSB, 转换器可能是非单调的。 这就意味着当输入幅度增加的情况下, 输出幅度反而变小。 也有可能丢失编码, 2n 个二进制编码中的一个或多个将永远不会输出。 微分非线性误差(INL) :实际转换函数和理想直线的偏差。理想直线普遍采用的定义是 增益和偏置误差被消除的前提下,连接函数端点之间的一条直线。偏离量是按照转换函数从 一个步长到下一个步长来度量。 动态误差:表征 ADC 参数表征 ADC 电路在动态环境下的性能,也就是说输入信号是时间的 函数。动态特性比表征 ADC 静态特性复杂得多,其动态特性参数主要包括信噪比(SNR) 、 信噪谐波比(SINAD) 、有效位数(ENOB) 、总谐波失真(THD) 、无杂散动态范围(SFDR) 、 满功率带宽(FPBW) 、孔径误差等。 在实际中,由于静态误差和动态误差的存在,即使 N 位的 ADC 的外围电路引入的误差可 以忽略不计,其有效位数 ENOB 往往是小于 N ,且从芯片制作工艺的角度而言,同样为 N 位 的 ADC,采样率不同,芯片类型(内部实现结构)不同,误差的影响也不同。在表 2 中比较 了 ADI 公司的几款 16 位 ADC 的性能。

ADC 的误差:

静态误差:在转换直流信号时影响转换器精度的误差,可以由偏置误差、增益误差、积分非 线性误差、微分非线性误差描述。 偏置误差:标准偏置点与实际偏置点之间的差值。当数字输出是零时,偏置点是步长的 中间值。这种误差是以同样的值影响所有的编码并通过修正处理过程来补偿,若不能修正, 这种误差是指零尺度误差。 增益误差:在偏置误差被修正为零后,转换函数标准增益点和实际增益点之间的误差。 当数字输出是全标度时增益点是步长中间值。这种误差表示实际转换函数和理想转换函数斜 率的差值以及每一步长中相应的同一百分比误差,可以通过修正的方法调整到零。

AD中关于差分线的设置和走线的方法

AD中关于差分线的设置和走线的方法差分线是一种用于传输高速信号的电路设计技术。

在高速信号传输中,信号会受到电磁干扰和信号损耗的影响,差分线技术能够有效地减小这些干扰和损耗,并提高信号传输的可靠性。

下面,我将详细介绍AD中关于差分线的设置和走线的方法。

一、差分线的设置:1.差分线的长度匹配:差分信号的传输速率越高,其对线路长度匹配的要求就越高。

在AD 中,可以通过Signal Integrity模块来进行差分线的长度匹配。

首先,在PCB设计阶段,可以根据差分线的长度和传输速率进行合理的走线规划,以确保差分信号在传输过程中能够同步到达。

其次,可以通过Signal Integrity模块中的差分线长度匹配功能,自动调整差分线的长度,以满足设计的要求。

2.差分阻抗的控制:差分线的阻抗匹配对于有效地传输差分信号至关重要。

在AD中,可以通过布局阶段中的差分线约束规则来设置差分线的阻抗。

首先,在布局阶段,可以通过选择合适的宽度和间距来控制差分线的阻抗值。

然后,在走线阶段,可以使用差分线走线规则来确保差分线的宽度和间距满足设计要求。

二、差分线的走线方法:1.差分线的走向选择:在AD中,可以通过走线规则和信号完整性分析来选择差分线的走向。

首先,在布局阶段,可以根据芯片引脚的布置情况和信号传输路径来确定差分线的走线方向。

其次,在走线阶段,可以使用规则驱动的走线方法,根据差分线的长度和布局情况来选择最佳的走线路径。

2.保持差分线的对称性:在设计中,差分线的对称性对于减小信号的不对称失配和减小共模噪声的影响非常重要。

因此,在走线过程中,应尽量保持差分线的对称性,包括差分线的宽度、间距和走线路径的相对位置等方面。

可以通过AD中的规则驱动走线功能和信号完整性分析,自动调整差分线的走线路径,以达到最佳的对称性。

3.避免与其他信号线的干扰:差分线的走线过程中,还应避免与其他信号线的干扰。

干扰可能包括电磁辐射、互电感和互电容等因素。

stm32f103 ad 差分 原理

stm32f103 ad 差分原理STM32F103是一款常用的ARM Cortex-M3内核的微控制器,它具有强大的性能和丰富的外设接口。

其中,AD差分原理是其重要的功能之一。

AD差分原理是指在模拟信号采集过程中,使用差分输入方式来提高信号的抗干扰能力和采样精度。

传统的单端输入方式只使用一个信号引脚作为输入,而差分输入方式则使用两个信号引脚,分别为正极和负极。

正极引脚接收信号,负极引脚接收对地的参考电压,通过比较两个引脚的电压差异来采集信号。

在STM32F103中,AD差分输入功能可以通过配置相关的寄存器和引脚来实现。

首先,需要将对应的引脚设置为ADC差分输入模式,然后通过设置相关的控制寄存器,使ADC模块能够识别差分输入模式。

接下来,可以通过设置采样时间、转换速率等参数来调整AD 转换的精度和速度。

使用AD差分原理进行信号采集时,可以有效地抑制共模干扰信号。

共模干扰是指信号源和地之间的电位差引入到输入信号中,对信号采集造成干扰。

而差分输入方式通过同时采集信号和参考电压,能够消除这种干扰,提高采样精度。

AD差分原理还可以增加信号的输入范围。

传统的单端输入方式只能采集正半周期的信号,而差分输入方式可以采集正负半周期的信号,扩大了采样范围。

这对于需要采集双极性信号或存在偏置的信号非常有用。

在实际应用中,AD差分输入方式广泛应用于需要抗干扰能力强、采样精度高的场景,如工业自动化、医疗设备、通信设备等领域。

例如,在工业控制系统中,需要采集各种传感器信号,而这些信号往往受到电磁干扰的影响,使用AD差分输入方式可以有效地提高信号的可靠性和准确性。

总结一下,STM32F103的AD差分原理是通过使用差分输入方式来提高信号的抗干扰能力和采样精度。

它能够抑制共模干扰、扩大采样范围,广泛应用于各种工业和通信设备中。

在实际应用中,我们可以通过配置相关的寄存器和引脚,灵活地使用AD差分功能,提高系统的性能和稳定性。

AD PCB中差分走线的设置

Altium Designer PCB中差分线的设置与布线

原创:Jimmy

转载请注明出处

引言:

精通一门CAD设计软件是衡量一个优秀PCB工程师的标准之一。

编写本教程的目的在于帮助刚接触Altium Designer的工程师更加了解此软件的使用。

操作步骤:

1,已经成功导入网表后的PCB文件,在Altium Designer界面的右下角【PCB】图标选择“PCB”

2,此时出现【DifferentialPairs Editor】对话框,单击【Add】命令,添加差分信号232RX1和232TX1

并将此差分对组命名为:232_DifferentialPair1

3,单击【Rule Wizard】命令,进入差分对各种参数设置,如线宽和间距。

4,设置好的界面如下图:

5,差分对走线。

执行【Place】/【Differential Pair Routing】,进行差分对布线。

单击差分对网络的两个相邻焊盘,然后移动鼠标,就会看到对应的另一走线也会跟随着一起平行走线。

如需要换层,可同时按下键盘的CTRL+SHIRT并且转动鼠标滚轮。

效果如下图:

欢迎交流!

专业PCB Layout,SI仿真技术论坛。

ad差分线规则

ad差分线规则AD差分线规则是一种常见的电路设计规则,主要用于在PCB板上布线时,保证信号传输的稳定性和可靠性。

下面是AD差分线规则的详细介绍:1. 差分线的定义差分线是指一对相互平衡的导线,它们在电压上具有相反的极性,并且它们之间的电压差值是一个确定的值。

2. 差分信号传输原理差分信号传输可以有效地减少共模噪声和电磁干扰。

当信号从发送器传输到接收器时,两根导线之间会产生一个相反极性的电场,这个电场可以抵消外部干扰信号对两根导线产生的影响,从而实现了可靠的信号传输。

3. AD差分线规则为了保证差分信号传输的稳定性和可靠性,在PCB板上进行布线时需要遵循以下AD差分线规则:(1) 差分对应该尽可能地靠近,并且在布局时应该保持平衡。

(2) 差分对应该采用同样长度、同样宽度、同样层次、同样距离等参数进行设计。

(3) 差分对应该采用同样的线宽、线距和阻抗控制参数。

(4) 差分对应该采用相同的引脚布局方式,以保证两根导线之间的长度和位置一致。

(5) 差分对应该采用相同的终端电阻,以保证信号传输的匹配性。

4. 差分线布局技巧在进行差分线布局时,需要注意以下技巧:(1) 在布局时应该尽可能地减少导线长度,以减小信号传输延迟和损耗。

(2) 在布局时应该尽可能地避免与其他信号线交叉或平行走向,以减少干扰和串扰。

(3) 在布局时应该尽可能地保持导线之间的距离一致,以保证阻抗匹配性。

(4) 在布局时应该尽可能地避免锐角转弯或直角转弯,以减小信号反射和损耗。

总之,AD差分线规则是保证差分信号传输稳定性和可靠性的重要设计规则。

在进行PCB板设计时,需要严格遵守这些规则,并结合实际情况灵活运用各种技巧来实现最佳的设计效果。

AD8138 单端变差分

电路笔记CN-0040连接/参考器件利用ADI公司产品进行电路设计差分输入、双通道、3 MSPS 12位SARADCAD7352放心运用这些配套产品迅速完成设计。

Rev.A“Circuits from the Lab” from Analog Devices have been designed and built by Analog Devicesengineers. Standard engineering practices have been employed in the design and constructionof each circuit, and their function and performance have been tested and verified in a labenvironment at room temperature. However, you are solely responsible for testing the circuitand determining its suitability and applicability for your use and application. Accordingly, inno event shall Analog Devices be liable for direct, indirect, special, incidental, consequential orpunitive damages due to any cause whatsoever connected to the use of any “Circuit from theLab”. (Continued on last page)One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.Tel: Fax: 781.461.3113©2009 Analog Devices, Inc. All rights reserved.AD8138低失真差分ADC驱动器欲获得更多信息和/或技术支持,请拨打4006-100-006或访问/zh/circuits。

全差分伪差分单端输入ADC理解

伪差分:伪差分信号连接方式减小了噪声,并允许在仪器放大器的共模电压范围内与浮动信号连接.在伪差分模式下,信号与输入的正端连接,信号的参考地与输入的负端连接。

伪差分输入减小了信号源与设备的参考地电位(地环流)不同所造成的影响,这提高了测量的精度。

伪差分输入与差分输入在减小地环流和噪声方面是非常相似的,不同的方面在于,差分输入模式下,负端输入是随时间变化的,而在伪差分模式下,负端输入一定仅仅是一个参考。

描述伪差分的另外一种方式就是,输入仅仅在打破地的环流这个意义上是差分的,而参考信号(负端输入)不是作为传递信号的,而仅仅是为信号(正端输入)提供一个直流参考点。

全差分与单端输入:在单端方式工作时;ADC转换的是单输入引脚对地的电压值;在增益为1时,测量的值就是输入的电压值;范围是0V到VREF;当增益增加时,输入的范围要相应的减小;在差分方式工作时;ADC转换的是AIN+与AIN-两个引脚的差值;在增益为1时,测量的值等于(AIN+)-(AIN-),范围是-VREF到+VREF;当增益增加时,输入的范围要相应的减小。

注意:在差分方式时所提的负压是指AIN-引脚的电压大于AIN+引脚的电压,实际输入到两个引脚的电压对地都必需是正的;例如:如果AIN+引脚输入的电压为0V,AIN-引脚的输入电压为1/2VREF时,差分的输入电压为(0V-1/2VREF) = -1/2VREF。

ADI公司目前针对10KHz左右采样速率的24位ADC推荐AD719X系列的产品。

AD779X属于老产品,老产品噪声较大。

对于单端输入,能测量双极性信号的ADC,内部原理为基准源分压方式,对于TI的MSP430F1161,基准源可提供正负方式。

对于ADuC845的AD输入配置,可以配置为4个全差分输入,或者8个伪差分输入,对于伪差分输入,AINCOM端为参考端。

GAIN越大,ADC的有效分辨率越小,采样速率越高,有效分辨率也越小。

上图参数可得出,全差分的每个输入端口电压不能低于0V,也不能高于规定的电压值。

理解什么是单端&差分&伪差分

Google+百度の英文关键词Single-Ended Input(单端)差分(Fully-Differential Input)伪差分(Pseudo-Differential Input) 单端输入&差分输入输入信号均以共同的地线为基准.这种输入方法主要应用于输入信号电压较高(高于1V),信号源到模拟输入硬件的导线较短(低于15ft),且所有的输入信号共用一个基准地线.如果信号达不到这些标准,此时应该用差分输入.对于差分输入,每一个输入信号都有自有的基准地线;由于共模噪声可以被导线所消除,从而减小了噪声误差.单端输入时,是判断信号与GND的电压差.差分输入时,是判断两个信号线的电压差.信号受干扰时,差分的两线会同时受影响,但电压差变化不大.(抗干扰性较佳)而单端输入的一线变化时,GND不变,所以电压差变化较大.(抗干扰性较差)差分信号和普通的单端信号走线相比,最明显的优势体现在以下三个方面:a.抗干扰能力强,因为两根差分走线之间的耦合很好(最好相邻布线),当外界存在噪声干扰时,几乎是同时被耦合到两条线上,而接收端关心的只是两信号的差值,所以外界的共模噪声可以被完全抵消。

b.能有效抑制EMI,同样的道理,由于两根信号的极性相反,他们对外辐射的电磁场可以相互抵消,耦合的越紧密,泄放到外界的电磁能量越少。

c.时序定位精确,由于差分信号的开关变化是位于两个信号的交点,而不像普通单端信号依靠高低两个阈值电压判断,因而受工艺,温度的影响小,能降低时序上的误差,同时也更适合于低幅度信号的电路。

目前流行的LVDS(low voltage differential signaling)就是指这种小振幅差分信号技术。

当AD的输入信号只有一路时,为了更好地抑制共模噪声,我们可以采用差分输入方式。

这就需要我们首先要将单端变成差分,可以用运放AD8138实现。

RS232C是单端输入,这样在输入中有干扰信号加到输入中就会影响输出,造成输出信号错误;RS485是差动输入,即两个输入端的电势差作为输入,有干扰信号的话也会在作差的时候减掉了,这样可以大大提高信号的抗干扰能力!!伪差分输入(NI关于什么是伪差分输入的解释)伪差分信号连接方式减小了噪声,并允许在仪器放大器的共模电压范围内与浮动信号连接.在伪差分模式下,信号与输入的正端连接,信号的参考地与输入的负端连接。

AD7356_中文资料

VDD VDRIVE

AD7356

VINA+ VINA– REFA T/H 12-BIT SUCCESSIVE APPROXIMATION ADC

SDATAA

Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties that may result from its use. Speci cations subject to change without notice. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices. Trademarks and registered trademarks are the property of their respective owners.

产品聚焦

1. 两个完整的 ADC,允许两个通道同步采样和转换。两 个通道的转换结果可通过独立的数据线路同时获得, 或如果仅有一个串行端口可用,则通过一条数据线路 先后获得。 2. 高吞吐速率、低功耗。AD7356提供5 MSPS吞吐速率, 功耗为36 mW。 3. 无转换延迟。AD7356采用两个标准逐次逼近型ADC, 通过CS输入和转换控制能够精确控制采样时刻。

AD的差分输入与单端输入

AD的差分输入与单端输入

单端输入,输入信号均以共同的地线为基准.这种输入方法主要应用于输入信号电压较高(高于1 V),信号源到模拟输入硬件的导线较短(低于15 ft),且所有的输入信号共用一个基准地线.如果信号达不到这些标准,此时应该用差分输入.对于差分输入,每一个输入信号都有自有的基准地线;由于共模噪声可以被导线所消除,从而减小了噪声误差.

单端输入时, 是判断信号与GND 的电压差. 差分输入时, 是判断两个信号线的电压差.

信号受干扰时, 差分的两线会同时受影响, 但电压差变化不大. (抗干扰性较佳) 而单端输入的一线变化时, GND 不变, 所以电压差变化较大. (抗干扰性较差) 差分信号和普通的单端信号走线相比,最明显的优势体现在以下三个方面:

a.抗干扰能力强,因为两根差分走线之间的耦合很好,当外界存在噪声干扰时,几乎是同时被耦合到两条线上,而接收端关心的只是两信号的差值,所以外界的共模噪声可以被完全抵消。

b.能有效抑制EMI,同样的道理,由于两根信号的极性相反,他们对外辐射的电磁场可以相互抵消,耦合的越紧密,泄放到外界的电磁能量越少。

c.时序定位精确,由于差分信号的开关变化是位于两个信号的交点,而不像普通单端信号依靠高低两个阈值电压判断,因而受工艺,温度的影响小,能降低时序上的误差,同时也更适合于低幅度信号的电路。

目前流行的LVDS(low voltage differential signaling)就是指这种小振幅差分信号技术。

当AD的输入信号只有一路时,为了更好地抑制共模噪声,我们可以采用差分输入方式。

这就需要我们首

先要将单端变成差分,可以用运放AD8138实现。

AD的差分输入与单端输入

AD的差分输入与单端输入(2010-11-09 11:52:46)转载▼标签:转载分类:电子技术单端输入,输入信号均以共同的地线为基准。

这种输入方法主要应用于输入信号电压较高(高于1V),信号源到模拟输入硬件的导线较短(低于15 ft,1ft=304.8mm),且所有的输入信号共用一个基准地线。

如果信号达不到这些标准,此时应该用差分输入。

对于差分输入,每一个输入信号都有自有的基准地线;由于共模噪声可以被导线所消除,从而减小了噪声误差。

单端输入时,是判断信号与GND 的电压差。

差分输入时,是判断两个信号线的电压差。

信号受干扰时,差分的两线会同时受影响,但电压差变化不大。

(抗干扰性较佳) 而单端输入的一线变化时,GND不变,所以电压差变化较大。

(抗干扰性较差)。

差分信号和普通的单端信号走线相比,最明显的优势体现在以下三个方面:A.抗干扰能力强,因为两根差分走线之间的耦合很好,当外界存在噪声干扰时,几乎是同时被耦合到两条线上,而接收端关心的只是两信号的差值,所以外界的共模噪声可以被完全抵消。

B.能有效抑制EMI,同样的道理,由于两根信号的极性相反,他们对外辐射的电磁场可以相互抵消,耦合的越紧密,泄放到外界的电磁能量越少。

C.时序定位精确,由于差分信号的开关变化是位于两个信号的交点,而不像普通单端信号依靠高低两个阈值电压判断,因而受工艺,温度的影响小,能降低时序上的误差,同时也更适合于低幅度信号的电路。

目前流行的LVDS(low voltage differential signaling)就是指这种小振幅差分信号技术。

当AD的输入信号只有一路时,为了更好地抑制共模噪声,我们可以采用差分输入方式。

阻抗匹配概念阻抗匹配是指负载阻抗与激励源内部阻抗互相适配,得到最大功率输出的一种工作状态。

对于不同特性的电路,匹配条件是不一样的。

在纯电阻电路中,当负载电阻等于激励源内阻时,则输出功率为最大,这种工作状态称为匹配,否则称为失配。

如何选择差分ADC驱动器并设计驱动电路

如何选择差分ADC驱动器并设计驱动电路∙Q:用AD9631设计电流转电压,后端加一个变压器,为什么信号会失真并且发热,是自激吗,怎么解决?∙A:应该是由自激的因素引起,由于变压器的输入也会呈现一定的阻容特性,可尝试在输出串联一个小电阻,看是否改善。

∙Q:在AD和运算放大器连接中,零点漂移如何抑制∙A:零点漂移是指当放大电路输入信号为零时,由于受温度变化,电源电压不稳等因素的影响,使静态工作点发生变化,并被逐级放大和传输,导致电路输出端电压偏离原固定值而上下漂动的现象.在实际电路中常采用补偿和调制两种手段。

补偿是指用另外一个元器件的漂移来抵消放大电路的漂移,如果参数配合得当,就能把漂移抑制在较低的限度之内。

∙Q:能推荐一套电桥信号调理的方案,谢谢。

需要带有输入端调零功能。

∙A:可以更具体的提出你的需求吗?ADI有这方面的参考方案,最好你发邮件到china.support@索取资料.∙Q:如何设计稳定合适的驱动电路∙A:这个问题有点大,驱动电路是否合适,要和后端的采样电路匹配才合适!需要从系统级考虑问题∙Q:MCU应用ADC时误差如何减小,怎样校准∙A:这个需要查看误差是从哪里来的,从而来减小噪声源,进行软件或硬件的校准,如布线,软件校准,器件选择等等∙Q:有can和485工业总线的解决方案吗?同样关心!∙A:ADI CAN总线的解决方案目前都是隔离的,如ADM3053,ADM3052等。

其中,ADM3053还提供隔离电源,方便用户使用。

RS-485的产品有很多,有隔离和非隔离型的。

ADM2582/7E是一款隔离电压2.5KVrms,带隔离电源的rs-485收发器。

∙Q:喜欢软件滤波,硬件滤波应该没有软件滤波灵活吧,对不?∙A:硬件滤波主要是通过电容电阻来组合起来滤波的,具有成本方面的优势。

但如果对滤波器的滚降特性等性能要求比较高的话,恐怕要使用软件滤波来实现了。

∙Q:如何减少输入端的共模信号?∙A:主要是要注意差分走线的规范性,比如尽量做到等长平行,并且把握好阻抗控制,另外注意滤除地弹噪声和电源噪声等。

AD差分信号走线规则

AD差分信号走线规则1.差分信号对的位置在PCB布局过程中,应将AD差分信号的正负对位置尽可能靠近,将一对差分信号走在一起,并保持相同的长度。

这样可以减少差分模式下的串扰和噪声。

2.差分信号对走线规则2.1差分信号对应当排布成平行的线对,长度相等,并且应尽量保持对称。

如果差分信号对的长度不一致,可能会引起不必要的相位不匹配或抖动。

2.2差分信号对之间应保持足够的间距,以防止相邻对之间的串扰。

间距的选取应根据具体的信号频率和布局情况进行调整,通常差分信号对之间的间距约为距离线对宽度的1到2倍。

2.3差分信号对的间距应尽量与其他信号线隔离,避免与其他信号线或地平面近距离交叉。

这样可以减少与其他信号的干扰和串扰。

2.4差分信号对的走线应尽量避免直角转弯,因为直角转弯会增加信号的回流路径,导致信号完整性下降。

建议使用45度角或圆角来进行连接。

2.5在追踪差分信号对时,应尽量避免共振现象的出现。

共振现象会导致信号的衰减和失真。

为了避免共振,可以在差分信号对的末端加入终端电阻和衰减电阻,同时保证终端电阻的阻抗与信号的特性阻抗相匹配。

3.差分信号与其他信号线的交叉如果差分信号与其他信号线交叉,则应尽量垂直交叉,并保持一定的间距。

这样可以减少串扰和互相影响。

4.差分信号走线的层次在多层板设计中,可以选择将差分信号走线在内层进行,以减少与其他信号的干扰。

同时,在内层走线时,应尽量保持平面和规则的结构,以降低损耗和串扰。

5.差分信号的接地在差分信号走线时,应尽量将信号的参考地与信号线相连,并通过短接引脚或电容等方式进行连接。

这样可以减少地回流路径,提高信号完整性和抗干扰能力。

总之,AD差分信号走线规则的遵循可以有效提高信号质量和抗干扰能力,确保数字信号的可靠传输。

在实际设计中,需要根据具体的布局和信号特性进行合理的调整,并进行必要的仿真和测试验证。

AD差分信号走线规则

AD差分信号走线规则AD(差分)信号走线规则是指在电路设计中,为了减少噪声和提高信号完整性而遵循的一系列规则和技巧。

AD信号是指差分信号,即由两个相等但相反的信号组成的信号对。

以下是一些常见的AD差分信号走线规则:1.相对路径长度匹配:差分信号对的两个信号线应尽可能地保持相等的长度,以减少传输延迟和时钟偏移。

在PCB布局中,可以使用等长规则和追踪长度匹配工具来确保信号线的长度相等。

2.信号线间距:为了减少互相干扰和串扰,差分信号对之间的间距应尽可能大。

通常,可以保持两条信号线之间的间距大于它们的宽度的3倍。

3.完整平面规划:差分信号对应引脚应保持在同一信号分层上,以实现完整平面设计。

这样可以减少电磁辐射和互相干扰,提高信号完整性。

4.周围引脚分布:差分信号对应引脚的周围应尽可能避免布满其他信号线或高速时钟信号。

这样可以减少干扰源,提高差分信号的质量。

5.地线引脚分布:差分信号对的地线引脚应尽可能放置在靠近信号引脚的位置,以减少共模噪声。

同时,地平面也应该尽可能接近信号引脚,以减少共模电容和电感。

6.串扰抑制:为了减少串扰和互相干扰,可以采用一系列方法。

例如,可以使用不同层次的信号分层,增加地平面的分割,使用屏蔽层等来隔离差分信号对。

7.等角度层叠:为了避免信号跑偏和时间偏移,应尽量采用等角度层叠的方式布局差分信号对。

等角度层叠是指差分信号对的通路长度和信号线之间的角度保持一致。

8.引脚布局:在AD转换器的设计中,引脚布局也非常重要。

差分信号对应的引脚应尽可能靠近一起,以减少传输线的长度和间距。

9.绝对地和参考平面:在AD转换器中,保持一个稳定的绝对地和参考平面非常重要。

这可以通过将地平面与参考平面连续铺设,使用细跨距信号连接和增加电源滤波器来实现。

10.信号线宽度和间距:为了满足差分信号对的特定阻抗要求,信号线的宽度和间距应按照设计要求进行计算和布局。

总之,AD差分信号走线规则是电路设计中十分关键的一环,通过遵循这些规则和技巧,可以有效减少噪声和互相干扰,提高差分信号的完整性和稳定性。

AD中关于差分线的设置和走线的方法

AD中关于差分线的设置和走线的方法在模拟电路设计中,差分线是一种用于传输差分信号的特殊线路结构。

差分信号是指由两个相互互补的信号组成的信号对,它们具有相同的幅值和频率,但相位相反。

差分线的设计和走线方法在高速、高精度的模拟电路设计中起着重要的作用。

本文将重点介绍AD设计中关于差分线的设置和走线的方法。

一、差分线的设置差分线的设置包括差分线的布线方向、布线层次、长度匹配等方面。

下面分别对这些方面进行详细介绍。

1.布线方向差分线的布线方向取决于信号的传输方向。

一般情况下,信号的传输方向是由发送方向接收方的方向确定的。

差分线的布线方向要尽量与信号传输方向保持一致,这样能最大程度地减小传输引起的干扰。

2.布线层次差分线的布线层次是指差分线在PCB板上布线的层次。

通常,差分线是通过内层进行布线的。

内层布线能有效地屏蔽外部干扰,减小信号的传输损耗和串扰。

内层布线的层数一般选取4-6层,具体根据设计需求和布局来确定。

3.长度匹配差分线的长度匹配是差分线设计中非常关键的一部分。

由于差分线上的两个信号是相互互补的,如果差分线的长度不匹配,会导致两个信号的相位差发生变化,从而影响信号的传输和接收。

因此,差分线的长度应该尽量匹配。

为了实现差分线的长度匹配,我们可以采用以下方法:(1)使用等长线:差分线的长度可以通过使用等长线的方式来保证。

通过差分线的等长设计,可以使差分线的传输时间相等,从而保证信号的传输质量。

(2)使用差分对延时器:差分对延时器是一种特殊的线路设计,可以用于实现差分线的长度匹配。

差分对延时器通过延时差分信号中一个信号的传输时间,从而使两个信号在接收端同时到达。

(3)使用布线工具:现代的电路设计软件和布线工具往往会提供差分线的长度匹配功能。

通过使用这些工具,我们可以很方便地实现差分线的长度匹配。

二、差分线的走线方法差分线的走线方法主要包括屏蔽、分干扰区和走线规则等。

1.差分线屏蔽差分信号在传输过程中容易受到周围的干扰,为了减小干扰的影响,可以采用差分线屏蔽的方法。

AD差分信号走线规则

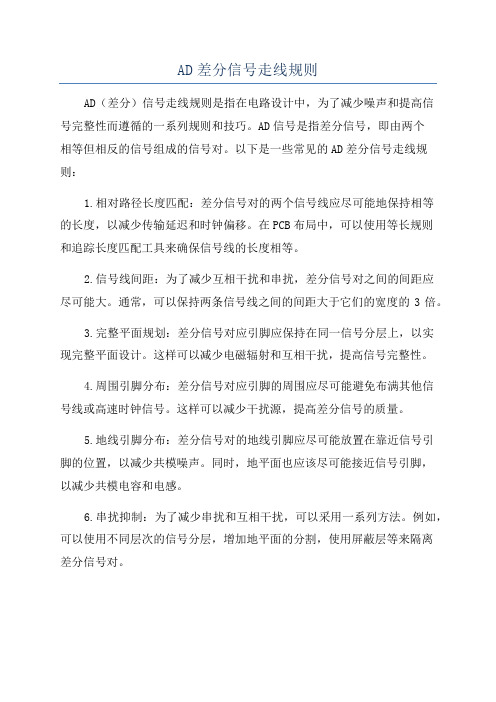

Altium designer软件中如何画差分信号线对?快捷键P-M在PCB中定义差分对在PCB面板中选择Differential Pairs Editor模式并点击Add按钮。

在弹出的Differential Pair对话框中,在现有的网络中选择正极和负极网络,并对差分对进行命名后点击OK。

Quickly create pairs from the named nets.同样可以通过网络名称进行差分对的定义,对于一个差分对,其名称有相同的前辍,并以不同的后辍作区分,如TX0_P或TX0_N。

在PCB面板中点击Create From Nets按钮打开Create Differential Pairs From Nets对话框。

在对话框顶部使用过滤器从现存的网络中筛选出差分对。

如图所示为对电路板上以“_P”或“_N”结尾的网络名称进行筛选。

适用的设计规则对差分对进行布线,必先在PCB Rules和Constraints Editor对话框(在Design>>Rules 中调出)中的三项设计规则进行配置,分别是:Routing Width -定义了差分对线路的宽度,线路宽度可以是实际的物理宽度或根据用户定义的特征阻抗自动计算而得。

把规则的范围设置到差分对的目标器件上,如*InDifferentialPair*。

Differential Pairs Routing -定义了差分网络线路的间距和解耦合长度(当间隔宽度大于Max Gap的设置值时成对的走线将失去耦合)。

把规则的范围设置到差分对的目标器件上,如*IsDifferentialPair*。

Electrical Clearance -定义了各个器件包括相同的网络和不同的网络(焊盘与焊盘间,焊盘与线路间)的间距。

把规则的范围设置到差分对的目标器件上,如*InDifferentialPair*。

差分对线路的长度可以通过Interactive Diff Pair Length Tuning(在Tools菜单中)功能进行调整。

ad20创建差分对规则

ad20创建差分对规则在AD20中创建差分对规则的步骤如下:1.在AD20中打开PCB设计项目,并打开PCB文件。

2.在左侧的"Components"面板中,找到要创建差分对的两个元件,双击它们,将它们放置到PCB工作区中。

3.选中两个元件中的一个,点击"Edit"菜单中的"Properties"选项,打开元件属性对话框。

4.在元件属性对话框中,找到"Pin Pair"选项卡,点击"Add"按钮添加一个新的差分对。

5.在弹出的对话框中,输入差分对的名称和描述,并选择差分对的类型(如LVDS、USB等)。

6.在"Pins"列表中,选择要组成差分对的两个引脚,并设置它们的方向(如输入或输出)。

7.根据需要设置差分对的电气规则,如阻抗、延迟等。

这些规则将用于确保差分对在高速信号传输时的性能和稳定性。

8.点击"OK"按钮保存差分对规则的设置。

9.重复以上步骤,可以创建多个差分对规则。

10.在PCB设计完成后,可以使用AD20中的仿真工具对差分对进行仿真和分析,以确保它们满足设计要求。

需要注意的是,在创建差分对规则时,应该根据实际需求和信号传输要求进行设置。

同时,还需要考虑PCB布局和布线的影响,以确保差分对的性能和稳定性。

此外,差分对规则的设置也需要考虑与其他元件和信号的兼容性和互操作性。

总之,在AD20中创建差分对规则需要仔细考虑多个因素,并进行合理的设置和调整。

只有通过对差分对的性能进行充分的分析和验证,才能确保其在高速信号传输中的应用效果和可靠性。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

A/D差分输入信号

在上一节已经提到过,控制字的第4位和第5位是用于控制PCF8591的模拟输入引脚是单端输入还是差分输入。

差分输入是模拟电路常用的一个技巧,这里我们把相关知识做一些简单介绍。

从严格意义上来讲,其实所有的信号都是差分信号,因为所有的电压只能是相对于另外一个电压而言。

但是大多数系统,我们都是把系统的GND作为基准点。

而对于A/D来说的差分输入,通常情况下是除了GND以外,另外两路幅度相同,极性相反的输入信号,其实理解起来很简单,就如同跷跷板一样。

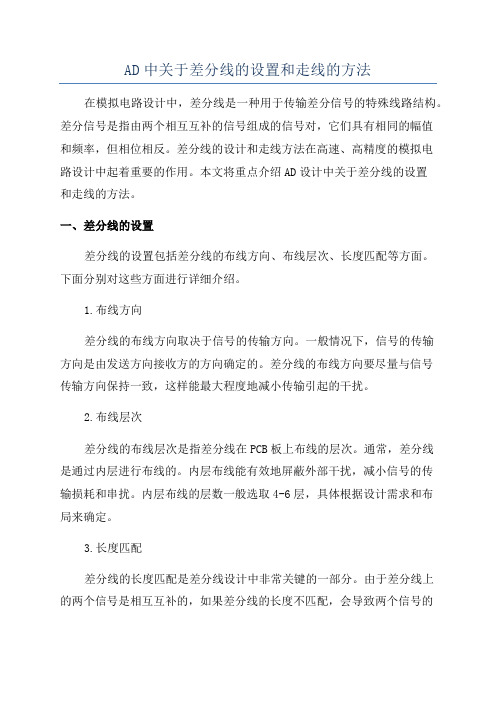

如图17-8所示。

图17-8差分输入原理

差分输入的话,就不是单个输入,而是由2个输入端构成的一组输入。

PCF8591一共是4个模拟输入端,可以配置成4种模式,最典型的是4个输入端构造成的两路差分模式,如图17-9所示。

图17-9PCF8591差分输入模式

当控制字的第4位和第5位都是1的时候,那么4路模拟被配置成2路差分模式输入channel0和channel1。

我们以channel0为例,其中AIN0是正向输入端,AIN1是反向输入端,它们之间的信号输入是幅度相同,极性相反的信号,通过减法器后,得到的是两个输入通道的差值,如图17-10所示。

图17-10差分输入信号

通常情况下,差分输入的中线是基准电压的一半,我们的基准电压是 2.5V,假如 1.25V作为中线,V+是AIN0的输入波形,V-是AIN1的输入波形,Signal Value就是经过减法器后的波形。

很多A/D都采用差分的方式输入,因为差分输入方式比单端输入来说,有更强的抗干扰能力。

单端输入信号时,如果一线上发生干扰变化,比如幅度增大5mv,GND不变,测到的数据会有偏差;

而差分信号输入时,当外界存在干扰信号时,只要布线合理,大都同时被耦合到两条线上,幅度增大5mv会同时增大5mv,而接收端关心的只是两个信号的差值,所以外界的这种共模噪声可以被完全抵消掉。

由于两根信号的极性相反,它们对外辐射的电磁场可以相互抵消,有效的抑制释放到外界的电磁能量。

在我们的KST-51开发板上,我们没有做差分信号输入的实验环境,由于这个内容在A/D部分比较重要,所以还是介绍给大家,以供参考。