飞思卡尔单片机增强型定时器计数器

单片机定时器 计数器

单片机定时器计数器单片机定时器/计数器在单片机的世界里,定时器/计数器就像是一个精准的小管家,默默地为系统的各种操作提供着精确的时间控制和计数服务。

无论是在简单的电子时钟、还是复杂的通信系统中,都能看到它们忙碌的身影。

那什么是单片机的定时器/计数器呢?简单来说,定时器就是能够按照设定的时间间隔产生中断或者触发事件的模块;而计数器则是用于对外部脉冲或者内部事件进行计数的功能单元。

我们先来看看定时器的工作原理。

想象一下,单片机内部有一个像小闹钟一样的东西,我们可以给它设定一个时间值,比如说 1 毫秒。

当单片机开始工作后,这个小闹钟就会以一个固定的频率开始倒计时,当倒计时结束,也就是 1 毫秒到了,它就会发出一个信号,告诉单片机“时间到啦”!这个信号可以用来触发各种操作,比如更新显示、读取传感器数据等等。

定时器的核心在于它的时钟源。

就好比小闹钟的动力来源,时钟源决定了定时器倒计时的速度。

常见的时钟源有单片机的内部时钟和外部时钟。

内部时钟一般比较稳定,但精度可能会受到一些限制;而外部时钟则可以提供更高的精度,但需要额外的电路支持。

再来说说计数器。

计数器就像是一个勤劳的小会计,不停地数着外面进来的“豆子”。

这些“豆子”可以是外部的脉冲信号,也可以是单片机内部产生的事件。

比如,我们可以用计数器来统计电机旋转的圈数,或者计算按键被按下的次数。

计数器的工作方式也有多种。

可以是向上计数,就是从 0 开始,不断增加,直到达到设定的最大值;也可以是向下计数,从设定的最大值开始,逐渐减少到 0。

还有一种更灵活的方式是双向计数,根据需要在向上和向下之间切换。

那么,定时器/计数器在实际应用中有哪些用处呢?比如说,在一个智能温度控制系统中,我们可以用定时器每隔一段时间读取一次温度传感器的数据,然后根据温度的变化来控制加热或者制冷设备的工作。

而计数器则可以用来统计设备运行的次数,以便进行维护和保养。

在电子时钟的设计中,定时器更是发挥了关键作用。

单片机的定时器计数器ppt课件

任务: 懂得设置TMOD和TCON以及初值计算 读懂程序

注意: 不同工作方式下初值的处理

7.1 定时器/计数器概述

实现定时功能,主要采用下面三种方法:

软件定时:软件定时不占用硬件资源,但占用了 CPU时间,降低了CPU的利用率。 采用硬件定时:完全由硬件实现,不占CPU,但 定时值与定时范围不能由软件进行控制和修改,即 不可编程。 采用可编程芯片定时:通过对系统时钟脉冲的计 数实现,计数值通过程序设定,此种定时功能强, 使用灵活。

2、求T0的方式控制字TMOD: M1M0=01,GATE=0,C/T=0,可取方式控 制字为01H;

ORG 0000H

LJMP MAIN 到主程序

;跳转

ห้องสมุดไป่ตู้

ORG 000BH 断入口地址

;T0的中

LJMP DVT0 断服务程序

;转向中

ORG 0100H

MAIN:MOV TMOD,#01H ; 置T0工作于方式1

MOV TL1,#9CH ;置初值

MOV TH1,#9CH

SETB TR1

;启动T1

DEL:JBC TF1,REP ;查询计数溢出

AJMP DEL

REP:CPL P1。0

;输出取反

AJMP DEL

❖门控位的应用

例:利用T0门控位测试INT0引脚上出现的正脉冲的宽度, 并以机器周期数的形式显示在显示器上。

那么:计数值 N=T/机器周期= 213-X

所以 X= 213-N= 8192-N= 8192-T/机器 周期

=8192-1×10-3/2×10-6=7692

THX0=对0F应0H的二进制数为 11110000 01100

单片机定时器计数器

定时器计数器的编程步骤

确定单片机型号和开发环境

根据项目需求选择合适的单片机型号和开发 环境。

编写程序代码

使用编程语言编写程序代码,实现定时器计 数器的功能。

配置定时器计数器

根据需要配置定时器计数器的模式、工作方 式、输入时钟源等参数。

编译和调试

将程序代码编译成可执行文件,并在单片机 上进行调试和测试。

率和周期。

02 单片机定时器计数器的原 理

定时器计数器的原理

定时器计数器是一种用于测量时间间隔的硬件设备,它通过 计数时钟脉冲来计算时间。在单片机中,定时器计数器通常 由一个加法器、一个预分频器、一个计数器和一个控制逻辑 组成。

当定时器计数器的输入时钟脉冲到来时,加法器将计数器的 当前值加1,并将结果存入计数器中。当计数器的值达到预设 的计数值时,定时器计数器就会产生一个中断信号或输出脉 冲信号。

05 单片机定时器计数器的优 化与改进

提高定时器计数器的精度

硬件设计优化

采用高精度的时钟源和计数器,减少计数误差。

软件算法改进

采用更精确的计时算法,如使用高精度计时库或 算法。

校准与补偿

定期对定时器计数器进行校准和补偿,以消除误 差。

优化定时器计数器的响应速度

01

02

03

减少中断延迟

优化中断处理程序,减少 中断响应时间。

1 2 3

自动化生产控制

单片机定时器计数器可以用于自动化生产线的控 制,实现精确的时间间隔控制和计数,提高生产 效率和产品质量。

电机控制

通过单片机定时器计数器,可以精确控制电机的 启动、停止和运行速度,实现电机的高效、稳定 运行。

工业传感器

单片机定时器计数器可以用于工业传感器的时间 基准和计数功能,提高传感器测量的准确性和可 靠性。

C语言实现控制电机加减速正反转(飞思卡尔C代码)

C语言实现控制电机加减速正反转(飞思卡尔C代码)用单片机控制直流电动机的正反转、加减速的程序如何用C语言写参考一下这个例子吧。

#include#defineucharunignedchar#defineuintunignedintbitPW1=P2^0;bitPW2=P2^1;//控制电机的两个输入bitaccelerate=P2^2;//调速按键bittop=P2^3;//停止按键bitleft=P2^4;//左转按键bitright=P2^5;//右转按键#defineright_turnPW1=0;PW2=1//顺时针转动#defineleft_turnPW1=1;PW2=0//逆向转动#defineend_turnPW1=1;PW2=1//停转uintt0=25000,t1=25000;//初始时占空比为50%uinta=25000;//设置定时器装载初值25m设定频率为20Hzucharflag=1;//此标志用于选择不同的装载初值uchardflag;//左右转标志ucharcount;//用来标志速度档位voidkeycan();//键盘扫描voiddelay(ucharz);voidadjut_peed();//通过调整占空比来调整速度//某某某某某某某某某某某某某某某某某某某某某某某某某某某某某某某某某某//voidmain(){keycan();//不断扫描键盘程序,以便及时作出相应的响应}}if(flag){flag=0;end_turn;a=t0;//t0的大小决定着低电平延续时间TH0=(65536-a)/256;TL0=(65536-a)%6;//重装载初值}ele{flag=1;//这个标志起到交替输出高低电平的作用if(dflag==0){right_turn;//右转}ele{left_turn;//左转}a=t1;//t1的大小决定着高电平延续时间TH0=(65536-a)/256;TL0=(65536-a)%6;//重装载初值}}TMOD=0某01;//工作方式寄存器软件起动定时器定时器功能方式1定时器0TH0=(65536-a)/256;TL0=(65536-a)%6;//装载初值ET0=1;//开启定时器中断使能EA=1;//开启总中断TR0=0;}//某某某某某某某某某某某某某某某某某某某某某某某某某某某某某某某某某某某某某某某某//voiddelay(ucharz)//在12M下延时z毫秒{ uint某,y;for(某=z;某>0;某--)for(y=110;y>0;y--);}//某某某某某某某某某某某某某某某某某某某某某某某某某某某某某某//voidkeycan(){if(top==0){TR0=0;//关闭定时器0即可停止转动end_turn;} if(left==0){TR0=1;dflag=1;//转向标志置位则左转}if(right==0){TR0=1;dflag=0;//转向标志复位则右转}if(accelerate==0){delay(5);//延时消抖if(accelerate==0){ while(accelerate==0);//等待松手count++;if(count==1){t0=20000;t1=30000;//占空比为百分之60}if(count==2){t0=15000;t1=35000;//占空比为百分之70}if(count==3){t0=10000;t1=40000;//占空比为百分之80}if(count==4){t0=5000;t1=45000;//占空比为百分之90}if(count==5){count=0;}}}}功能特点:1)总线速度高达40MHz,CAN总线:3个1Mbp的CAN总线,兼容CAN2.0A/B;2)128KB程序Flah和8KBDataFlah,用于实现程序和数据存储,均带有错误校正码(ECC);3)可配置A/D:16通道模数转换器;可选8位10位和12位精度,3μ的转换时间4)内嵌MSCAN模块用于CAN节点应用,内嵌支持LIN协议的增强型SIC模块和SPI模块;5)4通道16位计数器,CRG时钟和复位发生器:锁相环、看门狗、实时中断;增强型捕捉定时器;6)出色的低功耗特性,带有中断唤醒功能的10,实现唤醒休眠系统的功能;7)通道PWM:8位8通道或16位4通道PWM,易于实现电机控制。

FreeScale_HCS12系列单片机教程(dg128)

HCS12微控制器系列教程---第一讲:PWM 模块介绍该教程以MC9S12DG128单片机为核心进行讲解,全面阐释该16位单片机资源。

本文为第一讲,开始介绍S12 MCU的PWM模块。

PWM 调制波有8 个输出通道,每一个输出通道都可以独立的进行输出。

每一个输出通道都有一,一个周期控制寄存器和两个可供选择的时钟源。

每一个PWM 输出个精确的计数器(计算脉冲的个数)通道都能调制出占空比从0—100% 变化的波形。

PWM 的主要特点有:1、它有8 个独立的输出通道,并且通过编程可控制其输出波形的周期。

2、每一个输出通道都有一个精确的计数器。

3、每一个通道的PWM 输出使能都可以由编程来控制。

4、PWM输出波形的翻转控制可以通过编程来实现。

5、周期和脉宽可以被双缓冲。

当通道关闭或PWM计数器为0时,改变周期和脉宽才起作用。

6、8 字节或16 字节的通道协议。

,他们提供了一个宽范围的时钟频率。

7、有4 个时钟源可供选择(A、SA、B、SB)8、通过编程可以实现希望的时钟周期。

9、具有遇到紧急情况关闭程序的功能。

10、每一个通道都可以通过编程实现左对齐输出还是居中对齐输出。

HCS12微控制器系列教程---第二讲:PWM 寄存器简介1、PWM启动寄存器PWMEPWME 寄存器每一位如图1所示:复位默认值:0000 0000B图1 PWME 寄存器每一个PWM 的输出通道都有一个使能位PWMEx 。

它相当于一个开关,用来启动和关闭相应通道的PWM 波形输出。

当任意的PWMEx 位置1,则相关的PWM输出通道就立刻可用。

用法:PWME7=1 --- 通道7 可对外输出波形PWME7=0 --- 通道7 不能对外输出波形注意:在通道使能后所输出的第一个波形可能是不规则的。

当输出通道工作在串联模式时(PWMCTL寄存器中的CONxx置1),那么)使能相应的16位PWM 输出通道是由PWMEx的高位控制的,例如:设置PWMCTL_CON01 = 1,通道0、1级联,形成一个16位PWM 通道,由通道1 的使能位控制PWM 的输出。

飞思卡尔8位单片机-第7章 定时器和比较器模块

二、TPM中的寄存器

(三)TPM模寄存器(TPMMODH:TPMMODL)

TPMMOD高位 TPMMODH

TPMMOD低位 TPMMODL

两个可读/写8位寄存器,定义计数器的最大值 加法计数器(CPWMS=0),当计数器计数到与模寄存 器数值相等时,TPMCNT翻转至0x0000 加/减计数器(CPWMS = 1),当计数器计数到与模寄存器 数值相等时,计数器开始递减。

表7-5 模式、沿和电平选择

CPWMS MSnB: MSnA ELSnB: ELSnA

模式

功能

x 0

xx 00

00 01 10 11 00 01 10 11 10 x1

通道未使用外部管脚,可能是管脚作为TPM的外部时钟 输入或者是将管脚作为通用I/O使用。 输入捕捉 仅上升沿捕捉 仅下降沿捕捉 上升沿或下降沿都捕捉 仅软件比较,无管脚输出 比较匹配时,外部管脚翻转 比较匹配时,外部管脚清0 比较匹配时,外部管脚置1 脉宽有效期间高电平(比较匹配时, 外部管脚清0) 脉宽有效期间低电平(比较匹配时, 外部管脚置1) 脉宽有效期间高电平(比较匹配时, 外部管脚清0) 脉宽有效期间低电平(比较匹配时, 外部管脚置1)

触发:外部引脚发生有效电平跳变

响应: CHnF=1 , 主计数器TPMCNT值→通道辅助寄存器TPMCnV

三、TPM模块的功能模式

(二)输出比较

功能:从外部引脚输出可编程脉冲

模式设定方式:

CPWMS 0 MSnB: MSnA 01 ELSnB: ELSnA 00 01 10 11 模式 输出比较 功能描述 仅软件比较,无管脚输出 比较匹配时,外部管脚翻转 比较匹配时,外部管脚清0 比较匹配时,外部管脚置1

飞思卡尔MC9S12XS128(定时器)ECT寄存器详解

1、定时器IC/OC功能选择寄存器TIOSIOS[7..0]IC/OC功能选择通道0 相应通道选择为输入捕捉(IC)1 相应通道选择为输出比较(OC)2、定时器比较强制寄存器 CFORCFOC[7..0]设置该寄存器某个FOCn位为1将导致在相应通道上立即产生一个输出比较动作,在初始化输出通道时候非常有用。

【说明】这个状态和正常状态下输出比较发生后,标志位未被置位后的情况相同。

3、输出比较7屏蔽寄存器 OC7MOC7M[7..0]OC7(即通道7的输出比较)具有特殊地位,它匹配时可以直接改变PT7个输出引脚的状态,并覆盖各个引脚原来的匹配动作结果,寄存器OC7M决定哪些通道将处于OC7的管理之下。

OC7M中的各位与PORTT口寄存器的各位一一对应。

当通过TIOS将某个通道设定为输出比较时,将OC7M中的相应位置1,对应的引脚就是输出状态,与DDR中的对应位的状态无关,但OC7Mn并不改变DDR相应位的状态。

【说明】OC7M具有更高的优先级,它优于通过TCTL1和TCTL2寄存器中的OMn和OLn设定的引脚动作,若OC7M中某个位置1,就会阻止相应引脚上由OM和OL设定的动作。

4、输出比较7数据寄存器 OC7DOC7D[7..0]OC7M对于其他OC输出引脚的管理限于将某个二进制值送到对应引脚,这个值保存在寄存器OC7D中的对应位中。

当OC7匹配成功后,若某个OC7Mn=1,则内部逻辑将OC7Dn送到对应引脚。

OC7D中的各位与PORTT口寄存器的各位一一对应。

当通道7比较成功时,如果OC7M中的某个位为1,OC7D中的对应位将被输出到PORTT的对应引脚。

【总结】通道7的输出比较(OC7)具有特殊的位置,在OC7Mn和OC7Dn两个寄存器设置以后,OC7成功输出后将会引起一系列的动作。

比如:OC7M0=1,则通道0处在OC7的管理下,在OC7成功后,系统会将OC7D0的逻辑数据(仅限0或者1)反应在PT0端口上。

(整理)飞思卡尔8位单片机MC9S08JM60开发板实践教程

第一章搭建实验环境系统时钟设置#include "App\Include\App.h"#ifndef _MCG_C#define _MCG_C//oscillator 12MHZ 倍频为24MHZ()先8分频后16倍频void S_MCGInit(void){/* the MCG is default set to FEI mode, it should be change to FBE mode*//************************************************************************** ***********MCGC2[7:6] BDIV总线频率分频因子–选择由MCGC1寄存器中CLKS位决定的时钟源的分频。

这控制总线频率。

00 编码0 –时钟1分频01 编码1 –时钟2分频(复位后默认)10 编码2 –时钟4分频11 编码3 –时钟8分频[5] RANGE频率范围选择–选择外部振荡器或者外部时钟源的频率范围。

1 选择1MHz到16MHz外部振荡器的频率范围。

(1MHz到40MHz的外部时钟电源)的高频率范围0 选择32kHz到100kHz外部振荡器的频率范围。

(32kHz到1MHz的外部时钟电源)的低频率范围[4] HGO高增益振荡器选择–控制外部振荡器操作模式。

1 配置外部振荡器为高增益运行0 配置外部振荡器为低功耗运行[3] LP低功耗选择–控制在忽略模式中FLL(或者PLL)是否为无效1 FLL(或PLL)在忽略模式(低功耗)中为无效的。

0 FLL(或PLL)在忽略模式中为无效的。

[2] EREFS外部参考时钟选择–为外部参考选择时钟源1 选择振荡器0 选择外部时钟源[1] ERCLKEN外部参考时钟使能–使能外部参考时钟作为MCGERCLK1 MCGERCLK激活0 MCGERCLK 无效[0] EREFSTEN外部参考时钟停止使能MCGC2 0b0011 0110 激发外部时钟(晶振)(没有使能)*************************************************************************** ***********/MCGC2=MCGC2_RANGE_MASK|MCGC2_HGO_MASK|MCGC2_EREFS_MASK|MCGC2_ERCLK EN_MASK;while(!MCGSC_OSCINIT);//MCGSC寄存器中OSCINIT(第1位)为1,表示由EREFS位选择的晶振被初始化。

飞思卡尔eTPU中文使用说明(书签版)

>= Comparator >= 23 Comparator >= 捕获寄存器1 Comparator Comparator Comparator 23 捕获寄存器2

设置匹配和转型事件是在微 一个匹配同步两个24位自由运行定时器计数寄存器,TCR1或TCR2 同步捕获到的两个24位自由运行定时器计数寄存器,TCR1或TCR2.

15 15

CH0

0 0 0 0 0 0

输入输出引脚 CH31 CH0

TCR1视程

TCR2

0

TB2R

23

TCR2视程

0

23 匹配寄存器2 Compare/Match Register Capture Register Compare/Match Register Capture Register Compare/Match Register Compare/Match Register Compare/Match Register 23 比较器1 Compare/Match Register Compare/Match Register Compare/Match Register >= Compare/Match Register >= >= 23 比较器2 Comparator >= Comparator >= Comparator >= Comparator

页8

Freescale™ and the Freescale logo are trademarks of Freescale Semiconductor, Inc. All other product or service names are the property of their respective owners. © Freescale Semiconductor, Inc. 2005

单片机原理及应用-S12X单片机的结构与组成

单片机原理及应用-S12X单片机的结构与组成单片机原理及应用S12X 单片机的结构与组成在当今的电子技术领域,单片机的应用可谓无处不在。

从智能家居到工业控制,从汽车电子到医疗设备,单片机都扮演着至关重要的角色。

其中,S12X 单片机以其出色的性能和独特的结构组成,在众多单片机中脱颖而出。

S12X 单片机是飞思卡尔(现恩智浦)推出的一款高性能 16 位单片机。

它采用了增强型的 HCS12 内核,相较于传统的 8 位单片机,具有更强的处理能力和更丰富的功能。

从硬件结构上看,S12X 单片机主要由以下几个部分组成:1、中央处理器(CPU):这是单片机的核心,负责执行指令和进行数据处理。

S12X 的 CPU 采用了 16 位的架构,具有较高的运算速度和处理能力。

2、存储器:包括程序存储器(Flash 或 ROM)和数据存储器(RAM)。

程序存储器用于存储用户编写的程序代码,而数据存储器则用于存储运行过程中的临时数据。

S12X 单片机通常具有较大的存储空间,以满足复杂应用的需求。

3、输入/输出(I/O)端口:用于与外部设备进行数据交换。

这些端口可以配置为不同的工作模式,如输入、输出、高阻态等,以适应各种接口需求。

4、定时器/计数器:用于实现定时、计数和脉冲宽度调制(PWM)等功能。

S12X 单片机通常配备多个定时器/计数器,以满足不同的定时和计数需求。

5、串行通信接口:如SCI(串行通信接口)、SPI(串行外设接口)和 IIC(集成电路间总线)等,用于与其他设备进行串行数据通信。

6、模数转换器(ADC):用于将模拟信号转换为数字信号,以便单片机进行处理。

7、脉宽调制模块(PWM):可以生成不同占空比的脉冲信号,用于控制电机、灯光等设备。

在软件方面,S12X 单片机通常使用特定的开发工具和编程语言进行编程。

常见的编程语言有 C 语言和汇编语言。

开发人员可以使用这些语言编写程序,并通过下载工具将程序烧录到单片机的存储器中。

飞思卡尔S12xs128单片机BDM调试器使用技巧

S12(X)单片机BDM调试器使用技巧第五届全国大学生“飞思卡尔”杯智能气车竞赛限制采用最新的MC9S12XS128(以下简称XS128)单片机作为主控芯片,替代MC9S12DG128。

XS128是Freescale公司推出的S12系列单片机中的一款增强型16位单片机。

片内资源丰富,接口模块有SPI、SCI、IIC、A/D、PWM等常见模块,在汽车电子应用领域具有广泛用途。

XS128和以往大赛使用的S12DG128系列单片机一样,调试接口都是使用Freescale公司传统的BD M(Background Debug Module)接口。

1 MC9S12XS128单片机介绍(1)CPU:增强型16位HCS12 CPU,片内总线时钟最高40 MHz;(2)片内资源:8 KB RAM、128 KB程序闪存、2 KB数据闪存;(3)串行接口模块:SCI、SPI;(4)脉宽调制模块(PWM)可设置成4路8位或者2路16位,逻辑时钟选择频率宽;(5)1个16路12位精度A/D转换器;(6)控制器局域网模块(CAN);(7)增强型捕捉定时器。

MC9S12XS128单片机有112、80和64引脚3种封装形式。

80-pin封装的单片机没有引出用于扩展方式的端口,仅引出了一个8路A/D接口。

竞赛可使用112或80引脚封装器件。

2 BDM接口和使用BDM调试器内部有一个8位的MC9HC08JB16单片机,该单片机有USB接口,可与PC 机信息交互。

HC08单片机和S12单片机间仅使用一根 I/O线通信,这根相连的信号线名为BKGD。

HC08单片机将BKGD置为输出,以串行发送命令,发送完成后转为输入,以接收信息。

S12单片机收到命令后转为输出,根据调试器发来的命令回送信息,然后立即转入接收态。

BDM工具以此方式实现S12单片机的在线调试、内部闪存的烧写等功能。

关于BDM接口的实现,读者可以参考Freescale任何一款S12单片机的器件手册,其对BDM接口的命令字、交互模式等都有详细描述。

单片机定时器与计数器的工作原理及应用

单片机定时器与计数器的工作原理及应用摘要:单片机作为现代电子设备中广泛采用的一种集成电路,其内部包含了丰富的功能模块,其中定时器和计数器被广泛应用于各种领域。

本文将介绍单片机定时器和计数器的工作原理及应用,包括定时器的基本原理、工作模式和参数配置,以及计数器的工作原理和常见应用场景。

希望通过本文的阐述,读者能够深入了解单片机定时器和计数器的基本原理和应用,为电子系统设计提供参考。

引言:单片机作为嵌入式系统中的核心部件,承担着控制和处理各种信号的重要任务。

定时器和计数器作为单片机的重要功能模块,为实现各种实时控制任务提供了有效的工具。

定时器可以生成一定时间间隔的定时信号,而计数器则可以对外部事件的频率进行计数,实现时间测量和计数控制等功能。

一、定时器的工作原理单片机中的定时器通常为计数器加上一定逻辑控制电路构成。

定时器的基本工作原理是通过控制计数器的计数速度和计数值来实现不同时间间隔的输出信号。

当定时器触发时,计数器开始计数,当计数值达到预设值时,定时器产生一个输出信号,然后重新开始计数。

定时器通常由以下几个部分组成:1.计数器:定时器的核心部件是计数器,计数器可以通过内部振荡器或外部输入信号进行计数。

通常情况下,计数器是一个二进制计数器,它可以按照1、2、4、8等倍数进行计数。

2.预设值:定时器的预设值决定了定时器的时间间隔。

当计数器达到预设值时,定时器会产生一个输出脉冲。

3.控制逻辑电路:控制逻辑电路用于控制计数器的启动、停止和重置等操作。

通常情况下,控制逻辑电路由一系列的触发器和逻辑门组成。

二、定时器的工作模式定时器可以根据实际需求在不同的工作模式下运行,常见的工作模式有以下几种:1.定时工作模式:在定时工作模式下,定时器按照设定的时间间隔进行计数,并在计数值达到预设值时产生一个输出脉冲。

这种模式常用于周期性任务的触发和时间测量。

2.计数工作模式:在计数工作模式下,定时器通过外部输入信号进行计数,可以测量外部事件的频率。

单片机定时器计数器工作原理

单片机定时器计数器工作原理一、引言单片机作为嵌入式系统的核心部件,在工业控制、智能家居、汽车电子等领域中发挥着重要作用。

在单片机中,定时器和计数器是常用的功能模块,它们可以实现精确的定时控制和计数功能。

本文将详细介绍单片机定时器计数器的工作原理,以及其在实际应用中的作用。

二、单片机定时器和计数器概述单片机定时器和计数器是单片机内部的特殊功能模块,用于生成精确的时间延时和进行事件计数。

在单片机的内部结构中,定时器和计数器通常由定时/计数器模块和控制逻辑组成,通过寄存器配置和控制信号来实现各种定时和计数功能。

定时器和计数器通常包括以下几个重要的功能部分:1. 控制寄存器:用于配置定时器/计数器工作模式、计数模式、计数方向等参数。

2. 定时/计数寄存器:用于存储定时器/计数器的计数值,根据计数模式进行累加或递减。

3. 比较寄存器:用于存储比较值,用于与定时/计数器的计数值进行比较,从而触发相应的中断或输出信号。

定时器通常用于产生精确的时间延时,常用于生成精确的脉冲信号、PWM信号等。

而计数器则用于进行精确的事件计数,通常用于测量脉冲个数、计时等应用。

三、定时器和计数器的工作原理1. 定时器的工作原理定时器的工作原理主要分为定时/计数模式的选择、定时器计数器的递增和中断触发等几个方面。

在配置定时器工作模式时,可以选择不同的计数模式,包括定时器/计数器模式、分频器模式等。

通过配置控制寄存器和定时/计数寄存器,可以设置定时器的计数值和计数方向。

在定时器计数器的递增过程中,定时器会根据设定的计数模式和计数值进行递增,当达到比较寄存器中的比较值时,会触发相应的中断或输出信号。

这样就实现了定时器的定时操作。

2. 计数器的工作原理计数器的工作原理与定时器类似,同样涉及到计数模式的选择、计数器的递增和中断触发等几个方面。

在配置计数器工作模式时,同样可以选择不同的计数模式,通过配置控制寄存器和计数寄存器来设置计数器的计数值和计数方向。

单片机定时器计数器工作原理

单片机定时器计数器工作原理单片机定时器计数器是单片机中非常重要的一个模块,它通常用于实现各种定时和计数功能。

通过定时器计数器,单片机能够精准地进行定时操作,实现定时中断、计数、脉冲生成等功能。

本文将详细介绍单片机定时器计数器的工作原理。

1. 定时器计数器的功能单片机定时器计数器通常由若干寄存器和控制逻辑组成,可以实现以下几种功能:- 定时功能:通过设置计数器的初始值和工作模式,可以实现一定时间的定时功能,单片机能够在计时结束时触发中断或产生输出信号。

- 计数功能:可以实现对外部信号的计数功能,用于测量脉冲个数、频率等。

也可以用于实现脉冲输出、PWM等功能。

- 脉冲发生功能:可以在一定条件下控制定时器输出脉冲,用于控制外部器件的工作。

2. 定时器计数器的工作原理定时器计数器的工作原理可以分为初始化、计数及中断处理几个基本环节。

(1)初始化:在使用定时器前,需要对定时器计数器进行初始化设置。

主要包括选择工作模式、设置计数器的初始值、开启中断等。

不同的单片机厂商提供了不同的定时器初始化方式和寄存器设置方式,通常需要查阅相关的单片机手册来进行设置。

(2)计数:初始化完成后,定时器开始进行计数工作。

根据不同的工作模式,定时器可以以不同的频率进行计数。

通常采用的计数源是内部时钟频率,也可以选择外部时钟源。

通过对计数器的频率设置和初始值的设定,可以实现不同的定时功能。

(3)中断处理:在定时器计数完成后,可以触发中断来通知单片机进行相应的处理。

通过中断服务程序,可以定时执行一些任务,或者控制一些外部设备。

中断服务程序的编写需要根据具体的单片机和编程语言来进行相应的设置。

3. 定时器计数器的应用定时器计数器广泛应用于各种嵌入式系统中,最常见的应用包括定时中断、PWM输出、脉冲计数、定时控制等。

可以利用定时器计数器实现LED呼吸灯效果、马达控制、红外遥控编码等功能。

在工业自动化、通信设备、电子仪器等领域也有着广泛的应用。

飞思卡尔单片机中断(两篇)

引言概述飞思卡尔单片机中断是指在特定的条件下,单片机的运行被打断,转而执行特定的处理程序。

在飞思卡尔单片机的开发中,中断是非常重要的一部分,它可以提高系统的响应速度和实时性。

本文将详细介绍飞思卡尔单片机中断的相关知识。

正文内容一、中断的基本概念和原理1. 中断的定义:中断是指在特定的条件下,程序的执行被打断,转而执行事先定义好的处理程序。

2. 中断的分类:外部中断和内部中断。

外部中断是由外部设备引发的,例如按键、定时器等;内部中断是由单片机内部的某个事件引发的,例如指令执行完成、通信完成等。

3. 中断的触发方式:电平触发和边沿触发。

电平触发是指当外部信号保持一定电平时触发中断;边沿触发是指在信号的上升沿或下降沿触发中断。

二、飞思卡尔单片机中断的使用方法1. 中断的初始化:对中断控制寄存器进行设置,使能相应的中断源。

2. 中断的优先级设置:多个中断源同时触发时,可以通过设置优先级来确定执行顺序。

3. 中断服务程序的编写:根据不同的中断源,编写相应的中断服务程序,完成特定的处理。

4. 中断的开启和关闭:根据需要,可以在程序中开启或关闭特定的中断。

三、飞思卡尔单片机中断优化技巧1. 中断嵌套:可以在一个中断中触发另一个中断,提高系统的实时性和处理效率。

2. 临界区保护:在关键代码段加入关中断代码,保护临界区避免竞态条件的发生。

3. 中断延时处理:在某些特定情况下,需要延时处理中断,可以使用延时函数或软件延时方式实现。

四、飞思卡尔单片机中断的常见问题和解决方法1. 中断误触发问题:可能是由于外部干扰、软件错误等原因导致中断被误触发,可以通过加入滤波电路、改进软件设计等方式解决。

2. 中断处理时间过长问题:中断处理程序执行时间过长会导致系统响应变慢,可以通过优化中断程序、减少中断次数等方式解决。

3. 中断嵌套问题:如果中断嵌套层次太多,可能会导致系统死锁或无法预测的结果,可以通过合理设计中断嵌套层次、减少中断嵌套次数来解决。

单片机中的定时器和计数器

单片机中的定时器和计数器单片机作为一种嵌入式系统的核心部件,在各个领域都发挥着重要的作用。

其中,定时器和计数器作为单片机中常用的功能模块,被广泛应用于各种实际场景中。

本文将介绍单片机中的定时器和计数器的原理、使用方法以及在实际应用中的一些典型案例。

一、定时器的原理和使用方法定时器是单片机中常见的一个功能模块,它可以用来产生一定时间间隔的中断信号,以实现对时间的计量和控制。

定时器一般由一个计数器和一组控制寄存器组成。

具体来说,定时器根据计数器的累加值来判断时间是否到达设定的阈值,并在时间到达时产生中断信号。

在单片机中,定时器的使用方法如下:1. 设置定时器的工作模式:包括工作在定时模式还是计数模式,以及选择时钟源等。

2. 设置定时器的阈值:即需要计时的时间间隔。

3. 启动定时器:通过控制寄存器来启动定时器的运行。

4. 等待定时器中断:当定时器计数器的累加值达到设定的阈值时,会产生中断信号,可以通过中断服务函数来进行相应的处理。

二、计数器的原理和使用方法计数器是单片机中另一个常见的功能模块,它主要用于记录一个事件的发生次数。

计数器一般由一个计数寄存器和一组控制寄存器组成。

计数器可以通过外部信号的输入来触发计数,并且可以根据需要进行计数器的清零、暂停和启动操作。

在单片机中,计数器的使用方法如下:1. 设置计数器的工作模式:包括工作在计数上升沿触发模式还是计数下降沿触发模式,以及选择计数方向等。

2. 设置计数器的初始值:即计数器开始计数的初始值。

3. 启动计数器:通过控制寄存器来启动计数器的运行。

4. 根据需要进行清零、暂停和启动操作:可以通过控制寄存器来实现计数器的清零、暂停和启动操作。

三、定时器和计数器的应用案例1. 蜂鸣器定时器控制:通过定时器模块产生一定频率的方波信号,控制蜂鸣器的鸣叫时间和静默时间,实现声音的产生和控制。

2. LED呼吸灯控制:通过定时器模块和计数器模块配合使用,控制LED的亮度实现呼吸灯效果。

第二章 飞思卡尔单片机简介

2.2 HCS12X系列单片机概述

2.2.3 XGATE的基本特性

(5)互斥信号量 主处理器与XGATE 之间常用的通信方式是共享资源。 由于这两个内核可以独立异步的访问内存及片上外设,就会 产生数据完整性问题。为了保证共享数据的完整性,XGATE 集成了8 个硬件互斥信号量(Semaphore)。用户可以通过 硬件信号量来同步两个内核对共享数据的访问。信号量有3种 状态:释放、主处理器锁定和XGATE 锁定。每个内核在访问 共享资源前,应当首先锁定相应的信号量;在访问结束后应 当释放相应的信号量。

2.2 HCS12X系列单片机概述

S12X系列单片机与S12系列单片机的主要区别

2.2 HCS12X系列单片机概述

2.2.2 XGATE协处理器与主处理器的关系

在S12X系列中,中断控制器硬件产生的中断可以选择由XGATE 或者S12XD主处理器来处理。XGATE对于任何中断的处理都会减轻 主处理器的中断负荷,并且XGATE 完全有能力响应整个中断。

2.2 HCS12X系列单片机概述

2.2.4 典型S12X系列单片机简介

(4)MC9S12XS系列 MC9S12XS系列单片机是高性能MC9S12XE系列单片机 的经济性、高效性产品的补充,带有一套为汽车车身和乘客 舒适度应用而优化设计的改进型片上外围设备、存储器等模 块,可应用于汽车座椅控制模块、空调控制模块、各种车身 控制模块等的设计应用。

2.2 HCS12X系列单片机概述

2.2.4 典型S12X系列单片机简介

(1)MC9S12XA、MC9S12XB和MC9S12XD系列

这三个系列的单片机是以低成本和低功耗为目的设计的,具有良好的电磁兼 容性和高效的代码执行效率。MC9S12XA系列主要包括MC9S12XA256和 MC9S12XA512两种型号的单片机,其中MC9S12XA512包含外部总线接口EBI, 模块映像控制MMC功能,中断控制器INT,用于监控HCS12X CPU和XGATE总 线活动的调试模块DBG和背景调试模式BDM功能,具有2个A/D模块,每个为12 通道10位分辨率,具有4个独立暂停期限的定时器PIT,暂停期限可以在1~224总 线时钟周期之间选择,同时还有CRG模块,具有低噪声/低功耗皮尔斯(Pierce) 振荡器、PLL、COP监视器、实时中断、时钟监控器等功能。 MC9S12XB系列目前主要包括MC9S12XB128和MC9S12XB256两种型号的 单片机。它们的总线频率均为33 MHz,该系列单片机与MC9S12XD系列单片机 完全兼容,相比于S12XD系列而言,S12XB系列单片机精简了一些功能,并通过 降低总线速率来减少成本。

飞思卡尔9S12G系列单片机中文简介

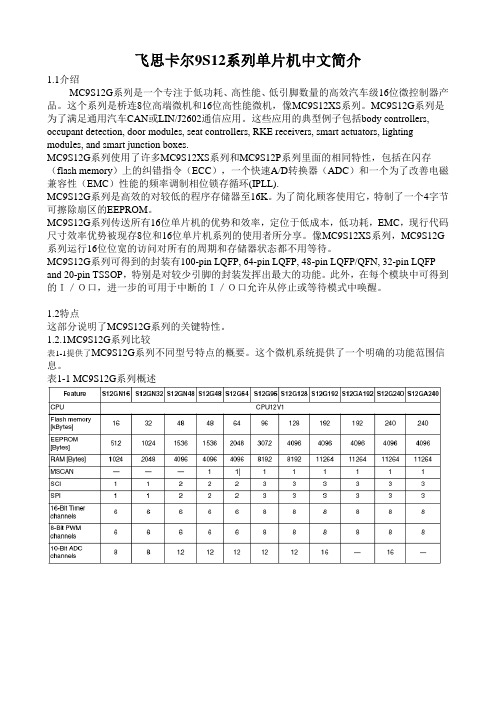

飞思卡尔9S12系列单片机中文简介1.1介绍MC9S12G系列是一个专注于低功耗、高性能、低引脚数量的高效汽车级16位微控制器产品。

这个系列是桥连8位高端微机和16位高性能微机,像MC9S12XS系列。

MC9S12G系列是为了满足通用汽车CAN或LIN/J2602通信应用。

这些应用的典型例子包括body controllers, occupant detection, door modules, seat controllers, RKE receivers, smart actuators, lighting modules, and smart junction boxes.MC9S12G系列使用了许多MC9S12XS系列和MC9S12P系列里面的相同特性,包括在闪存(flash memory)上的纠错指令(ECC),一个快速A/D转换器(ADC)和一个为了改善电磁兼容性(EMC)性能的频率调制相位锁存循环(IPLL).MC9S12G系列是高效的对较低的程序存储器至16K。

为了简化顾客使用它,特制了一个4字节可擦除扇区的EEPROM。

MC9S12G系列传送所有16位单片机的优势和效率,定位于低成本,低功耗,EMC,现行代码尺寸效率优势被现存8位和16位单片机系列的使用者所分享。

像MC9S12XS系列,MC9S12G 系列运行16位位宽的访问对所有的周期和存储器状态都不用等待。

MC9S12G系列可得到的封装有100-pin LQFP, 64-pin LQFP, 48-pin LQFP/QFN, 32-pin LQFP and 20-pin TSSOP,特别是对较少引脚的封装发挥出最大的功能。

此外,在每个模块中可得到的I/O口,进一步的可用于中断的I/O口允许从停止或等待模式中唤醒。

1.2特点这部分说明了MC9S12G系列的关键特性。

1.2.1MC9S12G系列比较表1-1提供了MC9S12G系列不同型号特点的概要。

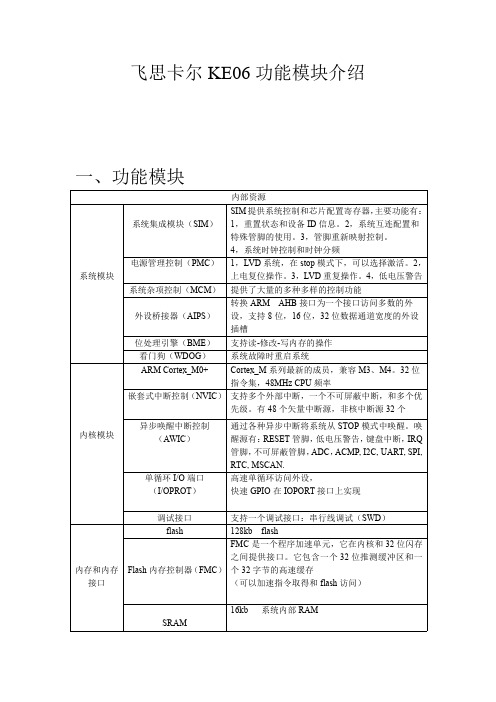

飞思卡尔KE06功能模块介绍

上电复位操作。3,LVD 重复操作。4,低电压警告

系统杂项控制(MCM) 提供了大量的多种多样的控制功能

外设桥接器(AIPS)

转换 ARM AHB 接口为一个接口访问多数的外 设,支持 8 位,16 位,32 位数据通道宽度的外设

插槽

位处理引擎(BME) 支持读-修改-写内存的操作

看门狗(WDOG) 系统故障时重启系统

4低电压警告系统杂项控制mcm提供了大量的多种多样的控制功能转换armahb接口为一个接口访问多数的外外设桥接器aips设支持位16位32位数据通道宽度的外设插槽位处理引擎bme支持读修改写内存的操作看门狗wdog系统故障时重启系统armcortexm0cortexm系列最新的成员兼容m3m432指令集48mhzcpu频率嵌套式中断控制nvic支持多个外部中断一个不可屏蔽中断和多个优48个矢量中断源非核中断源32异步唤醒中断控制通过各种异步中断将系统从stop模式中唤醒

ARM Cortex_M0+

Cortex_M 系列最新的成员,兼容 M3、M4。32 位 指令集,48MHz CPU 频率

嵌套式中断控制(NVIC) 支持多个外部中断,一个不可屏蔽中断,和多个优

先级。有 48 个矢量中断源,非核中断源 32 个

异步唤醒中断控制 (AWIC)

单循环 I/O 端口 (I/OPROT)

通过各种异步中断将系统从 STOP 模式中唤醒。唤 醒源有:RESET 管脚,低电压警告,键盘中断,IRQ 管脚,不可屏蔽管脚,ADC,ACMP, I2C, UART, SPI, RTC, MSCAN. 高速单循环访问外设, 快速 GPIO 在 IOPORT 接口上实现

内存和内存 接口

调试接口

支持一个调试接口:串行线调试(SWD)

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

基准计时器的核心仍然是一个16 位的可编程计数器,其时钟源来自一个预分频器。

该计时器可以被应用于多个方面,包括在对输入波形进行测量的同时产生一个输出波形。

波形的脉宽可以在几微秒到数秒的范围内变化。

增强型定时器模块(ECT)的结构框图如下,ECT功能相当于高速的I/O口,由一个4位预分频器、一个16位自由运行计数器,8个16位IC/OC通道,2个16位脉冲累加器以及一个16位模数递减计数器组成。

ECT实际上是一个16位的可编程计数器,它的基本时钟频率可以通过预分频器设置,用于产生波形输出,测量输入波形,统计脉冲个数,可以作为定时中断功能和独立时钟基准。

2、运行模式

停止:由于时钟停止,计时器和计数器均关闭。

冻结:计时器和计数器均保持运行,直到TSCR($06)的TSFRZ 位被置1。

等待:计数器保持运行,直到TSCR($06)的TSWAI 位被置1。

正常:计时器和计数器均保持运行,直到TSCR($06)的TEN 位和MCCTL($26)的MCEN 位被分别清0。

IC 通道组由四个标准的缓冲通道IC0-IC3 和四个非缓冲通道IC4-IC7 组成,两部分的基本功能都是捕捉外部事件发生的时刻,但是缓冲通道除了IC/OC 寄存器TCn 外,还设有保持寄存器TCnH,此外还在入口设置了延迟计数器,用来提高抗干扰能力。

非缓冲通道没有保持寄存器,入口也没有延迟计数器,但每个通道入口设置了一个 2 输入端的多路器,事件触发信号可以是来自本通道的输入引脚PORTn,也可以是来自其关联通道PORT(n-4)的延迟计数器输出,使用更加灵活。

当延迟功能有效时,输入引脚检测到一个有效的边沿后,延迟计数器开始对P 时钟(模块时钟)进行计数,当到达设定的计数值后,延迟计数器在其输出端有条件地产生一个脉冲,这个条件就是延迟前后的引脚电平相反。

这样可以避免对窄输入脉冲做出反应。

延迟计数结束后,计数器自动清除。

输入信号两个有效边沿之间的持续时间必须大于设定的延迟时间。

在ECT 中,所有IC 通道均设置了覆盖保护功能,可以通过寄存器ICOVW设置是否允许某个通道用新的捕捉结果覆盖上一个结果。

对于缓冲的IC 通道PT0-PT3,还具有锁存与队列两种工作方式。

在锁存方式下,每个有效的引脚事件只将自由定时器的值放入捕捉寄存器TCn,而TCn 到保持寄存器TCnH 的传送必须依赖递减模数计数器回0 或者其他强制锁存命令才能实现,这时IC 的工作情形与第 6 章的TIM 模块相似。

在队列方式下(图7-2),TCn 与TCnH 形成了一个类似先进先出的队列,每个捕捉结果从TCn 进入,然后随着下一个捕捉结果的到来移入TCnH,程序可以从TCnH 取得结果,然而这个队列是开放的,即程序也可以直接从TCn 取得捕捉结果。

队列方式为CPU 提供了充分的响应时间。

由于PAC0-3 与IC0-3 共享相同的引脚,而且共享入口的逻辑,因此在两种方式下,PAI 与IC 都可以同时工作,对同一引脚进行记录,前者记录脉冲或者边沿的数量,后者记录具体的时刻。

模数递减计数器

16 位递减模数计数器(MDC)可以用作时钟基准,产生周期性的中断请求,也可用于将IC 寄存器和脉冲累加器的值锁存到各自的保持寄存器中。

锁存动作可以通过程序设定为周期性的或一次性的。

MDC 的时钟频率可通过独立的定标器设定,内部设有定时常数寄存器,可以实现自动重装载,但MDC 的常数寄存器与MDC 计数器使用相同的地址,加载时通过特殊的时序实现。

每当MDC 回0 时,将在给定的时间段内控制贮和PAI 寄存器的内容向各自的缓冲寄存器传输。

反映了MDC 在IC、PAI 系统中的作用。

脉冲累加器由4 个8 位的通道PAC0-PAC3 组成,可以通过级联形成两个16 位通道PACA、PACB,它可以统计输入引脚上出现的有效边沿的数量,也可以统计有效电平出现的累计时间。

各个通道的8 位保持寄存器是与4 个缓冲IC 通道相关联的,它们共享边沿检测与延迟电路。

当IC 工作在两种不同的队列方式时,PAC 保持寄存器也处于不同的工作状态,在锁存方式下,PCnH 的加载依靠MDC 计数器或者强制命令实现,而在队列方式下,则依靠IC 通道的TCnH 读命令。

可见在ECT 模块下,IC 与PAI 的工作联系更加紧密。

此外,脉冲累加器还有饱和记忆功能,当8 位的脉冲累加器计数超过$FF 后记忆保持,而不回滚到0,这时,计数值$FF 意味着计数已经达到或超过255,如不需要,该功能可以关闭。

这可以用来监视某个通道的计数值是否已经达到预定的目标值。

值得注意的是,PACl、PAC0 级联后,输入引脚为PT0,而PAC3、PAC2 级联后,输入引脚并不是PT2,而是PT7,这样可以与那些无ECT 的MCU 保持一致性。