单片机实验--键盘扫描

实验五 键盘扫描实验 实验报告

键盘扫描实验实验报告一、实验目的1. 掌握线反转法键盘扫描原理。

2. 了解单片机的输入和输出过程,理解单片机的数据采集过程。

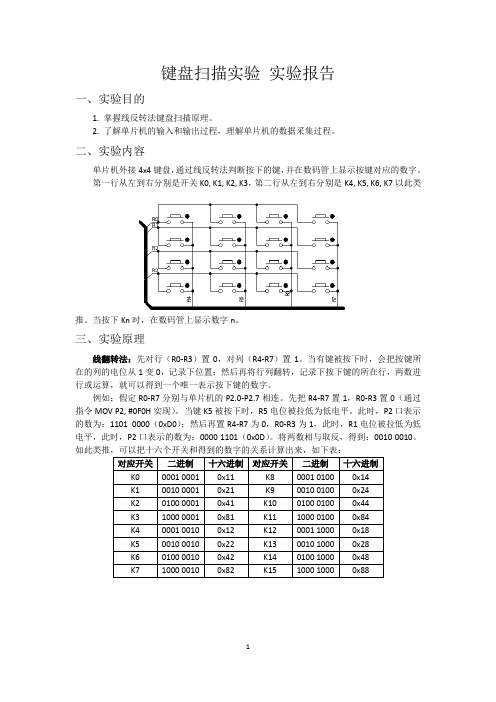

二、实验内容单片机外接4x4键盘,通过线反转法判断按下的键,并在数码管上显示按键对应的数字。

第一行从左到右分别是开关K0, K1, K2, K3,第二行从左到右分别是K4, K5, K6, K7以此类推。

当按下Kn时,在数码管上显示数字n。

三、实验原理线翻转法:先对行(R0-R3)置0,对列(R4-R7)置1。

当有键被按下时,会把按键所在的列的电位从1变0,记录下位置;然后再将行列翻转,记录下按下键的所在行,两数进行或运算,就可以得到一个唯一表示按下键的数字。

例如:假定R0-R7分别与单片机的P2.0-P2.7相连。

先把R4-R7置1,R0-R3置0(通过指令MOV P2, #0F0H实现)。

当键K5被按下时,R5电位被拉低为低电平。

此时,P2口表示的数为:1101 0000(0xD0);然后再置R4-R7为0,R0-R3为1,此时,R1电位被拉低为低电平,此时,P2口表示的数为:0000 1101(0x0D)。

将两数相与取反,得到:0010 0010。

四、实验过程1. 连接好单片机及其外围设备电路2. 编写汇编程序ORG LJMP KeyLJMP K7: CJNE R2, #82H, K8ORG 0100H MOV P0, #0F8H Init: CLR P1.3 LJMP KeyMOV P0, #0C0H K8: CJNE R2, #14H, K9 Key: MOV P2, #0F0H MOV P0, #080HMOV A, P2 LJMP KeyMOV R1, A K9: CJNE R2, #24H, K10MOV P2, #0FH MOV P0, #090HMOV A, P2 LJMP KeyORL A, R1 K10: CJNE R2, #44H, K11CPL A MOV P0, #088HMOV R2, A LJMP KeyJNZ KeyPro K11: CJNE R2, #84H, K12LJMP Key MOV P0, #083H KeyPro: CJNE R2, #11H, K1 LJMP KeyMOV P0, #0C0H K12: CJNE R2, #18H, K13LJMP Key MOV P0, #0C6H K1: CJNE R2, #21H, K2 LJMP KeyMOV P0, #0F9H K13: CJNE R2, #28H, K14LJMP Key MOV P0, #0A1H K2: CJNE R2, #41H, K3 LJMP KeyMOV P0, #0A4H K14: CJNE R2, #48H, K15LJMP Key MOV P0, #086H K3: CJNE R2, #81H, K4 LJMP KeyMOV P0, #0B0H K15: CJNE R2, #88H, K16LJMP Key MOV P0, #08EH K4: CJNE R2, #12H, K5 LJMP KeyMOV P0, #099H K16: LJMP KeyLJMP Key ENDK5: CJNE R2, #22H, K6MOV P0, #092HLJMP KeyK6: CJNE R2, #42H, K7MOV P0, #082H五、实验结果1. 当按下开关Kn时,数码管能够显示对应的数字。

实验八 键盘扫描实验

实验八键盘扫描实验一、实验目的1. 掌握中断键盘扫描编程方法。

2. 掌握LED动态显示方法。

二、实验原理及实验内容1. 实验原理无论是单片机控制系统还是单片机测量系统,都需要一个人机对话装置,这种人机对话装置通常采用键盘和显示器。

键盘是单片机应用系统中人机对话常用的输入装置,而显示器是单片机应用系统人机对话中的常用输出装置。

键盘是由若干个按键开关组成,键的多少根据单片机应用系统的用途而定。

键盘由许多键组成,而每个键相当于一个机械开关触点,当键按下时,触点闭合,当键松开时,触点断开。

单片机接收到按键的触点信号后作相应的功能处理。

因此对于单片机系统来说键盘接口信号是输入信号。

单片机的键盘接口分为独立式和矩阵式。

独立式键盘的每个按键都有一个信号线与单片机电路相连,所有按键有一个公共地或公共正端,每个键相互独立互不影响。

如图7-7所示,当按下键1时,无论其它键是否按下,键1的信号线就由1变0;当松开键1时,无论其它键是否按下,键1的信号线就由0变1。

矩阵式键盘的按键触点接于由行、列母线构成的矩阵电路的交叉处,每当一个按键按下时通过该键将相应的行、列母线连通。

若在行、列母线中把行母线逐行置0(一种扫描方式),那么列母线就用来作信号输入线。

矩阵式键盘原理图如图7-8所示。

图7-7 独立式按键原理图图7-8 矩阵式按键原理图针对以上两大类键盘工作方式,单片机又有三种键盘扫描方式:查询方式;定时扫描方式和中断扫描方式。

查询方式是指在程序中用一段专门的扫描和读按键程序不停查询有无按键按下,确定键值。

这种方式电路简单,但需要占用单片机的机器时间。

定时扫描方式是指利用单片机内的定时器来产生定时中断,然后在定时中断的服务程序中扫描,检查有无按键按下,确定键值。

这种方式的电路也比较简单,不占用单片机的机器时间,但需要占用一个定时器,同时定时的时间不能过长,否则可能检测不到相应得按键。

中断扫描方式是指当有键按下时由相应的硬件电路产生中断信号,单片机在中断服务程序中扫描,检查有无按键按下,确定键值。

实验四 键盘扫描与数码管显示实验

院别:电子信息学院课程名称:微处理器实验

班级:通信11A姓名:xxxx学号:

实验名称:键盘扫描与数码管显示实验实验时间:2013年10月21日

成绩:教师签名:批改时间:

一、实验原理与目的

原理:

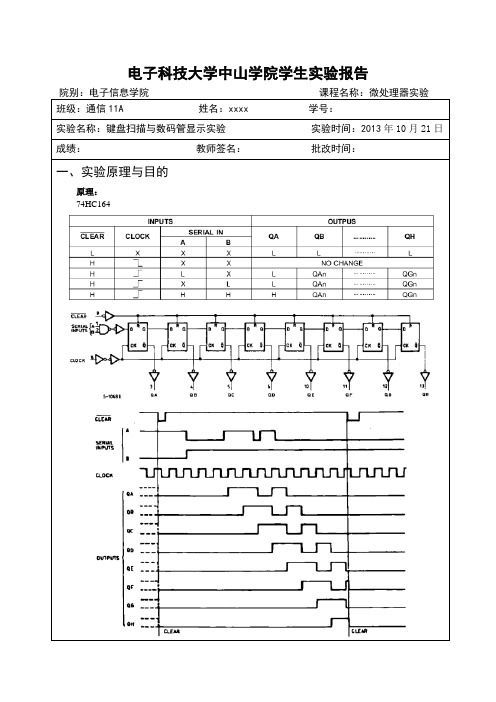

74HC164

74HC165

目的:

1、学会利用单片机进行键盘扫描行LED点阵的扫描显示;

2、学会利用单片机实现数码管显示。

二、实验仪器

1、PC机一台

2、DP-51PRO单片机综合仿真实验仪一台

三、实验内容与分析

1、编写一段程序,此程序的目的是通过单片机的P1口控制扫描,用C5区的74HC164控制显示输出,使C3区的8×8LED点阵显示一个“X”。

CLKEQUP3.2

DINAEQUP3.3

DINBEQUP3.4

CLEAREQUP3.5

ORG0000H

AJMPMAIN

ORG 0100H

MAIN:

MOVSP,#70H

MOV50H,#07EH

MOV51H,#0BDH

MOV52H,#0DBH

MOV53H,#0E7H

MOV54H,#0E7H

MOV55H,#0DBH

MOV56H,#0BDH

MOV57H,#07EH

PLEQUP3.0

CLK1EQUP3.1

CLK2EQUP3.2

SEREQUP3.3

Q7EQUP3.5

ORG0000H

LJMPMAIN

ORG0100H

MAIN:MOVSP,#60H;设置堆栈

MOVR4,#00;延时

DJNZR4,$

MOVA,#0;变量清零

SETBQ7;Q=1,端口设为输出状态

键盘扫描程序实验报告

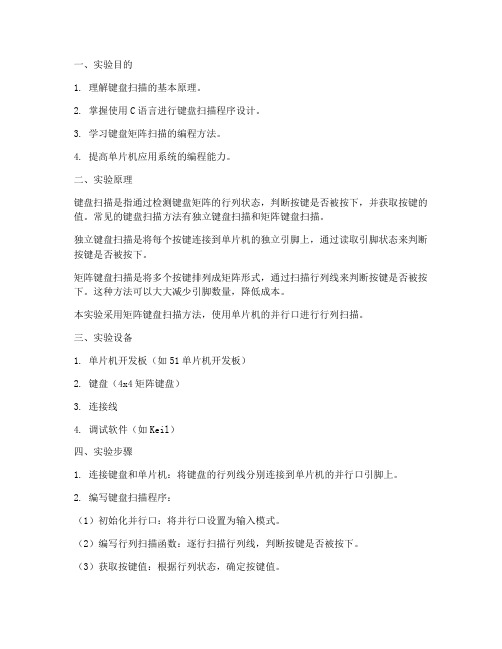

一、实验目的1. 理解键盘扫描的基本原理。

2. 掌握使用C语言进行键盘扫描程序设计。

3. 学习键盘矩阵扫描的编程方法。

4. 提高单片机应用系统的编程能力。

二、实验原理键盘扫描是指通过检测键盘矩阵的行列状态,判断按键是否被按下,并获取按键的值。

常见的键盘扫描方法有独立键盘扫描和矩阵键盘扫描。

独立键盘扫描是将每个按键连接到单片机的独立引脚上,通过读取引脚状态来判断按键是否被按下。

矩阵键盘扫描是将多个按键排列成矩阵形式,通过扫描行列线来判断按键是否被按下。

这种方法可以大大减少引脚数量,降低成本。

本实验采用矩阵键盘扫描方法,使用单片机的并行口进行行列扫描。

三、实验设备1. 单片机开发板(如51单片机开发板)2. 键盘(4x4矩阵键盘)3. 连接线4. 调试软件(如Keil)四、实验步骤1. 连接键盘和单片机:将键盘的行列线分别连接到单片机的并行口引脚上。

2. 编写键盘扫描程序:(1)初始化并行口:将并行口设置为输入模式。

(2)编写行列扫描函数:逐行扫描行列线,判断按键是否被按下。

(3)获取按键值:根据行列状态,确定按键值。

(4)主函数:调用行列扫描函数,读取按键值,并根据按键值执行相应的操作。

3. 调试程序:将程序下载到单片机,观察键盘扫描效果。

五、实验程序```c#include <reg51.h>#define ROW P2#define COL P3void delay(unsigned int ms) {unsigned int i, j;for (i = 0; i < ms; i++)for (j = 0; j < 123; j++);}void scan_key() {unsigned char key_val = 0xFF;ROW = 0xFF; // 初始化行delay(1); // 延时消抖key_val = ROW & COL; // 获取按键值ROW = 0x00; // 初始化行delay(1); // 延时消抖key_val = ROW & COL; // 获取按键值ROW = 0x00; // 初始化行delay(1); // 延时消抖key_val = ROW & COL; // 获取按键值ROW = 0x00; // 初始化行delay(1); // 延时消抖key_val = ROW & COL; // 获取按键值}void main() {while (1) {scan_key();if (key_val != 0xFF) {// 执行按键对应的操作}}}```六、实验结果与分析1. 实验结果:程序下载到单片机后,按键按下时,单片机能够正确读取按键值。

实验四 单片机按键扫描编程

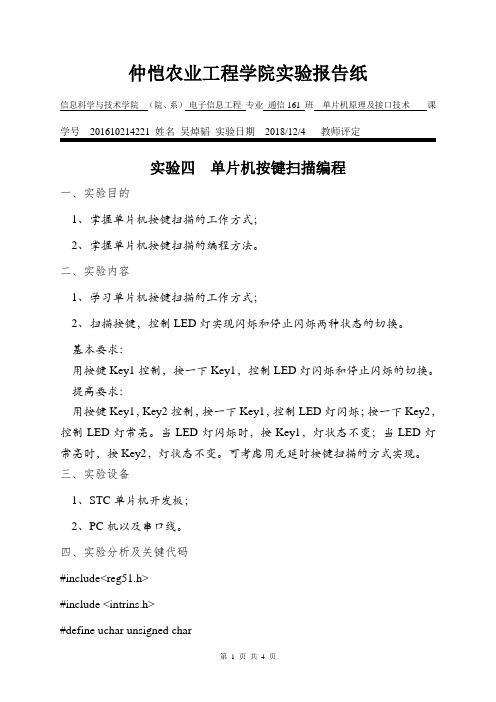

仲恺农业工程学院实验报告纸信息科学与技术学院(院、系)电子信息工程专业通信161 班单片机原理及接口技术课实验四单片机按键扫描编程一、实验目的1、掌握单片机按键扫描的工作方式;2、掌握单片机按键扫描的编程方法。

二、实验内容1、学习单片机按键扫描的工作方式;2、扫描按键,控制LED灯实现闪烁和停止闪烁两种状态的切换。

基本要求:用按键Key1控制,按一下Key1,控制LED灯闪烁和停止闪烁的切换。

提高要求:用按键Key1,Key2控制,按一下Key1,控制LED灯闪烁;按一下Key2,控制LED灯常亮。

当LED灯闪烁时,按Key1,灯状态不变;当LED灯常亮时,按Key2,灯状态不变。

可考虑用无延时按键扫描的方式实现。

三、实验设备1、STC单片机开发板;2、PC机以及串口线。

四、实验分析及关键代码#include<reg51.h>#include <intrins.h>#define uchar unsigned charuchar counter=0;sbit KEY1=P2^6; //按下,值为0sbit LEDG=P2^5;void delay_10ms(void) //10ms延时函数{unsigned char i,j;for(j=0;j<10;j++){for (i=0;i<250;i++)_nop_();}}void timer()interrupt 1 using 1 //定时器1方式1,采用中断方式{TH0=(65536-50000)/256;TL0=(65536-50000)%256; //重置初值counter++;if(counter==10){LEDG=!LEDG; //LEDG取反改变灯的状态counter=0;}}void main(){TMOD=0X21;EA=1;ET0=1;TR0=1; //启动T/C0开始定时while(1){if(!KEY1){ delay_10ms();if(!KEY1){while(!KEY1);delay_10ms();TR0=!TR0; //执行按键任务LEDG=0;}}}实验分析:主函数分析:1.计时器初始化 2.进入while循环延时按键扫描,如果KEY1=0(按下),进行按键延时,再判断KEY1是否=0,=0再进行按键延时,然后定时器启动取反(既每次按下定时器依次启动或中断),使LEDG 灯定义亮。

单片机实验--键盘扫描

实验4 键盘实验一、实验目的:1.掌握8255A编程原理。

2.了解键盘电路的工作原理。

3.掌握键盘接口电路的编程方法。

二、实验设备:CPU挂箱、8031CPU模块三、实验原理:1.识别键的闭合,通常采用行扫描法和行反转法。

行扫描法是使键盘上某一行线为低电平,而其余行接高电平,然后读取列值,如所读列值中某位为低电平,表明有键按下,否则扫描下一行,直到扫完所有行。

本实验例程采用的是行反转法。

行反转法识别键闭合时,要将行线接一并行口,先让它工作于输出方式,将列线也接到一个并行口,先让它工作于输入方式,程序使CPU通过输出端口往各行线上全部送低电平,然后读入列线值,如此时有某键被按下,则必定会使某一列线值为0。

然后,程序对两个并行端口进行方式设置,使行线工作于输入方式,列线工作于输出方式,并将刚才读得的列线值从列线所接的并行端口输出,再读取行线上的输入值,那么,在闭合键所在的行线上的值必定为0。

这样,当一个键被按下时,必定可以读得一对唯一的行线值和列线值。

2.程序设计时,要学会灵活地对8255A的各端口进行方式设置。

3.程序设计时,可将各键对应的键值(行线值、列线值)放在一个表中,将要显示的0~F字符放在另一个表中,通过查表来确定按下的是哪一个键并正确显示出来。

实验题目利用实验箱上的8255A可编程并行接口芯片和矩阵键盘,编写程序,做到在键盘上每按一个数字键(0~F),用发光二极管将该代码显示出来。

四、实验步骤:将键盘RL10~RL17接8255A的PB0~PB7;KA10~KA12接8255A的PA0~PA2;PC0~PC7接发光二极管的L1~L8;8255A芯片的片选信号8255CS接CS0。

五、实验电路:六、程序框图7.程序清单八、附:8251/8255扩展模块该模块由8251可编程串行口电路和8255可编程并行口电路两部分组成,其电源、数据总线、地址总线和片选信号均由接口挂箱上的接口插座提供。

一、8251可编程串行口电路(1)8251可编程串行接口芯片引脚及功能8251A是通用同步/异步收发器USART,适合作异步起止式数据格式和同步面向字符数据格式的接口,其功能很强。

单片机键盘检测控制实验原理

单片机键盘检测与控制实验是嵌入式系统和数字电子技术领域的一个常见实验,通过该实验,可以学习到单片机输入输出的基本原理、数字信号的处理方法以及键盘输入的检测和控制技术。

以下是这个实验的基本原理和步骤:**实验目的:**1. 了解单片机的输入输出原理。

2. 掌握键盘输入的检测原理。

3. 实现对键盘输入的基本控制。

**实验原理:**1. **单片机输入输出原理:** 单片机通常具有一些通用输入输出引脚,用于与外部设备进行信息交互。

这些引脚可以配置为输入或输出模式。

在实验中,我们主要使用单片机的输入引脚,将键盘连接到这些引脚上,以便单片机可以读取键盘的输入信号。

2. **键盘输入的检测原理:** 键盘通常是由多个按键组成的矩阵结构。

每个按键都与键盘的一行和一列相连。

通过扫描键盘的行和列,可以检测到哪个按键被按下。

具体步骤如下:- **行扫描:** 单片机首先选择一行,将该行置为低电平,同时检测每一列的状态。

如果某一列为低电平,说明该列对应的按键被按下。

- **列扫描:** 单片机依次选择每一列,将该列置为低电平,同时检测每一行的状态。

如果某一行为低电平,说明该行对应的按键被按下。

3. **实现对键盘输入的基本控制:** 一旦检测到按键按下的信号,单片机可以采取相应的措施,例如在数码管上显示按下的键值、驱动LED灯等。

**实验步骤:**1. **连接键盘:** 将键盘的行和列引脚连接到单片机的相应引脚上。

2. **编写程序:** 使用编程语言(如C语言或汇编语言)编写程序,实现键盘输入的检测和控制逻辑。

3. **下载程序:** 将编写好的程序下载到单片机中。

4. **运行实验:** 接通电源,运行实验,观察键盘输入的检测和相应控制的效果。

**实验注意事项:**1. 确保键盘连接正确,行和列的对应关系准确。

2. 程序中的扫描算法要正确,确保能够准确检测到键盘的按键状态。

3. 在程序中加入防抖动处理,防止由于按键机械弹性导致的多次触发。

单片机实验--键盘扫描

实验4 键盘实验一、实验目的:1.掌握8255A编程原理。

2.了解键盘电路的工作原理。

3.掌握键盘接口电路的编程方法。

二、实验设备:CPU挂箱、8031CPU模块三、实验原理:1.识别键的闭合,通常采用行扫描法和行反转法。

行扫描法是使键盘上某一行线为低电平,而其余行接高电平,然后读取列值,如所读列值中某位为低电平,表明有键按下,否则扫描下一行,直到扫完所有行。

本实验例程采用的是行反转法。

行反转法识别键闭合时,要将行线接一并行口,先让它工作于输出方式,将列线也接到一个并行口,先让它工作于输入方式,程序使CPU通过输出端口往各行线上全部送低电平,然后读入列线值,如此时有某键被按下,则必定会使某一列线值为0。

然后,程序对两个并行端口进行方式设置,使行线工作于输入方式,列线工作于输出方式,并将刚才读得的列线值从列线所接的并行端口输出,再读取行线上的输入值,那么,在闭合键所在的行线上的值必定为0。

这样,当一个键被按下时,必定可以读得一对唯一的行线值和列线值。

2.程序设计时,要学会灵活地对8255A的各端口进行方式设置。

3.程序设计时,可将各键对应的键值(行线值、列线值)放在一个表中,将要显示的0~F字符放在另一个表中,通过查表来确定按下的是哪一个键并正确显示出来。

实验题目利用实验箱上的8255A可编程并行接口芯片和矩阵键盘,编写程序,做到在键盘上每按一个数字键(0~F),用发光二极管将该代码显示出来。

四、实验步骤:将键盘RL10~RL17接8255A的PB0~PB7;KA10~KA12接8255A的PA0~PA2;PC0~PC7接发光二极管的L1~L8;8255A芯片的片选信号8255CS接CS0。

五、实验电路:六、程序框图7.程序清单八、附:8251/8255扩展模块该模块由8251可编程串行口电路和8255可编程并行口电路两部分组成,其电源、数据总线、地址总线和片选信号均由接口挂箱上的接口插座提供。

一、8251可编程串行口电路(1)8251可编程串行接口芯片引脚及功能8251A是通用同步/异步收发器USART,适合作异步起止式数据格式和同步面向字符数据格式的接口,其功能很强。

键盘扫描显示实验报告

一、实验目的1. 理解键盘扫描的基本原理,掌握键盘扫描的方法。

2. 掌握数码管显示的基本原理,实现键盘扫描信息的实时显示。

3. 熟悉8255并行接口芯片在键盘扫描和数码管显示中的应用。

二、实验原理1. 键盘扫描原理:键盘扫描是指通过硬件电路对键盘按键进行检测,并将按键信息转换为可识别的数字信号的过程。

本实验采用行列式键盘,通过扫描键盘的行线和列线,判断按键是否被按下。

2. 数码管显示原理:数码管是一种用来显示数字和字符的显示器,由多个发光二极管(LED)组成。

本实验采用七段数码管,通过控制各个段(A、B、C、D、E、F、G)的亮灭,显示相应的数字或字符。

3. 8255并行接口芯片:8255是一款通用的并行接口芯片,具有三个8位并行I/O口(PA、PB、PC),可用于键盘扫描和数码管显示的控制。

三、实验设备1. 实验平台:PC机、8255并行接口芯片、行列式键盘、七段数码管、面包板、导线等。

2. 软件环境:汇编语言编程软件、仿真软件等。

四、实验步骤1. 硬件连接:将8255并行接口芯片、行列式键盘、七段数码管连接到实验平台上,按照电路图进行连线。

2. 编写程序:使用汇编语言编写键盘扫描和数码管显示的程序。

(1)初始化8255并行接口芯片:设置PA口为输出端口,PB口为输出端口,PC口为输入端口。

(2)扫描键盘:通过PC口读取键盘的行线状态,判断是否有按键被按下。

若检测到按键被按下,读取对应的列线状态,确定按键的位置。

(3)数码管显示:根据按键的位置,控制数码管的段(A、B、C、D、E、F、G)的亮灭,显示相应的数字。

3. 仿真调试:使用仿真软件对程序进行调试,确保程序能够正确扫描键盘和显示数字。

五、实验结果与分析1. 实验结果:成功实现了键盘扫描和数码管显示的功能。

当按下键盘上的任意按键时,数码管上会显示对应的数字。

2. 分析:(1)键盘扫描部分:通过读取PC口的行线状态,判断是否有按键被按下。

当检测到按键被按下时,读取PB口的列线状态,确定按键的位置。

实验五 键盘扫描实验 实验报告

实验五键盘扫描实验实验报告一、实验目的本次实验的主要目的是深入了解键盘扫描的工作原理,掌握键盘扫描的编程实现方法,以及提高对硬件接口和软件编程的综合应用能力。

二、实验设备1、计算机一台2、实验开发板一套3、下载线一根4、键盘一个三、实验原理键盘扫描的基本原理是通过逐行或逐列扫描键盘矩阵,检测按键的按下和释放状态。

常见的键盘扫描方式有行列式扫描和编码式扫描。

在行列式扫描中,将键盘的行线和列线分别连接到微控制器的输入输出端口。

通过依次将行线设置为低电平,同时读取列线的状态,来判断是否有按键按下。

如果在某一行被设置为低电平时,对应的列线检测到低电平,则表示该行和该列交叉处的按键被按下。

编码式扫描则是利用专门的编码芯片对键盘进行扫描和编码,微控制器只需读取编码芯片输出的按键编码即可确定按键的状态。

四、实验步骤1、硬件连接将实验开发板与计算机通过下载线连接好。

将键盘连接到实验开发板的相应接口。

2、软件编程选择合适的编程语言和开发环境,如 C 语言和 Keil 开发环境。

定义键盘的行线和列线所对应的端口。

编写扫描函数,实现键盘扫描的逻辑。

在主函数中调用扫描函数,并根据返回的按键值进行相应的处理,如显示按键字符或执行特定的操作。

3、编译下载对编写好的程序进行编译,检查是否有语法错误。

将编译生成的可执行文件下载到实验开发板中。

4、实验测试按下键盘上的不同按键,观察实验开发板上的显示或输出结果是否正确。

检查是否能够准确检测到按键的按下和释放,以及是否存在按键抖动等问题。

五、实验结果与分析1、实验结果在实验过程中,成功实现了对键盘的扫描,并能够准确检测到按键的按下。

按下不同的按键时,实验开发板能够正确显示相应的按键字符或执行预定的操作。

2、结果分析对于按键的准确检测,说明编写的扫描函数逻辑正确,能够有效地识别键盘矩阵中的按键状态变化。

在检测到按键按下时,没有出现误判或漏判的情况,表明行线和列线的设置以及读取操作正常。

单片机键盘扫描实验

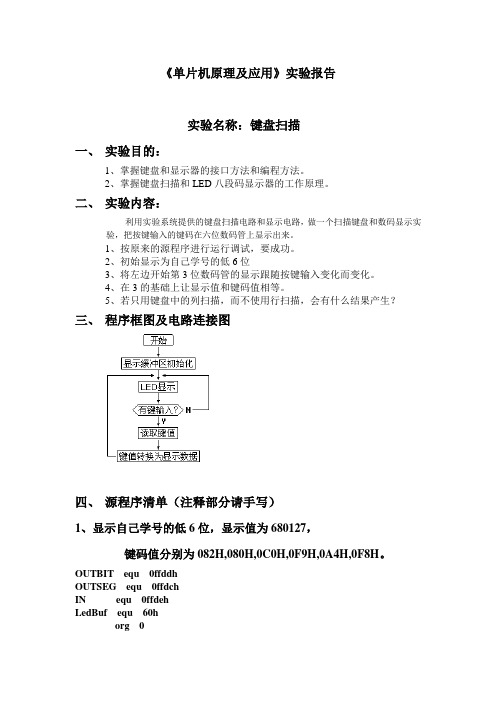

《单片机原理及应用》实验报告实验名称:键盘扫描一、实验目的:1、掌握键盘和显示器的接口方法和编程方法。

2、掌握键盘扫描和LED八段码显示器的工作原理。

二、实验内容:利用实验系统提供的键盘扫描电路和显示电路,做一个扫描键盘和数码显示实验,把按键输入的键码在六位数码管上显示出来。

1、按原来的源程序进行运行调试,要成功。

2、初始显示为自己学号的低6位3、将左边开始第3位数码管的显示跟随按键输入变化而变化。

4、在3的基础上让显示值和键码值相等。

5、若只用键盘中的列扫描,而不使用行扫描,会有什么结果产生?三、程序框图及电路连接图四、源程序清单(注释部分请手写)1、显示自己学号的低6位,显示值为680127,键码值分别为082H,080H,0C0H,0F9H,0A4H,0F8H。

OUTBIT equ 0ffddhOUTSEG equ 0ffdchIN equ 0ffdehLedBuf equ 60horg 0Start:mov sp,#40hmov LedBuf+0,#082hmov LedBuf+1,#080hmov LedBuf+2,#0c0hmov LedBuf+3,#0f9hmov LedBuf+4,#0a4hmov LedBuf+5,#0f8hMLoop:call DisplayLEDcall ScanKeyjb acc.5,MLoopjb acc.4,MLoopanl a,#00001111bmov dptr, #keytable (2)movc a, @a+dptrmov dptr,#LedMapmovc a,@a+dptrmov LedBuf+5,a (1)sjmp MLoopDelay:mov r7,#0DelayLoop:djnz r7,DelayLoopdjnz r6,DelayLoopretDisplayLED:mov r0,#LedBufmov r1,#6mov r2,#20hLoop:mov dptr,#OUTBITmov a,#0movx @dptr,amov a,@r0mov dptr,#OUTSEGmovx @dptr,amov dptr,#OUTBITmov a,r2movx @dptr,amov r6,#1call Delaymov a,r2rr amov r2,ainc r0djnz r1,LoopretScanKey:setb RS1mov r2,#0fehmov r3,#08hmov r0,#00hLoopS: mov r1,#Low(OUTBIT)mov a,r2movx @r1,arl amov r2,ainc r1movx a,@r1cpl aanl a,#0fhjnz Scan (3)inc r0djnz r3,LoopSReTKey3:mov a,#20hTKey3: mov r2,aclr amov r1,#Low(OUTBIT)movx @r1,amov a,r2clr RS1retScan1: mov a, r0sjmp TKey3Scan:cpl ajb acc.0,TKey0mov a,#00hsjmp EndLoopTKey0: jb acc.1,TKey1mov a,#08hsjmp EndLoopTKey1: jb acc.2,TKey2mov a,#10hsjmp EndLoopTKey2: jb acc.3,ReTKey3mov a,#18hEndLoop:add a,r0sjmp TKey3LedMap:db 0c0h,0f9h,0a4h,0b0h,099h,092h,082h,0f8hdb 080h,090h,088h,083h,0c6h,0a1h,086h,08eh KeyTable:db 07h,04h,08h,05h,09h,06h,0ah,0bhdb 01h,00h,02h,0fh,03h,0eh,0ch,0dhend2、在原有的程序上修改:把(1)处的mov LedBuf+5,a改为mov LedBuf+2,a3、在2的基础上让显示值和键码值相等:把(2)处的mov dptr, #keytable改为mov dptr, # LedMap 然后把后两行删除4、只用键盘中的列扫描,而不使用行扫描把(3)处的jnz Scan改为jnz Scan1。

【单片机实验七】键盘扫描及显示设计实验

程序及注解见附件CLEAR: MOV DPTR, #B_8255 ;清屏 MOV A,#00H MOVX @DPTR,A RET DIS: PUSH ACC ;显示子程序 PUSH 00H PUSH 03H MOV R0,#50H ;显示缓冲首地址 MOV R3,#0DFH ;显示扫描值AGAIN: MOV A,#0FFH ;关闭显示 MOV DPTR,#A_8255 MOVX @DPTR,A MOV A,@R0 MOV DPTR,#DSEGS ;数码管段表地址 MOVC A,@A+DPTR ;查表 MOV DPTR,#B_8255 ;送段显示 MOVX @DPTR,A MOV A,R3 MOV DPTR,#A_8255 MOVX @DPTR,A ACALL DL1MS INC R0 ;显示缓冲加1 MOV A,R3 JNB ACC.0,OUT ;扫描结束否 RR A ;向右移一位 MOV R3,A AJMP AGAIN OUT: POP 03H POP 00H POP ACC RET ;数码管段显示值DSEGS: DB 03FH, 06H,05BH,04FH,066H,06DH,07DH, 07H DB 07FH,06FH,077H,07CH,039H,05EH,079H,071H DL1MS: MOV R7,#01H DL0: MOV R6,#080H DL1: DJNZ R6,DL1 DJNZ R7,DL0 RET PUTBUF: PUSH 00H ;保存键值到缓冲RAM 中 PUSH ACC MOV A,R5 MOV R0,A POP ACC MOV @R0,A DEC R5 CJNE R5,#04FH,GOBACK MOV R5,#55H ;重置缓冲地址GOBACK: POP 00H RET END ;==============================================================; 文件名称: KeyScan.Asm; 功能描述: 8255扩展IO, 完成键盘及数码管显示实验.; 按下按键, 数码管显示相应键值.;==============================================================A_8255 EQU 7F00H ;8255端口定义B_8255 EQU 7F01HC_8255 EQU 7F02HCON_8255 EQU 7F03HORG 0000HLJMP MAINORG 0100HMAIN: MOV 50H,#00H ;键值缓冲清0MOV 51H,#00HMOV 52H,#00HMOV 53H,#00HMOV 54H,#00HMOV 55H,#00HMOV R5, #55HMOV A, #81H MOV DPTR, #CON_8255 ;8255控制端口MOVX @DPTR, A ;写入控制字BEGIN: LCALL DIS ;调用显示子程序LCALL CLEAR ;清屏LCALL CCSCAN ;调用键扫子程序JNZ INK1 ;判是否有键按下LJMP BEGININK1: LCALL DISLCALL DL1MS ;消除按键抖动LCALL DL1MSLCALL CLEARLCALL CCSCANJNZ INK2AJMP BEGININK2: MOV R2,#0FEHMOV R4,#00H ;从第0列开始扫描COLUM: MOV DPTR,#A_8255MOV A,R2MOVX @DPTR,A ;写入列扫描值MOV DPTR, #C_8255MOVX A,@DPTRJB ACC.0,LINE1 ;判第0行的值MOV A,#00H ;第0行AJMP KCODELINE1: JB ACC.1,LINE2MOV A,#04H ;第1行AJMP KCODELINE2: JB ACC.2,LINE3MOV A,#08H ;第2行AJMP KCODELINE3: JB ACC.3,NEXTMOV A, #0CH ;第3行KCODE: ADD A,R4 ;得到键值ACALL PUTBUFPUSH ACCKON: ACALL DISACALL CLEARACALL CCSCANJNZ KONPOP ACCNEXT: INC R4MOV A,R2JNB ACC.4,KERRRL AMOV R2,AAJMP COLUMKERR: AJMP BEGINCCSCAN: MOV DPTR,#A_8255 ;按键扫描MOV A,#00HMOVX @DPTR,AMOV DPTR,#C_8255MOVX A,@DPTRCPL A ;取反ANL A,#0FHRET。

键盘扫描显示实验报告

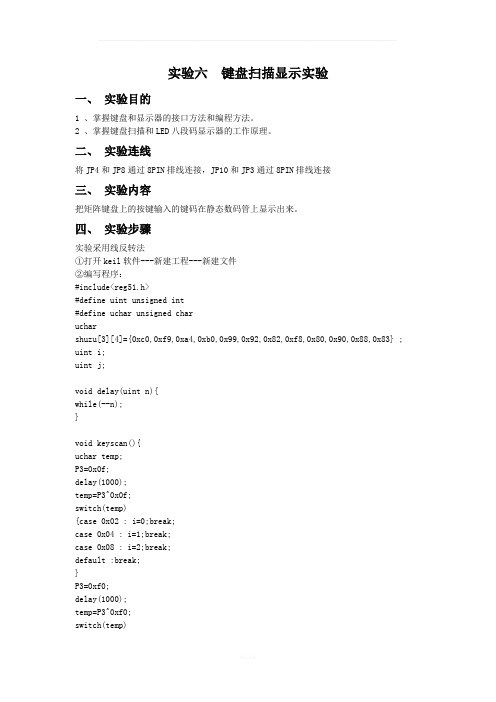

实验六键盘扫描显示实验一、实验目的1 、掌握键盘和显示器的接口方法和编程方法。

2 、掌握键盘扫描和LED八段码显示器的工作原理。

二、实验连线将JP4和JP8通过8PIN排线连接,JP10和JP3通过8PIN排线连接三、实验内容把矩阵键盘上的按键输入的键码在静态数码管上显示出来。

四、实验步骤实验采用线反转法①打开keil软件---新建工程---新建文件②编写程序:#include<reg51.h>#define uint unsigned int#define uchar unsigned charucharshuzu[3][4]={0xc0,0xf9,0xa4,0xb0,0x99,0x92,0x82,0xf8,0x80,0x90,0x88,0x83} ; uint i;uint j;void delay(uint n){while(--n);}void keyscan(){uchar temp;P3=0x0f;delay(1000);temp=P3^0x0f;switch(temp){case 0x02 : i=0;break;case 0x04 : i=1;break;case 0x08 : i=2;break;default :break;}P3=0xf0;delay(1000);temp=P3^0xf0;switch(temp){case 0x10 : j=0;break;case 0x20 : j=1;break;case 0x40 : j=2;break;case 0x80 : j=3;break;default : break;}}main(){P2=0x00;while(1){ P3=0x00;if(P3!=0xf0)keyscan();P2=shuzu[i][j];delay(1000);}}保存、编译---生成hex文件③连接线,使用下载软件将编好程序载入单片机中。

实验四键盘扫描及显示设计实验报告

实验四键盘扫描及显⽰设计实验报告实验四键盘扫描及显⽰设计实验报告⼀、实验要求1. 复习⾏列矩阵式键盘的⼯作原理及编程⽅法。

2. 复习七段数码管的显⽰原理。

3. 复习单⽚机控制数码管显⽰的⽅法。

⼆、实验设备1.PC 机⼀台2.TD-NMC+教学实验系统三、实验⽬的1. 进⼀步熟悉单⽚机仿真实验软件 Keil C51 调试硬件的⽅法。

2. 了解⾏列矩阵式键盘扫描与数码管显⽰的基本原理。

3. 熟悉获取⾏列矩阵式键盘按键值的算法。

4. 掌握数码管显⽰的编码⽅法。

5. 掌握数码管动态显⽰的编程⽅法。

四、实验内容根据TD-NMC+实验平台的单元电路,构建⼀个硬件系统,并编写实验程序实现如下功能:1.扫描键盘输⼊,并将扫描结果送数码管显⽰。

2.键盘采⽤ 4×4 键盘,每个数码管显⽰值可为 0~F 共 16 个数。

实验具体内容如下:将键盘进⾏编号,记作 0~F,当按下其中⼀个按键时,将该按键对应的编号在⼀个数码管上显⽰出来,当再按下⼀个按键时,便将这个按键的编号在下⼀个数码管上显⽰出来,数码管上可以显⽰最近 4 次按下的按键编号。

五、实验单元电路及连线矩阵键盘及数码管显⽰单元图1 键盘及数码管单元电路实验连线图2实验连线图六、实验说明1. 由于机械触点的弹性作⽤,⼀个按键开关在闭合时不会马上稳定地接通,在断开时也不会⼀下⼦断开。

因⽽在闭合及断开的瞬间均伴随有⼀连串的抖动。

抖动时间的长短由按键的机械特性决定,⼀般为 5~10ms。

这是⼀个很重要的时间参数,在很多场合都要⽤到。

键抖动会引起⼀次按键被误读多次。

为了确保 CPU 对键的⼀次闭合仅做⼀次处理,必须去除键抖动。

在键闭合稳定时,读取键的状态,并且必须判别;在键释放稳定后,再作处理。

按键的抖动,可⽤硬件或软件两种⽅法消除。

2. 为了减少键盘与单⽚机接⼝时所占⽤ I/O 线的数⽬,在键数较多时,通常都将键盘排列成⾏列矩阵形式。

3. 从数码管显⽰⽅式看,数码管分为静态显⽰和动态显⽰两种⽅式。

实验三 键盘扫描控制

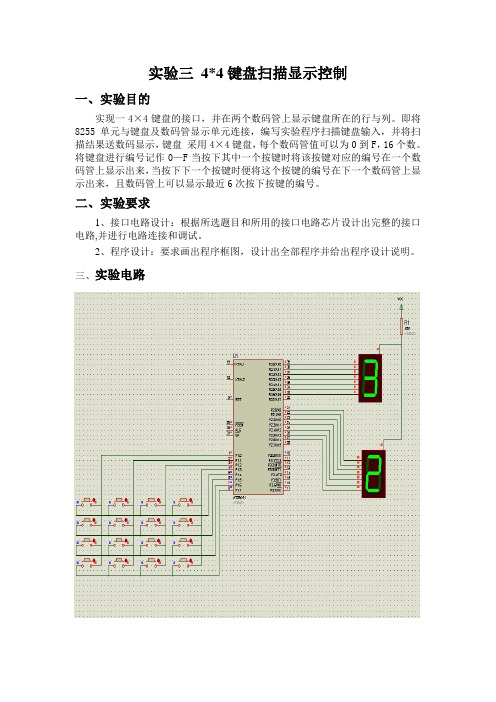

实验三4*4键盘扫描显示控制一、实验目的实现一4×4键盘的接口,并在两个数码管上显示键盘所在的行与列。

即将8255单元与键盘及数码管显示单元连接,编写实验程序扫描键盘输入,并将扫描结果送数码显示,键盘采用4×4键盘,每个数码管值可以为0到F,16个数。

将键盘进行编号记作0—F当按下其中一个按键时将该按键对应的编号在一个数码管上显示出来,当按下下一个按键时便将这个按键的编号在下一个数码管上显示出来,且数码管上可以显示最近6次按下按键的编号。

二、实验要求1、接口电路设计:根据所选题目和所用的接口电路芯片设计出完整的接口电路,并进行电路连接和调试。

2、程序设计:要求画出程序框图,设计出全部程序并给出程序设计说明。

三、实验电路四、实验原理说明图2 数码管引脚图图1为AT89C51引脚图,说明如下:VCC:供电电压。

GND:接地。

P0口:P0口为一个8位漏级开路双向I/O口,每脚可吸收8TTL门电流。

当P1口的管脚第一次写1时,被定义为高阻输入。

P0能够用于外部程序数据存储器,它可以被定义为数据/地址的第八位。

在FIASH编程时,P0 口作为原码输入口,当FIASH进行校验时,P0输出原码,此时P0外部必须被拉高。

P1口:P1口是一个内部提供上拉电阻的8位双向I/O口,P1口缓冲器能接收输出4TTL门电流。

P1口管脚写入1后,被内部上拉为高,可用作输入,P1口被外部下拉为低电平时,将输出电流,这是由于内部上拉的缘故。

在FLASH 编程和校验时,P1口作为第八位地址接收。

P2口:P2口为一个内部上拉电阻的8位双向I/O口,P2口缓冲器可接收,输出4个TTL门电流,当P2口被写“1”时,其管脚被内部上拉电阻拉高,且作为输入。

并因此作为输入时,P2口的管脚被外部拉低,将输出电流。

这是由于内部上拉的缘故。

P2口当用于外部程序存储器或16位地址外部数据存储器进行存取时,P2口输出地址的高八位。

在给出地址“1”时,它利用内部上拉优势,当对外部八位地址数据存储器进行读写时,P2口输出其特殊功能寄存器的内容。

【单片机实验指导】8255扫描键盘,显示实验

8255扫描键盘,显示实验

一.实验要求

利用8255可编程并行口做一个扫描键盘实验,把按键输入的键码,显示在由8279控制的七段数码管上。

8255PA口做键盘输入线,PB口作扫描线。

二.实验目的

1.掌握8255编程方法。

2.掌握扫描键盘和显示的编程方法。

三.实验电路及连线

8255的CS/接138的8400H,则命令字地址为8406H,PA口地址为8400H,PB口地址为8402H,PC口地址为8404H。

8279电路部分与实验机监控所用电路相同,地址已确定如下:

8279的状态口地址为0FF82H;

8279的数据口地址为0FF80H;

K10的十个短路套都套在8255侧。

四.实验说明

在PA口与PB口组成的64点阵列上,把按键接在不同的点上,将得到不同的键码,本实验采用8×2的阵列,共可按16个键。

显示部分由8279控制,由7407驱动8位数码管显示。

五.实验框图

主程序框图读键显示部分框图。

4 4键盘扫描实验

4*4键盘扫描实验目的:1. 熟悉51系列单片机矩形4*4键盘扫描的工作原理。

2. 掌握4*4键盘扫描的编程方法。

实验原理:键盘实际上是由排列成矩阵形式的一系列按键开关组成的,它是单片机系统中最常用的人机联系的一种输入设备。

用户通过键盘可以向CPU输入数据、地址和命令。

键盘按其结构形式可分为编码式键盘和非编码式键盘两大类。

编码式键盘是由其内部硬件逻辑电路自动产生被按键的编码。

这种键盘使用方便,但价格较贵。

4×4表示有4根行线和4根列线,在每根行线和列线的交叉点上均分布1个单触点按键,共有16个按键。

行扫描法所谓行扫描法,就是通过行线发出低电平信号,如果该行线所连接的键没有按下的话,则列线所连接的输出端口得到的是全“1”信号;如果有键按下的话,则得到的是非全“1”信号。

列扫描法所谓列扫描法,就是通过列线发出低电平信号,如果该列线所连接的键没有按下的话,则列线所连接的输出端口得到的是全“1”信号;如果有键按下的话,则得到的是非全“1”信号。

实验内容:1.编写一程序,4*4键盘扫描#include"reg51.h"#define uchar unsigned char#define uint unsigned intuchar keyno;uchar disp[]={0x3f,0x06,0x5b,0x4f,0x66,0x6d,0x7d, 0x07, 0x7f, 0x6f, 0x77, 0x7c,0x39,0x5e,0x79,0x71}; uchar lieno;void delay1ms(uchar i){uchar j;while(i--)for(j=0;j<110;j++);}void main(){uchar tem;P0=0xff;while(1){P1=0x0f;if(P1!=0x0f)delay1ms(5);if(P1!=0x0f)tem=P1^0x0f;switch (tem){case 0x01:lieno=0;break;case 0x02:lieno=4;break;case 0x04:lieno=8;break;case 0x08:lieno=12;break;default :lieno=16;}P1=0xf0;tem=(P1>>4)^0x0f;switch (tem){case 0x01:keyno=lieno;break;case 0x02:keyno=lieno+1;break;case 0x04:keyno=lieno+2;break;case 0x08:keyno=lieno+3;}P0=disp[keyno];delay1ms(10);}}。

单片机按键扫描实验报告

单片机按键扫描实验报告

实验目的:

通过实验,掌握单片机按键的原理和按键的扫描方法。

实验器材:

1. STC89C52单片机开发板

2. 按键模块

3. 面包板、杜邦线等

实验原理:

单片机按键的原理是通过按键模块接通或断开单片机的某个IO口,从而改变该IO口的电平状态,由单片机检测到电平状态的改变,从而实现对按键的检测和响应。

按键模块一般采用矩阵按键的形式,通过多个IO口设为输出,多个IO口设为输入的方式,实现对多个按键的扫描检测。

按键模块一般会采用行列扫描的方法,即将按键分为多个行和列,按下按键时,某一行和某一列之间接通,从而改变了IO口的电平状态。

实验步骤:

1. 将按键模块连接到单片机开发板的IO口上。

根据按键模块的接口定义将VCC、GND和各个行列引脚分别连接到开发板上。

2. 根据按键模块的引脚定义,编写单片机程序进行按键的扫描。

通过循环检测每个行引脚和每个列引脚之间的电平变化,来判断按键是否被按下。

3. 在程序中可以通过LED等显示设备来显示按键是否被按下的状态。

4. 执行程序,观察按键是否可以正常检测和响应。

实验结果:

实验完成后,观察到按键的检测和响应正常,按下按键时,LED等显示设备可以正确显示按键被按下的状态。

经过实验,掌握了单片机按键的原理和按键的扫描方法,进一步提升了对单片机设备的理解和应用能力。

实验四 键盘扫描实验

一、实验目的、要求设计一个4X4的矩阵键盘,键盘的号码0~15,要求编写出一个键盘输入扫描程序,要求单片机能根据键盘排列顺序,能将按下去键盘号正确识别出来,并采用两个数码管分别键盘号码的个位和十位。

二、实验原理三、源程序清单或实验步骤1.设计电路,并按照电路接线2.编写调试程序:#include<reg51.h> //包含51单片机寄存器定义的头文件sbit P14=P1^4;sbit P15=P1^5;sbit P16=P1^6;sbit P17=P1^7;unsigned char codeTab[ ]={0xc0,0xf9,0xa4,0xb0,0x99,0x92,0x82,0xf8,0x80,0x90}; //数字0~9的段码unsigned char keyval;/**************************************************************函数功能:数码管动态扫描延时**************************************************************/void led_delay(void){unsigned char j;for(j=0;j<200;j++);}/**************************************************************函数功能:按键值的数码管显示子程序**************************************************************/void display(unsigned char k){P2=0xbf;P0=Tab[k/10];led_delay();P2=0x7f;P0=Tab[k%10];led_delay();}/**************************************************************函数功能:软件延时子程序**************************************************************/void delay20ms(void){unsigned char i,j;for(i=0;i<100;i++)for(j=0;j<60;j++);}/************************************************************** 函数功能:主函数**************************************************************/ void main(void){EA=1;ET0=1;TMOD=0x01;TH0=(65536-500)/256;TL0=(65536-500)%256;TR0=1;keyval=0x00;while(1){display(keyval);}}/************************************************************** 函数功能:定时器0的中断服务子程序,进行键盘扫描,判断键位**************************************************************/ void time0_interserve(void) interrupt 1 using 1{P1=0xf0;if((P1&0xf0)!=0xf0)delay20ms();if((P1&0xf0)!=0xf0){P1=0xfe;if(P14==0)keyval=1; if(P15==0) keyval=2; if(P16==0) keyval=3;if(P17==0)keyval=4;P1=0xfd;if(P14==0)keyval=5;if(P15==0)keyval=6;if(P16==0)keyval=7;if(P17==0)keyval=8;P1=0xfb;if(P14==0)keyval=9;keyval=10;if(P16==0)keyval=11;if(P17==0)keyval=12;P1=0xf7;if(P14==0)keyval=13;if(P15==0)keyval=14;if(P16==0)keyval=15;if(P17==0)keyval=16;}TR0=1;TH0=(65536-500)/256;TL0=(65536-500)%256;}四、实验结果经过调试:矩阵键盘上的输入按键的键号能够正常显示在LED数码管上。

单片机按键扫描实验报告

单片机按键扫描实验报告键盘扫描一.实验目的(1)掌握矩阵键盘接口电路和键盘扫描编程方法。

(2)掌握按键值处理与显示电路设计。

二.实验任务(1)设计 4_4 键盘,编写各个键的特征码和对应的键值(0~F);(2)编程扫描按键,将按键对应的数字值使用数码管显示出来。

三.实验电路及连线方法1.采用动态显示连线方法:电路由2 片74LS573,1 个六字一体的共阴数码管组成。

由U15 输出段选码,U16 做位选码,与单片机的采用I/O 口连接方式,短路片J22 连接P2.0,J23 连接P2.3,做输出信号锁存。

(实际电路连接是 d7-d6-d5-d4-d3-d2-d1-d0 h-c-d-e-g-b-a-f)。

PW12 是电源端。

2.键盘电路连线方法:电路由16 个按键组成,用P1 口扩展4 _____4 行列式键盘。

J20 是键盘连接端,连接到P1 口。

J21 是行列键盘、独立键盘选择端,当J21 的短路片连接2-3 脚时,构成4 _____4 行列式键盘;当J21 的短路片连接2-1 脚时,可形成3 _____4 行列式键盘,4 个独立式按键S4、S8、S12、S16,这4 个独立按键分别连接P1.4~P1.7;其他12 个键3 _____4 行列式键盘。

PW15 是电源端。

四.编程思路1.采用反转法识别按键的闭合。

2.采用动态显示将键值显示出来。

五.算法流程图六.资源分配 1.用 P1 口进行查找按键 2.用 R3 做键值指针 3.用 R1 做动态显示为选码指针。

4.R5 为延时指针。

七.程序设计ORG0000H KPIN: MOVP1,#0F0HMOVA,P1ANLA,#0F0HMOVB,AMOVP1,#0FHMOVA,P1ANLA,#0FHORLA,BCJNEA,#0FFH,KPIN1 AJMPE_IT KPIN1: MOV B,AMOVDPTR,#TABKP MOVR3,#0 KPIN2: MOV A,R3MOVCA,@A+DPTRCJNEA,B,KPIN3MOVA,R3LOOP: MOVR1,#0FEH;键盘动态显示 LOOP1: MOV A,R3ANLA,#0FHMOVDPTR,#TABMOVCA,@A+DPTRCLRP2.0CLRP2.1MOVP0,ASETBP2.0NOPCLRP2.0 LOOP2: MOVA,R1;位选码MOVP0,ASETBP2.1MOVR5,#250 LOOP3: DJNZR5,LOOP3CLRP2.1SJMPLOOPKPIN3: INCR3CJNEA,#0FFH,KPIN2 E_IT: RET TABKP: DB0EEH,0DEH,0BEH,7EH,0EDH,0DDH,0BDH,7DH,0EBHDB0DBH,0BBH,7BH,0E7H,0D7H,0B7H,77H,67H,0FFH TAB: DB 77H,44H,3EH,6EH,4DH,6BH,7BH,46H,7FH,6FH,5FHDB79H,33H,7CH,3BH,1BHEND 八.调试出现的问题及解决问题 1:程序正常运行,但按键显示出现乱码解决:动态显示笔形码错误,并改正。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

实验 4 键盘实验一、实验目的:1.掌握 8255A 编程原理。

2.了解键盘电路的工作原理。

3.掌握键盘接口电路的编程方法。

二、实验设备:CPU 挂箱、 8031CPU 模块三、实验原理:1.识别键的闭合,通常采用行扫描法和行反转法。

行扫描法是使键盘上某一行线为低电平,而其余行接高电平,然后读取列值,如所读列值中某位为低电平,表明有键按下,否则扫描下一行,直到扫完所有行。

本实验例程采用的是行反转法。

行反转法识别键闭合时,要将行线接一并行口,先让它工作于输出方式,将列线也接到一个并行口,先让它工作于输入方式,程序使 CPU 通过输出端口往各行线上全部送低电平,然后读入列线值,如此时有某键被按下,则必定会使某一列线值为 0。

然后,程序对两个并行端口进行方式设置,使行线工作于输入方式,列线工作于输出方式,并将刚才读得的列线值从列线所接的并行端口输出,再读取行线上的输入值,那么,在闭合键所在的行线上的值必定为 0 。

这样,当一个键被按下时,必定可以读得一对唯一的行线值和列线值。

2.程序设计时,要学会灵活地对8255A 的各端口进行方式设置。

3.程序设计时,可将各键对应的键值(行线值、列线值)放在一个表中,将要显示的0〜F字符放在另一个表中,通过查表来确定按下的是哪一个键并正确显示出来。

实验题目利用实验箱上的 8255A 可编程并行接口芯片和矩阵键盘,编写程序,做到在键盘上每按一个数字键(0〜F),用发光二极管将该代码显示出来。

四、实验步骤:将键盘 RL10 〜 RL17 接 8255A 的 PB0 〜 PB7;KA10 〜 KA12 接 8255A 的 PA0〜 PA2;PC0〜PC7接发光二极管的 L1〜L8 ; 8255A 芯片的片选信号 8255CS接CS0。

五、实验电路:3-- -^-LJ-X*—7白I丿.,I n T —;白—广一□1六、程序框图7.程序清单根据豹th/1啲陆査者Q输冷"O' ・ >'.Pr3JU 入伯是国为愛"广〔寛期匕上八、附:8251/8255 扩展模块该模块由8251可编程串行口电路和 8255可编程并行口电路两部分组成,其电源、数 据总线、地址总线和片选信号均由接口挂箱上的接口插座提供。

•、8251可编程串行口电路(1)8251可编程串行接口芯片引脚及功能8251A 是通用同步/异步收发器USART ,适合作异步起止式数据格式和同步面向字符数据格式的接口,其功能很强。

它是用来作为CPU 与外部设备或调制解调器之间的接口芯片。

图3-158251管脚图下面简单介绍一下 8251各引脚的主要功能: -D0~D7 :三态双向数据线; RD:读信号,低电平有效; WR :写信号,低电平有效; CS :片选,低电平有效;RESET :芯片复位线,高电平有效。

当该线上加高电平(宽度为时钟的 6倍)时,芯片复位而处于空闲态,等待命令;C/D :地址线。

若此脚加高电平,则CPU 访问8251A 命令寄存器或状态寄存器,若加低电平,则访问数据寄存器;TXRDY( Tran smitter Ready):发送器准备好,高电平有效。

在用查询方式时,此 信号作为一状态位, CPU 可从状态寄存器的D0位检测这个信号;在中断方式时,可作为中断请求信号;RXRDY( Receiver Ready):接收器准备好,高电平有效;在用查询方式时,此信 号作为一状态位,CPU 可从状态寄存器的 D1位检测这个信号;在中断方式时,可作为 中断请求信号;TXE(Transmitter Empty ):发送器空,高电平有效;SYNDET ( Synchronous Detection ) /BD(Break Detection):双功能引脚。

这个 弓I 脚在同步方式时,作同步字符检出信号,为双向线。

在异步方式时,作间断信号检出-p ——FYKDEZIZBD———n mP H. 賞—匝2i — Da豐——ELKBD ,是输出。

当检测到间断码时,输出高电平。

TXC (Transmitter Clock ):发送器时钟,由外部(波特率时钟发生器)提供。

由它 控制 8251A 发送数据速率。

RXC (Receiver Clock ):接收器时钟,由外部(波特率时钟发生器)提供。

由它控制 8251A 接收数据速率。

实际应用中,与发送器时钟相接。

CLK :工作时钟,由外部时钟源提供。

为芯片内部电路提供定时,并非接收或发送数 据的时钟。

8251A 提供了 4个与MODEM 相连的控制信号和数据发送以及数据接收信号线DTR 、DSR 、RTS 、CTS 。

它们的含义与 RS-232C 标准定义相同。

(2 ) 8251电路图及说明医』图3-16 8251电路图模块上提供十个插孔,分别是:RESET 、DTR 、RTS 、RXRDY 、TXRDY 、RXD 、TXD 、8251CLK 、RXCLK 、TXCLK ,它们分别对应于图中相应的引脚。

CS8251的用法如前所述。

8251芯片的详细用法请查阅相关手册。

(3)8251电路的基本测试方法将8251/8255 模块上CS8251片选排上的片选 CS1用跳线帽短接,8251CLK 接到CPU 挂箱时钟发生电路的 CLK3,RXCLK 与TXCLK 接到CPU 挂箱看门狗电路的 DOGO (将 DOGO 输出频率调为最大),RXD 与TXD 相接。

运行测试程序,在程序返回前设置断点,如模块正常,内存单元 50H~5FH 中的数据应为00H — 0FH 。

测试参考程序如下:CSEG AT 0000H LJMP START CSEG AT 4100H CON EQU 0A009H洛 : CS3“助 : 1i3 4 J1 73 910 11 12 13 If 1J1CTxD IiWY !s£?EE. ExDlAirrPVKDEt13TJKTLK-13CDD£LD!1 Gif JE :eiSJJiDO 27CS8251 11 戸 rc®.ri is :;E0WK 10 … w12-°DIamDJ DLDT13ELE14CfU3C J OcamDAT EQU 0A008HSTART: MOV DPTR, #CON MOVA, #0DEH MOVX@DPTR, A MOV A,#55H MOVX @DPTR, ANOPNOPMOV DPTR, #CON MOVA, #0DEH MOVX@DPTR, A MOV A,#15H MOVX @DPTR, AMOV R0, #50H MOVR2, #10H CLR ALP: MOV @R0, AINC R0DJNZ R2, LPMOV R0, #50HMOV R1, #00HMOV R2, #10HLP1: MOV DPTR, #CON MOVXA, @DPTR JNBACC.0, LP1 MOVDPTR, #DAT MOV A,R1MOVX @DPTR, ALP2: MOV DPTR, #CON MOVXA, @DPTR JNBACC.1, LP2 MOVDPTR, #DAT MOVX A,@DPTR MOV @R0, AINC R0;8251 初始化;8251 初始化;50H~5FH 清 0;发送;接收INC R1 DJNZ R2, LP1HALT: JMP HALTEND、8255可编程并行口电路(1) 8255并行接口芯片引脚及功能8255是一种常用的可编程并行I/O 接口芯片,片内有PA 、PB 、PC 三个8位可编程双向通用扩展I/O 口。

8255有40条引脚,采用双列直插式封装,其引脚如图各引脚及功能介绍如下:A 、B 、C 三个I/O 接口的引线分别为: PA0~PA7、PB0~PB7、PC0~PC7 共24条端 线。

3个口均为8位I/O 数据口。

A 口由一个8位数据输出缓冲/锁存器和一个8位数据输 入缓冲/锁存器组成,可设置为输入或输出或双向方式工作;B 口和C 口各有一个8位数据输出缓冲/锁存器和一个8位数据输入缓冲器(无输入数据锁存器,故 B 口不可在模式2下 工作)组成。

其中,B 口只能设为输入或输出方式,不能双向工作。

C 口可设置为输入/输出口,上半部PC4~PC7与A 口组成A 组;下半部PC0~PC3与B 口组成B 组,便于控制。

控制线控制8255的读、写、复位及片选等: RD :读控制线,低电平有效,当其为低电平时, CPU 对8255进行读操作,此时8255相应口为输入口。

WR :写控制线,低电平有效,当其为低电平时, CPU 输出数据或命令到 8255端口, 此时8255相应口为输出口。

RESET :复位端,高电平有效。

当其为高电平时,8255内部寄存器全部清零,24条I/O 口线为高阻态。

CS :片选端,低电平有效。

当其为低电平时,CPU 选中此8255芯片。

8255共占有4个口地址,为A 、B 、C 口及控制口地址。

这4个地址之间的选择由 A0、3-17所示:图3-178255管脚图A1两端口线控制,二者组合决定了4个端口地址,口地址选择方式如下:A1A0 选择口0 0A 口0 1 B 口1 0 C 口1 1 控制口从引脚及结构图可见8255 有和其它接口芯片类似的结构,即除了三个I/O 口寄存器外还有一个控制寄存器,由控制信号送控制字来确定芯片各个I/O口的工作状态。

⑵8255电路及说明图3-18 8255电路图图中PA、PB、PC 口共24根线全部引至模块上的相应插孔。

CS8255的用法与前述相同。

8255的详细用法请查阅相关手册。

(3)8255电路的基本测试方法将CS8255跳线排上的片选 CSO用跳线帽短接,PB7~PB0接接口挂箱电平开关电路输出插孔K8~K1 ,PA7~PA0 接LED8~LED1。

运行测试程序,女口 8255电路正常,LED8~LED1的亮灭应能反应 K8~K1的电平状况。

然后将程序稍加修改,测试PC 口的输出。

测试参考程序如下:CSEG AT 0000HLJMP STARTCSEG AT 4100HPA EQU 0A000HPB EQU 0A001HPCTL EQU 0A003HSTART : MOV DPTR,#PCTL ;置 8255A 控制字,A、B、C 口均工作;方式0, A、C 口为输出,B 口为输入CE3 --------S "I1—11—1----------- 111 土X31一1IISB __ 111TFTTMOV A, #82HMOVX @DPTR, AMOV DPTR,#PB ;从 B 口读入开关状态值MOVX A, @DPTRCPL AMOV DPTR, #PAMOVX @DPTR,A;从 A 口将状态值输出显示SJMP LOOPENDLOOP:。