PADS学习方法

PADS学习教程

PADS学习教程PADS(PowerPC Assembly Language Debugger Simulator)是一款用于学习和调试PowerPC汇编语言的软件工具。

本文将介绍PADS的基本功能和使用方法,以及学习PowerPC汇编语言的一些建议。

一、PADS的基本功能PADS提供了一个模拟的PowerPC处理器环境,可以逐条执行PowerPC汇编语言指令,以实时调试和跟踪程序的执行过程。

它具有以下主要功能:1.单步执行:PADS可以逐条执行程序指令,通过单步执行可以观察每条指令的执行结果,并监测寄存器和内存的变化。

2.断点调试:PADS允许在程序中设置断点,当程序执行到断点处时会停下来等待进一步的调试操作。

3.观察寄存器和内存:PADS可以显示程序运行时的寄存器和内存状态,包括寄存器的值和内存中的数据。

4.查看汇编码:PADS可以将程序反汇编为汇编语言,方便对程序进行分析和调试。

5.仿真寄存器和内存:PADS可以设定寄存器和内存的初始值,以及修改和保存寄存器和内存的值。

二、PADS的使用方法2. 创建项目:在PADS中创建一个新的项目,可以选择一个已有的PowerPC汇编程序,或者自己编写一个新的程序。

4.调试程序:在程序中设置断点,可以通过单步执行和观察寄存器和内存的方式来调试程序,可以观察程序的执行结果和对比期望结果,找出程序的错误。

5.优化程序:通过观察程序执行过程中的寄存器和内存状态,可以针对性地优化程序,提高程序的效率。

三、学习PowerPC汇编语言的建议1. 学习汇编基础:在学习PowerPC汇编语言之前,先学习一些基础的汇编知识,了解汇编语言的基本概念和常用指令,熟悉寄存器和内存的访问方式。

2. 学习指令集:详细研读PowerPC汇编指令集手册,了解每个指令的作用和使用方法,通过实际编写和调试程序来加深理解。

3. 分析示例程序:找一些PowerPC汇编语言的示例程序,通过分析和调试这些程序,理解指令的用法,掌握常用的编程技巧。

pads 教程

pads 教程Pads教程:基本操作入门Pads是一款常用的电子设计自动化(EDA)工具,用于电路设计、仿真和布局。

下面是Pads的基本操作入门教程。

步骤1:创建新项目首先,打开Pads软件并点击“文件”菜单中的“新建项目”。

在弹出的对话框中输入项目名称,并选择存储项目的目录。

然后,点击“确定”按钮。

步骤2:添加原理图在新建项目中,右键点击“设计文件”文件夹,并选择“添加新文件”。

选择创建原理图文件,并命名为“schematic”。

然后,进入原理图编辑器。

步骤3:绘制电路图在原理图编辑器中,使用工具栏上的元件库选择所需的元件,如电阻、电容、晶体管等。

将这些元件拖拽到画布上,并使用连接线连接它们。

步骤4:添加零件属性在绘制电路图时,需要为每个元件添加属性。

选中元件,右键点击并选择“属性”。

然后,填写元件的参数,如阻值、容值等。

步骤5:进行仿真完成电路图的绘制后,可以进行仿真以验证电路设计的正确性。

点击“工具”菜单中的“仿真”选项,并选择相应的仿真工具。

配置仿真参数后,运行仿真。

步骤6:完成布局设计在验证电路设计无误后,可以进行布局设计。

在Pads中,可以通过将原理图导入布局编辑器来完成布局设计。

点击“文件”菜单中的“导入”选项,并选择原理图文件。

步骤7:布局布线在布局编辑器中,使用工具栏上的布线工具将元件进行布线。

确保布局符合电路设计的要求,并注意避免干扰和干扰源的位置。

步骤8:进行设计规则检查完成布线后,进行设计规则检查以确保布局符合规范。

点击“工具”菜单中的“设计规则检查”选项。

根据检查结果进行必要的修正。

步骤9:生成制造文件最后,生成制造文件以供PCB(印刷电路板)制造商使用。

点击“文件”菜单中的“生成制造文件”选项,并选择所需的制造文件格式。

这就是Pads的基本操作入门教程。

通过学习这些步骤,您可以开始在Pads中进行电路设计、仿真和布局。

希望本教程能对您有所帮助!。

PADS应用技巧

PADS新手的一点心得和技巧偶是PADS的新手,原来一直用protel。

花了四天时间第一次用PADS2005画了一块大板子,开始确实有很多感觉不方便不熟悉的地方。

现在算是入门了,也总结了一些经验和技巧。

希望对PADS的新手能有所帮助。

1.布局时飞线(鼠线,connection)的处理。

Layout的缺省设置并不是让飞线最短化。

一开始布元件时,飞线实在是密如蛛网,晕头转向。

Tools\length minimization (CRTL+M) 也没有用,硬着头皮在缺省设置下完成了元件布局。

几欲faint。

后来才发现其实没有设置好。

正确或者说方便的设置应该是让飞线最短并且在移动中始终最短。

Setup\design rules\default rules\routing\ topology type\minimize这样在按CTRL+M,很多飞线就消失了,也就最短了另外,很多飞线其实是地线。

可以把地线的飞线先hide起来。

并把地线的net设置成比较特殊的颜色。

这样就布局就方便多了。

View\nets\ 选在左边net list 选GND net,加到右边view list。

在右边选GND,下面view unroute details 选none,在左边颜色中选一个颜色。

这样地线的飞线就hide起来了,并且是同一种颜色。

当然这里要小心信号地和power地要分开先。

这样的设置布局起来就方便多了。

早知道就好,ft。

2.改全部元件的字体属性。

和protel一样,这个是可以一次全部改成相同的属性的。

单击鼠标右键,选select components, 再单击右键,选select all (CTRL+A)。

再单击右键,选query/modify (CTRL+Q),part outline width 输入想要的宽度,下面选label,选Ref. Des. Press the big button under it. 弹出新窗口,input the value you want at size and width. Press OK. Then the size, width , even the part outline width are same. 有点麻烦。

pads logic学习

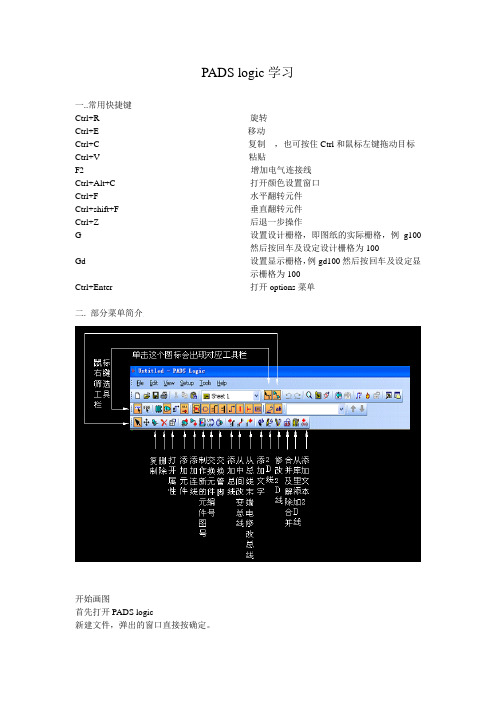

PADS logic学习一..常用快捷键Ctrl+R 旋转Ctrl+E 移动Ctrl+C 复制,也可按住Ctrl和鼠标左键拖动目标Ctrl+V 粘贴F2 增加电气连接线Ctrl+Alt+C 打开颜色设置窗口Ctrl+F 水平翻转元件Ctrl+shift+F 垂直翻转元件Ctrl+Z 后退一步操作G 设置设计栅格,即图纸的实际栅格,例g100然后按回车及设定设计栅格为100Gd 设置显示栅格,例gd100然后按回车及设定显示栅格为100Ctrl+Enter 打开options菜单二. 部分菜单简介开始画图首先打开PADS logic新建文件,弹出的窗口直接按确定。

文件建好后可以Ctrl+Enter 进行基本设置设置 鼠标 显示设置 栅格文本编码,不用管,我也不知道啥意思用这个就行自动保存间隔设置及路径都选 上吧在这里可以改变图框大小设置图纸电气连接线交点直径总线拐角直径设置文字属性三.简单原理图绘制1.绘制如下的原理图2.元件封装制作在原比例图绘制界面选择Tools>Part Editor 设置各种线宽度2.1先做CAE封装File>New选择CAE Decal显示如下窗口设置栅格,显示栅格gd100 ,设计栅格g100勾上做个简单的发光二极管CAE 封装点击这个打开工具栏选择2D线画LED图形,如图增加管脚然后保存。

2.2做Part 封装点Gate没CAE 封装的话先点着个做CAE 封装这里利用刚才的CAE 装直接做Part 封装双击然后点OK点Pins设置管脚信息添加PCB封装选中CAE 封装,然后点这里这里找不同管脚数的CAE封装找PCB封装选中PCB封装检查最后确定TGT20120514欢迎交流qq1798949399。

Pads 学习笔记

Pads layout 学习笔记201507310.封装制作PADS的封装制作思想和protel一样。

新建封装可以放在一个库文件中,一个库文件可以存放多个封装。

1)新建封装库文件文件/库,点击“新建库”在新建的库中可以新建封装,编辑封装1.导入板框File/import选择文件类型dxf或者手动画板框:位图工具栏->板框和挖空区域2.导入网表文件File/Import点需要的.asc文件即可3.参数设置1)过孔设置两种方法:1:在菜单 setup---pad stacks 选via,在Decal name里面找到你要修改的过孔,或者点add via新加一个过孔并在下面name输入名字,名字下面是设置通过或者盲埋孔的,右边设置形状和大小2:在板子上选中你要修改的过孔,右键选porperties,下面一排有个PAD图片点击然后可以修改(试了,对话框里啥也没有..)注意这些修改完后所有这类过孔都修改,也就是说修改的是这一类孔。

2)线宽设置SETUP->DESIGN RULES->DEFAULT->CLEARANCE中LAYOUT中,选择SETUP->DESIGN RULES->DEFAULT->CLEARANCE中可以设置TRACH WIDTH,就是默认的线宽,有最小,推荐,最大的值可以设置,这里设置都是默认值,就是你没有特别要求的画线的值。

在画线过程中,就是在走线的时候,LAYOUT中是F2,ROUTER中是F3,按W,可以输入线宽,例如W 20,假如之前单位是MIL,那么此时就不是推荐线宽,再画出来的就是20MIL的线宽。

3)栅格设置命令: G,然后输入格点数字4)叠层设置设置->层定义先设定总的层数。

平面类型:信号层选择“无平面”;内电层选择“分割/混合”其次,为电源层分配电源网络。

5)MM/MIL转换毫米切换命令:um米尔切换命令:umm6)安装孔,开孔安装孔有两种方式:A:安装孔制作成元件,原理图中画出B:2D线下,Drill Drawing 任意图形7)颜色配置,每层显示内容配置设置/显示颜色4.设置原点Setup/Set Origin5.测量距离命令:Q(直线测量)、QL(任意形状走线测量)鼠标放在测量起始位置,按Q,开始测量6.布局1)打散元件Tools/Disperse components7.布线1)差分2)等长3)扇出4)过孔添加走线过程中,右键/添加过孔5)走线长度双击走线,可查看已布线长度6)改变线宽命令: W,输入新的走线线宽7)铺铜步骤:1)先画铺铜区域绘图工具栏/铺铜2)铺铜1)Tools/Pour Manager/Flood2)Tools/Pour Manager/Hatchflood是第一次铺铜或者PCB设计规则有变动时使用。

PADS学习教程

PADS学习教程PADS是一款专业的电子设计自动化软件,被广泛应用于电子产品设计和布局方面。

它提供了丰富的功能和工具,可以帮助工程师在电路设计、印制电路板(PCB)布局和制造流程中提高效率和质量。

本文将为大家介绍PADS的基本知识和学习教程。

一、PADS的基本概念1. PADS Designer: PADS的主要设计工具,用于电路设计和布局。

2. PADS Layout: PADS的PCB布局工具,用于设计和布局印制电路板。

3. PADS Router: PADS的PCB布线工具,用于连接电路元件和布线。

4.PADS的优势:PADS具有易学易用、功能强大且价格较为合理等特点。

2.界面布局和基本操作:了解PADS的界面布局和基本操作方法,如创建新项目、导入和导出文件、打开和保存设计等。

3. 创建原理图: 使用PADS Designer创建电路原理图,选择合适的元件并进行连接。

4. 添加封装和布局: 在PADS Layout中为每个电路元件选择相应的封装,并进行布局。

5. 绘制电路板轮廓: 在PADS Layout中绘制电路板的外形和大小,确定其轮廓。

6. 定义和分配层次: 在PADS Layout中定义和分配不同层次的电路元件,如信号层、电源层和地层。

7. 进行布线和调整: 使用PADS Router进行电路元件的布线和调整,确保信号传输的良好。

8. 添加丝印和焊盘: 在PADS Layout中为电路板添加丝印和焊盘,以方便组装和焊接。

9. 生成Gerber文件: 在PADS Layout中生成Gerber文件,以便用于制造电路板。

10.输出制造文件:通过PADS将设计文件输出为制造所需的文件格式,如IPC-D-356A、ODB++和DXF等。

11.电路模拟和验证:在PADS中进行电路模拟和验证,确保设计的正确性和可靠性。

12.PCB制造和组装:制造电路板并进行组装,测试其可靠性和性能。

三、PADS学习资源1.官方文档和教程:PADS官方网站提供了大量的文档和教程,介绍了PADS的各种功能和使用方法。

PADSlogic入门教程

设置PIN脚起始号、步进值 (默认序号从1开始递增, 步进为1),单击OK完成。

标好序号后再对 引脚进行命名

输入引脚名称,电阻电 容可直接名为1、2,MOS 管则可为G、D、S,具体 应参考元件规格书。

如果命名错误也可 以更改引脚名称。

点击Set Pin Type按 钮,设置PIN脚类型, 例如电源引脚、双向引 脚、未定义等等,我们 一般设置成未定义。

PADS Logic入门教程

—以PADS2007为例

点击菜单栏file,新 建一个原理图文件

一.手工编辑元件库

点击菜单栏Tools/Part Editor,进入元件库编

辑模式

点击工具栏中Edit Graphics按钮,创建元 件的CAE图形及类型。

注:一个PADS Logic元件由以下三个基本单元组成 *元件类型:元件名称、连接引脚、逻辑单元、门交换信息 *CAE图形符号:原理图中元件的几何形状 *PCB封装:PCB设计中元件的几何形状

元 件 名 称

传递成功后即可对元 件进行布局、布线

网 络 名 称

布线前先设置一些规则, 我们将在PADS Layout入

门中继续探讨学习

三.绘制原理图

编辑好所需元件进入原理图 编辑界面,点击设计工具栏中

Add Part按钮,添加元件.

先选择元件库, 再在元件库中 查找所需元件, 和Protel类似, 选中元件点击 Add按钮即可添 加到原理图中

依次放置所需元件,单击 右键完成一个元件的放置, 再点击Add添加其它元件.

放置好后对元件进 行布局调整并编号

注:AutoCAD格式的图形尺寸需 要先放大39.37倍才能导入到 PADSLayout中。

选择放大后的*.DXP文档,导 入到PADS Layout的结构图

PADS详细入门教程

PADS详细入门教程PADS(PowerPCB),是一种电路设计和布局软件。

它具有用户友好的界面,可用于设计和布局不同类型的电路板。

在本文中,我们将提供一个详细的PADS入门教程,帮助您了解如何使用该软件来设计和布局电路板。

第一步:安装和准备工作第二步:创建新项目在PADS中,每个电路板设计都是一个项目。

要创建一个新项目,您可以在主菜单中选择“文件”>“新建”,然后选择“项目”。

在弹出的对话框中,您需要输入项目的名称和保存路径。

第三步:添加原理图原理图是电路设计的基础。

在PADS中,您可以通过导入CAD文件或从头开始绘制一个原理图。

要导入CAD文件,您可以选择“文件”>“导入”>“导入原理图”。

要从头开始绘制一个原理图,您可以选择“文件”>“新建”>“原理图”。

第四步:进行布局设计布局设计是将原理图转化为电路板布局的过程。

在PADS中,您可以通过调整和定位器件,进行布局设计。

您可以在左侧菜单中选择适当的工具,如选择工具、放置工具、旋转工具等。

要添加器件,您可以选择“放置工具”,然后在电路板上单击鼠标左键。

然后选择适当的器件类型,并将其拖动到所需的位置。

使用放置工具和旋转工具,您可以调整器件的位置和方向。

第五步:进行布线设计布线设计是将器件连接起来的过程。

在PADS中,您可以使用布线工具将器件之间的连接绘制在电路板上。

要使用布线工具,您可以选择“布线工具”,然后在器件之间单击鼠标左键并拖动以绘制线。

您还可以使用调整工具和删除工具来调整和删除线。

第六步:进行规则检查在完成布线设计之后,您需要进行规则检查,以确保电路板的设计符合规范。

在PADS中,您可以选择“规则”>“规则检查”,然后PADS将自动检查并显示任何违规的地方。

第七步:生成生产文件一旦您完成了电路板设计,就可以生成生产文件。

在PADS中,您可以选择“文件”>“生成输出”>“生成生产文件”。

在弹出的对话框中,您可以选择所需的输出文件类型和存储路径。

PADS-LAYOUT-入门教程(共22张)

计过程误操作。

第11页,共22页。

View 菜单(cài dān)

设计资源管理器:可 以很方便的选择操作

对象

网络显示设置:可设定网络以 不同的颜色来显示。

“Ctrl+V+N”或“Ctrl+Alt+N” 网络表

显示网络颜色的对象,如果要整条 网络(包含铜皮、走线)都要显示 设定的颜色,请把下边的复选框钩

上。 选中某一网络,指定相应 的颜色。如果要取消,选

择黑色即可。

缩放:一般用鼠标中 间键进行操作

整板显示:“Home”键

或“Ctrl+B”实现 刷新视图:“Ctrl+D”

网络显示设置:可设定网络以不同的 颜色来显示。

“Ctrl+V+N”或“Ctrl+Alt+N”

设计资源管理器

工具栏显示设置

显示状态栏

Flood 灌铜

Hatch 显示影线

Layer 层别

Solder Mask 阻焊开窗层 Past Mask 助焊层 Silkscreen 丝印层

Assembly Drawing 装配层

Connection 网络飞线(鼠线)

Ground ( Plane ) 地(平面) Power (Plane ) 电源(平面)

第9页,共22页。

Edit 菜单(cài

dān)

删除:选中对象后:“Del”键 要删除网络和元件,需在ECO模式下才

能进行

查找: 取消高亮:选中高亮对象后: “Ctrl+U”键即可取消高亮显示。 取消所有高亮网络:“N”敲回

车即可

选择所有:“Ctrl+A” 相对于“过滤选择”里面的不

PADS快捷键和技巧大全教学提纲

P A D S快捷键和技巧大全另外发一些最基本常用的几个快捷键:设置通孔显示模式:D+O设置铜只显示外框形式:P+O改变当前层:L(如改当前层为第二层,为L2)测量:从当前位置开始测量:Q改变线宽:W设置栅格:G对找元件管脚或元件:S寻找绝对坐标点:S(n)(n)改变走线角度:AA任意角,AD斜角,AO直角取消当前操作:UN,如UN(1)为取消前一个操作重复多次操作:RE设计规则检查:打开: DRP,关闭:DRO,忽略设计规则:DRI,以无过孔形式暂停走线:E锁定当前操作层对:PL(n)(n)选择当前过孔使用模式:自动过孔选择:VA埋孔或盲孔:VP通孔模式:VT保存:CTRL+S打开:CTRL+O新建:CTRL+N选择全部:CTRL+A全屏显示:CTRL+W移动:CTRL+E翻转:CTRL+F任意角度翻转:CTRL+I高亮:CTRL+H查询与修改:CTRL+Q45度翻转:CTRL+R增加走线:F2锁定层对:F4选择网络:F6选择管脚对:F5Ctrl+A 选择全部。

Ctrl+B 以板框为界整体显示当前设计。

Ctrl+C 复制。

Ctrl+D 刷新。

Ctrl+E 移动。

Ctrl+F 水平镜像翻转。

Ctrl+G 建立组合。

Ctrl+H 高亮。

Ctrl+I 以任意角度转换。

Ctrl+J 在布线模式下使用鼠标“十”字光标中心呈环形。

Ctrl+K 建立簇。

Ctrl+L 排列元件。

Ctrl+M 长度最短化。

Ctrl+N 建立新元件。

Ctrl+O 打开文件。

Ctrl+P 不在使用中。

PowerPCB 专业群 42336805、PCB Layout 学习群 48381494Ctrl+Q 调出被选中对象的“查询与修改”对话框。

Ctrl+R 以90°角度为单位旋转。

Ctrl+S 存盘。

Ctrl+T 不在使用中。

Ctrl+U 取消高亮。

Ctrl+V 粘贴。

Ctrl+W 以Zoom模式查看。

Ctrl+X 剪切。

Ctrl+Y 扩展。

pads学习笔记

Pads学习笔记(1)PADS Layout/Router支持完整的PCB设计,涵盖了从原理图网表导入,规则驱动下的交互式布局布线,DRC、DFT、DFM校验与分析,直到最后的生产文件(Gerber)、装配文件及物料清单(BOM)输出等全方位的功能需求,确保PCB工程师高效地完成设计任务。

Layout布高速板子效率低,但操作便捷,Router用于布高速板子,使用比较繁琐一些。

Logic是一种原理图设计环境,设计者可以高效地完成原理图及PCB的设计工作。

(2)CAE封装纯粹的图形,可以认为只是元件的一个图形表示方式,大小可以与真实元件不同。

PCB封装是元件在电路板上安装放置的样式。

CAE加上引脚的定义构成门Gate。

创建一个新元件,不但要绘制CAE封装,还需要绘制引脚定义。

(3)原理图只能在Logic中建立,封装只能在Layout中建立。

(4)元件类型可以简单的认为是原理图和元件封装的对应关系。

只有对应起来的原理图符号才能被放置在原理图中,元件封装才能被放置到PCB中。

(5)ECO就是工程更改,为避免用户违规操作,你从LOGIC导过去的无件,网络,封装等信息,只能在PCB的模式下才能更改,操作方法如下:1、点击ECO图标,软件进入ECO模式自动启动一个对话框,提醒你进行更改后的文件存放位置。

以进行更改后的恢复操作。

2、进行网络、元件、管脚、元件位号删减,更改等操作。

软件进行记录。

3、进行更改后的布线操作。

特别要注意的是你布线,布局等状态时最好留意一下不能在ECO模式下,因为有时候不小心鼠标一点有可能你的网络已经更改了但你没有留意到。

(6)PADS中的网络说白了就是连线,网络关系就是布线的关系。

(7)页间连接符其实就是不方便接线时或者为了简便而做的一个公用节点,可以认为相同命名的页间连接符实际上就是一个节点。

不管是同一图页中还是不同的图页中。

(8)总线(Bus)是计算机各种功能部件之间传送信息的公共通信干线,它是由导线组成的传输线束,按照计算机所传输的信息种类,计算机的总线可以划分为数据总线、地址总线和控制总线,分别用来传输数据、数据地址和控制信号。

pads logic中文学习教程

本文是PCB设计学习资料文档,使用软件为:PADS2007版。

主要介绍的是《PADS Logic原理图设计》,喜欢的朋友可以下下看。

PADS Logic ½Ì³ÌPADS Logic ½Ì³Ì¼ò½é»¶Ó-ʹÓÃPADS Logic ½Ì³Ì¡£±¾½Ì³ÌÓɱÈ˼µç×ÓÓÐÏÞ¹«Ë¾(KGS Technology Ltd.)±àд£¬±¾¹«Ë¾ÊÇMentor (ÒÔÇ°µÄInnoveda-PADS) PADS£¨ÒÔÇ°µÄPowerPCB£© ²úÆ·¡¢APLAC µÄÉäƵºÍ΢²¨·ÂÕ湤¾ß¡¢DpS µÄµçÆøͼCADϵͳPCschematic ÔÚÖйúµÄÊÚȨ´úÀíÉÌ¡£KGS¹«Ë¾×Ô1989Ä꿪ʼ£¬Ò»Ö±ÖÂÁ¦ÓÚPADSÈí¼þ²úÆ·µÄ ÏúÊÛºÍÖ§³Ö¡£¹«Ë¾Ìṩµç×Ó²úÆ·ÔÚÔ-ÀíÑù»úÉè¼Æ¿ª·¢½×¶ÎÈ«ÃæµÄ½â¾ö·½°¸¡£°üÀ¨Ïà¹ØµÄ CAE/CAD/CAMµÈEDAÈí¼þ¡¢ÌṩPCBÉè¼Æ·þÎñ¡¢PCBÑù°å¼Ó¹¤ÖÆÔì¡¢¿ìËÙ PCB ¼Ó¹¤É豸¡¢PCBÔªÆ÷¼þ×°Åä¡£ËùÓм¼ÊõÈËÔ±¶¼¾ßÓÐÊ®ÄêÒÔÉϵÄPCB Éè¼ÆÁìÓò´ÓÒµ¾-Àú¡£±¾½Ì³ÌÃèÊöÁËPADS Logic µÄ¸÷ÖÖ¹¦ÄܺÍÌص㡢ÒÔ¼°Ê¹Ó÷½·¨¡£ÕâЩ¹¦ÄÜ°üÀ¨£º_ ÈçºÎÔÚ PADS Logic ÖÐʹÓù¤×÷Çø(Working Area)¡£_ÈçºÎÔÚPADS LogicµÄÔª¼þ¿âÖж¨ÒåÄ¿±ê¿â(Library)¡£_ÈçºÎ´Ó¿âÖÐËÑË÷ÓйصÄÔª¼þ(Part)¡£_ÈçºÎÌí¼ÓÁ¬Ïß(Connection)¡¢×ÜÏß(Bus)¡¢Ê¹ÓÃÒ³¼äÁ¬½Ó·ûºÅ(Off-Page)¡£_Òƶ¯(Move)¡¢¿½±´(Copy)¡¢É¾³ý(Delete)ºÍ±à¼-(Edit)µÈ²Ù×÷·½Ê½(Mode)¡£_ÔÚÉè¼ÆÊý¾Ý±à¼-ʱʹÓòéѯ/ÐÞ¸Ä(Query/Modify)ÃüÁî¡£_ ÈçºÎ¶¨ÒåÉè¼Æ¹æÔò(Design Rules)¡£_ÈçºÎ½¨Á¢Íø±í(Netlist)ºÍSPICE ¸ñʽÍøÂç±íÒÔ¼°²ÄÁÏÇåµ¥(BOM)±¨¸æºÍÉú³ÉÖÇÄÜPDF Îĵµ¡£_ÈçºÎÊäÈëÖÐÓ¢ÎÄÎı¾ºÍÊäÈë±äÁ¿ÊýÖµ¡£_ÈçºÎʹÓÃÄ¿±êÁ¬½ÓÓëǶÈë(OLE)¹¦ÄÜ¡£_ ÈçºÎʹÓù¤³ÌÉè¼Æ¸ü¸Ä(Engineering Change Orders (ECO))¡£µ±ÄúѧϰÁËÕâЩ»ù±¾µÄÄÚÈݺ󣬿ÉÒԲο¼PADS Logic µÄÔÚÏß°ïÖú(On-line Help)²¿·Ö£¬ÒÔ±ãµÃµ½PADS Logic È«²¿¹¦ÄܵÄÏêϸ½éÉÜ¡£Í¬Ê±ÄúÒ²¿ÉÒÔÓëÎÒÃǹ«Ë¾ÔÚ¸÷µØµÄ°ìÊ´¦È¡µÃÁªÏµ£¬ÒÔ±ãµÃµ½¸ü¶àµÄ°ïÖú¡£Æô¶¯ PADS LogicÈç¹ûÏÖÔÚPADS Logic³ÌÐò»¹Ã»ÓÐÔËÐУ¬¿ÉÒÔͨ¹ýÔÚWindows 2000»òWindowsXP»·¾³ÏµÄÆô¶¯³ÌÐò²Ëµ¥Öеē¿ªÊ¼/³ÌÐò/Mentor GraphicsSDD/PADS2007/System Design”Ñ¡ÔñPADS Logic£¬Ê¹ÆäÔËÐС£×¢Ò⣺ÕâÀïÌṩµÄһЩÉè¼ÆÎļþÓÃÓÚ±¾½Ì³Ì£¬ÔÚÕû¸ö½Ì³ÌµÄѧϰʹÓÃÖУ¬Äú¿ÉÒÔʹÓÃÕâЩÎļþ£¬»òÕß½¨Á¢¡¢±£´æºÍ´ò¿ªÄú×Ô¼ºµÄÉè¼ÆÎļþ¡£Ìáʾ£ºÈç¹ûÄúʹÓÃÏÖÔÚÌṩµÄÕâЩÎļþ£¬᳔ºÃÔÚÒ»¸ö²»Í¬µÄĿ¼Ï¿½±´ÕâЩÎļþ£¬½øÐб¸·Ý¡£½Ì³ÌÔÊÐíÄúÒÔÁíÍâÖ¸¶¨µÄÎļþÃû±£´æÉè¼ÆÎļþ£¬µ«ÊÇÈç¹ûÄúÓÃÔ-À´µÄÎļþÃû£¬Ôò½«Ô-À´µÄÎļþ½«±»¸²¸Ç¡£ÎªÁ˱ÜÃ⽫Ô-ʼµÄÎļþ¸²¸Ç£¬ËùÒÔ½«ËüÃDZ¸·ÝÆðÀ´£¬»òÕß»»Ò»¸öÆäËüµÄÎļþÃû±£´æÆðÀ´¡£HK +852-******** SZ 755-88859921 SH 21-5108 7906 BJ 10-5166 5105support@2»¶Ó-ʹÓà PADS Logic ½øÐÐÔ-ÀíͼÉè¼Æ¼¼ÊõÖ§³Ö£ºsupport@Ä¿ ¼µÚÒ»½Ú - ͼÐÎÓû§½çÃæ(GUI)µÚ¶þ½Ú- ÔÚPADSµÄ¿âÄÚ¶¨ÒåÔª¼þ¿â(Library) µÚÈý½Ú- Ìí¼ÓºÍ±à¼-Ôª¼þ(Parts)µÚËĽÚ-½¨Á¢ºÍ±à¼-Á¬Ïß(Connections)µÚÎå½Ú - Ìí¼Ó×ÜÏß(Buses)µÚÁù½Ú - ÐÞ¸ÄÉè¼ÆÊý¾ÝµÚÆß½Ú - ¶¨ÒåÉè¼Æ¹æÔò(Design Rules)µÚ°Ë½Ú - ²úÉúÍøÂç±í¡¢±¨¸æ¡¢ÖÇÄÜ PDF ÎĵµµÚ¾Å½Ú - Îı¾µÄÊäÈëºÍÌí¼Ó±äÁ¿Îı¾£¨Add Field£©µÚÊ®½Ú - ʹÓà PADS Logic µÄÄ¿±êÁ¬½ÓÓëǶÈë OLE ¹¦ÄܵÚʮһ½Ú -¹¤³ÌÉè¼Æ¸ü¸Ä(Engineering Change Orders (ECO))HK +852-******** SZ 755-88859921 SH 21-5108 7906 BJ 10-5166 5105support@3µÚÒ»½Ú - ͼÐÎÓû§½çÃæ(GUI)PADS LogicµÄÓû§½çÃæÉè¼ÆµÃ·Ç³£Ò×ÓÚʹÓã¬PADSLogicÔÚŬÁ¦Âú×ã¸ß¼¶Óû§ÐèÒªµÄͬʱ£¬»¹¿¼Âǵ½Ðí¶à³õ´ÎʹÓÃPADSÈí¼þµÄÈËÔ±Çé¿ö¡£±¾½Ú½Ì³Ì°üº¬ÒÔÏÂÄÚÈÝ£º_PADS LogicÖеĽ»»¥²Ù×÷¹ý³Ì_¹¤×÷¿Õ¼äµÄʹÓÃ_ ÉèÖÃÕ¤¸ñ(Grids)_ʹÓÃÈ¡¾°( Pan)ºÍËõ·Å(Zoom)_ ³£ÓòÎÊýµÄÉèÖÃPADS Logic ÖеĽ»»¥²Ù×÷¹ý³ÌPADS LogicʹÓñê×¼Windows·ç¸ñµÄ²Ëµ¥(Menu)ÃüÁʽ£¬È絯³ö²Ëµ¥(Pop-up Menus)¡¢Èȼü(Shortcut Keys)¡¢¹¤¾ßÌõ(Toolbars)ºÍ¹¤¾ßºÐ(Toolboxes)Ö´ÐÐÃüÁî¡£ÔÚ ±¾ ½Ì ³Ì ÖÐ £¬ ʹ Óà Ï À- ²Ë µ¥ (Pull-down) µÄ Ãü Áî ¸ñ ʽ ÊÇ²Ë µ¥/ÃüÁî(Menu/Command)¡£ÀýÈ磬ʹÓÃÎļþ²Ëµ¥ÖеĴò¿ªÎļþÃûΪÎļþ/´ò¿ª(File/Open)¡£µ¯³ö²Ëµ¥(Pop-up Menus)PADS LogicʹÓõ¯³ö²Ëµ¥(Pop-up Menu)ÃüÁ°´Êó±êÓÒ¼üÏÔʾ¿ÉÒÔÖ´ÐеÄÃüÁ»òÕß¿ÉÒÔÑ¡ÔñµÄÄ¿±êÏîÄ¿¡£1. ÔÚ PADS Logic ´°¿ÚÄÚµÄÈκεط½°´Ò»ÏÂÊó±ê£¬»÷»îÕâ¸ö´°¿Ú¡£2. °´Êó±êÓÒ¼ü£¬µ¯³ö²Ëµ¥(Pop-up Menu)½«³öÏÖÔÚÊó±êµÄλÖô¦£¬Õâ¸öµ¯³ö´°¿Ú£¬¿ÉÒÔÈÃÄú¿ìËÙ½øÐйýÂËÆ÷µÄÑ¡Ôñ£¬»òÕßÄúÒ²¿ÉÒÔͨ¹ý Filter…×ÔÐÐÑ¡ÔñÅäÖùýÂËÏîÄ¿¡£HK +852-******** SZ 755-88859921 SH 21-5108 7906 BJ 10-5166 5105support@4¹¤¾ßÌõ(Toolbars)ºÍ¹¤¾ßºÐ(Toolboxes)PADS Logic ʹÓà Windows ±ê×¼µÄ¹¤¾ßÌõ(Standard Toolbars)ºÍ¹¤¾ßºÐ(Toolboxes)Éè¼Æ(Design)¹¤¾ßºÐ £¬¸Ã¹¤¾ßºÐ°üº¬¹¤¾ßÌõºÍÑ¡Ôñ(Selection)¹¤¾ßºÐ £¬¸Ã¹¤¾ßºÐ°üº¬¹¤¾ßÌõÕâЩͼÐδú±íÁËÓÐЧµÄÃüÁ³ÆΪͼ±ê(Icons)¡£¹¤¾ßÌõ(To olbars)λÓڲ˵¥À¸(Menu Bar)µÄÏÂÃæ¡£ÎÞÄ£ÃüÁî(Modeless Commands)ºÍ¿ì½Ý¼ü(Shortcut Keys)ÎÞÄ£ÃüÁî(Modeless Commands)ºÍ¿ì½Ý¼ü(Shortcut Keys)ÔÊÐíÄúͨ¹ý¼üÅÌ Ö±½ÓÊäÈëÃüÁî¼°ÆäÑ¡Ïî¡£Àý£º±ê×¼µÄWindows¿ì½Ý¼ü£¬ÈçAlt-F ÓÃÓÚÏÔʾÎļþ²Ëµ¥µÈÃüÁÔÚ PADS Logic ÖРͬ Ñù ÓРЧ ¡£ ¹Ø ÓÚ ¾ßÌåµÄ ÎÞ Ä£ÃüÁî¿É ´ò¿ª°ïÖú²Ë µ¥(Help)Ï µÄModeless Commands Ñ¡Ïî½øÐв鿴¡£È¡ÏûÃüÁî²Ù×÷Äú¿ÉÒÔÔÚÈκÎʱºò£¬Í¨¹ý°´¼üÅÌÉϵÄEsc ¼ü»ò°´Êó±êÓÒ¼ü²¢´Óµ¯³ö²Ëµ¥(Pop-up Menu)ÖÐÑ¡ÔñÈ¡Ïû(Cancel)ÃüÁȡÏûµ±Ç°µÄÃüÁîºÍÃüÁîÐòÁС£HK +852-******** SZ 755-88859921 SH 21-5108 7906 BJ 10-5166 5105support@5ʹÓù¤×÷¿Õ¼äPADS LogicµÄ¹¤×÷¿Õ¼äΪ56Ó¢´çx 56Ó¢´ç¡£¹¤×÷¿Õ¼äµÄÔ-µã(0,0)ÓÃÒ»¸ö°×É«µÄСԲµã±íʾ¡£Ô-µãλÓÚÒ³ÃæµÄ×óϽǡ£Ò»¸ö´óµÄ°×É«µÄ¾ØÐδú±íÒ³ÃæµÄÇøÓò¡£³ß´ç B µÄÔ-ÀíͼµÄÃæ»ýÊÇ 11 Ó¢´ç x 17 Ó¢´ç£¬³ß´ç C µÄÒ³ÃæÊÇ17Ó¢´çx 22Ó¢´çµÈµÈ¡£µ±Äú½«¹â±ê(Cursor)ÔÚ¹¤×÷ÇøÓòÄÚÒƶ¯Ê±£¬ËüËùÔÚλÖõÄX/Y¾ø¶Ô×ø±êÖµ½«¶¯Ì¬µØÏÔʾÔÚÆÁÄ»µ×²¿µÄ״̬Ìõ(Status Bar)ÄÚ¡£¹¤×÷ÇøÓòÁ·Ï°1. ½«¹â±ê·ÅÖÃÔÚÔ-µã£¬×¢Òâ0,0×ø±êÖµÓ¦¿ÉÒÔÔÚ״̬Ìõ(StatusBar)¶Á³ö¡£2. ÔÚ¹¤×÷ÇøÄÚÒƶ¯¹â±ê£¬×¢ÒâX/Y×ø±êÖµÓ¦¸ÃËæ׏â±êµÄλÖöø¸Ä±ä¡£ÉèÖÃÕ¤¸ñ(Grids)PADS LogicÓÐÁ½ÀàÕ¤¸ñ(Grid)£ºÉè¼ÆÕ¤¸ñ(DesignGrid)ºÍÏÔʾդ¸ñ(Display Grid)¡£Éè¼ÆÕ¤¸ñ(Design Grid)Éè¼ÆÕ¤¸ñ(DesignGrid)Ö¸µÄÊǹâ±êÿÒƹýһС¸ñµÄ¾àÀ룬ȷ¶¨Ôö¼ÓÔª¼þ(Parts)ºÍÁ¬Ïß(Connections)µÄ¼ä¸ôºÍת½ÇµÄλÖá£Õâ¸öÕ¤¸ñÓÃÓÚ»æÖÆÏîÄ¿£¬Èç¶à±ßÐÎ(Polygons)¡¢²»·â±ÕͼÐÎ(Paths)¡¢Ô²(Circles)ºÍ¾ØÐÎ(Rectangles)¡£᳔СµÄÕ¤¸ñÉèÖà ÊÇ 2mils¡£Ñ¡Ôñ¹¤¾ß/Ñ¡Ïî(Tools/Options)ÃüÁ²¢ÇÒÑ¡ÔñÉè¼Æ(Design)±êÇ©¿ÉÒÔ¹Û ²ìµ½µ±Ç°µÄÉè¼ÆÕ¤¸ñ(Design Grid)ÉèÖÃÇé¿ö¡£HK +852-******** SZ 755-88859921 SH 21-5108 7906 BJ 10-5166 5105support@6 PADS Logic ½Ì³ÌÏÔʾդ¸ñ(Display Grid)ÕâÊÇÒ»ÖÖµã×´µÄÕ¤¸ñ£¬ÓÃÓÚÉè¼ÆµÄ¸¨Öú¡£Äú¿ÉÒÔÉèÖÃÏÔʾդ¸ñ(Display Grid) ÓëÉè¼ÆÕ¤¸ñ(Design Grids)Æ¥Å䣬»òÕßÄú¿ÉÒÔÉèÖÃËüΪÉè¼ÆÕ¤¸ñ(DesignGrids)µÄ±¶Êý¡£Ñ¡Ôñ¹¤¾ß/Ñ¡Ïî(Tools/Options)ÃüÁ²¢Ñ¡ÔñÈ«¾Ö(Global)±êÇ©£¬²é¿´µ±Ç°µÄÏÔ Ê¾Õ¤¸ñ(Display Grid)ÉèÖá£ÎªÁ˹رÕÏÔʾդ¸ñ(DisplayGrid)£¬¿ÉÒÔÉèÖÃÏÔʾդ¸ñ(Display Grid)СÓÚ10¡£µ«Õâ²¢²»ÊÇÕæÕýµÄÈ¡Ïû£¬³ý·ÇÄúÓÃËõ·Å(Zoom)½«Ò»¸öСÇøÓò·Å´óºÜ¶à±¶£¬·ñÔòÄúÊÇ¿´²»µ½ËüµÄ¡£HK +852-******** SZ 755-88859921 SH 21-5108 7906 BJ 10-5166 5105support@7 PADS Logic ½Ì³ÌÕ¤¸ñÁ·Ï°(Grid Exercise)ÿ¸öÕ¤¸ñ¶¼ÊÇÔÚ¹¤¾ß²Ëµ¥(ToolsMenu)Ï£¬Í¨¹ýÑ¡Ïî(Options)ÃüÁî»òÕßʹÓÃÎÞÄ£(Modeless)ÃüÁîµ¥¶ÀÉèÖõġ£ÔÚÏÂÃæµÄÁ·Ï°ÖУ¬Äú½«Ê¹ÓÃÎÞÄ£(Modeless)ÃüÁîÉèÖÃÉè¼ÆÕ¤¸ñ(DesignGrid)ºÍÏÔʾդ¸ñ(Display Grids)¡£1. ¶ÔÓÚÏÔʾդ¸ñ(Display Grid)£¬¼üÈë×Ö·ûGD£¨²»Çø·Ö´óСд×Öĸ£©¡£ÔÚ×Ö ·û´°¿Ú½«ÏÔʾһ¸öÖ±½Ó(Modeless)ÃüÁ²¢ÏÔʾ GD ×Ö·û¡£2. ¼üÈë 500£¬²¢ÇÒ°´»Ø³µ(Enter)¡£×¢Ò⣺ÄúÒ²ÐíÐèÒª·Å´ó(Zoom in)»òËõС(Zoom out)£¬ÒԱ㿴µ½Õ¤¸ñ(Grid)¡£HK +852-******** SZ 755-88859921 SH 21-5108 7906 BJ 10-5166 5105support@8 PADS Logic ½Ì³ÌÄÜ·ñÓÐЧµØ¿´µ½Õ¤¸ñ(Grid)È¡¾öÓÚÊäÈëµÄÕ¤¸ñ(Grid)Öµ¡£²Î¿¼Ê¹ÓÃÈ¡¾°ºÍËõ·Å (Using Pan and Zoom)¡£Äú¿ÉÒÔÒ»²½¼üÈëG500£¬È»ºó°´»Ø³µ(Enter)£¬ÉèÖÃÉè¼ÆÕ¤¸ñ(Design Grid) ¡£Èç¹ûÄú²»ÄÜ¿´µ½Õ¤¸ñ(Grid)£¬ÊÔͼ·Å´ó(Zoomingin)»òËõС(Zooming out)¡£²Î ¿¼ÏÂÒ»½Ú“ʹÓÃÈ¡¾°ºÍËõ·Å(Using Pan andZoom)¡£”×¢Ò⣺ÔÚÎÞÄ£(Modeless)ÃüÁîºÍÖµ(V alue)Ö®¼ä᳔ºÃ¼ÓÒ»¸ö¿Õ¸ñ(Space)¡£Í¨¹ýÉèÖÃ/²ÎÊý(Setup/Preferences)µÄÆäËü¿ØÖÆ·½·¨Í¬ÑùÊÇÓÐЧµÄ¡£Ê¹ÓÃÈ¡¾°(Pan)ºÍËõ·Å(Zoom)Óм¸ÖÖ·½·¨¿ÉÒÔ¿ØÖÆÉè¼ÆͼÐεÄÏÔʾÖÐÐÄ¡¢·Å´óºÍËõС¡£ÔÚÕâ¸öÁ·Ï°ÖУ¬ÎÒ ÃÇʹÓÃÊó±ê(Mouse)¡£Ê¹ÓÃÁ½¼üÊó±ê(Mouse)£¬¿ÉÒÔ´ò¿ªºÍ¹Ø±ÕËõ·Å(Zoom)ͼ±ê¡£ÔÚËõ·Å(Zoom)·½Ê½Ï£¬µã»÷Êó±ê×óÓÒ¼ü·Ö±ð½øÐзŴóºÍËõСµÄ²Ù×÷¡£Ê¹ÓÃÈý¼üÊó±ê(Mouse)£¬Öмä¼üµÄËõ·Å(Zoom)·½Ê½Ê¼ÖÕÊÇÓÐЧµÄ¡£·Å´ó(Zooming in)ºÍËõС(Zoomingout)ÊÇͨ¹ý½«¹â±ê·ÅÔÚÇøÓòµÄÖÐÐÄ£¬°´×¡Êó±ê×ó¼üÈ»ºóÍϳöÒ»¸öÇøÓò½øÐеģ¬µ±Êó±êÍùϵķ½ÏòÍ϶¯Ê±£¬¿ÉÒÔ½øÐÐËõС²Ù×÷£»µ±Êó±êÍùÉϵķ½ÏòÍ϶¯Ê±£¬¿ÉÒÔ½øÐзŴóµÄ²Ù×÷¡£È¡¾°(Pan)ºÍËõ·Å(Zoom)¹¦ÄÜ»¹¿ÉÒÔͨ¹ý²é¿´²Ëµ¥(ViewMenu)ʹÓÃÃüÁͨ。

pads个人学习笔记

课程安排:Pgup 放大Pgdn 缩小(以坐标中心为基准)(ctrl+滚动滑轮;按住滚动滑轮拖动)G50 移动栅格GD100 显示栅格end 刷新esc 返回,退出s+空格+名字查找Sx1空格y1 定位回车(输入)空格(确定)ctrl+e 移动ctrl+r 旋转del 删除设置一段时间自动保存文件在Pads Layout 9.3的tool -> options->Grobal选项的左下方有一个有一个automatic backups,可以设置间隔时间和备份文件个数一,Logic(5副)知识1.注释框1)页面大小设置:Tools—options—design—size2)Tools—options—general—style—full screan3)作图栅格设置G50 移动栅格GD100 显示栅格4)设置页数Setup—sheets5)如果选不中?万能法则:右键—select anything6)画注释框:A)2D线—右键宽度;多边形,圆,矩形,直线;直角,45度,任意角度(多边形与矩形不可填充颜色:双击边框—filled勾上)B)修改2d线(右键pull arc)C)加注释字:添加注释添加分类D)颜色设置Setup—display colors7)保存注释框全选—右键—combine合并(explode 解散)—右键—save to library8)从库里调出注释框--选库--*名字*知识2.建库1.Logic库File—libraly—creat new lib(选路径,建文件夹名为库,建文件名为logic)2.添加库File—libraly—manage lib list(选路径,选文件夹名为库,选文件名为layout)--add知识3.添加元器件及联线1)--选库,元器件名(*res*电阻,*cap*电容,*diode*二极管,*2n*三极管,*led*发光二极管,*7805*三端稳压,*80cxx*单片机)2)联线---引线出(右键—power电源,ground地,off page 网络标号)知识4.做原器件-----确定---G50 gd100 设置栅格添加引脚复制—右键--修改引脚设置引脚编号修改引脚编号设置引脚名修改引脚名引脚类型设置引脚属于哪个门排列顺序-----编辑电器属性---家族--添加pcb1.门数量设置--引脚设置--特殊属性设置File----选库—命名。

PADS学习笔记

要在setup-->Preferences,在Routing中的选择Layer Pair层对,例如,想在第2层与第3层打盲孔,就要first选层2,second选择3。如果是想在

1.画好板后检查连线正确与否的方法:在TOOS菜单下点Verify Dsign,在弹出来的对话框中选择connectivi....即Check中的第二项。

它的操作相当于protel中的DRC电气检测。

2.无模命令T设置PCB视图为透明显示与普通显示的切换。

3.选中元件,按CTRL+R可以旋转元件。按F2会画出直线,选中元件,再按ctrl+j可以在同两个脚上的以面画线,要是不这样操作只能画一面的线

二是setup-->Preferences,在Drafting中的Flood中的smoothing值改小即可,例如0.5改成0.4。三是有时铺铜时出现死软件的时候,也可以用以上

两种方法,但是有时两种都不行,这时就把上面两种方法混合使用,即两个设置都改;第四种解决方法是把PCB用export导出.asc文件,然后再

的Linear中填入要显示的小数个数就可以了

10.想统一改元件名称字体的大小,先选择select Documenttation,再在EDIT菜单下选择find命令,在弹出来的框中下拉选择Label Fonts,点中中间的PADS stroke Font,看到右边那个框有东西显示

,然后勾选add to selection,然后点击APPLY,再按Ctrl+Q(或是点击右鍵,选中修改)写入要改的字体大小,再按OK就行了.,再按OK就行了.

PADS教程(1-21)

PADS教程(1-21)第一节 - 图形用户界面(GUI)PADS Layout的用户接口具有非常易于使用和有效的特点。

PADS Layout 在满足专业用户需要的同时,还考虑到一些初次使用PCB软件的用户需求。

教程的这节将将覆盖以下内容:· 使用 PADS Layout 进行交互操作· 工作空间的使用· 设置栅格(Grids)· 使用取景(Pan)和缩放(Zoom)· 面向目标(Object Oriented)的选取方式使用 PADS Layout进行交互操作PADS Layout 使用标准的 Windows 风格的菜单(Menus)、字符感应(亦称上下文相关的)(Context-sensitive)的弹出菜单(Pop-up Menus)、热键(亦称快捷键)(Shortcut keys)、工具条(Toolbars)和工具盒(Toolboxes)执行命令。

在整个教程中,从下拉菜单执行命令的使用格式是菜单 / 命令(Menu/Command)。

例如从文件菜单(File menu)选择打开(Open)命令,选择文件/打开(File/Open)。

工具条(Toolbars)和工具盒(Toolboxes)PADS Layout 使用Windows 标准的工具条(Toolbars)和工具盒((Toolboxes)—绘图工具盒(Drafting Toolboxes)设计工具盒(Design Toolboxes)尺寸标注工具盒(Automatic Dimensioning Toolboxes)ECO工具盒(ECO T oolboxes)BGA工具盒(BGA Toolboxes)这些工具盒是一些图标(Icons)的集合,每个图标代表了有效的命令。

工具条(Toolbars)放在菜单条的下面。

你可以通过选择PADS Layout 工具条(Toolbars)中的工具盒(Toolboxes)按钮,打开代表命令集的工具盒((Toolboxes),或者通过选择Window 菜单工具条命令。

PADS学习方法

PADS学习方法交流

有很多初学者由于学习方法不对,导致学习慢学习吃力,原因就是方法不对和没有坚持不断地学习直到学会为止。

以下是个人的学习PADS的经验,仅供大家参考。

希望对初学者有帮助。

1.首先要了解用PADS画原理图和PCB的流程,有很多人不了解流程,不知道从何开始学习,流程大慨为:画封装,画原理

图符号,建元件,建元件库,画原理图,导入生成PCB,画外形边框,布局,布线,设计检验,生成GERBER.

2.了解了流程后就要开始看资料或者看视频讲解一步一步的按照流程中需要掌握的学习,把流程走一遍。

3.找一块完整的简单项目从头到尾地按照流程画一块完整的PCB。

在画的过程中,你会碰到很多问题,这时需要不断的问或

者查资料看教程来解决在画的过程中碰到的问题,直到项目画完。

4.总结在画的过程中慢的地方,找到最快的操作方法和技巧,学会总结一些快捷键。

5.经常练习,给自己规定一个时间在时间内完成,提高自己的速度和熟练程度。

6.学习一些布线规则和一些生产工艺,以确保画出来的PCB无论是性能还是工艺最好。

7.建立积累自己的元件库,为后续画其他的PCB板做准备,可以避免再去重新做元件而浪费时间。

8.介绍一个学习PADS的网址给大家,里面有很多好的学习资料,尤其是一些视频讲解资料和PADS的技巧,和大家分享,

希望对大家有帮助。

下载方法,点击电信下载后进入另外一个页面,再点击下载,下载的为EXE文件,再在电脑上运行安装此文件就会自动将资料下载到电脑上。

PADS技巧性操作

PADS技巧性操作PADS(Physical Activity Daily Situations)是一种提高技巧性操作能力的训练方法,它通过日常生活活动中的各项任务,让个体获得更强的技巧性操作能力。

以下是一些在PADS训练中的技巧和练习方法,共计1200字以上。

1.抓握与手指力量训练:-抓握练习:使用不同材质和形状的物品进行抓握练习,如橡皮球、海绵、纸杯等,每天进行20分钟的练习。

-手指力量训练:使用各种手指力量训练器材进行练习,如弹簧夹子、手指力量球等,每天进行10-15分钟的练习。

2.平衡与协调训练:-单脚站立:每天进行10分钟的单脚站立练习,可以选择不同的站立姿势,如站立、闭眼、抬腿等。

-平衡板训练:使用平衡板进行平衡训练,每天进行15-20分钟的练习,可进行前后、左右摇晃的练习。

3.眼手协调训练:-真实物体练习:使用各种真实物体进行眼手协调练习,如抛接球、拼图、拧瓶盖等,每天进行15分钟的练习。

-电子游戏练习:使用各种电子游戏进行眼手协调训练,如打字游戏、打篮球游戏等,每天进行20分钟的练习。

4.空间意识与精确度训练:-空间意识练习:使用各种材料进行空间意识练习,如搭积木、建造模型等,每天进行15-20分钟的练习。

-精确度训练:使用各种目标物进行精确度训练,如投掷、射击等,每天进行15分钟的练习。

5.反应速度训练:-反应球练习:使用反应球进行反应速度训练,每天进行20分钟的练习,反应球的速度可以逐渐增加。

-视觉训练:使用不同的光线和颜色进行视觉训练,如观察图片、追踪移动物体等,每天进行15分钟的练习。

6.肌肉记忆训练:-手指舞蹈训练:通过练习特定的手指动作和舞蹈动作,训练手指的肌肉记忆,每天进行15-20分钟的练习。

-敲击乐器训练:使用各种敲击乐器进行敲击训练,训练手指的肌肉记忆和协调能力,每天进行15分钟的练习。

7.心理训练:-冥想训练:每天进行10-15分钟的冥想训练,通过放松和专注来提高心理集中能力。

PADS最最最最易教程

PADS最最最最易教程PADS是一种非常流行的电路设计和仿真软件,用于帮助工程师设计电路板和进行电路仿真。

在本教程中,我将向您介绍PADS的基本概念和操作步骤,帮助您快速入门PADS。

接下来,让我们先了解PADS的用户界面。

当您第一次启动PADS时,您将看到一个主要的控制面板。

这个面板上有各种功能区域,如导航栏、工具栏和资源管理器。

您可以使用这些区域的不同工具来创建和管理您的电路设计。

首先,让我们创建一个新的电路设计。

在资源管理器中,右键单击“工程”文件夹,并选择“新建工程”。

为您的工程选择一个名称,并指定保存位置。

然后点击“创建”按钮。

现在,您可以开始设计您的电路了。

在工具栏中,您将找到各种功能按钮,如放置元件、绘制线路和修改元件属性等。

您还可以使用菜单栏中的各种命令来执行特定的操作。

在放置元件之前,您需要先选择一个元件库。

PADS提供了许多预定义的元件库,您可以根据您的需求选择适当的库。

选择一个库后,您可以从工具栏中的“放置元件”按钮开始放置元件。

在放置元件时,您可以使用鼠标左键单击来放置元件,并使用右键单击来选择或取消选择元件。

您还可以使用键盘上的快捷键来切换不同的放置模式。

完成元件放置后,您可以开始绘制线路。

在工具栏中选择“画线”按钮,并使用鼠标左键单击来将线路连接到元件的引脚上。

您还可以使用右键单击来选择线的类型和属性。

完成电路设计后,您可以保存并导出您的设计文件。

在菜单栏中选择“文件”>“保存”来保存您的设计。

您还可以选择“文件”>“导出”来导出设计文件到其他格式,如PDF或DXF等。

在本教程中,我们只提到了一些PADS的基本操作步骤和功能。

PADS是一个非常强大且复杂的软件,还有很多高级功能和技巧需要进一步学习和掌握。

如果您对PADS感兴趣,建议您参考PADS的官方文档和在线教程,了解更多高级功能和用法。

希望这个简短的PADS教程能够帮助您开始使用PADS并进行电路设计。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

1. pads学习方法交流有很多初学者由于学习方法不对,导致学习慢学习吃力,原因就是方法不对和没有坚持不断地学习直到学会为止。

以下是个人的学习pads的经验,仅供大家参考。

希望对初学者有帮助。

首先要了解用pads画原理图和pcb的流程,有很多人不了解流程,不知道从何开始学习,流程大慨为:画封装,画原理图符号,建元件,建元件库,画原理图,导入生成pcb,画外形边框,布局,布线,设计检验,生成gerber. 2.3. 了解了流程后就要开始看资料或者看视频讲解一步一步的按照流程中需要掌握的学习,把流程走一遍。

找一块完整的简单项目从头到尾地按照流程画一块完整的pcb。

在画的过程中,你会碰到很多问题,这时需要不断的问或者查资料看教程来解决在画的过程中碰到的问题,直到项目画完。

4.5.6.7.8. 总结在画的过程中慢的地方,找到最快的操作方法和技巧,学会总结一些快捷键。

经常练习,给自己规定一个时间在时间内完成,提高自己的速度和熟练程度。

学习一些布线规则和一些生产工艺,以确保画出来的pcb无论是性能还是工艺最好。

建立积累自己的元件库,为后续画其他的pcb板做准备,可以避免再去重新做元件而浪费时间。

介绍一个学习pads的网址给大家,里面有很多好的学习资料,尤其是一些视频讲解资料和pads的技巧,和大家分享,希望对大家有帮助。

下载方法,点击电信下载后进入另外一个页面,再点击下载,下载的为exe文件,再在电脑上运行安装此文件就会自动将资料下载到电脑上。

篇二:pads学习学会orcad和pads layout软件的基本使用步骤,orcad(找元件,定参数,添加库,生成链接文件,放大缩小、删除等基本操作等等),pads layout( 导入链接文件、设置各种规则,布局、布线、检查等等) 利用上面学到的完整的画一个简单的电路图。

先把整个流程过一遍。

pads logic,是设计电子电路图,原理图的工具,pads layout是设计pcb,pcb布局,布局,到gerber file,pads router是自动布线工具,附助pcb layout布线的工具。

建议用orcad画原理图,pads layout 进行pcb布局,布线当你将一个元件叠放在另一个元件上时,出现元件后退现象,说明两个元件在同一层,是报警的意思!要改变其中一个元件的层属性。

ctrl+click 同时选择 u1 和 c1。

:click是点击的意思。

1:为了移动原点,选择设置/设置原点(setup/set origin),在工作空间的某处按一下鼠标,这点将作为新的原点。

2:ctrl+enter:打开options 3:循环选择(cycle pick) 当你在一个工作区域按鼠标时,而目标处有多个目标切密度很高,选择一个目标也许要试许多次。

为了减少尝试选择的次数,你可以接受第一个选择,然后循环将哪个位置处所有的目标依此被选中。

1. 将光标放在u1 的脚28 上,然后选择它。

2. 重复按键盘上的tab 键,在管理脚28 处的各种可选目标将循环出现。

当你希望的目标出现后停止选择。

4:cae封装(cae decal),在pads 库中的一个逻辑符号,或称为cae封装(cae decal). 5: ctrl+e:移动(先选中)ctrl+i:用光标任意角度旋转(spin)元件ctrl+f,元件将返回到主元件面7.打入ss u1,并且按回车(enter),使用搜索(search)和选择(select)直接命令,搜索(search)并且选择元件u1 8:输入 ss u* 在选中、在按ctrl+e、输入s 100 100。

第一:查找选中你要搜索的器件,(如果查找的是联合体,则事先要选择选中联合体unions,然后点击)第二:移动的快捷方式,第三要移动到的具体坐标。

9:元件摆放对齐操作,选中一排或一列元件,点击鼠标右键,从弹出菜单中选择align。

或者使用快捷键方式ctrl+l,、这时将弹出 align parts 对话框,根据你需要对齐的方式。

10: 顺序地(sequentially)放置器件,1. 同时选中r1、r2和r5。

2. 在powerpcb 中,从弹出菜单(pop-up menu)中选择顺序移动(move sequential),proceed with next object? 提示将出现。

3. 选择yes to all。

组内的第一个元件将粘附在光标上。

一旦元件放置完后,组内的下一个元件将自动地粘附在光标上。

4. 在下列位置放置电阻(resistors): r1 2050, 550r2 2050, 1200r5 400, 1550 11:不要输入网表而直接添加一些元件和连线,建立一个新的设计,这就是空中飞入法(on thefly)-------------------------------------------------------------------------117接11当你在更新eco功能后,并且在logic导入文件后,原理图还是没有更改,这时可以采取在logic中---layout link-----design--------eco from pcb.在logic中导入。

12:改变画线角度的其它方法是使用无模命令,ao 对应正交方式(orthogonal)、ad 对应对角方式(diagonal)以及aa 对应任意角度(any angle)。

13:使用无模命令键入 r8,设置实际显示宽度为8 mils,则所有等于或大于8 mils 宽度的线和导线将以实际宽度显示。

14:键入直接命令n 24mhz,并且按回车(enter),高亮24mhz 网络. 15:开始布线(routing)从弹出菜单(pop-up menu) 中点中选择导线/ 管脚/ 未布的线(selecttraces/pins/unroutes)。

16:改变层的操作,采用和添加拐角相同的操作,只是按着shift 键再按鼠标即可。

层的改变能够在布线时当前光标位置处,或者在上一个拐角的位置处进行。

或者按f417:dblclick是doubleclick的简写,中文意思为“双击”18.完成布线19:规则检查(on-line drc), 你可以在工具/选项(tools/options)的design 页面对话框中设置drc 方式(drc modes),或者通过dr*无模命令。

有四种基本的 drc 方式:drc off指明不进行检查。

在布局(placement)和布线(routing)期间的(关闭drc) 规则的冲突(violation)是允许的。

安全间距(clearance)冲突(violations)和插入(intersection)导线是不禁止的。

直接(modeless)命令是dro。

drc ign clr 在布线(routing)期间,防止导线的插入,但是其它的工作同(忽略drc) drc off 一样。

你可以从drc ignore clearance 状态快速地切换到drc prevent 状态,它比从drc off 状态切换到drc prevent状态要快一点,因为drc ignore clearance 是drc prevent 的一个子集,而drc off 不是。

直接(modeless)命令是dri。

drc warn在布局(placement)和布线(routing)期间,生成出错信息报告,(drc 告警) 但是允许你继续建立空间冲突(violations)。

在drc warning方式下的布线(routing)和布线修改(routemodification)禁止建立冲突(violations)或导线插入(trace intersections),就象drcprevent 一样。

直接(modeless)命令是drw。

drc prevent 在布局(placement)、布线(routing)和布线修改(route(drc 防止) modification)期间,禁止建立冲突(violations)。

直接(modeless)命令是drp。

20:在画线时即线黏在鼠标上时,ctrl+左击=结束当前布线,该方式有三种模式,1结束点什么都没有,2结束点有焊盘,3结束点有测试点。

(。

ctrl+click 在光标处以有过孔(via)或无过孔(via) 模式结束布线。

可以在画线状态下右击选中 end via mode来选择接收方法) shift+左击=加一个焊盘跳到另一次层去。

(shift+click 在当前光标处插入一个过孔(via)并且改变当前层) 21:动态布线(dynamic route)图标。

22:设置布线栅(routing grid)和过孔栅格(via grid)为25,键入g25,并且按回车(enter)。

23:取消和进行元件锁定功能,先选择元件选定功能--全选--alt+enter弹出器件属性菜单选中glued 24:默认线宽按照布线规则设定值,要更改线宽可以双击走线或者在走线时输入命令w **即可更改现行线宽。

25:测量距离的方法:第一设置design grid栅格为1,比如你要测量a到b点的距离,指针移动到a点,然后按键盘q键后按回车,跟着把针移动到b点,这时指针的右下角会相应显示你所测量的距离(d=**),并且指针在移动的过程中会拉出一条线以方便直观!26:画封装的(向导)tool-pcb decal edit进入封装编辑模式,选择选择进入向导模式,,在第五节–定义设计规则(defining design rules) ·设置pcb 各层的定义(layerarrangement)----------------------------------------75 增加板子的层数-------------------------------------------------------------------------75 设置层的排列(layer arrangement)和命名(names)-----------------------------77 设置层的stackup----------------------------------------------------------------------79·设置缺省的安全间距规则(clearancerules)----------------------------------------80 设置缺省的布线规则(default routingrules)------------------------------------82 ·设置网络的安全间距规则(netclearance rules)-----------------------------------83 ·设置条件规则(conditionalrules)-----------------------------------------------------85 ·设置层的显示颜色(layer colors)-----------------------------------------------------87显示元件管脚号(7以上版本)-------------------------------------88 指定其它项目的颜色--------------------------------------------89 第六节内容:本节中你将学到以下内容:·设置通过原点移动(move)-------------------------------------------------------------91 通过光标点位置、原点、中心的、·使用属性(properties)命令改变元件放置的状态(status)----------------------99 第七节内容:在这一节中,你将学习:·放置晶体管(transistors)和去耦电容(filtercapacitors)-----------------------111 ·进行元件的极坐标方式布局(radialplacement)-------------------------------111 ·对齐元件----------------------------------------------------114 第八节– eco (engineening change order)工程更改--------------116 在这一节中,你将学习:·管脚和门的交换(swap pin/swap gate)--------------------------121 在pcb更改后更新你的 pads logic 原理图操作-------------------118 第九章–布线编辑(route editing) pads layout 具有几个交互式的和半自动的布线工具,用于缩短设计时间。