低功耗物门控时钟的三种功耗分析

门控时钟 低功耗芯片设计方案

门控时钟低功耗芯片设计方案全文共四篇示例,供读者参考第一篇示例:门控时钟低功耗芯片设计方案随着物联网技术的飞速发展,原本以人类为中心的智能家居和智能办公等应用场景也逐渐普及,门控时钟低功耗芯片成为这些智能设备的重要组成部分。

门控时钟低功耗芯片设计方案要求具有高性能、低功耗、稳定可靠等特点,以满足现代智能设备对芯片性能的需求。

1. 高性能:门控时钟低功耗芯片需要具有高性能的时钟控制功能,能够对设备的时序信号进行准确控制,确保设备的正常运行。

2. 低功耗:门控时钟低功耗芯片需要具有低功耗的特点,以延长设备的使用时间,提高设备的续航能力。

3. 稳定可靠:门控时钟低功耗芯片需要具有稳定可靠的性能,能够在各种工作环境下保持稳定的工作状态,确保设备的正常运行。

4. 外设接口丰富:门控时钟低功耗芯片需要具有丰富的外设接口,以支持设备与其他外部设备的连接和通讯。

5. 易集成:门控时钟低功耗芯片需要具有易于集成的特点,能够方便地与其他组件进行接口连接,实现功能的扩展和定制。

1. 芯片选用:在选择芯片时,可以考虑采用低功耗的CMOS工艺制程,以降低整体功耗。

可以选择具有高性能和稳定可靠性的时钟控制器芯片,以确保时序信号的准确控制。

2. 功耗优化设计:在芯片设计过程中,可以采用功耗优化设计策略,通过降低功耗模块的工作频率、优化电源管理电路等方式,降低整体功耗,延长设备的续航时间。

3. 时钟控制算法优化:通过优化时钟控制算法,可以提高时钟控制的准确性和稳定性,确保设备的正常运行。

可以提供丰富的时序控制功能,以满足不同应用场景对时序信号的需求。

4. 外设接口设计:在芯片设计中,可以设计丰富的外设接口,如UART、SPI、I2C等接口,以支持设备与其他外部设备的连接和通讯。

可以提供GPIO接口和PWM输出等功能,实现设备的功能扩展和定制。

5. 集成设计:在芯片设计中,可以将时钟控制器、功耗管理电路、外设接口等功能集成到同一芯片中,实现功能的集成和有效管理。

基于门控时钟的CMOS电路低功耗设计

基于门控时钟的C MOS 电路低功耗设计罗 罹(安徽大学计算机科学与技术学院,安徽合肥 230039)摘 要:阐述了如何运用门控时钟来进行C MOS 电路的低功耗设计。

分析了门控时钟的实现方式,如何借助E DA 工具在设计中使用门控时钟,并且附有部分脚本程序,以一个watchdog ti m er模块为例,给出了相关的功耗分析报告和优化结果。

这样,可以借助E DA 工具的帮助,在综合时插入门控时钟,较大幅度地降低功耗,同时附带减小面积,为使用门控时钟进行低功耗设计者提供有益的参考。

关键词:低功耗;门控时钟;泄漏中图分类号:T N431.2 文献标识码:A 文章编号:1000-2162(2005)03-0021-04通常在C MOS 电路设计中,面积和速度是最为重要的性能指标。

目前,随着嵌入式设备和手持设备的普及,由于电池的大小和重量的限制,决定了电池的供电量有限,因此降低功耗成为很紧迫的问题。

设备功耗中的很大一部分是采用C MOS 工艺设计的芯片所引起的。

因此,降低C MOS 电路的功耗很有意义,功耗也成为C MOS 电路设计中一个重要的性能指标。

C MOS 电路的低功耗设计的概念和方法学应运而生,成为目前超大规模集成电路设计中的一个重要方向。

C MOS 电路的低功耗设计有很多方法,主要有:降低供电电压、使用门控时钟等。

但是降低供电电压,会带来很多副作用:首先,降低供电电压,会导致速度下降,减小电容充放电的电流或负载驱动电流;其次,会导致较低的输出功率或较低的信号幅度,从而产生噪声和信号衰减的问题。

相比之下,门控时钟是一个很有效的方法。

门控时钟可以有效地对某些较少使用的时序逻辑进行开关控制,从而大大降低功耗[1]。

本文将以一个watchdog ti m er 模块为例,使用Synop sys 公司的综合工具DesignComp iler,详细阐述如何在设计中插入门控时钟,并且给出了使用的脚本,通过详细的分析报告,特别是使用门控时钟前后的功耗对比,相信可以为工程师使用门控时钟进行低功耗设计提供有益的参考。

低功耗集成电路设计中的时钟与功耗优化方法研究

低功耗集成电路设计中的时钟与功耗优化方法研究随着科技的不断进步,集成电路设计已经成为现代电子产品的核心。

在设计过程中,时钟与功耗优化是至关重要的两个方面。

本文将探讨低功耗集成电路设计中的时钟与功耗优化方法,并分析其在实际应用中的效果。

一、时钟优化方法1.1 时钟频率调整在集成电路设计中,时钟频率是一个重要的参数。

过高的时钟频率会导致功耗增加,而过低的时钟频率则会影响电路性能。

因此,通过合理调整时钟频率可以在保证电路性能的同时降低功耗。

1.2 时钟门控在设计时,可以通过时钟门控的方式来控制时钟信号的传输和使用。

通过选择合适的时钟门控策略,可以有效减少功耗。

例如,当某个电路模块不需要时钟信号时,可以将其时钟门控为关闭状态,从而减少功耗。

1.3 时钟树优化时钟树是指将时钟信号从时钟源传输到各个电路模块的网络结构。

在设计时,可以通过优化时钟树的布线和结构,减少时钟信号的传输路径和延迟,从而降低功耗。

二、功耗优化方法2.1 电源管理电源管理是低功耗设计的重要手段之一。

通过采用合适的电源管理策略,可以在不影响电路性能的前提下降低功耗。

例如,可以通过动态电压调节技术,在电路空闲或负载较轻时降低电压,从而减少功耗。

2.2 时钟门控除了在时钟优化中提到的时钟门控策略外,时钟门控也可以用于功耗优化。

通过合理控制时钟信号的传输和使用,可以减少电路模块的活动次数,从而降低功耗。

2.3 逻辑优化逻辑优化是功耗优化的关键环节。

通过对电路逻辑结构进行优化,可以减少冗余逻辑和不必要的计算,从而降低功耗。

例如,可以通过逻辑合并、布尔运算等技术来简化电路结构,减少功耗。

三、实际应用效果分析时钟与功耗优化方法在实际应用中已经得到广泛应用,并取得了显著的效果。

以智能手机芯片设计为例,通过采用时钟频率调整、时钟门控和时钟树优化等方法,可以将功耗降低至原来的一半甚至更低。

同样,在其他领域的集成电路设计中,时钟与功耗优化方法也取得了不错的效果。

fpga 门控时钟 功耗

fpga 门控时钟功耗FPGA(可编程逻辑门阵列)是一种灵活的集成电路芯片,其门控时钟和功耗是在设计和应用FPGA时需要考虑的重要因素。

下面将介绍FPGA的门控时钟和功耗的相关概念和影响因素:1.门控时钟:FPGA中的门控时钟(Clock Gating)技术是一种用来减小功耗的技术。

它基于时钟信号,通过控制特定部分的电路时钟使能信号,实现对电路的部分停止或冻结。

通过精确控制时钟信号的分配,可以降低那些不需要运行或处于空闲状态的部分的功耗。

2.功耗:FPGA的功耗是指FPGA芯片在工作中消耗的电能。

FPGA的功耗由多个因素决定,包括运行的电路逻辑、时钟频率、输入输出功耗、时钟和数据冲突等。

功耗的高低直接影响到芯片的工作稳定性、散热需求和电池寿命等。

影响FPGA功耗的因素包括:•逻辑电路:芯片中运行的逻辑电路数量和复杂度直接影响功耗。

•时钟频率:时钟频率越高,功耗也越高。

高时钟频率可能需要更多的功率来驱动逻辑和开关电容。

•输入输出功耗:与外部设备的通信和I/O电路相关的功耗。

•激活逻辑:即芯片中具体逻辑的使用情况,未使用或未激活的逻辑不会消耗功耗。

•工艺制程:不同的工艺制程也会影响功耗,先进的工艺通常具有更低的功耗。

减小FPGA的功耗可以通过以下策略实施:•优化逻辑设计:减少逻辑元件的数量和复杂度,精简逻辑电路。

•优化时钟频率:选择适当的时钟频率,以平衡性能和功耗。

•使用门控时钟技术:通过控制部分电路的时钟使能信号,降低空闲电路的功耗。

•合理布局和布线:减少布线的长度和电容负载,优化功耗表现。

在设计和实现FPGA时,需要综合考虑门控时钟和功耗,根据实际需求进行优化和权衡。

同时,对于特定的应用场景,还可以选择适合的低功耗模式、电源管理和时钟路由等技术,以进一步减小FPGA的功耗。

低功耗设计中的时钟门控技术

低功耗设计中的时钟门控技术

时钟门控技术是低功耗设计中非常重要的一项技术。

在数字电路中,时钟信号

的频率越高,功耗也就越大。

因此,在设计低功耗的数字电路时,需要采用一些技术手段来降低时钟信号的频率以达到降低功耗的目的。

时钟门控技术就是一种有效的降低功耗的方法之一。

它通过控制时钟信号的开

关来实现对电路的时钟信号进行控制。

在时钟门控技术中,当电路不需要进行运算时,可以通过控制时钟门控信号来使时钟信号停止,从而降低功耗。

时钟门控技术的实现方法有很多种,其中比较常见的是利用时钟门控信号对寄

存器、触发器以及各种逻辑门进行控制。

通过合理的设计,可以实现在保证电路正常功能的前提下,尽可能地减少功耗。

时钟门控技术在数字集成电路设计中有着广泛的应用。

特别是在移动设备、智

能传感器等对功耗要求较高的领域中,时钟门控技术更是必不可少的一项技术。

通过合理地应用时钟门控技术,可以大幅降低电路的功耗,延长设备的使用时间,提高设备的稳定性。

总的来说,时钟门控技术在低功耗设计中扮演着非常重要的角色。

它通过控制

时钟信号的开关来实现对电路功耗的有效控制,是实现低功耗设计的一种重要手段。

在未来的数字集成电路设计中,时钟门控技术将继续发挥着重要的作用,为我们提供更加节能高效的数字电路设计方案。

门控时钟-理论分析----转载

门控时钟-理论分析----转载门控的基本要求:1. 所需要的沿(对于正沿触发的寄存器是正沿,对于负沿触发的寄存器是负沿)不增加,不减少;1. 不会产⽣⽑刺;1. 使⽤后功耗要能够降低;1. 最好⾯积还会减⼩。

1. 上升沿触发的门控时钟的结构研究:应⽤与上升沿触发的寄存器的门控。

1. 直接与门结构:1. ⾼电平使能Latch + 与门结构:1. 低电平使能Latch + 与门结构:1. 波形研究:从下⾯的波形可以看出:1. 如果En信号的上升沿在时钟的上升沿和下降沿之间的话,则结构1与结构2都会多产⽣⼀个时钟沿;见波形中的Error。

1. 如果En的下降沿在时钟的下降沿和上升沿之间,则很容易产⽣⼀个⽑刺;1. 结构3是符合我们需要的,上升沿没有丢失或减少。

所以DC在正沿触发的寄存器前插⼊的都是这类CG;1. 下降沿触发的门控时钟的结构研究:应⽤与下降沿触发的寄存器的门控。

1. 或门结构:1. 低电平使能Latch + 与门结构:1. ⾼电平使能Latch + 与门结构:1. 波形研究:从下⾯的波形可以看出:1. 如果En信号的上升沿在时钟的下降沿和上升沿之间的话,则结构1与结构2都会多产⽣⼀个时钟沿;见波形中的Error。

1. 如果En的上升沿在时钟的上升沿和下降沿之间,则很容易产⽣⼀个⽑刺;1. 结构3是符合我们需要的,下降沿没有丢失或减少。

所以DC在负沿触发的寄存器前插⼊的都是这类CG;1. 特殊情况分析:1. 如果En信号的上升沿和下降沿都能保证在时钟的低电平区域,则与门结构可以作为门控来使⽤:分析:1. 如果En是ClkSrc时钟域的寄存器负沿触发输出的信号,或者产⽣En的信号都是ClkSrc时钟域负沿触发产⽣的信号;则通过合适的约束,可以做到En的沿都在时钟的低电平区域。

1. 如果从功能上可以确认,En的沿都在时钟的低电平区域,则也可⾏。

1. 这种结构不管是对上升沿触发的寄存器或者对下降沿触发的寄存器都是有效的。

SoC设计中的时钟低功耗技术

Clock Low Power Consumption Technique in SoC Design

WANG Yan-sheng, LIU Lei-bo

(Institute of Microelectronics, Tsinghua University, Beijing 100084)

【Abstract】Aiming at clock network’s function in SoC chip and its own characteristic, this paper studies and implements three kinds of clock low power consumption techniques including using dynamic clock management technique to cut down and distribute module’s clock dynamicly in system level, inserting clock gating cells based on power consumption optimization tool named Power Compiler during logic synthesis, and doing a low power consumption Clock Tree Synthesis(CTS) targeting on clock tree’s dimension during clock tree synthesis. These three techniques are implemented during the design of audio and video decoding chip, and the results show that their power consumption optimization effects are obvious. 【Key words】clock; dynamic clock management; gated clock; low power consumption Clock Tree Synthesis(CTS)

时钟芯片的低功耗设计

时钟芯片的低功耗设计时钟芯片广泛地应用于各种需要记录特定时间的设备中。

对于便携式设备,时钟芯片的功耗对维持整个系统的正常时间记录是非常重要的。

芯片具有较低的功耗,可以满足更长的工作时间要求。

在嵌入式系统中,时钟芯片是工作频率较高的电路,降低其功耗,对于整个系统的功耗降低有着显著的作用。

在低功耗ASIC设计中,前端的逻辑设计和后端的物理设计结合得越来越密切。

系统的低功耗设计必须从设计的各个层次上加以考虑,以实现整体优化设计。

在前端逻辑设计中,从分析功耗物理特性入手,进行功耗估计,为低功耗的整体设计提供理论依据,然后在后端的电路实现上加以控制,这样就可以更好地达到降低芯片功耗的目的。

而且还可以降低设计成本,缩短设计周期。

本文采用自顶而目的设计原则,从体系结构到电路实现上分层次探讨了时钟芯片的功耗来源,并采取相应的控制手段实现芯片的低功耗设计。

1 时钟电路功耗分析1.1 CMOS电路功耗分析对于CMOS集成电路,影响功耗的因素主要包括三个部门:动态功耗、短路功耗和静态功耗。

由于动态功耗占CMOS电路总功耗的80%以上,因此在功耗设计上主要考虑如何降低这部分功耗。

动态功耗P d可用下式表示:P d=C L V DD2f0→1 (1)式中,C L为输出节点的总负载电容;VDD为工作电压,也是CMOS电路的逻辑摆幅;f0→1为开关活性因子。

下面就来分析与时钟芯片功耗设计密切相关的两个因素。

1.1.1 功耗与工作电压V DD的关系从(1)式中可以看出,降低工作电压会使功耗呈平方律下降,因此绝大多数低功耗设计都首先考虑采用尽可能低的工作电压。

但对于确定的工艺,如果电源电压过低,将会导致电路性能下降。

当电源电压降低到接近PMOS和NMOS晶体管的阈值电压值之和时,延迟时间急剧增大,器件的工作速度下降,功耗反而增加。

1.1.2 功耗与开关活性因子f0→1的关系对于CMOS逻辑器件,只有当输出节点出现0到1的逻辑转换时,才从电源吸引能量。

低功耗MCU动态时钟分析

低功耗MCU动态时钟分析

本文结合MSP430 系列微处理器,详细论述了通过控制改变MCU 的时钟频率来降低功耗的设计方法。

1 功耗产生的原因

在CMOS 电路中,功耗损失主要包括静态功耗损失和动态功耗损失两部分。

其中静态功耗主要是由反偏PN 结的漏电流和晶体管的亚阈值电流引起的,其最主要的形式就是漏电损失。

其实CMOS 电路理论上不会有静电功耗损失,因为从供应电源到地面没有直接的路径,但实际上晶体管总会有漏电电流的出现,从而出现漏电损失。

在0.18μm 工艺水平之下,其在功耗中所占比重大约为5%~10%,一般可以忽略(但是随着工艺的提高,供电电压的降低,又使其所占比重逐渐上升)。

这样,在CMOS 电路中,动态功耗就成了这个系统功耗的主要组成部分,约占整体功耗的90%以上。

定量地分析电路的动态功耗,可用以下公式表示:

其中:C 为负载电容;VDD 为电源电压;?琢为翻转几率,即每个时钟周期中发生的充放电周期个数;fCLK 为时钟频率。

从这个公式可以看到如何降低动

态功耗从而降低整个CMOS 电路的功耗。

即可以减小翻转的负载电容,降低电源电压,减小节点的翻转几率,或者降低时钟频率。

本文将主要围绕如何动态降低时钟频率实现低功耗设计。

2 动态时钟低功耗管理原理

MCU 系统设计是个很复杂的过程,在一些条件下可能会用到整个系统

的所有硬件资源,但是在一些应用中可能只需要其中很少的一部分硬件资源;在某些应用中可能需要很高的时钟频率,而在其他应用中却可以工作在很低的工作频率中。

例如:当任务量很大时,MCU 满负荷工作,则需要较高的时钟频。

芯片设计中的低功耗时钟与时序优化研究

芯片设计中的低功耗时钟与时序优化研究在现代电子设备中,芯片设计起着至关重要的作用。

低功耗时钟与时序优化是芯片设计领域的一个重要研究方向。

本文将深入探讨低功耗时钟与时序优化的研究内容和应用。

一、低功耗时钟与时序优化的重要性随着移动设备和物联网应用的普及,对电子设备的电池寿命和功耗要求越来越高。

芯片设计中的时钟和时序优化就显得尤为重要。

低功耗时钟与时序优化可以减少功耗,延长电池寿命,提高系统性能。

二、低功耗时钟与时序优化的研究内容1. 时钟树优化时钟树是芯片中提供稳定和准确时钟信号的重要组成部分。

优化时钟树可以减少功耗和时钟抖动,提升系统性能。

常用的时钟树优化方法有时钟资源共享、布线寻优和时钟树拓扑结构优化等。

2. 时钟门控优化时钟门控是在芯片中控制时钟信号传递的重要技术。

优化时钟门控可以减少功耗和时钟延迟,提升系统的响应速度。

常用的时钟门控优化方法有时钟门控树优化和时钟门控策略优化等。

3. 时序路径优化时序路径是芯片中数据传输的路径,优化时序路径可以减少功耗和延迟,提高芯片的运行速度。

常用的时序路径优化方法有转发路径优化、时序约束优化和时序修复策略优化等。

4. 功耗分析与优化芯片设计中的功耗分析与优化是低功耗时钟与时序优化的核心内容。

通过对芯片功耗进行分析,找到功耗的热点和问题所在,可以采取相应的优化措施。

常用的功耗分析与优化方法有功耗分析技术和功耗优化技术等。

三、低功耗时钟与时序优化的应用低功耗时钟与时序优化技术广泛应用于各种电子设备中,如移动电话、智能手表、物联网设备等。

这些设备对功耗和电池寿命的要求较高,低功耗时钟与时序优化的应用可以显著提升设备的性能和使用时间。

四、未来发展趋势随着科学技术的不断进步和应用需求的不断升级,低功耗时钟与时序优化的研究也将不断深入。

未来的发展趋势包括更高效的时钟树设计和时钟门控策略,更精确的时序路径优化算法,以及更智能化的功耗分析与优化方法。

结语低功耗时钟与时序优化是芯片设计中的重要研究方向,对于提高电子设备的性能和延长电池寿命具有重要意义。

SOC的功耗分析

低功耗SOC设计1)为什么需要低功耗?随着SOC的集成度与性能的不断发展,如今的SOC已达到百瓦量级。

如Intel的Itanium2功耗约130瓦,这需要昂贵的封装,散热片及冷却环境。

根据摩尔定律,每18个月晶体管密度增加一倍,而电源技术要达到相同的增速,需要5年,显然电源技术已成瓶颈。

电路里的大电流会使产品的寿命和可靠性降低。

电源的动态压降严重的时候还会造成失效。

2)功耗从哪儿来?功耗一般分两种:来自开关的动态功耗,和来自漏电的静态功耗。

而动态功耗又可分为电容充放电(包括网络电容和输入负载),还有当P/N MOS 同时打开形成的瞬间短路电流。

静态功耗也可分为几类:扩散区和衬底形成二极管的反偏电流(Idiode),另外一类是关断晶体管中通过栅氧的电流(Isubthreshold)。

芯片的漏电会随温度变化,所以当芯片发热时,静态功耗指数上升。

另外漏电流也会随特征尺寸减少而增加。

公式:Ptotal = Pdynamic + Pshort + PleakagePswitch = A * C * V2 * FPshort = A (B/12) (V-2Vth)3 * F * TPleakage = (Idiode + Isubthreshold) * V3)怎样减少功耗呢?首先定义对功耗的需求,然后分析不同的架构,决定如下需求:system performance, processor and other IP selection, new modules to be designed, target technology, the number of power domains to be considered, target clock frequencies, clock distribution and structure, I/O requirements, memory requirements, analog features and voltage regulation.你还需要定义工作模式:如startup, active, standby, idle, and power down等等,当然这些模式是由软硬件共同决定的。

门控时钟 低功耗芯片设计方案

门控时钟低功耗芯片设计方案

门控时钟是数字电路中常见的一个模块,它用于控制数据在不

同部件之间的传输和处理。

在低功耗芯片设计方案中,门控时钟的

设计是至关重要的。

首先,我们需要考虑选择合适的门控时钟电路,以确保在低功耗的同时能够稳定地控制数据传输。

一般来说,采用

低功耗的CMOS技术设计门控时钟电路是一个不错的选择,因为CMOS技术具有低静态功耗和高抗干扰能力。

其次,我们需要考虑如何优化门控时钟的工作模式以降低功耗。

这可能涉及到采用动态频率调整、睡眠模式和快速唤醒等技术,以

确保在需要时能够提供足够的性能,而在空闲时能够最大限度地降

低功耗。

另外,对于低功耗芯片设计方案来说,还需要考虑如何合理规

划整个芯片的电源管理。

门控时钟电路需要与其他模块协同工作,

因此在设计时需要考虑到整个芯片的功耗分配和管理,以确保门控

时钟在低功耗的同时能够满足整个芯片的需求。

此外,还有一些其他的技术可以用于降低门控时钟的功耗,比

如采用多级时钟缓冲器来降低时钟信号的传输功耗,采用时钟门控

技术来实现局部时钟门控等。

总的来说,低功耗芯片设计方案中的门控时钟设计涉及到多个方面,包括选择合适的电路技术、优化工作模式、合理规划电源管理等。

在实际设计中,需要综合考虑这些因素,以实现低功耗和稳定性的平衡。

集成电路的低功耗设计策略分析

CE MAGAZINE PAGE 91集成电路的低功耗设计策略分析王奇君【摘 要】集成电路是现代电子设备的核心,其功耗对设备的性能和续航时间有着重要影响。

随着集成电路规模的不断扩大,功耗问题日益严重,低功耗设计成为集成电路设计的重要研究方向。

故此将针对集成电路的低功耗设计策略进行分析,从设计意义、设计思路等方面展开探究,总结相应的低功耗设计方法,为提高系统的性能和可靠性提供学术支持。

【关键词】集成电路;低功耗设计;策略分析;功耗优化作者简介:王奇君,武汉梦芯科技有限公司,CTO。

近年来,移动设备的普及和无线通信技术的快速发展,使得低功耗设计成为集成电路设计的一个重要方向。

随着功耗的不断增加,电池寿命问题成为制约设备续航能力的重要因素。

因此,在集成电路设计中,低功耗设计已经成为不可或缺的一部分,在移动设备和物联网技术的快速发展背景下,对于集成电路的低功耗设计需求越来越迫切。

低功耗设计不仅可以延长电池续航时间,还可以降低设备的热量和功率消耗。

因此,研究低功耗设计策略对于当前集成电路领域具有重要意义。

一、集成电路的低功耗设计意义集成电路(IC)的低功耗设计是指在设计和制造过程中,通过各种技术手段减少集成电路的功耗,提高其能效比。

其中,电源管理是低功耗设计的核心,其使得集成电路在不同工作状态下能够动态调整功耗,从而达到节能的效果。

电路结构优化可以通过改变电路的结构和布局,减少功耗并提高电路性能。

时钟频率控制可以根据不同的需求来动态调整时钟频率,以达到降低功耗的效果。

IO接口设计可以减少与外部设备的通信开销,从而减少功耗。

随着科技的发展,电子产品对集成电路的性能和功耗要求越来越高。

低功耗设计不仅可以降低电子产品的能耗,减少环境污染,还可以提高产品的可靠性和稳定性,延长产品的使用寿命。

具体而言,集成电路作为电子产品的核心部件,其功耗直接影响着整个电子产品的能耗。

通过低功耗设计,可以减少集成电路的功耗,降低电子产品的能耗,从而减少环境污染,低功耗设计还有助于减少电子产品的散热问题,降低产品温度,提高产品的可靠性。

芯片设计中的低功耗时钟技术研究

芯片设计中的低功耗时钟技术研究随着移动设备、物联网和智能家居等领域的快速发展,对低功耗芯片的需求也越来越大。

而在芯片设计中,时钟技术是重要的一部分,它对芯片的功耗和性能有着直接的影响。

因此,研究和应用低功耗时钟技术成为了现代芯片设计中的一个热门方向。

一、低功耗时钟技术的意义时钟信号在芯片中起到同步和驱动的作用,它控制了芯片内各个功能部件的工作状态。

在低功耗芯片设计中,优化时钟技术可以帮助降低功耗、提高芯片性能,并延长电池寿命。

此外,低功耗时钟技术还能减少由于时钟信号传输引起的功耗损耗和噪音干扰,提高芯片的可靠性和稳定性。

二、低功耗时钟技术的研究方向1. 时钟频率调节技术在低功耗芯片设计中,时钟频率调节技术是一种常用的手段。

通过动态地调整时钟频率,可以根据芯片当前的工作状态来灵活地改变时钟频率。

例如,在芯片处于空闲状态时,可以降低时钟频率以减少功耗;而在需要高性能的场景下,可以提高时钟频率以提升芯片运算能力。

2. 时钟门控技术时钟门控技术是低功耗芯片设计中的另一种重要手段。

它通过在芯片中插入可控的时钟门,实现对芯片内部功能单元的时钟供应进行精确控制。

当某个功能单元不需要工作时,可以关闭对其的时钟供应,从而实现功耗的降低。

3. 功耗感知时钟树设计时钟树是芯片中时钟信号传输的重要组成部分,它的设计对芯片功耗有着直接的影响。

为了降低时钟树的功耗,可以采用功耗感知的时钟树设计方法。

这种方法通常包括时钟树的分级设计、时钟缓冲的优化以及时钟信号的容错机制等,以实现低功耗的时钟信号传输。

4. 时钟域划分与管理在复杂的芯片设计中,常常存在多个时钟域。

合理地进行时钟域划分与管理可以有效地降低功耗。

通过将芯片划分为不同的时钟域,并采用适当的互联方式和时钟同步策略,可以减少时钟信号的功耗消耗和传输延迟,提高芯片性能和可靠性。

三、低功耗时钟技术的挑战与前景低功耗时钟技术在芯片设计中具有重要的意义,但同时也面临着一些挑战。

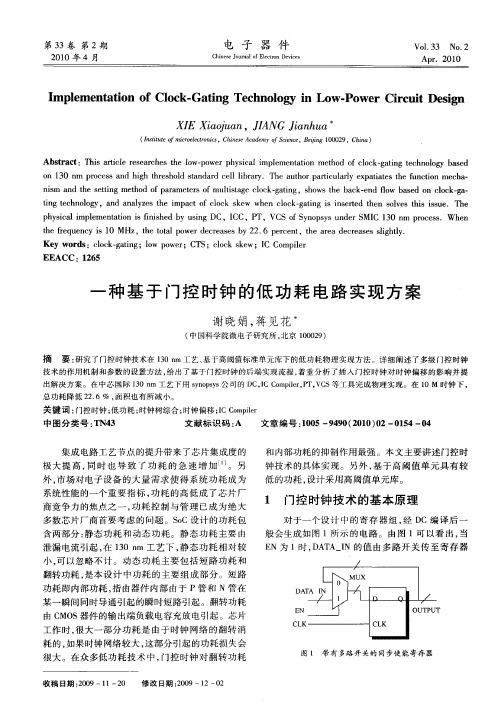

一种基于门控时钟的低功耗电路实现方案

商 竞争力 的焦点之 一 , 功耗 控 制 与 管理 已成 为 绝 大

多 数芯 片厂 商首要 考虑 的问题 。S C设 计 的功 耗包 o 含 两部分 : 态 功耗 和 动 态 功耗 。静 态功 耗 主 要 由 静 泄 漏 电流引起 , 10 n 工 艺下 , 态功 耗 相 对 较 在 3 m 静 小 , 以忽 略不计 。动 态 功耗 主 要 包 括短 路 功 耗 和 可

Ab ta t s r c :Th sa tce r s a c s t e lw・ o rp y ia m p e e t t n m eh d o lc - ai g tc n lg a e i ril e e rhe h o - we h sc li lm n a i t o fc o k- t e h oo y b s d p o g n

p y i a mp e n a in i i ih d b sn h sc li lme tto sfn s e y u ig DC,I CC,PT,VCS o y o s s u d rS C 0 n p o e s W h n fS n p y n e MI 1 m r c s . 3 e

一

种 基 于 门 控 时钟 的低 功 耗 电 路 实 现 方 案

谢 晓娟 , 见 花 蒋

( 国科 学 院微 电子 研 究 所 , 京 10 2 ) 中 北 00 9

摘 要 : 研究了门控时钟技术在 10n 3 m工艺、 基于高阈值标准单元库下的低功耗物理实现方法。详细阐述了多级门控时钟

技 术 的作 用 机 制 和参 数 的设 置 方 法 , 出 了 基 于 门控 时钟 的后 端 实 现 流 程 , 重 分 析 了插 入 门 控 时 钟 对 时 钟 偏 移 的 影 响 并 提 给 着 出解 决 方 案 。在 中芯 国际 10n 工 艺 下 用 sn py 公 司 的 D I o i rP , C 3 m yoss C, C mp e,T V S等 工 具 完 成 物 理 实 现 。在 1 时 钟 下 , C l 0M 总功耗降低 2. 2 6% , 面积 也 有 所 减 小 。

MCU低功耗设计技术及其功耗分析

MCU低功耗设计技术及其功耗分析标题1:MCU低功耗设计技术中的时钟优化时钟是MCU的核心,它对MCU功耗的影响非常大。

本文将介绍如何通过时钟优化技术在MCU低功耗设计中发挥重要作用。

首先,使用低功耗时钟源,如RC振荡器或低功耗晶体振荡器。

这些时钟源功耗较低,可以帮助降低MCU系统功耗。

其次,使用时钟关闭技术。

在MCU运行期间,许多外设不需要时钟,如定时器和ADC等,关闭这些外设的时钟可以减少系统功耗。

最后,使用时钟预分频技术。

这可以将时钟变为低频,并减少MCU系统功耗。

同时,考虑到MCU的实时性能,需要根据具体应用场景进行权衡。

毕业总结:时钟优化技术是MCU低功耗设计中不可缺少的因素,通过合适的时钟源、时钟关闭和时钟预分频技术,可以有效减少MCU系统功耗,并保证MCU实时性能。

标题2:MCU低功耗设计技术中的电源优化电源管理是MCU低功耗设计的关键。

本文将介绍如何通过电源优化技术在MCU低功耗设计中发挥重要作用。

首先,选择适合的电源供应器是MCU低功耗设计的关键。

选择过大的电源供应器意味着浪费大量功耗,并将影响MCU系统的响应速度。

相反,选择过小的电源供应器会影响MCU系统的稳定性。

其次,使用电源管理技术。

例如,通过关闭不使用的外设,或在不同的工作状态下切换不同的电源模式可以减少MCU系统功耗。

最后,使用睡眠模式。

在不使用MCU时,将其设置为睡眠模式可以将功耗降至最低。

毕业总结:通过合适的电源供应器、电源管理技术和睡眠模式等电源优化技术,可以在MCU低功耗设计中起到关键作用。

这些技术的有效应用可以帮助提高MCU系统的稳定性和响应速度,并减少系统功耗。

标题3:MCU低功耗设计技术中的睡眠模式优化睡眠模式是MCU低功耗设计中最常用的技术。

本文将介绍如何通过睡眠模式优化技术在MCU低功耗设计中发挥重要作用。

首先,选择合适的睡眠模式。

对于不同的应用场景,选择合适的睡眠模式可以最大程度地减少MCU系统功耗。

低功耗时钟门控电路设计研究

设计应用技术 2024年1月25日第41卷第2期21 Telecom Power TechnologyJan. 25, 2024, Vol.41 No.2王子鑫:低功耗时钟门控电路设计研究使能时钟锁存器门控时钟与门D ENQ图2 数据保持模块基于文章的设计思路,首先电路对同一组中的N 个触发器的输入信号执行“与非/或”逻辑运算,其次将这一运算的输出信号作为使能信号传输至数据保持模块,最后利用数据保持模块输出门控时钟并连接到触发器的时钟端,实现其预定功能。

3 仿真结果及分析文章制定的仿真流程如图3所示。

选择的测试电路为ISCAS 89,由于其功能不固定,被广泛应用于各类电路测试任务。

此外,文章采用Verilog HDL 搭建测试平台,设定加入文章所提出的新型时钟门控技术改进的电源电路为电路1,采用传统时钟门控技术进行优化的电源电路为电路2,仿真对比结果如表1所示。

编写电路修改并编译开始基于实验平台进行仿真基于仿真波形改进电路二次编译并仿真结束图3 仿真流程表1 仿真对比结果对比电路名称功耗总额/mW漏电功耗/mW门控效率/%门控类型交变功耗/mW原电路42.3712.210.00无门控28.77电路130.2211.2030.764/619.42电路238.4413.7734.214/626.20由表1可知,电路1在降低能耗方面的效果更加显著,在减少功耗方面的性能优越。

4 结 论文章围绕电源管理中的关键挑战,即降低电子设备时钟门控电路的功耗,设计了一种新型的低功耗时钟门控电路,为电源管理和节能技术的发展提供一定的帮助。

通过开展本研究,填补现有技术的不足,从而推动时钟门控电路设计朝着更高效和更低功耗的方向前进。

参考文献:[1] 陈铁年,王 闯,刘佳伟.煤矿输送机变频器控制单元电源管理技术[J].煤矿机械,2023,44(12):49-51.[2] 张 亚,田 慧,唐 波,等.用于脉冲电源模块的数据采集与管理系统设计[J].传感器与微系统,2023,42(10):111-113.[3] 支宏旭,张华勇,鲍忠利,等.随钻地层测试器电源管理模块设计[J].仪表技术,2023(4):10-13.[4] 陈嘉豪.低压压电能量采集电源管理电路关键技术研究与设计[D].成都:电子科技 大学,2023.[5] 王 管.基于分布时钟的低功耗光子计时阵列读出电路设计[D].南京:东南大学,2021.[6] 朱涛涛,项晓燕,陈 晨,等.面向宽电压应用的容错时钟门控单元设计[J].浙江大学学报,2018,52(9):1796-1803.[7] 姬 强.基于时钟门控技术对内存控制模块的RTL 级功耗优化[D].西安:西安电子科技 大学,2017.[8] 杨远花.基于物联网传感技术的过滤器接头零件成型控制系统设计[J].机械设计与制造工程,2022,51(10):101-105.[9] 吴淘锁.FPGA 设计中抗干扰问题及毛刺信号的消除[J].呼伦贝尔学院学报,2009,17(6):59-62.[10] 曾 莉,易 鸿.PLD 系统设计过程中抗干扰问题及毛刺现象的处理[J].甘肃联合大学学报,2008(3):70-74.。

低功耗物门控时钟的三种功耗分析

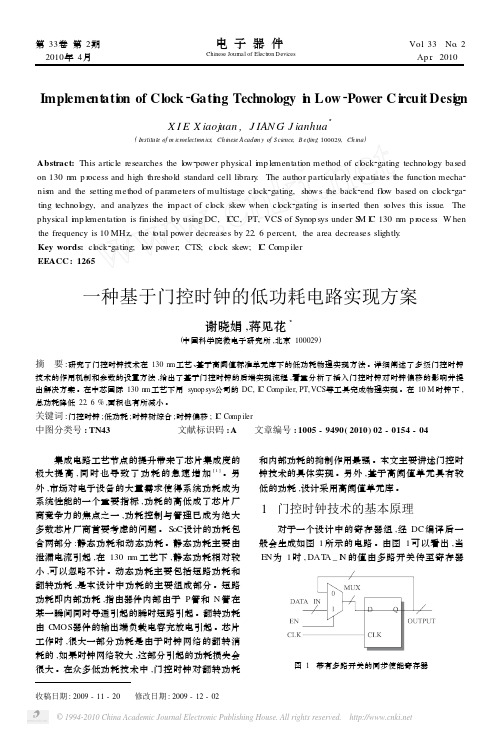

低功耗物门控时钟的三种功耗分析电路在功能仿真通过后,开始进行寄存器级综合。

采用高阈值标准单元库和多级门控时钟技术相结合,在RTL阶段插入门控时钟单元,并在布局布线时在IC Comp iler中进行了基于门控时钟的布局布线优化,布局布线正确完成仿真通过后,在PT中做静态时序分析并进行最终的功耗分析。

1、时钟门控的RTL级实现在RTL级,门控时钟的实现不需要对设计本身进行修改,而只需在综合脚本中加入一些控制项。

控制项set_clock_gating_ STyle是门控时钟的核心。

它的参数大小决定门控时钟的质量,对功耗的优化效果和对CTS的影响。

目前尚无完备的体系介绍如何设置控制项以使门控效果达到最优。

首先确定时序单元的类型。

为了避免非Latch单元易产生毛刺的缺点,此处选定时序单元的类型为Latch。

由于库中提供基于锁存器的门控单元,固正边沿逻辑positive_edge_ logic采用工艺库提供的专用单元。

采用集成单元的优势在于不仅不需要设置门控单元输入端建立时间和保持时间,因为集成单元的时序信息在单元库中已有说明,而且有效缓解了插入门控单元对延时带来的不利影响。

fanout的大小对功耗和时序都有影响。

数值越大则表示一个门控单元可承受较多的负载,即代表越节省功耗,需要的门控单元也越少,但对门控单元输入端建立时间的要求也就更加严格。

位宽决定一组寄存器能被门控的最小宽度。

级数则确定多级门控时钟的最大级数。

这三个参数主要是依据设计本身对功耗的要求,结合综合时的时序约束和单元库中门控单元的时延信息加以估计,确定一个粗略的数值范围。

2、时钟门控的版图级实现在布局布线阶段,基于门控时钟的功耗优化流程主要如下:在布局之前,设置set_power_op tiONs–clock_gating true,之后在布局、时钟树综合和布线阶段的主要命令中添加选项- power即可。

设置可实现最基本的门控时钟布局布线,但在设计中生成的时钟网络分布不均匀,而且skew很大。

一种基于门控时钟的低功耗电路实现方案

第33卷第2期2010年4月电子器件Chinese Journal of Electr on DevicesVol .33 No .2Ap r .2010收稿日期:2009-11-20 修改日期:2009-12-02Implement ati on of Clock 2Gati n g Technology i n Low 2Power C i rcuit Desi gnX I E X iaojuan ,J IAN G J ianhua3(Institute of m icroelectronics,Chinese Acade m y of Science,B eijing 100029,China )Abstract:This article researches the l ow 2power physical i m p le mentati on method of cl ock 2gating technol ogy based on 130nm p r ocess and high threshold standard cell library .The author particularly expatiates the functi on mecha 2nis m and the setting method of para meters of multistage cl ock 2gating,shows the back 2end fl ow based on cl ock 2ga 2ting technol ogy,and analyzes the i m pact of cl ock ske w when cl ock 2gating is inserted then s olves this issue .The physical i m p le mentati on is finished by using DC,I CC,PT,VCS of Synop sys under S M I C 130nm p r ocess .W hen the frequency is 10MHz,the t otal power decreases by 22.6percent,the area decreases slightly .Key words:cl ock 2gating;l ow power;CTS;cl ock ske w;I C Comp iler EEACC:1265一种基于门控时钟的低功耗电路实现方案谢晓娟,蒋见花3(中国科学院微电子研究所,北京100029)摘 要:研究了门控时钟技术在130n m 工艺、基于高阈值标准单元库下的低功耗物理实现方法。

基于门控时钟技术的低功耗三值D型触发器设计

基于门控时钟技术的低功耗三值D型触发器设计

叶锡恩;陶伟炯;王伦耀

【期刊名称】《电路与系统学报》

【年(卷),期】2006(11)3

【摘要】本文在三值D型触发器的基础上提出了一种低功耗三值门控时钟D型触发器的设计.该设计通过抑制触发器的冗余触发来降低功耗,PSPICE模拟验证了该触发器具有正确的逻辑功能.与三值D触发器相比,该触发器在输入信号开关活动性较低的情况下具有更低的功耗.同时该电路结构可以推广到基值更高的低功耗多值触发器的设计中.

【总页数】4页(P106-109)

【作者】叶锡恩;陶伟炯;王伦耀

【作者单位】宁波大学,电路与系统研究所,浙江,宁波315211;宁波大学,电路与系统研究所,浙江,宁波315211;宁波大学,电路与系统研究所,浙江,宁波315211

【正文语种】中文

【中图分类】TN432;TP331

【相关文献】

1.基于门控时钟的低功耗时序电路设计新方法 [J], 徐扬;沈继忠

2.基于门控时钟技术的IC低功耗设计 [J], 田素雷;张勇;张磊;曹纯

3.基于MCML的高性能三值D型触发器的设计 [J], 赵祥红;沈继忠

4.基于时钟控制技术的低功耗三值D触发器设计 [J], 耿亮;沈继忠;许聪源

5.时钟低摆幅三值双边沿低功耗触发器的设计 [J], 曾小旁; 汪鹏君

因版权原因,仅展示原文概要,查看原文内容请购买。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

低功耗物门控时钟的三种功耗分析

电路在功能仿真通过后,开始进行寄存器级综合。

采用高阈值标准单元库和多级门控时钟技术相结合,在RTL阶段插入门控时钟单元,并在布局布线时在IC Comp iler中进行了基于门控时钟的布局布线优化,布局布线正确完成仿真通过后,在PT中做静态时序分析并进行最终的功耗分析。

1、时钟门控的RTL级实现

在RTL级,门控时钟的实现不需要对设计本身进行修改,而只需在综合脚本中加入一些控制项。

控制项set_clock_gating_ STyle是门控时钟的核心。

它的参数大小决定门控时钟的质量,对功耗的优化效果和对CTS的影响。

目前尚无完备的体系介绍如何设置控制项以使门控效果达到最优。

首先确定时序单元的类型。

为了避免非Latch单元易产生毛刺的缺点,此处选定时序单元的类型为Latch。

由于库中提供基于锁存器的门控单元,固正边沿逻辑positive_edge_ logic采用工艺库提供的专用单元。

采用集成单元的优势在于不仅不需要设置门控单元输入端建立时间和保持时间,因为集成单元的时序信息在单元库中已有说明,而且有效缓解了插入门控单元对延时带来的不利影响。

fanout的大小对功耗和时序都有影响。

数值越大则表示一个门

控单元可承受较多的负载,即代表越节省功耗,需要的门控单元也越少,但对门控单元输入端建立时间的要求也就更加严格。

位宽决定一组寄存器能被门控的最小宽度。

级数则确定多级门控时钟的最大级数。

这三个参数主要是依据设计本身对功耗的要求,结合综合时的时序约束和单元库中门控单元的时延信息加以估计,确定一个粗略的数值范围。

2、时钟门控的版图级实现

在布局布线阶段,基于门控时钟的功耗优化流程主要如下:在布

局之前,设置set_power_op tiONs–clock_gating true,之后在布局、时钟树综合和布线阶段的主要命令中添加选项- power即可。

设置可实现最基本的门控时钟布局布线,但在设计中生成的时钟网络分布不均匀,而且skew很大。

需要采取额外的优化措施来消除其带来的不利影响。

门控单元的加入给CTS带来的影响主要有两个方面,一方面会

造成整个时钟网络分布不平衡,另一方面导致时钟偏移增大。

单采用上述措施,时钟偏移最大可达到1. 11,严重偏离了不采用门控时钟时的偏移量0. 12。

在优化时钟偏移上,目标有三个方面:构造一个

相对平衡的时钟网络,使得在各个层上,层的各个分支上的单元数目相近;减小时钟偏移至可承受范围;尽量保持功耗同只采用门控时钟

而不优化时钟偏移状况下的功耗相近或更小。

分析引起skew偏大的原因,通过在ICC中跟踪路径,查看时钟网络电路图,发现时钟层分布极不均匀,分支节点最大相差6 层。

在具体时序路径中,两条路径延时过大,插入了许多不必要的buffe r,为构造一个平衡的时钟树,减小skew并减少对功耗的影响,在CTS阶段采取了三个措施。

第一,设置set_clock_tree_op tions–LOGIC_ level_bal 2ance为true。

CTS的操作模式有三种: 模块模式,顶层模式,逻辑级平衡模式,默认为模块模式。

第二,复制门控单元。

主要是通过修正ICG输出端的DRC来平衡扇出,并添加缓冲单元来驱动没有被门控的寄存器使得整个时钟树的结构更加平衡。

首先设置cts_push _down_ buffer为true。

然后sp lit_ clock _ gate –ob2jects { 3 . / latch} –gate _ sizing–gate_ relocation。

第三,为了弥补功耗优化方面的不足,在CTS完毕之后用p s ynop t–power。

不采用门控时钟、采用门控时钟但不做skew优化、采用门控时钟且进行skew优化。

3、功耗测量过程及实验结果分析

布局布线完成后,导出网表到VCS中进行后仿,并得到分析功耗所需的saif文件。

将此saif文件和布局布线后带有实际延时信息的网表读入PT中,加以适当的时序约束进行功耗分析。

采用门控时钟技术后的设计总体功耗下降了22. 6 %。

其中,开关功耗下降了63. 2 % ,内部功耗下降了21. 9 %,体现了引入门控时钟技术的优势,因为门控时钟主要用于降低动态功耗,泄露功耗略有下降。

总功耗由原来的1 mW降低至778 uW,功耗降低效果非常明显。

除此之外,芯片核的面积也略有减小。