锁相环环路滤波器的元件值计算

环路滤波器参数确定公式

环路滤波器参数确定公式在信号处理领域中,环路滤波器是一种常用于提取某一频率成分的滤波器。

环路滤波器通常由一个环形反馈结构组成,其参数的确定对于滤波器的性能起着至关重要的作用。

环路滤波器的基本原理环路滤波器是一种反馈控制系统,其基本原理是通过将滤波器的输出信号与输入信号进行比较,然后根据比较结果调整滤波器的参数,使得滤波器输出的信号更好地满足特定的要求。

环路滤波器的设计可以采用不同的结构,如环路带通滤波器、环路带阻滤波器等,不同结构的环路滤波器对应不同的信号处理需求。

环路滤波器参数确定的问题环路滤波器的参数确定是环路滤波器设计中的重要问题之一。

确定良好的参数可以使得环路滤波器在滤波效果和稳定性方面得到较好的平衡。

在确定环路滤波器的参数时,需要考虑到滤波器的截止频率、增益、带宽等参数,以及环路滤波器的阶数、结构等因素。

环路滤波器参数确定的方法环路滤波器参数的确定通常可以通过以下步骤来实现:1.确定滤波器类型:首先需要确定所需的滤波器类型,如低通滤波器、高通滤波器等,根据信号处理的需求选择合适的类型。

2.建立滤波器模型:根据选择的滤波器类型建立相应的数学模型,包括传递函数、差分方程或状态空间方程等。

3.设定设计要求:确定需要满足的设计要求,如截止频率、通带波动、阻带衰减等指标。

4.选择参数优化方法:根据设计要求选择合适的参数优化方法,如传统的频域设计方法、时域设计方法或者优化算法等。

5.参数调整和优化:通过参数调整和优化,不断迭代设计过程,直至满足设计要求为止。

环路滤波器参数确定的公式环路滤波器的参数确定公式可能因滤波器类型和设计要求的不同而有所差异。

但一般而言,环路滤波器的参数确定可归纳为以下一般性公式:•截止频率确定:截止频率通常根据信号的频率成分和处理要求确定,可以使用公式f c=1来计算,其中f c为截止频率,R为电阻值,C为电容值。

2πRC•增益确定:增益是指滤波器对不同频率信号的放大倍数,可以根据设计要求和滤波器结构来确定增益系数。

锁相环的电路组成、器件参数及工作原理

摘要:简单介绍了锁相环电路的基本概念及原理,以通用型集成锁相环4046为例主要介绍了锁相环的电路组成、器件参数及工作原理,并对COMS集成锁相环CC4046的应用做了简单研究。

关键词:锁相环鉴相器压控振荡器1 引言锁相环作为一种重要的功能电路在通信、导航、控制、仪器仪表等领域得到了广泛的应用。

20世纪70年代以后随着集成电路技术的飞速发展,出现了多种型号的集成锁相环产品,其中模拟式集成锁相环以NE/SE 560系列最为常用,COMS集成锁相环CD/CC4046最具代表性。

两者基本原理相同,区别在于前者的鉴相器由模拟电路组成,而后者由逻辑电路组成。

2 锁相环的基本概念所谓锁相,就是相位同步的自动控制。

完成两个信号间相位同步的自动控制系统的环路叫做锁相环,也称PLL(Phase Locked Loop)。

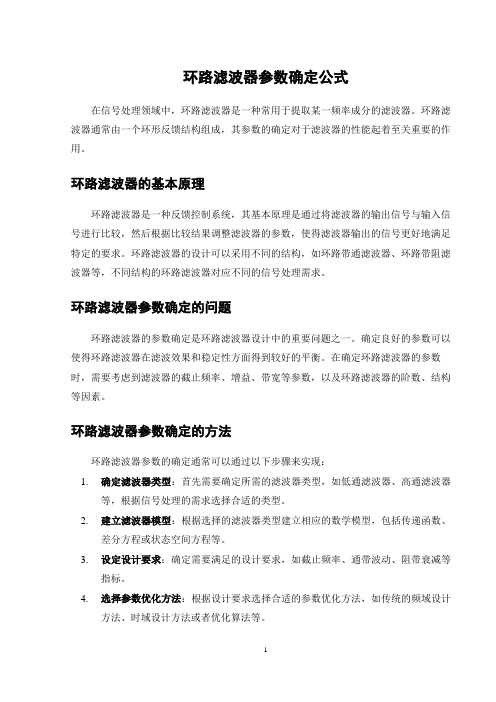

最典型的锁相环由鉴相器(Phase Detector),环路滤波器(Loop Filter),压控振荡器(Voltage Controlled Oscillator)三部分组成,如图1所示。

图1 PLL功能框图其中,鉴相器相位比较作用,其输出电压反映两个输入信号间的相位差(与频率之差成线性关系)的大小。

该电路通过具有低通特性的环路滤波器后,建立起一个平均电压,作用于VCO的控制输入端,VCO的振荡频率则由其控制电压的大小决定,当控制电压=0时,对应的振荡频率称为VCO的固有频率。

整个环路根据负反馈的原理构成,鉴相器的输出电压总是朝着减小VCO振荡频率与输入信号之差的方向变化,直到VCO振荡频率与输入信号频率获得一致,当这种情况出现时,称VCO的频率锁定于输入信号的频率或简称锁定。

环路由失锁状态进入锁定状态的过程称为捕捉过程。

在捕捉过程中,VCO振荡频率逐渐趋同于输入信号频率的现象,称作频率牵引。

在频率牵引过程中,环路有能力自行锁定的最大输入信号频率范围称为捕捉频带或简称捕捉带,它是反映捕捉能力优劣的一个重要指标。

锁相环计算方法

2、理论分析计算与电路设计2.1 锁相环2.1.1 锁相环原理为了使系统产生稳定的载波,本系统设计中采用锁相环路。

锁相环路是一种反馈控制电路,将参考信号与输出信号之间的相位进行比较,产生相位误差电压来调整输出信号的相位以达到与参考信号同频的目的。

由MC145152、MC12022及压控振荡器组成的锁相环路产生的载波的稳定度达到4×10-5,准确度达到3×10-5。

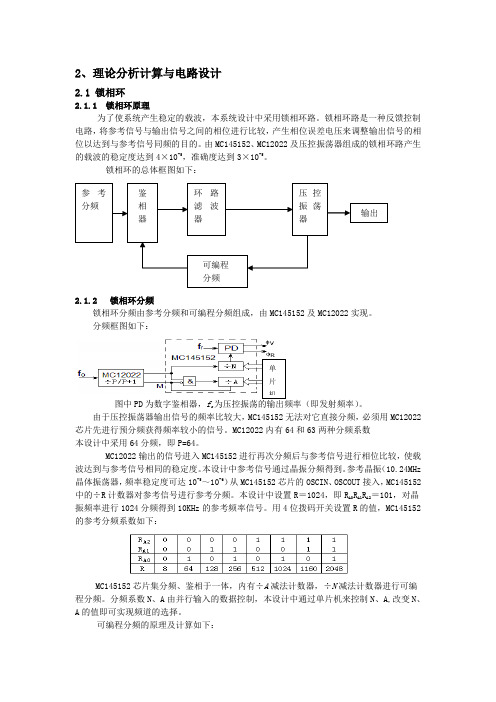

锁相环的总体框图如下:2.1.2 锁相环分频锁相环分频由参考分频和可编程分频组成,由MC145152及MC12022实现。

分频框图如下:图中PD 为数字鉴相器,f o 为压控振荡的输出频率(即发射频率)。

由于压控振荡器输出信号的频率比较大,MC145152无法对它直接分频,必须用MC12022芯片先进行预分频获得频率较小的信号。

MC12022内有64和63两种分频系数 本设计中采用64分频,即P=64。

MC12022输出的信号进入MC145152进行再次分频后与参考信号进行相位比较,使载波达到与参考信号相同的稳定度。

本设计中参考信号通过晶振分频得到。

参考晶振(10.24MHz晶体振荡器,频率稳定度可达10-5~10-6)从MC145152芯片的OSCIN 、OSCOUT 接入,MC145152中的÷R 计数器对参考信号进行参考分频。

本设计中设置R =1024,即R A0R A1R A2=101,对晶振频率进行1024分频得到10KHz 的参考频率信号。

用4位拨码开关设置R 的值,MC145152的参考分频系数如下:MC145152芯片集分频、鉴相于一体,内有÷A 减法计数器,÷N 减法计数器进行可编程分频。

分频系数N 、A 由并行输入的数据控制,本设计中通过单片机来控制N 、A,改变N 、A 的值即可实现频道的选择。

可编程分频的原理及计算如下:根据吞咽脉冲计数的原理:吞咽脉冲计数器开始计数时,M的初值为1,÷A和÷N两个计数器被置入预置数并同时计数,当计到A(P+1)个输入脉冲(f o)时,÷A计数器计完A个预置数,M变为0;此时÷A计数器被控制信号关闭,停止计数;而÷N计数器中还有N -A个数,它继续计(N-A)P个输入脉冲后,输出一个脉冲到鉴相器PD。

pll锁相环的公式

pll锁相环的公式PLL锁相环是一种广泛应用于通信、计算机、控制等领域的电子设备,它的作用是将输入信号的频率锁定到参考信号频率上。

在PLL锁相环的设计中,计算PLL锁相环的公式是非常重要的,因为它能够推导出PLL锁相环的相关参数,从而影响其性能和稳定性。

本文将详细介绍PLL 锁相环的公式及其应用。

一、 PLL锁相环基本原理PLL锁相环是一种基于反馈的电子电路,可以将不同频率的信号锁定在一个稳定的参考信号上。

PL锁相环由三部分组成:比较器、低通滤波器和可变频率振荡器(VCO)。

比较器将输入信号和参考信号进行比较,输出的误差信号经过低通滤波器滤波后控制VCO的频率,以使得VCO的输出频率与参考信号的频率同步。

二、PLL锁相环的公式在PLL锁相环中,有以下基本参数:1. 相位差(Phase difference),用$\Delta\phi$ 表示。

它表示输入信号和参考信号的相位差,即两个信号的相位差。

2. 频率差(Frequency difference),用 $\Delta f$ 表示。

它表示输入信号和参考信号的频率差,即两个信号的频率之差。

3. 循环误差(Loop error),用 $\delta$ 表示。

它表示输出信号的相位与参考信号的相位差。

根据上述参数,PLL锁相环的公式如下:$$\delta = K_v\Delta f$$其中$K_v$是VCO的增益,即输出频率随输入电压的变化率。

它通常用Hz/Volts或MHz/Volts表示。

需要注意的是,上述公式中的单位应该保持一致。

例如,如果频率单位是kHz,那么增益单位应该是kHz/Volts。

三、PLL锁相环的应用PLL锁相环在通信、计算机、控制等领域都有广泛的应用。

例如:1. 频率合成器:通过PLL锁相环将输入信号锁定到参考信号的频率上,然后使用倍频器或分频器将输出信号的频率调整到所需要的频率,从而实现频率合成。

2. 时钟恢复:在数据传输中,使用PLL锁相环将接收到的数据中的时钟与本地时钟进行同步,以便正确接收数据。

adi锁相环配置参数

adi锁相环配置参数

ADI锁相环(PLL)是一种控制系统,用于将输入信号的相位和

频率与参考信号同步。

ADI公司提供了多种不同型号的锁相环芯片,每个型号都有不同的配置参数。

一般来说,ADI锁相环的配置参数

包括但不限于以下几个方面:

1. 输入信号频率和幅度,这些参数确定了锁相环需要跟踪的输

入信号的频率范围和幅度范围。

对于ADI锁相环芯片,通常会有特

定的输入频率范围和输入幅度范围的要求。

2. 参考信号频率和幅度,参考信号是锁相环的参考基准,其频

率和幅度对锁相环的性能和稳定性有重要影响。

配置参数中需要指

定参考信号的频率范围和幅度范围。

3. 锁相环环路滤波器参数,环路滤波器是锁相环中的重要组成

部分,其参数包括带宽、阶数、衰减等,这些参数会影响锁相环的

响应速度、抑制噪声等性能。

4. 输出参数,ADI锁相环芯片通常会有多种输出模式和输出接

口可选,配置参数需要包括输出信号的频率范围、幅度范围、输出

电平等。

5. 控制参数,锁相环的控制参数包括锁定时间、抖动性能、温度稳定性等,这些参数会影响锁相环的性能指标和稳定性。

在实际应用中,根据具体的系统需求和性能指标,需要根据数据手册和应用指南来配置ADI锁相环芯片的参数,以实现最佳的性能和稳定性。

同时,还需要考虑到电路设计、布局和调试等方面的因素,以确保锁相环能够正常工作并满足系统要求。

高频电路基础第5章-锁相环

vd

2

kViVo[sin

sin(2t

)

1 sin(2t

3

3 ) ......]

2021/3/18

高频电路基础

9

可能还会有两个输入都是方波的情况。 但不管哪种情况,输出信号中的低频分量均为

vd

1 2

kViVo

sin

Kd

sin[i (t) o (t)]

乘积型鉴相器的特点: • 定义两个输入正交时的相位差为0 • 输出电压平均值与两个输入的相位差的正弦成正比(所以

i (t) i (t)

鉴相器 vd (t) 环路滤波器 vc (t) 压控振荡器

PD

LF

VCO

分频电路 (可选)

o (t) o (t)

2021/3/18

高频电路基础

6

锁相环主要部件1——鉴相器

作用:比较输入与反馈两个信号的相位,输出与 相位差相关的电压(或电流)

形式:乘积型鉴相器 异或门鉴相器 边沿触发的RS触发器构成的鉴相器 边沿触发的鉴频-鉴相器

VCO

o (t) o (t)

瞬时相差: e ( t ) i ( t ) o ( t )

瞬时频差: (t) i (t) o (t)

d dt

e

(t

)

2021/3/18

高频电路基础

26

以算子 p 代表微分运算,则乘积型鉴相器(若采

用的其他鉴相器,可以相应的函数关系代替)、

环路滤波器、压控振荡器对于相位的数学运算表

不同环路滤波器情况下PLL的传递函数

简单RC

开环传递函数 H (s) K d K o

s(1 s)

闭环传递函数

(s)

s2

电荷泵锁相环环路滤波器参数设计与分析

电荷泵锁相环环路滤波器参数设计与分析作者:张涛陈亮来源:《现代电子技术》2008年第09期摘要:从环路滤波器的基本概念出发,主要论述了电荷泵锁相环环路滤波器参数的设计方法(包括1阶,2阶,3阶环路滤波器),通过比较闭环的参数设计方法的不足,提出了一种新的开环环路滤波器参数的设计方法,并做出总结,最后利用Cadence公司Virtuoso系列主要对二阶无源低通滤波器进行仿真,验证了本方法的正确性,有一定的实用价值。

关键词:电荷泵锁相环;低通滤波器;环路带宽;相位余度中图分类号:TN713 文献标识码:B文章编号:1004-373X(2008)09-087-Parameters′ Design and Analysis of the Charge Pump Phase-locked Loop′s Loop Filter(Information Science and Engineering College,Wuhan University of the Science and Technology,Wuhan,430081,China)Abstract:Based on the basic concept of loop filter,the paper mainly discusses the design method of the parameter of a charge pump phase-locked loop loop filter(concluding one order,two order,three order).According to compare with the design method of the parameter of closed loop,it puts forward a kind of design method which is the design method of the parameter of the opened loop,and make a summary.At last,making use of the Virtuoso series of the Cadence firm mainly to two order without source low-pass filter carry on imitate really,the accuracy of this method is verified,there is certain practical value.Keywords:charge pump phase-locked loop;low-pass filter;loop bandwidth;phase remaining环路滤波器的设计是电荷泵锁相环设计中的重要环节。

锁相环环路滤波器系数计算

锁相环环路滤波器系数计算锁相环(Phase-Locked Loop, PLL)是一种广泛应用于通信系统、时钟同步、频率合成等领域的电子电路。

而锁相环环路滤波器是锁相环中的重要组成部分,用于实现信号的滤波和抑制噪声。

本文将从锁相环环路滤波器的系数计算方法入手,详细介绍其原理和应用。

锁相环环路滤波器的设计目标是通过滤波器对输入信号进行滤波,使得输出信号的频率和相位与参考信号保持一致。

在锁相环中,环路滤波器通常采用低通滤波器的形式,用于滤除高频噪声和抑制输入信号的高频分量。

锁相环环路滤波器的系数计算主要包括滤波器的阶数、截止频率和滤波器类型等方面。

首先,确定滤波器的阶数,即滤波器的自由度。

一般来说,阶数越高,滤波器的性能越好,但计算复杂度也会增加。

根据实际需求和资源限制,选择适当的滤波器阶数。

确定滤波器的截止频率。

截止频率是指滤波器开始起作用的频率,通常用于抑制输入信号中的高频分量。

截止频率的选择应根据系统的频率范围和带宽要求进行,一般需要根据具体应用场景进行调整。

确定滤波器的类型。

常见的滤波器类型包括巴特沃斯滤波器、切比雪夫滤波器、椭圆滤波器等。

不同的滤波器类型具有不同的频率响应特性,如通带波纹、阻带衰减等。

根据具体应用需求和性能要求,选择合适的滤波器类型。

在锁相环环路滤波器的系数计算中,常用的方法包括频率抽样法和脉冲响应法。

频率抽样法是一种基于频域的计算方法,通过对输入信号和滤波器的频谱进行采样和计算,得到滤波器的系数。

脉冲响应法是一种基于时域的计算方法,通过对输入信号和滤波器的脉冲响应进行卷积运算,得到滤波器的系数。

在实际应用中,锁相环环路滤波器的系数计算需要考虑多种因素,如噪声抑制能力、滤波器的稳定性和计算复杂度等。

为了满足不同应用场景的需求,可以根据具体情况进行参数调整和优化。

除了滤波器系数的计算,锁相环环路滤波器的设计还需要考虑其他因素,如锁定范围、锁定时间和抗干扰能力等。

锁相环环路滤波器的设计是一个综合考虑多个因素的工程问题,需要结合具体应用场景和系统需求进行。

三阶锁相环环路滤波器参数设计

+ … + an = 0 ( a0 > 0 ) 的系统 , 当

4 三参数模型

本节推导的滤波器称为三参数滤波器 , 其模型 如下 :

F ( s) = as + bs + c 2 s

2

n = 3 时的劳思 - 赫尔维茨稳定判据为 : a1 a2 - a0 a3

计算出环路带宽 : 3 τ K 2 2 2 +3 2 τ τ 1 K BL = ・ 2 ・ 3 4 τ K τ 2 1 2 2 - 1 τ 1 将 r代入式 ( 11 ) ,整理得 : r 2r + 3 BL = ・ τ 4 2r - 1 2

[ 6, 8 ]

( 11 )

( 12 )

相位余量 : ωTτ < = 2a rc tg 2 - 90 °= 2a rc tg r - 90 ° ( 13 ) 利用 r的取值和式 ( 11 ) ,滤波器的参数为 r 2r + 3 τ ・ 2 = 4B L 2 r - 1 τ 1 = τ K 2

2 ( 1 + 2mξ ) ω2 ・ n k

mξ 3 ωn ・ k

( 21 )

式 ( 21 )即为所求的参数计算公式 , 可以利用进 行滤波器的参数设计 。其稳定性的分析采用劳思 图 2 三阶数字滤波器结构

赫尔维茨稳定判据 ,判据的内容如下 : 特征方程形如

D ( s) = a0 s + a1 s

Param eter D esign for L oop F ilter of Th ird - order PLL

WAN G Yu - zhou

( Southwest China Institute of Electronic Technology, Chengdu 610036, China ) Abstract: PLL has the w ide app lication in communication, telemetry and navigation field. B ecause of fre2 quency slope tracking capability, the third - order PLL gets more and more attention in the very narrow 2 band app lication for deep space exp loration. B y using of system stability analysis methods and high - order system analysis theory, the parameter designing formulas of two kinds of second - order loop filters which are ideal second - order and three - parameter filters are derived respectively . The analog and digital loop formulas of third - order PLL designing parameters are p rovided, and also compared w ith experienced for2 mulas of JPL ’ s DPLL designing param eters . The sim ulation results show that the three kinds of methods are sim ilar, but the position of system zero points, pole points and dump ing parameter in this deduced pa2 rameters design m ethod can be set freely, so it can p rovide p rincip les and app lication basis for each kind of variable bandw idth and adap tive algorithm. Key words: deep space exp loration; digital PLL (DPLL ) ; loop filter; stability condition; high - order system analysis; parameter design

matlab锁相环环路滤波器计算

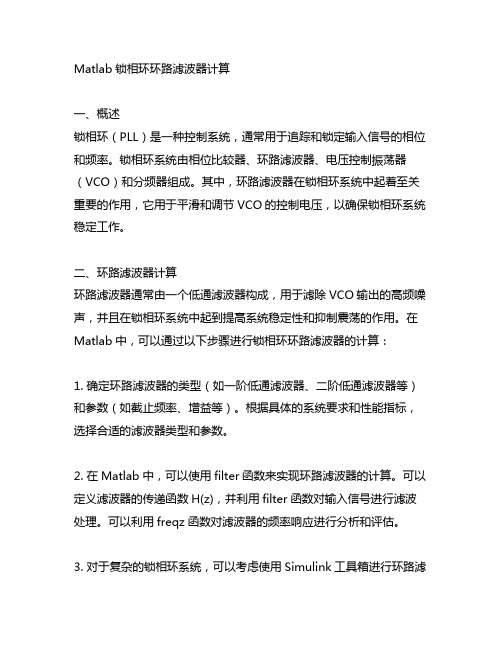

Matlab锁相环环路滤波器计算一、概述锁相环(PLL)是一种控制系统,通常用于追踪和锁定输入信号的相位和频率。

锁相环系统由相位比较器、环路滤波器、电压控制振荡器(VCO)和分频器组成。

其中,环路滤波器在锁相环系统中起着至关重要的作用,它用于平滑和调节VCO的控制电压,以确保锁相环系统稳定工作。

二、环路滤波器计算环路滤波器通常由一个低通滤波器构成,用于滤除VCO输出的高频噪声,并且在锁相环系统中起到提高系统稳定性和抑制震荡的作用。

在Matlab中,可以通过以下步骤进行锁相环环路滤波器的计算:1. 确定环路滤波器的类型(如一阶低通滤波器、二阶低通滤波器等)和参数(如截止频率、增益等)。

根据具体的系统要求和性能指标,选择合适的滤波器类型和参数。

2. 在Matlab中,可以使用filter函数来实现环路滤波器的计算。

可以定义滤波器的传递函数H(z),并利用filter函数对输入信号进行滤波处理。

可以利用freqz函数对滤波器的频率响应进行分析和评估。

3. 对于复杂的锁相环系统,可以考虑使用Simulink工具箱进行环路滤波器的建模和仿真。

Simulink提供了丰富的信号处理模块和仿真环境,可以方便地进行锁相环系统的设计、调试和优化。

三、环路滤波器设计注意事项在进行锁相环环路滤波器计算的过程中,需要注意以下几个方面的设计要点:1. 确定滤波器的截止频率和带宽:根据锁相环系统的频率特性和稳定性要求,选择合适的截止频率和带宽,以平衡相位延迟和抖动的性能指标。

2. 考虑滤波器的裙延迟和相位失真:在实际系统设计中,需要考虑滤波器的裙延迟和相位失真对系统稳定性的影响,尽量降低相位延迟和失真,以确保锁相环系统的性能。

3. 考虑VCO的控制电压范围:在设计环路滤波器时,需要考虑VCO的控制电压范围和动态范围,以确保滤波器对VCO控制电压的平滑调节和响应。

4. 考虑环路滤波器对系统稳定性的影响:在整个锁相环系统中,环路滤波器的稳定性和抑制震荡的能力是至关重要的,因此需要对滤波器的频率响应和动态特性进行充分的分析和评估。

锁相环基本原理

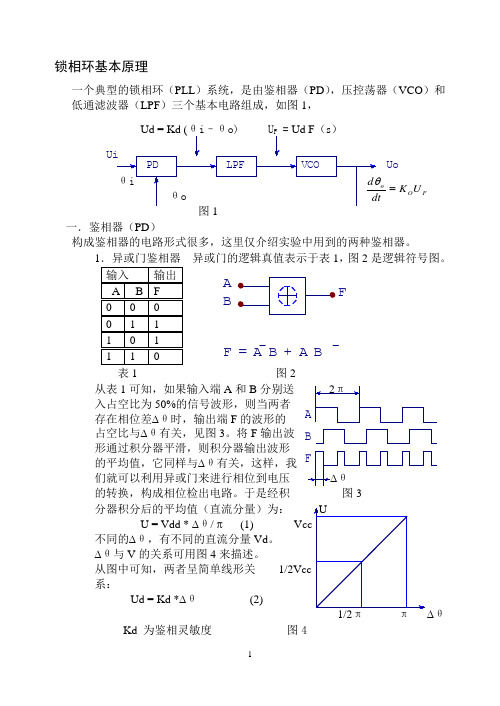

锁相环基本原理一个典型的锁相环(PLL )系统,是由鉴相器(PD ),压控荡器(VCO )和低通滤波器(LPF )三个基本电路组成,如图1,Ud = Kd (θi –θo) U F = Ud F (s )θi θo图1一.鉴相器(PD )构成鉴相器的电路形式很多,这里仅介绍实验中用到的两种鉴相器。

异或门的逻辑真值表示于表1,图2是逻辑符号图。

表1 图2从表1可知,如果输入端A 和B 分别送 2π 入占空比为50%的信号波形,则当两者存在相位差∆θ时,输出端F 的波形的 占空比与∆θ有关,见图3。

将F 输出波 形通过积分器平滑,则积分器输出波形 的平均值,它同样与∆θ有关,这样,我 们就可以利用异或门来进行相位到电压 ∆θ 的转换,构成相位检出电路。

于是经积 图3 分器积分后的平均值(直流分量)为: UU = Vdd * ∆θ/ π (1) Vcc不同的∆θ,有不同的直流分量Vd 。

∆θ与V 的关系可用图4来描述。

从图中可知,两者呈简单线形关 1/2Vcc 系:Ud = Kd *∆θ (2)1/2π π ∆θ Kd 为鉴相灵敏度 图4FO oU K dtd =θVP D L PF V CO U iU o VA B F__F = A B + A B F B A2. 边沿触发鉴相器 前已述及,异或门相位比较器在使用时要求两个作比较的信号必须是占空比为50%的波形,这就给应用带来了一些不便。

而边沿触发鉴相器是通过比较两输入信号的上跳边沿(或下跳边沿)来对信号进行鉴相,对输入信号的占空比不作要求。

二. 压控振荡器(VCO )压控振荡器是振荡频率ω0受控制电压U F (t )控制的振荡器,即是一种电压——频率变换器。

VCO 的特性可以用瞬时频率ω0(t )与控制电压U F (t )之间的关系曲线来表示。

未加控制电压时(但不能认为就是控制直流电压为0,因控制端电压应是直流电压和控制电压的叠加),VCO 的振荡频率,称为自由振荡频率ωom ,或中心频率,在VCO 线性控制范围内,其瞬时角频率可表示为: ωo (t )= ωom + K 0 U F (t )式中,K 0——VCO 控制特性曲线的斜率,常称为VCO 的控制灵敏度,或称压控灵敏度。

pll 环路参数的计算与建模

标题:PLL环路参数的计算与建模引言:相位锁定环路(Phase-Locked Loop,简称PLL)是一种常用的电子系统调频技术。

它可以将输入信号的频率与参考信号的频率进行同步,实现频率合成、时钟恢复等功能。

本文将详细介绍PLL环路参数的计算与建模方法,以帮助读者更好地理解和应用PLL技术。

一、PLL环路基本原理1.1 相位锁定环路的定义相位锁定环路是一种闭环控制系统,由相位比较器、积分环节、低通滤波器和VCO(Voltage-Controlled Oscillator,电压控制振荡器)组成。

通过不断调整VCO的频率或相位,使得输入信号与参考信号保持同步。

1.2 PLL环路的工作原理首先,相位比较器将输入信号与参考信号进行比较,得到相位误差信号。

然后,相位误差信号经过积分环节和低通滤波器处理后,控制VCO的频率或相位。

最终,VCO的输出信号被反馈给相位比较器,形成一个闭环控制系统。

二、PLL环路参数的计算2.1 带宽与稳定裕度PLL的带宽决定了其响应速度和稳定性。

带宽越大,系统的追踪能力越强,但也容易产生噪声和震荡。

带宽的计算可以根据系统的要求和参考信号的频率来确定。

稳定裕度是指PLL系统在输入信号频率变化时的稳定性,一般通过相位裕度和增益裕度来描述。

2.2 频率分辨率与拉RANGE频率分辨率是指PLL系统能够分辨的最小频率变化量,它与VCO 的调谐范围(拉RANGE)有关。

拉RANGE表示VCO可以调整的频率范围,一般由VCO的设计参数确定。

频率分辨率的计算可以通过拉RANGE除以分辨率比得到。

2.3 相位噪声与抖动相位噪声是指PLL系统输出信号在频谱上的相位随机变化。

抖动是指PLL系统输出信号的周期性相位扰动。

相位噪声和抖动对于某些应用场合具有重要影响,一般需要根据系统需求进行计算和优化。

三、PLL环路的建模方法3.1 传递函数模型传递函数模型是一种常用的PLL环路建模方法,通过建立输入信号与输出信号之间的传递函数关系,可以分析PLL系统的频率响应和稳定性。

锁相环

所谓锁相环路,实际是指自动相位控制电路(APC),它是利用两个电信号的相位误差,通过环路自身调整作用,实现频率准确跟踪的系统,称该系统为锁相环路,简称环路,通常用PLL表示。

锁相环路是由鉴相器(简称 PD)、环路滤波器(简称 LPF或LF)和压控振荡器(简称 VCO)三个部件组成闭合系统。

这是一个基本环路,其各种形式均由它变化而来PLL概念设环路输入信号v i= V im sin(ωi t+φi)环路输出信号v o= V om sin(ωo t+φo)——其中ωo=ωr+△ωo通过相位反馈控制,最终使相位保持同步,实现了受控频率准确跟踪基准信号频率的自动控制系统称为锁相环路。

PLL构成由鉴相器(PD)环路滤波器(LPF)压控振荡器(VCO)组成的环路。

PLL原理从捕捉过程→锁定A.捕捉过程(是失锁的)a.φi┈φi均是随时间变化的,经相位比较产生误差相位φe=φi-φo,也是变化的。

b.φe(t)由鉴相器产生误差电压v d(t)=f(φe)完成相位误差—电压的变换作用。

v d(t)为交流电压。

c. v d(t)经环路滤波,滤除高频分量和干扰噪声得到纯净控制电压,由VCO产生控制角频差△ω0,使ω0随ωi变化。

B.锁定(即相位稳定)a.一旦锁定φe(t)=φe∞(很小常数)v d(t)= V d(直流电压)b.ω0≡ωi输出频率恒等于输入频率(无角频差,同时控制角频差为最大△ω0max, 即ω0=ωr+△ω0max。

ωr为VCO固有振荡角频率。

)锁相基本方程和相位模型(时域)★★各部件相位模型★鉴相器(PD)相位模型⊙数学模式v d(t)=A D sinφe(t)⊙相位模式★环路滤波器(LPF)相位模式⊙数学模式v c(t)=A F(P)v d(t)⊙相位模式★压控振荡器(VCO)相位模式⊙数学模式⊙相位模式★★环路相位模型★相位模式:指锁相环(PLL)输入相位和输出相位的反馈调节关系。

★相位模型:把鉴相器,环路滤波器和压控振荡器三个部件的相位模型依次级联起来就构成锁相相位模型。

电荷泵锁相环环路滤波器的设计与优化

电荷泵锁相环环路滤波器的设计与优化廉吉庆;陈大勇;翟浩【摘要】环路滤波器是锁相环电路的重要部分,其性能好坏直接决定了电路输出信号的质量.以二阶无源环路滤波器为例介绍了电荷泵锁相环环路滤波器的设计方法,讨论了基于相位裕度和设计参数γ的环路滤波器优化设计,并且给出了仿真结果.结果证明这种环路滤波器设计方法正确,优化方法切实可行.【期刊名称】《时间频率学报》【年(卷),期】2015(000)001【总页数】6页(P38-43)【关键词】环路滤波器;锁相环;电荷泵;相位裕度;参数优化【作者】廉吉庆;陈大勇;翟浩【作者单位】兰州空间技术物理研究所,兰州730000;空间量子频标技术核心专业实验室,兰州730000;真空技术与物理重点实验室,兰州730000;兰州空间技术物理研究所,兰州730000;空间量子频标技术核心专业实验室,兰州730000;真空技术与物理重点实验室,兰州730000;兰州空间技术物理研究所,兰州730000;空间量子频标技术核心专业实验室,兰州730000;真空技术与物理重点实验室,兰州730000【正文语种】中文【中图分类】TN74频率源广泛应用于现代电子设备中,其指标好坏直接影响电子系统的性能,因此频率源被许多人称为电子系统的“心脏”。

常用的频率源有自激振荡源和合成频率源,其中合成频率源使用灵活、控制方便、性能优越,越来越受到人们的重视。

常用的频率合成技术中,锁相环是非常重要的一种,在高速通信、导航定位和航空航天等方面都有应用。

环路滤波器是锁相环的重要组成部分,它连接在鉴相器和压控振荡器之间,起到维持环路稳定性、控制环路带内外噪声、抑制参考边带杂散干扰等重要作用,是锁相环频率合成器设计的关键[1]。

目前已有许多文章对环路滤波器设计方法进行了讨论,但在关于滤波器性能的一些细节优化设计方面,并未深入探讨。

本文在环路滤波器设计基础上,探讨针对环路锁定时间和输出噪声等方面的优化设计,并通过仿真验证优化设计的正确性。

(完整版)环路滤波器

常用的环路滤波器是一个线性低通滤波器,它可以滤除误差电压中的高频分量和噪声。

常用的有RC积分滤波器、无源比例积分滤波器和有源比例积分滤波器。

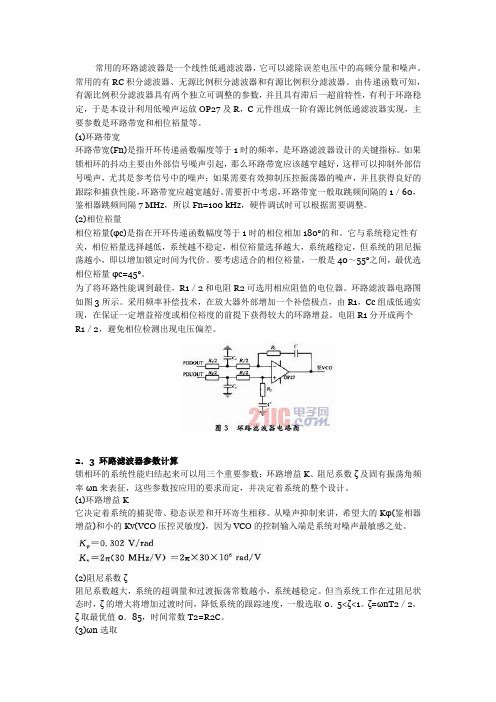

由传递函数可知,有源比例积分滤波器具有两个独立可调整的参数,并且具有滞后一超前特性,有利于环路稳定,于是本设计利用低噪声运放OP27及R,C元件组成一阶有源比例低通滤波器实现,主要参数是环路带宽和相位裕量等。

(1)环路带宽环路带宽(Fn)是指开环传递函数幅度等于1时的频率,是环路滤波器设计的关键指标。

如果锁相环的抖动主要由外部信号噪声引起,那么环路带宽应该越窄越好,这样可以抑制外部信号噪声,尤其是参考信号中的噪声;如果需要有效抑制压控振荡器的噪声,并且获得良好的跟踪和捕获性能,环路带宽应越宽越好。

需要折中考虑,环路带宽一般取跳频间隔的1/60,鉴相器跳频间隔7 MHz,所以Fn=100 kHz,硬件调试时可以根据需要调整。

(2)相位裕量相位裕量(φc)是指在开环传递函数幅度等于1时的相位相加180°的和。

它与系统稳定性有关,相位裕量选择越低,系统越不稳定,相位裕量选择越大,系统越稳定,但系统的阻尼振荡越小,即以增加锁定时间为代价。

要考虑适合的相位裕量,一般是40~55°之间,最优选相位裕量φc=45°。

为了将环路性能调到最佳,R1/2和电阻R2可选用相应阻值的电位器。

环路滤波器电路图如图3所示。

采用频率补偿技术,在放大器外部增加一个补偿极点,由R1,Cc组成低通实现,在保证一定增益裕度或相位裕度的前提下获得较大的环路增益。

电阻R1分开成两个R1/2,避免相位检测出现电压偏差。

2.3 环路滤波器参数计算锁相环的系统性能归结起来可以用三个重要参数:环路增益K、阻尼系数ζ及固有振荡角频率ωn来表征,这些参数按应用的要求而定,并决定着系统的整个设计。

(1)环路增益K它决定着系统的捕捉带、稳态误差和开环寄生相移。

从噪声抑制来讲,希望大的Kφ(鉴相器增益)和小的Kv(VCO压控灵敏度),因为VCO的控制输入端是系统对噪声最敏感之处。

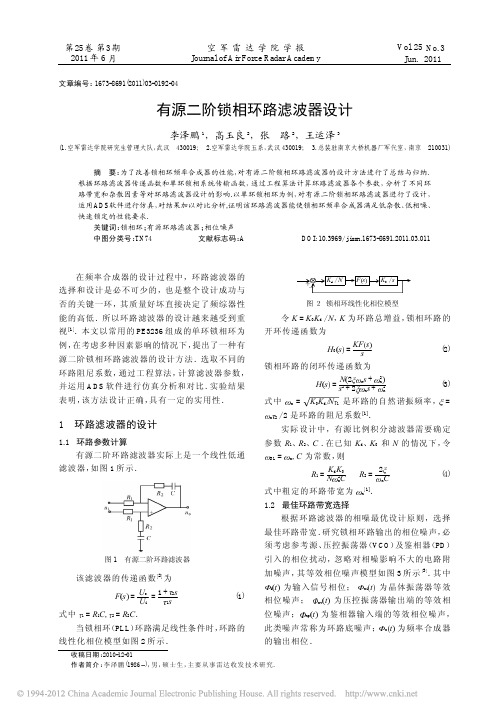

有源二阶锁相环路滤波器设计

6

(6)

194

200.00 150.00 100.00 dB (Vout_Open_Lp) phase (Vout_Open_Lp)

空 军雷 达学 院 学报

200.00 150.00 100.00 dB (Vout_Open_Lp) phase (Vout_Open_Lp) 200.00 150.00 100.00 dB(Vout_Open_Lp) phase (Vout_Open_Lp) m1 freq=20.00 kHz phase (Vout_Open_Lp) =-134.347 m1

m1 freq=21.54 kHz PNTotal=-109.045

-100.0

-150.0

-150.0

-150.0

-200.0 1.00 10.00 100.0 1.00k 10.00k 100.0k 1.00M 10.00M

-200.0 1.00 10.00 100.0 1.00k 10.00k 100.0k 1.00M 10.00M

-150.00 -200.00 1.00 10.00 100.0 1.00k 10.00k 100.0k 1.00M 10.00M

频率 / Hz

频率 / Hz

频率 / Hz

(a) = 0.5

(b) = 0.7

(c) = 0.9

图5

-50.0

开环频域响应曲线

PNTotal PN_VCO_only PN_Ref_only PN_PFD_only m1 -50.0 m1 freq=21.54kHz PNTotal=-109.870 PNTotal PN_VCO_only PN_Ref_only PN_PFD_only m1

参考频率相位噪声 M F H I X A J O

滤波电路电容电感计算公式

滤波电路电容电感计算公式滤波电路是电子电路中常见的一种电路,用于滤除输入信号中的杂波或者对输入信号进行频率选择。

在滤波电路中,电容和电感是两种常见的元件。

在设计滤波电路时,需要计算电容和电感的数值,以满足滤波器的性能要求。

本文将介绍滤波电路中电容和电感的计算公式,并且讨论它们在滤波电路中的应用。

电容的计算公式。

在滤波电路中,电容通常用于对输入信号进行滤波。

电容的数值取决于所需的截止频率和电路的阻抗。

电容的计算公式如下:C = 1 / (2 π f R)。

其中,C为电容的数值,单位为法拉德(F);f为所需的截止频率,单位为赫兹(Hz);R为电路的阻抗,单位为欧姆(Ω);π为圆周率。

根据上述公式,可以得出电容的数值。

在实际设计中,需要根据具体的滤波要求和电路的特性来选择合适的电容数值。

电感的计算公式。

电感也是滤波电路中常用的元件,用于对输入信号进行滤波或者频率选择。

电感的数值取决于所需的截止频率和电路的阻抗。

电感的计算公式如下:L = R / (2 π f)。

其中,L为电感的数值,单位为亨利(H);R为电路的阻抗,单位为欧姆(Ω);f为所需的截止频率,单位为赫兹(Hz);π为圆周率。

根据上述公式,可以得出电感的数值。

在实际设计中,需要根据具体的滤波要求和电路的特性来选择合适的电感数值。

电容和电感在滤波电路中的应用。

电容和电感是滤波电路中不可或缺的元件,它们可以单独使用,也可以组合在一起使用,以实现不同类型的滤波效果。

在低通滤波器中,电容和电感通常被串联使用。

电容的作用是阻止低频信号通过,而电感的作用是允许高频信号通过。

通过合理选择电容和电感的数值,可以实现对低频信号的滤波效果。

在高通滤波器中,电容和电感通常被并联使用。

电容的作用是允许高频信号通过,而电感的作用是阻止低频信号通过。

通过合理选择电容和电感的数值,可以实现对高频信号的滤波效果。

除了单独使用电容和电感外,它们还可以组合在一起使用,形成多种不同类型的滤波电路,如带通滤波器、陷波滤波器等。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

R1=(Kd*Kφ)/(ω*ω*N*C2),

R2=2ξ/(ωn*C2);

其中Kd是鉴相器的鉴相灵敏度,HMC440的Kd是0.286 V/rad,Kφ是VCO的压控灵敏度(rad/V),N是锁相环的倍频倍数。阻尼系数ξ为兼顾滤波器的过冲和衰减取0.707~1之间的一个值即可。

4、有源环路的特点总结如下:

有源环路滤波器的用处十分广泛,例如有源环路能够提供较高的环路增益,因此可以使锁相环具备较宽的同步带等,有时VCO以及其他振荡器的调谐范围非常宽而导致调谐电压非常高,这是可以采用有源环路来实现;但是这种情况下由于运算放大器的放大倍数太高而导致相噪恶化以及产生不必要的频率调制现象等等。但是,实际上有源环路的优点远远多于其缺点的,一般来说,不要把倍数放大得太高,反而可以降低环路上的杂散以及优化相位噪声,例如:可以优化环路滤波器的电阻带来的噪声等等;所以合适地使用有源环路中的运放,会收到比无源意想不到的效果。

3、采用有源的常常为以下几个方面:

要求锁相环具备极好的稳定性时建议用有源方式,虽然无源方式也能锁定;

不采用捷变频并且要求振荡器的调谐电压非常高的时候

对相位噪声等要求非常高,例如仪器仪表等;虽然无源方式也能锁定;(此时需要一定的基础才行)并且此时的运算放大器选择也非常讲究,我一般选择BB公司的OPA227等运放;

纯粹模拟锁相环,例如利用混频器鉴相,二极管鉴相等等;

相噪要求非常高场合,例如相噪要求小于-140dBc/Hz@10KHz等等不一而足;

极窄锁相环时,例如深空探测等的锁相环,极低的锁相时间要求,例如环路带宽要求100KHz以上等等建议用有源方式;

总之,何时用有源何时用无源,需要根据实际情况而定,不能一概而论;

最后根据实际情况进行适当调整。

1、 环路带宽的选择比较灵活,一般来说,取鉴相频率的1/10到1/30,例如,鉴相频率为1MHz,环路带宽一般选20KHz左右,但是这并非绝对,因为不同的项目有不同的指标,其环路带宽选择也不一样。1/10到1/30环路带宽的选择主要是综合了杂散抑制、相噪指标以及锁相时间得出的一个综合考虑。所以根据不同的情况,其选择范围是十分灵活的。不能一概而论。

2、楼主采用的HMC440器件,一般用于光传输系统以及要求信道数量不多的情况下使用,该器件的基底噪声较低,但远远不是最低,因为这类器件采用的工艺与常见的数字鉴相器不一样,如果我没有记错的话,该器件采用的是ECL工作方式来保证高速鉴相和基底噪声抑制,另外,该器件与其他数字鉴相器相比较,其鉴相增益较低,因此采用有源方式工作来满足环路的锁定以及环路的稳定性。这类器件没什么窍门,详细看一下datasheet就明白。 只要C2取Βιβλιοθήκη 一个值,就可以同时确定R1,R2。

C1的主要滤除鉴相器产生的谐波,一般来说其引入的极点应远离主极点,一般取ωc=1/(R1C1)>10ωn。也即C1<1/(10ωnR1)。

例如:环路带宽取300~400 kHz。ξ取0.707,N=136,C2=2 200 pF则l元件的取值为:R1=200 Ω,C1=470 pF,R2=430 Ω,

4、环路滤波器的仿真可以用ADS中的designguide,具有很多锁相环仿真,可以参考一下;另外我一般不仿真,所以我不知道如何用ADS来仿真。建议从事频率源的同时多用手工计算,这样了解得更加深入。

5、目前大部分的锁相芯片都是针对移动通信以,其芯片的自身指标并不高,在很多特殊的场合并不能满足要求,所以很多情况下都需要自己用电路来搭建自己需要的鉴频鉴相器