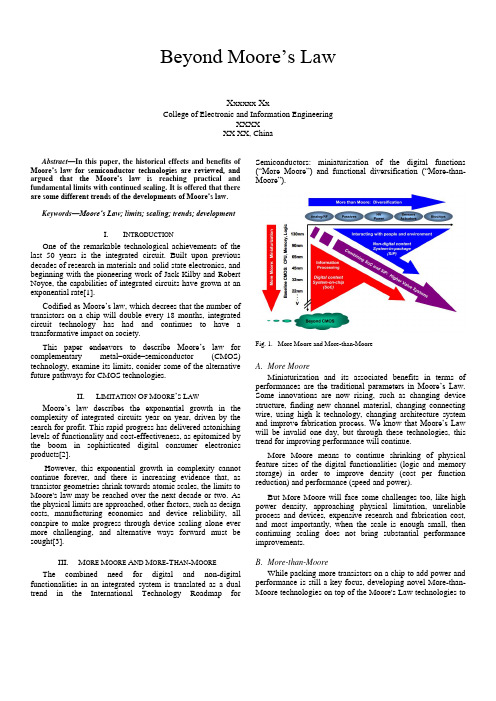

more than moore,MEMS

国际半导体技术发展路线图

国际半导体技术发展路线图为了回答如何保持半导体产业按照摩尔定律继续发展的问题,国际上主要的半导体协会共同组织制定了国际半导体技术发展路线图ITRS《International technology roadmap for semiconductors》它为半导体产业界提供了被工业界广泛认同的;对未来十年内研发需求的最佳预测以及可能的解决方案,它对整个半导体茶叶需要开发什么样的技术起到了一个导向作用。

国际半导体技术发展路线图一、半导体产业生态环境半导体产业诞生于上世纪70年代,当时主要受两大因素驱动:一是为计算机行业提供更符合成本效益的存储器;二是为满足企业开发具备特定功能的新产品而快速生产的专用集成电路。

到了80年代,系统规范牢牢地掌握在系统集成商手中。

存储器件每3年更新一次半导体技术,并随即被逻辑器件制造商采用。

在90年代,逻辑器件集成电路制造商加速引进新技术,以每2年一代的速度更新,紧跟在内存厂商之后。

技术进步和产品性能增强之间不寻常的强相关性,使得相当一部分系统性能和利润的控制权转至集成电路(IC)制造商中。

他们利用这种力量的新平衡,使整个半导体行业收入在此期间年均增速达到17%。

21世纪的前十年,半导体行业全新的生态环境已经形成:一是每2年更新一代的半导体技术,导致集成电路和数以百万计的晶体管得以高效率、低成本地生产,从而在一个芯片上或同一封装中,可以以较低的成本整合极为复杂的系统。

此外,封装技术的进步使得我们可以在同一封装中放置多个芯片。

这类器件被定义为系统级芯片(system on chip,SOC)和系统级封装(system in package, SIP)。

二是集成电路晶圆代工商能够重新以非常有吸引力的成本提供“新一代专用集成电路”,这催生出一个非常有利可图的行业——集成电路设计。

三是集成电路高端设备的进步带动了相邻技术领域的发展,大大降低了平板显示器、微机电系统传感器、无线电设备和无源器件等设备的成本。

MEMS Industry Status & Trends

Future

Consumer and Medical dominance * IDMs + Outsourcing by IDMs * Specialty MEMS Foundries (Low volume, high value products) * CMOS Foundries (Low cost, high volume products)

Manufacturing

Wafer size

* 8” dominance * 12”emergence

Processes/Packages with Reusable IP and building blocks for multiple products

Customization

Technology

© 2012 •

3-10 years High

2-4 years Low

7

2011-2020 MEMS Market Forecast in $M

MF PS

MF IS

IS PS

© 2012 •

8

2011-2020 MEMS Market Forecast in units

RF

IS

MP

IS

© 2012 •

9

MEMS Market Value Forecast Evolution

MEMS微系统 复习红宝书(北理)

20.BGA : Ball Grid Array 球状矩阵排列

21.SHM:Structural Health Monitoring 结构健康监测

22.ICT:Information and Communications Technologies 信息与通信技术

23.MtM More than Moore 超越摩尔定律

24.FEA:Finite Element Analysis 有限元分析

25.SEM:Scanning Electron Microscope 扫描电子显微镜

12.ITRS International technology Roadmap for Semiconductor 国际半导体技术规

划

.

27.DARPA :Defence Advanced Research Projects Agency of theDepartment of

成,它们各具不同的能带隙。这些材料可以是 GaAs 之类的化合物,也可以是 Si-Ge 之类的半导体合金。按异质结中两种材料导带和价带的对准情况可以把异 质结分为Ⅰ型异质结和Ⅱ型异质结两种。 12.微加工:以微小切除量获得很高精度的尺寸和形状的加工。 13.引线键合:引线键合(Wire Bonding)是一种使用细金属线,利用热、压力、 超声波能量为使金属引线与基板焊盘紧密焊合,实现芯片与基板间的电气互连和 芯片间的信息互通。 14. 倒装芯片:倒装芯片(Flip chip)是一种无引脚结构,一般含有电路单元。 设 计用于通过适当数量的位于其面上的锡球(导电性粘合剂所覆盖),在电气上和 机械上连接于电路。 15.热声焊:热声焊是一种固态键合技术,为热压结合与超音波结合的混合方法。 它可完成电路片与芯片、腔体之间的电连接。 16.各向异性粘接:用各向异性导电胶(主要使用单一或双重成分的环氧树脂)完 成对电路基板与倒装芯片之间的互连。 17.柔性印刷电路:即 FPC,是以聚脂薄膜或聚酰亚胺为基材制成的一种具有高度 可靠性,绝佳曲挠性的印刷电路。通过在可弯曲的轻薄塑料片上,嵌入电路设计, 使在窄小和有限空间中堆嵌大量精密元件,从而形成可弯曲的挠性电路。 18.高深宽比:垂直于加工表面的高度与其加工表面上所具有的特征尺寸的比值 大。 19. 盲孔: 定义 1.位于印刷线路板的顶层和底层表面,具有一定深度,用于表层线路和下面 的内层线路的连接,孔的深度通常不超过一定的比率(孔径)。

系统级封装技术(SiP)引领封测产业的“混搭”潮

系统级封装技术(SiP)引领封测 产业的 混搭 潮 产业的“混搭”潮2010年6月25号混搭英文原词为Mix and Match。

混搭是一个时尚界专用名词,指将不同 风格,不同材质,不同身价的东西按照个人口味拼凑在 起,从而混合 风格,不同材质,不同身价的东西按照个人口味拼凑在一起,从而混合 搭配出完全个人化的风格,就是不要规规矩矩,是一种时髦,但决不能 等同于胡穿乱配的毫无章法。

混搭最典型的莫过于韩式混搭,韩国街头流行起一种更实用,更有味道 的混搭新哲学。

穿出层次,叠穿法则是混搭哲学中最基础课程,其中最 奏 重要的是搭配的节奏感,这也正是混搭风能在当今流行的重要原因。

系统级封装技术的特点非常符合和“混搭”的精髓,有一 脉相承 异曲同工之处 脉相承、异曲同工之处内容1、系统级封装的发展背景 2、系统级封装的定义 系统级封装的定义 3、系统级封装的优势 系统级封装的优势 4、系统级封装的成本 5、长电科技系统级封装技术及服务的介绍 6、长电科技系统级封装产品及应用 长电科技系统级封装产品及应用 7、总结1、系统级封装的发展背景¾当今社会,电子系统的发展趋势是小型化、高性能、多功能、高 可靠性和低成本,在这些需求的强力驱动下,电子产品的演进速度 超乎寻常 ¾在物联网、移动支付、移动电视、移动互联网、3G通讯等新生应 用的引导下,一大批新型电子产品孕育而生 ¾目前系统级封装产品在计算机、汽车电子、医疗电子、军事电子、 消费类电子(手机 蓝牙 消费类电子(手机、蓝牙、Wi-Fi、交换机等)等领域内都有巨大 交换机等)等领域内都有巨大 的市场 ¾系统级芯片(System 系统级芯片(S t on Chip, Chi SoC)的发展随着摩尔定律的脚 S C)的发展随着摩尔定律的脚 步不断演进,然而随着SoC发展至深次微米以下先进制程世代后, 已经面临极大的技术发展瓶颈,SoC已难面面俱到。

后摩尔时代的特色工艺及中国发展机遇

2022年第5期 总第198期科学传播后摩尔时代的特色工艺及中国发展机遇◎ 张 波我国是集成电路的市场大国,半导体工艺技术的发展,怎么也绕不开摩尔定律。

1965年,时任美国仙童半导体(Fairchild Semiconductor)公司研发主管的摩尔(Gordon E. Moore)博士为《电子学》杂志撰写了一篇文章“Cramming More Components onto integrated circuits”,预测集成电路的集成度(单芯片集成晶体管数目)每年增加一倍。

1975年,已参与创建英特尔(Intel)公司的摩尔博士在IEDM(国际电子器件年会)以“Progress in digital integrated electronics”为题做主题报告,进一步将集成电路集成度的发展速度修订为每两年增加一倍。

这就是半导体业界著名的“摩尔定律”(Moore's Law)。

一、半导体行业进入后摩尔时代摩尔定律自诞生以来一直指引着半导体工艺技术的发展,这也是英特尔公司很长一段时间坚持两年一代工艺和Tick-Tock发展战略的主要依据。

长期以来,集成电路集成度的提升依赖于工艺线宽的不断缩小,从早期的10微米工艺线宽逐步缩小到现在的7纳米、5纳米工艺节点,这是以摩尔定律为引领的单一维度创新发展。

但随着集成电路工艺线宽持续降低,特别是半导体微细加工工艺进入纳米尺度后,建厂成本、工艺研发和产品研制等费用急剧增加。

一条先进的集成电路生产线建厂成本已高达150亿~200亿美元,超过新一代航空母舰(130亿美元)或一座新核电站(40亿~80亿美元)的建设成本;一个采用5纳米工艺节点的先进集成电路产品开发成本也已超过5亿美元。

因此,从2005年开始,集成电路工艺技术逐渐从单一追求尺寸依赖的先进工艺,向先进工艺(More Moore)、非尺寸依赖的特色工艺(More than Moore)和先进封装(System in Package:SiP)三个维度并举发展,半导体行业进入后摩尔时代。

可穿戴设备与MEMS的现状和趋势

Lagging

Galaxy S

Accelerometer E-Compass Si Microphone Proximity

Catch up

Galaxy S2

Accelerometer E-Compass Si Microphone Proximity Gyroscope Ambient Light

iPhone 5

Accelerometer E-Compass Gyroscope Si Microphone Proximity Ambient Light

Sensor Expansion

三星接力苹果

Exceeding

Galaxy S3 Galaxy S4

Accelerometer E-Compass Si Microphone Proximity Gyroscope Ambient Light Barometer Accelerometer E-Compass Si Microphone Proximity Gyroscope Ambient Light Barometer Temperature Humidity Hall Sensor RGB Sensor Gesture Sensor

可穿戴设备现状和趋势

© 2013 • 9

2013年——可穿戴计算年

• 谷歌、三星、苹果、微软等科技界的佼佼者都 有计划开发自己的可穿戴设备。因此,很多人 把2013年称为“可穿戴计算年”。 • 根据美国地区关于可穿戴技术的调查数据显示:

– 87%受访者认为可以提升佩戴者的个人综合能力 – 71%的受访者则认为有利于个人健康状况的改善 – 还有54%的受访者认为提升了他们的自信

© 2013 • 2

计算机技术的发展潮流

摩尔定律讲义

Drain

• S/D leakage current • Gate leakage current

Power

• • • • •

Surface scattering - mobility High E-field - mobility DIBL drain to source leakage IOFF Subthreshold slope >> ln(10)kT/q IOFF VG - VT decrease ION

2.特点:

一是:采用非CMOS的等比例缩小方法,将集成电感、 电容等占据大量PCB空间的无源元件集成在封装内,甚至芯 片上,使电子系统进一步小型化,以达到提高其性能的目的。 二是:按需要向电子系统集成“多样化”的非数字功能, 形成具有感知、通信、处理、致动等功能的微系统。

3.目的:

对环境智能所需要的意识和响应能力实现全面补充,使 人体和环境实现直接接口 模拟和模拟/混合信号技术、RF技术、高压/功率技术、 光电子技术、生物技术MEMS/NEMs和传感/致动等多学 科和多学科融合技术

4.技术组成:

汽车 通信 MTM 军事 娱乐 安全 医疗

三、Beyond CMOS

碳纳米管

2009年美国NSF启 动超越摩尔定律的科 学与工程 SEBML(Science and Engineering Beyond Moore‘s Law)项目要 求全新的科学、工程 和概念框架。例如: 碳纳米管、器件小型 化和系统中容错技术 等等。

6.解决方案

两个对策:More-Than-Moore & Beyond CMOS

二、 More-Than-Moore

摩尔定律讲义综述

4.技术组成:

汽车 通信 MTM 军事 娱乐 安全 医疗

三、Beyond CMOS

碳纳米管

2009年美国NSF启 动超越摩尔定律的科 学与工程 SEBML(Science and Engineering Beyond Moore‘s Law)项目要 求全新的科学、工程 和概念框架。例如: 碳纳米管、器件小型 化和系统中容错技术 等等。

Channel/Drain

Drain

• S/D leakage current • Gate leakage current

Power

• • • • •

Surface scattering - mobility High E-field - mobility DIBL drain to source leakage IOFF Subthreshold slope >> ln(10)kT/q IOFF VG - VT decrease ION

3.半导体发展趋势:

2001(年)

2003 2005 2007 2009 2011

130(nm)

90 65 45 32 22

4.装置

应用

5.困难:

5.1 制造成本的技术制约

硅片价格与掩模成本趋势

$1,600

制造成本

$1,400 $1,200 $1,000 $800 $600 $400 $200 $0 Q3 Q4 Q1 Q2 Q3 2008 2008 2009 2009 2009 0.35nm 0.25nm 0.18nm 0.15nm 0.13nm

6.解决方案

两个对策:More-Than-Moore & Beyond CMOS

微电子学概论知识点

1什么是微电子学答: 微电子学作为电子学的一门分支科学,主要是研究电子或离子在固体材料中的运动规律及其应用,并利用它实现信号处理功能的科学。

2什么叫集成电路?答:Integrated Circuit,缩写IC通过一系列特定的加工工艺,将晶体管、二极管等有源器件和电阻、电容等无源器件,按照一定的电路互连,“集成”在一块半导体单晶片(如硅或砷化镓)上,封装在一个外壳内,执行特定电路或系统功能3集成电路的分类:按器件结构类型分类:双极集成电路,金属-氧化物-半导体(MOS)集成电路,双极-MOS(BiMOS)集成电路按集成电路规模分类↗小规模集成电路(Small Scale IC,SSI)↗中规模集成电路(Medium Scale IC,MSI)↗大规模集成电路(Large Scale IC,LSI)↗超大规模集成电路(Very Large Scale IC,VLSI)↗特大规模集成电路(Ultra Large Scale IC,ULSI)↗巨大规模集成电路(Gigantic Scale IC,GSI)按结构形式的分类:单片集成电路,混合集成电路(厚膜集成电路、薄膜集成电路)按电路功能分类:数字集成电路,模拟集成电路,数模混合集成电路4微电子学的特点答:(1)、微电子学是一门综合性很强的边缘学科涉及了固体物理学、量子力学、热力学与统计物理学、材料科学、电子线路、信号处理、计算机辅助设计、测试与加工、图论、化学等多个学科(2)、微电子学是一门发展极为迅速的学科,高集成度、低功耗、高性能、高可靠性是微电子学发展的方向(3)、微电子学的渗透性极强,它可以是与其他学科结合而诞生出一系列新的交叉学科,例如微机电系统(MEMS)、生物芯片等5半导体及其基本特征是什么?导体:自然界中很容易导电的物质称为导体绝缘体:有的物质几乎不导电,称为绝缘体,半导体:另有一类物质的导电特性处于导体和绝缘体之间,称为半导体固体材料:超导体: 大于106(Ωcm)-1导体: 106~104(Ωcm)-1半导体: 104~10-10(Ωcm)-1绝缘体: 小于10-10(Ωcm)-1半导体的导电机理不同于其它物质,所以它具有不同于其它物质的特点:(基本特征)1、在纯净的半导体材料中,电导率随温度的上升而指数增加;2、半导体中杂质的种类和数量决定着半导体的电导率,而且在重掺杂情况,温度对电导率的影响较弱;3、在半导体中可以实现非均匀掺杂;4、光的辐照、高能电子等的注入可以影响半导体的电导率。

电-热多物理场耦合的对偶有限元分析

电-热多物理场耦合的对偶有限元分析殷英;徐小宇;闰帅;任卓翔【摘要】随着集成电路、微机电系统的快速发展,各种物理场的交互作用成为影响电路可靠性或者增加设计难度的重要问题.其中,大量工程应用中都会发生稳恒电流场和热场的相互作用.电流场产生的焦耳热与电阻率的温变持性是这两个物理场之间双向相互耦合的联系因素.当几何结构复杂时,分析该多物理场问题会有计算方面的挑战.通常利用有限元法来求解多物理问题,其中采取节点单元法来处理电流场.本论文首先在多物理耦合分析中实现了棱边单元法来分析电流场,并通过一个典型的微阻梁算例问题,与常规方法进行充分对比,考察了随着网格加密、与热场耦合迭代深度的对偶持点及收敛持性.【期刊名称】《电子设计工程》【年(卷),期】2018(026)021【总页数】5页(P11-15)【关键词】对偶方程方法;有限元法;多物理场;稳态电热耦合【作者】殷英;徐小宇;闰帅;任卓翔【作者单位】中国科学院微电子研究所北京100029;中国科学院大学北京100049;三维及纳米集成电路设计自动化北京市重点实验室北京100029;中国科学院微电子研究所北京100029;三维及纳米集成电路设计自动化北京市重点实验室北京100029;中国科学院微电子研究所北京100029;三维及纳米集成电路设计自动化北京市重点实验室北京100029;中国科学院微电子研究所北京100029;三维及纳米集成电路设计自动化北京市重点实验室北京100029【正文语种】中文【中图分类】TN402集成电路沿着More Moore、More than Moore等方向不断迅速发展,一方面,集成电路的集成度越来越高,功耗与散热成为影响与制约电路性能与可靠性的核心因素,另一方面,各种物理效应也可以在微机电系统(MEMS)之中用于各类传感器、执行器等的设计。

因而,电磁学、热学、力学等多物理场的耦合分析变得尤其必要,并已经在集成电路领域受到关注及快速发展[1-5]。

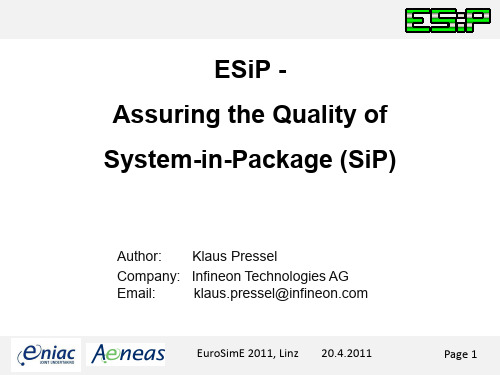

EuroSimE-2011-ENIAC-session-ESiP

EuroSimE 2011, Linz

20.4.2011

Page 3

ESiP – Assuring the quality of SiP

Content: 1) 2) 3) 4) 5) General information on the project Challenges for SiP Project set-up and management Highlights and first results Conclusion

ESiP - a project on 3D system integration reliability, failure analysis and test

„More than Moore“ is important chance for European microelectronics.

ESiP supports European applications for earlier introduction into manufacturing and into market.

Issues

Size

Interconnect Gap

Cost RF-Performance Shielding

Package as Interposer

Heat dissipation Reliability Environment

Customer Board (800 µm 500 µm)

Miniaturization Moore: More Moore) (More Scaling

130nm 90nm 65nm 45nm 32nm 22nm . . . V

Interacting with people and environment

Beyond_Moore's_Law

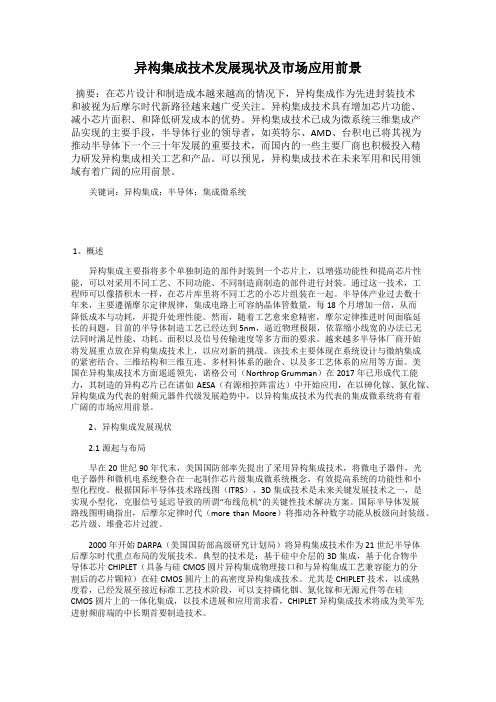

Beyond Moore’s LawXxxxxx XxCollege of Electronic and Information EngineeringXXXXXX XX, ChinaAbstract—In this paper, the historical effects and benefits of Moore’s law for semiconductor technologies are reviewed, and argue d that the Moore’s law is reaching practical and fundamental limits with continued scaling. It is offered that there are some different trends of the developments of Moore’s law.Keywords—Moore’s Law; limits; scaling; trends; developmentI.I NTRODUCTIONOne of the remarkable technological achievements of the last 50 years is the integrated circuit. Built upon previous decades of research in materials and solid state electronics, and beginning with the pioneering work of Jack Kilby and Robert Noyce, the capabilities of integrated circuits have grown at an exponential rate[1].Codified as Moore’s law, which decrees that the number of transistors on a chip will double every 18 months, integrated circuit technology has had and continues to have a transformative impact on society.This paper endeavors to describe Moore’s law for complementary metal–oxide–semiconductor (CMOS) technology, examine its limits, conider some of the alternative future pathways for CMOS technologies.II.L IMITATION O F M OORE’S L AWMoore’s law describes the exponentia l growth in the complexity of integrated circuits year on year, driven by the search for profit. This rapid progress has delivered astonishing levels of functionality and cost-effectiveness, as epitomized by the boom in sophisticated digital consumer electronics products[2].However, this exponential growth in complexity cannot continue forever, and there is increasing evidence that, as transistor geometries shrink towards atomic scales, the limits to Moore's law may be reached over the next decade or two. As the physical limits are approached, other factors, such as design costs, manufacturing economics and device reliability, all conspire to make progress through device scaling alone ever more challenging, and alternative ways forward must be sought[3].III.M ORE M OORE A ND M ORE-T HAN-M OORE The combined need for digital and non-digital functionalities in an integrated system is translated as a dual trend in the International Technology Roadmap for Semiconductors: miniaturization of the digital functions (“More Moore”) and functional diversification (“More-than-Moore”).Fig. 1.More Moore and More-than-MooreA.More MooreMiniaturization and its associated benefits in terms of performances are the traditional parameters in Moore’s Law. Some innovations are now rising, such as changing device structure, finding new channel material, changing connecting wire, using high k technology, changing architecture system and improve fabrication process. We know that Moore’s Law will be invalid one day, but through these technologies, this trend for improving performance will continue.More Moore means to continue shrinking of physical feature sizes of the digital functionalities (logic and memory storage) in order to improve density (cost per function reduction) and performance (speed and power).But More Moore will face some challenges too, like high power density, approaching physical limitation, unreliable process and devices, expensive research and fabrication cost, and most importantly, when the scale is enough small, then continuing scaling does not bring substantial performance improvements.B.More-than-MooreWhile packing more transistors on a chip to add power and performance is still a key focus, developing novel More-than-Moore technologies on top of the Moore's Law technologies toprovide further values to semiconductor chips has also becomea more important issue.More-than-Moore means that Incorporation into devices offunctionalities that do not necessarily scale according to “M oore’s L aw”, but provide addition al value in different ways.More-than-Moore approach allows for the non-digitalfunctionalities to migrate from the system board-level into thepackage (sip) or onto the chip (soc).The second trend is characterized by functionaldiversification of semiconductor-based devices. These non-digital functionalities do contribute to the miniaturization ofelectronic systems, although they do not necessarily scale at the same rate as the one that describes the development of digital functionality. Consequently, in view of added functionality, this trend may be designated “More-than-Moore” (MtM).But we will face some problems by using the technologies of More-than-Moore. Such as integration of More Moore with More-than-Moore and Creation of intelligent compact systems.More-than-Moore technologies cover a wide range of fields. For example, MEMS applications include sensors, actuators and ink jet printers. RF CMOS applications include Bluetooth, GPS and Wi-Fi. CMOS image sensors are found in most digital cameras. High voltage drivers are used to power LED lights. These applications add value to computing and memory devices that are made from the traditional Moore's Law technology.Fig. 2.2007 ITRS “Moore’s Law and More” Definition Graphic Proposal Fig.2 is a definition of “Moore’s Law and More”. The red part is More Moore and the blue part is More-than-Moore. The red part contains the computing and data storage logic, while the blue part contains RF, HH Power, Passives, Sensors, Actuators, Bio-chips, Fluidics and other functionalities.parisonComparing More Moore and More-than-Moore from Fig.3 and Fig.4, we can draw some conclusions:•More Moore has smallest footprint but limited functionality.•More-than-Moore has full functionality but complex supple chain.They all have advantages and disadvantages. We can use them according to specific application. Fig. 3.Following Moore’s Law is one approach:Monolithic CMOS logic System-on-ChipFig. 4.Adding More-than-Moore is another: System-on-Chip and System-in-PackageIn modern society, the concept of Internet of Things is verypopular. In the past, people may pay attention to computingand storage more, so the IC industry develops rapidly following Moore’s Law. But now, people pay more attention tointernet of things, biomedical and so on. That is to say, peopleneed more demands of the IC besides the computing andstorage functionality.Fig. 5.An ideal application of More-than-MooreFig.5 is an example of More-than-Moore, of course, it is anideal application. But it shows some benefits of this trend.IV.B EYOND C MOSA.What is Beyond CMOSWhat we have talked about before is all based on Si-based CMOS technology. But we should realize that Si-based CMOS technology cannot do everything, especially when the transistors continue shrinking of physical feature sizes towards atomic scale.Fig. 6.More Moore, More-than-Moore and Beyond CMOSWhat More Moore do is to continue to go forward along the road of “Moore’s Law”. And More-than-Moore do is to d evelop and extend “Moore’s Law”. When the scaling bellows about 10nm, traditional Si-based CMOS technology may be invalid. So what Beyond CMOS want to do is to invent new devices or technologies when Si-based CMOS comes across its limitation.Fig. 7.Some new devices and technologyThe main idea of Beyond CMOS is to invent one or several new type switches which can replace the Si-based CMOS to process information. So these ideal devices need to have higher function density, higher performance, less power consumption, acceptable manufacturing cost, stable enough and suitable for large-scale manufacturing and so on.B.Several new devices1)Tunneling FET(TFET)TFET mainly according to the principle of tunneling of quantum mechanics, directly goes through channel from the source to drain rather than by diffusion. Fig. 8.Tunneling FET(TFET)2)Quantum Cellular Automata (QCA)Representing the binary information by changing the structure of the Cellular.Transmitting information based on neighbor interaction.Fig. 9.Quantum Cellular Automata (QCA)Fig. 10.Quantum Cellular Automata (QCA)3)Atomic Switch(QCA)Atomic switch based on the formation and the annihilation of the metal atoms bridge between the two electrons, forming a gate-control switch mode.Fig. 11.Atomic Switch4)SpinFETSpinFET use the spinning direction of electron to carry information.Fig. 12.SpinFETFig. 13.SpinFETThey all have advantages or dis advantages. Maybe they are not the best devices, but they represent the potential development trend of the devices in the future[4].V.S UMMARYMicroelectronics therefore seeks to develop in new ways, not only to continue to deliver better performance in traditional markets, but also to grow into new markets based on devising new, non-electronic, functions on integrated circuits.Microelectronics relies on complementary metal oxide semiconductor (CMOS) technology, the backbone of the electronics industry. Beyond Moore's law, it is foreseen that microelectronics will be a platform to support optical, chemical and biotechnology to deliver a step change beyond electronics-only integration.R EFERENCES[1]Cavin R K, Lugli III P, Zhirnov V V. Science and engineering beyondMoore's law[J]. Proceedings of the IEEE, 2012, 100(Special Centennial Issue): 1720-1749.[2]Cumming D R S, Furber S B, Paul D J. Beyond Moore's law[J].Philosophical transactions. Series A, Mathematical, physical, and engineering sciences, 2014, 372(2012).[3]Saraswat K C. How far can we push Si CMOS and what are thealternatives for future ULSI[C]//Device Research Conference (DRC), 2014 72nd Annual. IEEE, 2014: 3-4.[4]Kazior T E. Beyond CMOS: heterogeneous integration of III–V devices,RF MEMS and other dissimilar materials/devices with Si CMOS to create intelligent microsystems[J]. Philosophical Transactions of the Royal Society of London A: Mathematical, Physical and Engineering Sciences, 2014, 372(2012): 20130105.。

异构集成技术发展现状及市场应用前景

异构集成技术发展现状及市场应用前景摘要:在芯片设计和制造成本越来越高的情况下,异构集成作为先进封装技术和被视为后摩尔时代新路径越来越广受关注。

异构集成技术具有增加芯片功能、减小芯片面积、和降低研发成本的优势。

异构集成技术已成为微系统三维集成产品实现的主要手段,半导体行业的领导者,如英特尔、AMD、台积电已将其视为推动半导体下一个三十年发展的重要技术,而国内的一些主要厂商也积极投入精力研发异构集成相关工艺和产品。

可以预见,异构集成技术在未来军用和民用领域有着广阔的应用前景。

关键词:异构集成;半导体;集成微系统1、概述异构集成主要指将多个单独制造的部件封装到一个芯片上,以增强功能性和提高芯片性能,可以对采用不同工艺、不同功能、不同制造商制造的部件进行封装。

通过这一技术,工程师可以像搭积木一样,在芯片库里将不同工艺的小芯片组装在一起。

半导体产业过去数十年来,主要遵循摩尔定律规律,集成电路上可容纳晶体管数量,每18个月增加一倍,从而降低成本与功耗,并提升处理性能。

然而,随着工艺愈来愈精密,摩尔定律推进时间面临延长的问题,目前的半导体制造工艺已经达到5nm,逼近物理极限,依靠缩小线宽的办法已无法同时满足性能、功耗、面积以及信号传输速度等多方面的要求。

越来越多半导体厂商开始将发展重点放在异构集成技术上,以应对新的挑战。

该技术主要体现在系统设计与微纳集成的紧密结合、三维结构和三维互连、多材料体系的融合、以及多工艺体系的应用等方面。

美国在异构集成技术方面遥遥领先,诺格公司(Northrop Grumman)在2017年已形成代工能力,其制造的异构芯片已在诸如AESA(有源相控阵雷达)中开始应用,在以砷化镓、氮化镓、异构集成为代表的射频元器件代级发展趋势中,以异构集成技术为代表的集成微系统将有着广阔的市场应用前景。

2、异构集成发展现状2.1源起与布局早在20世纪90年代末,美国国防部率先提出了采用异构集成技术,将微电子器件,光电子器件和微机电系统整合在一起制作芯片级集成微系统概念,有效提高系统的功能性和小型化程度。

超越摩尔,一文看懂SiP封装技术

超越摩尔,一文看懂SiP封装技术根据TRS的定义:SiP为将多个具有不同功能的有源电子元件与可选无源器件,以及诸如MEMS或者光学器件等其他器件优先组装到一起,实现一定功能的单个标准封装件,形成一个系统或者子系统。

从架构上来讲,SiP是将多种功能芯片,包括处理器、存储器等功能芯片集成在一个封装内,从而实现一个基本完整的功能。

与SOC(片上系统)相对应。

不同的是系统级封装是采用不同芯片进行并排或叠加的封装方式,而SOC则是高度集成的芯片产品。

1.1. More Moore VS More than Moore——SoC与SiP之比较SiP是超越摩尔定律下的重要实现路径。

众所周知的摩尔定律发展到现阶段,何去何从?行业内有两条路径:一是继续按照摩尔定律往下发展,走这条路径的产品有CPU、内存、逻辑器件等,这些产品占整个市场的50%。

另外就是超越摩尔定律的More than Moore路线,芯片发展从一味追求功耗下降及性能提升方面,转向更加务实的满足市场的需求。

这方面的产品包括了模拟/RF器件,无源器件、电源管理器件等,大约占到了剩下的那50%市场。

针对这两条路径,分别诞生了两种产品:SoC与SiP。

SoC是摩尔定律继续往下走下的产物,而SiP则是实现超越摩尔定律的重要路径。

两者都是实现在芯片层面上实现小型化和微型化系统的产物。

SoC与SIP是极为相似,两者均将一个包含逻辑组件、内存组件,甚至包含被动组件的系统,整合在一个单位中。

SoC是从设计的角度出发,是将系统所需的组件高度集成到一块芯片上。

SiP是从封装的立场出发,对不同芯片进行并排或叠加的封装方式,将多个具有不同功能的有源电子元件与可选无源器件,以及诸如MEMS或者光学器件等其他器件优先组装到一起,实现一定功能的单个标准封装件。

从集成度而言,一般情况下,SoC只集成AP之类的逻辑系统,而SiP 集成了AP+mobile DDR,某种程度上说SIP=SoC+DDR,随着将来集成度越来越高,emmc也很有可能会集成到SiP中。

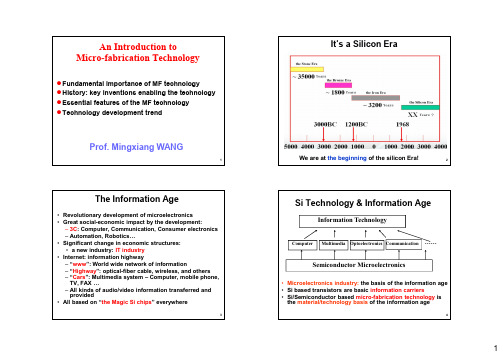

introductiontomicro-fabricationtechnology

1An Introduction toMicro-fabrication Technology●Fundamental importance of MF technology●History: key inventions enabling the technology ●Essential features of the MF technology ●Technology development trendProf. Mingxiang WANG2It’s a Silicon EraWe are at the beginning of the silicon Era!The Information Age•Revolutionary development of microelectronics •Great social-economic impact by the development:–3C : Computer, Communication, Consumer electronics –Automation, Robotics…•Significant change in economic structures:• a new industry: IT industry •Internet: information highway–“www ”: World wide network of information–“Highway ”: optical-fiber cable, wireless, and others –“Cars ”: Multimedia system –Computer, mobile phone, TV, FAX …–All kinds of audio/video information transferred and provided•All based on “the Magic Si chips ” everywhere3Si Technology & Information Age•Microelectronics industry: the basis of the information age •Si based transistors are basic information carriers•Si/Semiconductor based micro-fabrication technology is the material/technology basis of the information ageInformation TechnologyComputer Multimedia CommunicationOptoelectronics ……Semiconductor Microelectronics4Historical milestones:key inventions enablingthe IC micro-fabrication technology •1st transistor 1947•1st junction transistor 1949•1st integrated circuit 1958•1st monolithic integrated circuit 1959•Invention of the planar process 1960•1st silicon MOSFET 19605Invention of Transistor•1947.12.23: Invention of pointcontact transistor by Bardeen &Brattain–1st paper on Transistor: “Thetransistor, a semiconductortriode”, Phys. Rev. 74, 230,1948–By Webster’s:Transistor = transfer + resistortransferring electrical signalacross a resistor6How does the 1st transistor works? John Bardeen, Nobel lecture, Dec.11, 1956 Semiconductor research leading to the pointcontact transistor7First transistor & its inventors 1947, John Bardeen, Walter Brattain & William Shockley,Bell lab (1956 Nobel Prize winner in Physics)8 Shockley developed basic theory of transistor (1948-1952)First PN Junction TransistorWilliam Shockley Gordon Teal Morgan SparksGordon Teal and Morgan Sparks made the first junction transistor in 1949,the construction of which eliminated many of the reliability problems of the point contact transistor.99/21/2013•1958.9.12 1st IC---“Solid Circuit” by J. Kilby of TI –Flip-flop phase shift oscillator–On Ge substrate–Mesa structure with 1 BJT, 3R, and 1C–Etching by black wax protection–Wire bond interconnect2000 Nobel Prize in Physics on Integrated Circuits (shared with Afilov and Kroemer )First Integrated Circuit101st monolithic IC by R.N. Noyce 1959 (Fairchild) –First micro-chip –On Si substrate–Flip-flop circuit with 6devices by Al interconnect –Based on Si BJT which is first made in 1954 (TI)First monolithic IC11Invention of Planar Process•1958-1960 b asic IC process developed: oxidation (Atalla; bell Lab), pn junction isolation (K. Levovec), Al film evaporation…•1960Si planar process inventedInventor :Jean Hoerni --Fairchild1213First MOS Transistors1st MOSFET Bell lab 1960•1959-63: MOS devices–1959: MOS capacitor (J. Moll; Stanford)–1960: Kahng & Atalla(Bell lab), structure same as modern MOSFETs –1960-63: research on Si surface & MOS devices (Sah, Deal, Grove…)–1963: concept of CMOS (Wanlass, Sah; Fairchild)14Modern Micro-Processor Unit1st CPU, 2300T Intel 4004, 1971, 8umIntel dual-core MPU, 410MT ,Nov. 2007, 45nm15Flowchart of IC fabrication16Essential Featuresof Micro-fabrication Technology●Extremely capital intensiveHeavy capital Investment for clean rooms & Fab equipments ●Batch Process:>100 Billion Transistors per wafer ●Outstanding Manufacturability : Yield>95% per lot●Extremely cheap productsContinuously lower price per function ●Technology widely extendable17Capital intensive●Heavy capital investment for -clean rooms -fab equipments-materials used in a fab: rigorous requirements ●Estimated cost for a fab-Intel’s Fab22 in Arizona (8-inch, 0.13μm, copper based) opened in October 2001 cost 2 billion USD (cost of 2 Tsing Ma Bridges!)-Cost for a new 12-inch 45-65nm generation fab cost about 10 billion USD->70% cost used for equipments●NOT affordable by most countries!18300mm Global Fab LandscapeUnited States IBM Bldg 323Infineon Richmond Intel D1C Intel D1D Intel F11x Intel F12C Micron MTC TI DMOS 6TI DMOS 7JapanElpida Fab 1Elpida Fab 2Renesas/ Trecenti Toshiba OitaSony Kumamoto Sony Fab 2 Nagasaki Toshiba Yokkaichi City NEC Elec Yamagata TaiwanPowerchip Fab 1ProMOS Fab 2TSMC Fab 12A & B UMC Fab 12AInotera (Nanya + Infineon)Powerchip Fab 1Powerchip Fab 2TSMC Fab 14SingaporeUMC SingaporeEuropeAMD Fab 36Infineon SC300Intel Fab 24Crolles2 (TD)(STM, Philips, Moto)STM CataniaKoreaSamsung Line 12Samsung Line 13Samsung Line 14Sources: Silicon Strategies, EE Times, Nikkei Microelectronics, Industry MeetingsChinaSMIC Fab 419Toshiba Oita Works 300 mm Fab TSMC300 mm Super clean room in Tsukuba,SeleteIntel fabFab20NikonArF Scanner l = 193nm 2004Contact mask aligner 1970’sMainstream photo-lithography21Single Crystal Silicon300mm and 400mm Silicon Ingots w/o a single defects22When do we start planning for nextwafer size transition?9 yrs + 2 yrs delay*9 yrs + 6 yrs delay? 9 yrs + ?yrs delay675mm/2025?450mm/2015?300mm/2001200mm/1990 (125/150mm -1981)We are hereWhen does this happen?23Batch process●Requirement of cost recoveryhave to produce >10,000 wafers per month to recover the cost of 12-inch fab investment●Batch process->100 Billion transistors per wafer fabricated in parallel-sometimes ~20 wafers per lot processed in parallel -extremely productive●The essential feature of the planar process ●Ensure that fabricated products are cheap24Intel 300 mm75 mm, 100 mm, 50 mmWafers25Outstanding Manufacturability●Yield >95%per lot to earn money -evaluated by chip function●About 108(0.1 billion) transistors per ULSI chip, which would FAIL if only one transistor, one metal line, one contact or one other component fails!●What’s the yield at transistor/component level to achieve 95% yield at chip level?●Reliability: lifetime >10yrs●What’s other technologies could have such ability? -yield, batch process, micro/nano-fabrication, …26Modern MPU Chip1st CPU, 2300T Intel 4004, 1971, 8um Intel dual-core MPU, 410MT ,Nov. 2007, 45nm27Inside the chips28Electron Micrograph on MOS interface29Continuously cheaper products●Moore’s law means exponential decay of the price per function●What’s the price of a “car” if Moore’s law also holds?●The continuous price reduction is a tremendous competitiveness over traditional technology●Cheap product means the tremendous impact of the new technology is affordable to everyone!●A simple and strong reason why Silicon Era becomes the reality30Technology extendable●It’s more than an IC technology!●It’s more than just 3Cs,the micro-fabrication technology is widelyextendable to address almost all issues in our life ●Solar cells, photo-voltaic industry, energy harvest ●LED lightings●Flat panel displays, Thin film electronics ●MEMS devices: Sensors and Actuators ●Bio-chips, Health care…●It’s another strong reason why we are in Silicon Era!31Other applications of micro-fabrication(Source: University of Florida)32MEMS devices: an extension of Siplanar processEtched profiles of MEMS structures33Technology Development Trends ●Moore’s Law:would continues for another 30yrs ●More than Moore (MtM):●Micro-Systems: SoC, SiPMoore’s Law•Double the number of transistor every 18-24 months •Exponential growth ofsemiconductor technology & industry (A common law at early stage for a new industry under rapid development)•Govern the trend since 1960 and would continue in the next 20-30 yrs •An economics law of technology and market expansionFirst proposed in 1965by Gordon Moore ,co-founder of Intel3435New Generations under Moore’s Law●A new generationper 18-24 months ●X0.7 Min. feature size scaling ●X2 increase in transistor density ●X1.5 faster device switching speed ●Reduced chip power●Reduced chip cost●Increased functionality3619001950196019702000Vacuum Tube Transistor IC LSI VLSI 10 cm cm mm 10 m m 100 nm In 100 yrs, the feature size reduced by 106times Technology driver: BJT —CMOS —DRAM/CPU —Flash —Communication10-1m10-2m10-3m10-5m10-7mDownsizing of the components has been the driving force for circuit evolution37Transistor Scaling38Device feature sizeIntel 90nm Tech. Node Transistor Smallest species: VirusIn another 30yrs, device feature size wouldapproach molecular size <1nm (could be a limit), before which Moore’s law still continues.The Paradox of Moore’s Law●As transistors grow smaller, opportunities grow largerAs the basic element of information,and the basis ofthe information society ,IC &related micro-fabrication technology have been deeply involving into all hi-tech fields.3940More than Moore’s Law●More than Moore (MtM) Law:●System level Integration: SoC, SiP , it is the system that matters !●Micro-fabrication technology follows the trend of SoC and SiP, under Moore’s law as well as under More than Morre’s Law .9/21/2013414344。

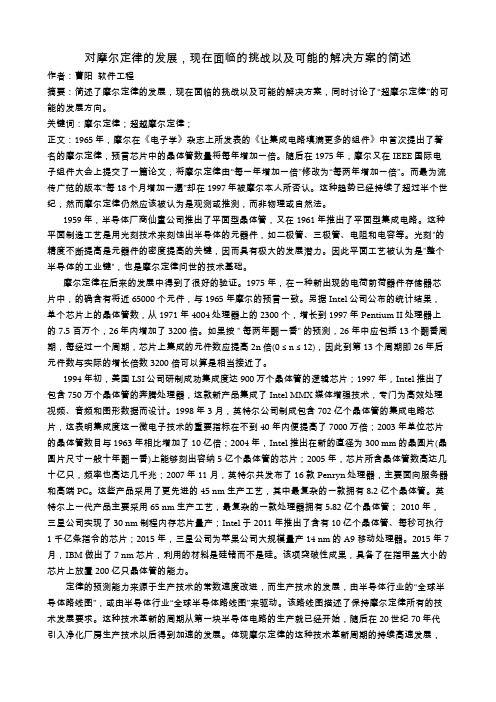

对摩尔定律的发展,现在面临的挑战以及可能的解决方案的简述

对摩尔定律的发展,现在面临的挑战以及可能的解决方案的简述作者:曹阳软件工程摘要:简述了摩尔定律的发展,现在面临的挑战以及可能的解决方案,同时讨论了“超摩尔定律”的可能的发展方向。

关键词:摩尔定律;超越摩尔定律;正文:1965年,摩尔在《电子学》杂志上所发表的《让集成电路填满更多的组件》中首次提出了著名的摩尔定律,预言芯片中的晶体管数量将每年增加一倍。

随后在1975年,摩尔又在IEEE国际电子组件大会上提交了一篇论文,将摩尔定律由“每一年增加一倍”修改为“每两年增加一倍”。

而最为流传广范的版本“每18个月增加一遍”却在1997年被摩尔本人所否认。

这种趋势已经持续了超过半个世纪,然而摩尔定律仍然应该被认为是观测或推测,而非物理或自然法。

1959年,半导体厂商仙童公司推出了平面型晶体管,又在1961年推出了平面型集成电路。

这种平面制造工艺是用光刻技术来刻蚀出半导体的元器件,如二极管、三极管、电阻和电容等。

光刻"的精度不断提高是元器件的密度提高的关键,因而具有极大的发展潜力。

因此平面工艺被认为是"整个半导体的工业键",也是摩尔定律问世的技术基础。

摩尔定律在后来的发展中得到了很好的验证。

1975 年,在一种新出现的电荷前荷器件存储器芯片中,的确含有将近65000 个元件,与1965 年摩尔的预言一致。

另据Intel公司公布的统计结果,单个芯片上的晶体管数,从1971 年4004 处理器上的2300 个,增长到1997 年Pentium II处理器上的7.5 百万个,26年内增加了3200 倍。

如果按 " 每两年翻一番" 的预测,26 年中应包括13 个翻番周期,每经过一个周期,芯片上集成的元件数应提高2n倍(0 ≤ n ≤ 12),因此到第13 个周期即26 年后元件数与实际的增长倍数3200 倍可以算是相当接近了。

1994 年初,美国LSI公司研制成功集成度达900万个晶体管的逻辑芯片;1997 年,Intel推出了包含750 万个晶体管的奔腾处理器,这款新产品集成了Intel MMX媒体增强技术,专门为高效处理视频、音频和图形数据而设计。

3-Plenary-JMC-FINAL

Technology R&Dand ManufacturingJean-Marc CheryExecutive Vice PresidentChief Manufacturing & Technology Officer,General Manager, Digital SectorAgenda2IntroductionTechnology –Embedded Processing SolutionsTechnology –Sense & Power and AutomotiveManufacturingConclusionAgenda3IntroductionTechnology –Embedded Processing SolutionsTechnology –Sense & Power and AutomotiveManufacturingConclusionThe Right Model for Our Industry4Advanced Technology R&D & Innovation Application-targetedprocess & packagedevelopmentOptimized in-housemanufacturingprocessesCollaborative Technology R&D ISDA, FoundryPartnersFlexiblemanufacturingFoundry PartnersOSAT partnersSimplicityCost, QualityFigures of MeritDesign LegacySupply securityISDA: International Semiconductor Development AllianceOSAT: Outsourced Assembly and TestScalabilityTime to marketTechnology Portfolio Enabling Business5S e n s e & P o w e r a n d A u t o m o t i v e P r o d u c t sE m b e d d e d P r o c e s s i n g S o l u t i o n sPackagingAutomotive Products GroupAnalog, MEMS& SensorsIndustrial & Power DiscreteMicrocontrollers, Memory & SecurityDigitalConvergence GroupImaging, BiCMOS ASIC & Silicon PhotonicsProcessAdvanced CMOS FD-SOIPower & DiscreteAnalog Mixed Signal/RFeNVMBCDMEMSBiCMOSCMOS Image Sensor Agenda6IntroductionTechnology –Embedded Processing Solutions Technology –Sense & Power and Automotive Manufacturing ConclusionEPS -Technology Roadmap7CMOS Digital (including RF)Prototyping start2014/152016/17201328nm UTBB FD-SOI14nm UTBB FD-SOI10nm UTBB FD-SOIFD-SOI: Fully Depleted Silicon On IsolatorUTBB: Ultra Thin Body and BOX (Buried Oxide)•Convergence to FinFET expected at 7nm•FinFET know-how being developed in the framework of the ISDA Alliance•Superior technology at 28nm delivering what customers want •ST products based on FD-SOI have competitive advantage •Winning ASIC business thanks to performance/power and simpler process than alternative •Yield Learning Equivalent to Traditional Bulk ProcessBest in Class Technology at 28nm820%40%60%80%100%120%140%0%20% 40% 60% 80% 100% 120% 140%0.60.81.01.21.40.20.4Speed (DMIPS)P o w e r e f f i c i e n c y (D M I P S /m W )V d d (V )+30%>3x+43%+45%28nm Planar UTBB FD-SOI vs 28nm BulkContinuing Technology Superiority at 14nm928nm FD-SOI 14nm FD-SOI + FBBPerformance @ same VddPower @ same High speedArea scaling28nm FD-SOI14nmFD-SOI + RBB28nm FD-SOI+30%-50%-40%+15%-10%RBB: Reverse Body Bias14nm FD-SOI 14nm FD-SOI 14nm FD-SOIFBB: Forward Body Bias Planar UTBB FD-SOI :Scalability obtained by reduction of T SOI & T BOX10Node 28nm 14nm 10nm T SOI (nm)7.5 6.56T BOX (nm)252015T SOI BOXT SO IBOXT SOIBOX•Electrostatic control improved by Thinning T BOX •Scalability down to 10nm node•Devices already processed with 3.5nm SOI filmPerformancePlanar UTBB FD-SOI ScalabilityBoosters Roadmap11+30%a t s a m e V d d+20%a t s a m e V d d28nm FD-SOI14nm FD-SOI10nm FD-SOIIn-situ doped Raised Source Drain (RSD)SiGe channel for PFETStrained SOI15nm BOX2nd gen RSD & SiGechannel 15nm BOXV th and µ boostImproved RaccessImproved RaccessBoosted back biasµ boostDoped Doped SiGeDoped Doped SiGeRaccess : Access resistance of the transistor in ON stateµ: electron mobiltyVth : Transistor Threshold voltage SiGe : Silicon Germanium PFET : P-channel MOSFET BOX : Buried OxideEPS -Technology Roadmap12Prototyping start2014/152016/172013CMOS ImagingBiCMOS & Photonics1.4μP BSI / 1.1μP BSI Photonics 25Gbps 0.9μP BSI BiCMOS 55nmAdvanced architecture Photonics 40GbpsCollaborative R&D through agreement with UMC BSI: Backside IlluminationCMOS Digital (including RF)28nm UTBB FD-SOI14nm UTBB FD-SOI10nm UTBB FD-SOIHigh Speed IOs Image Sensors Differentiating Factors13Optimized Design SolutionColorisation / micro-lens StitchingOptical SimulationsSPADTSV -WLPTSV: Though Silicon Via WLP : Wafer-Level PackageBSIBSI: Backside IlluminationDTIDTI:Deep Trench IsolationEPS -Technology Roadmap14Prototyping start2014/152016/172013CMOS eNVM* (Automotive micro)CMOS eNVM* (GP/secure micro)*Logic with embedded memories55nm NOR80nm NOR / 90nm PCM40nm NOR 40nm NOR28nm PCMeNVM: embedded Non Volatile Memory PCM: Phase Change MemoriesCMOS Digital (including RF)28nm UTBB FD-SOI14nm UTBB FD-SOI10nm UTBB FD-SOICMOS ImagingBiCMOS & Photonics1.4μP BSI / 1.1μP BSI Photonics 25Gbps 0.9μP BSI BiCMOS 55nmAdvanced architecture Photonics 40GbpsNon-Volatile Memory Differentiators15Phase Change Memory (PCM) TechnologyAmorphousphaseCrystalline phase1Top electrode GSTBottom electrodeHeaterBit cell (In state “1”)1NOR 40nm eFlashPhase change materialGST : GeSbTe, Germanium-Antimony-Tellurium alloy•Breakthrough for process cost saving and improved performance •Power consumption fitting RF requirements•Most mature solution among novel memory concepts•Qualification for the 90nm nodeEPS -Technology Roadmap16Prototyping start2014/152016/172013CMOS eNVM* (Automotive micro)CMOS eNVM* (GP/secure micro)*Logic with embedded memories55nm NOR80nm NOR / 90nm PCM40nm NOR 40nm NOR28nm PCMFD-SOI: Fully Depleted Silicon On IsolatorUTBB: Ultra Thin Body and BOX (Buried Oxide)Cooperative R&D through agreement with FoundryBSI: Backside IlluminationeNVM: embedded Non Volatile Memory PCM: Phase Change MemoriesCMOS Digital (including RF)28nm UTBB FD-SOI14nm UTBB FD-SOI10nm UTBB FD-SOICMOS ImagingBiCMOS & Photonics1.4μP BSI / 1.1μP BSI Photonics 25Gbps 0.9μP BSI BiCMOS 55nmAdvanced architecture Photonics 40GbpsAgenda17IntroductionTechnology –Embedded Processing Solutions Technology –Sense & Power and Automotive Manufacturing ConclusionBIPOLAR CMOS DMOS 0-100V •90nm (200/300mm)•65nm (300mm)•160nm/110nm •0.35µm•Oxide Filled Trench •Silicon Carbide (SIC)•0.2µm•Oxide Filled Trench Gen2•Gallium Nitride (GaN)•Environmental (Hr,Temp)•Audio (Hperf Micro)•Actuators•Motion (6 axis,AMR,Geophone)•ActuatorsMEMSPowerBIPOLAR CMOS DMOS >100V •320nm OL/160nmSOI •HV Scr Triacs 1500V •GaN Pschottky 600 V •EnFilm Gen1Discrete•HV Scr Triacs 2000V •GaN Pschottky1200V •EnFilm Gen2•HV Scr Triacs 2500V •EnFilm Gen318Prototyping start2014/152016/172013SPA -Technology RoadmapSmart Power: Leading with BCD9SBCD9S• 1.8V CMOS / 5V Analog •8V to 100V •130Kgates/mm2190.11 µm BCDTier-1 automotive customer award for next generation braking systemFull Cu MetallizationThick (10um) Cu Power Metal•Getters •Polymers•Shape Memory Alloy •Piezoelectric (PZT)•SiC & GaN •Graphene•Wafer Level Packaging (Stacked Multi Dice)•New interconnections(Bondless, Sintering, Cu on Cu)•Smart System In Package (SiP)•Moore’s Law: Miniaturization •More than Moore: Functionalities •3D Structure: i.e. MEMS •Through-Silicon ViasAll Technologies for MEMS20New Materials Silicon TechnologiesPackageMOTION MEMSAccelerometers Compass Gyroscopes BrainACOUSTIC MEMSMicrophones LoudspeakersENVIRONMENTAL MEMSPressure Temperature Humidity Chemical InfraredMICRO-ACTUATORSElectrostatic Piezoelectric Thermal++Technology and manufacturing for full spectrum of MEMSSenseMEMS & microphones (LGAs)Optical modules and Imagers towards BSIDigital with advanced CMOS Integration and miniaturization based on BGAs. Towards Flip Chip &WLPPower & BCDHigh dissipation, miniaturized packages (PSSO, QFNs)Packaging Technology R&D21ApplicativeAdvanced28nm CMOS video processor for active safety0.13um BiCMOS RF 24/77GHz Radar for active safety CMOS Video Camerasfor active safety 28nm FD-SOI for the navigation110nm BCD Smart Power forSafety, Engine, BodySOI technology for battery controlPower module for electrificationPMOS, IGBT, VIPowerfor Power ActuatorMastering all Technologies and Manufacturingfor AutomotiveCrolles:CRO300Agrate:AG8/AGM/R240nm e-Flash for 32 bit Microprocessor22Priorities for 2013 -Technology23 BCD9S technology platform to beready for productionPower ASIC for Automotive (ABS/ESP)engineering samples deliverydemonstrating superior device performances and die area reduction FD-SOI 14 nmtechnology to be readyfor prototyping and IPsvalidation vehicles forsuperior performancesand low powerconsumption SoC andASICsEmbedded flash 40nmtechnology for highperformance MCUsReadiness for prototyping andIPs validation vehicles2013Agenda24IntroductionTechnology –Embedded Processing SolutionsTechnology –Sense & Power and AutomotiveManufacturingConclusionManufacturing Model25Front-EndBack-EndMoroccoFrance(Crolles, Rousset, Tours)Italy(Agrate, Catania)MalaysiaSingaporePhilippinesChina (Shenzhen / Longgang)Malta•Manufacturing model unchanged•Independent manufacturing•Supply flexibility provided by foundries•Efficient manufacturing tool at about $2.2B-$2.3B quarter run rate • 6 Front-end sites•20% outsourcing target•6 Back-end plants•30% outsourcing targetManufacturing & Technology R&D CAPEX26•Proven ability to significantly modulate Capex•Essentially driven by decisions to add global capacity on top of technology mix evolution•2013 Capex expected to be approximately $550M-$600M•300mm 14nm FD-SOI capability •300mm Image Sensor BSI capacity •MEMS•Smart-Power mix change•Capacity increase & mix evolution in back-end •Copper wire conversion5001000150020092010201120122013eCapex in US$MFront-End R&D Test&Others Back-EndExpected Capex 2013Internal Manufacturing Advantage27We win business thanks to the full control and flexibility in oursupply chainAutomotive•Customer requirement •Quality & ReliabilityDigital•Fastest prototyping service•Fast ramp to volumeMEMS•Fast ramp to volume •Control of all the partsPrototype shipped13 days in advance of committed schedulewith 0.37 days permask layerFastest Prototyping for Digital ASIC26 July28 July 30 July 01 August 03 August 05 August 07 August 09 August 11 August 13 August 15 August 17 August 19 August 21 August FAB REAL FAB COMMITDiffusion Process Tracking chartDigital ASIC28Priorities 2013 –Manufacturing29 2013300mm Crolles•CMOS FD-SOI 28nmManufacturing ramp-up•Imaging 1.4μP BSI volume productionMEMS•6-Axis combovolume production•μPhone and Compassproduction ramp-upSmart Power and Discrete•BCD mix evolution to0.16um/ thick Cu•IGBT 650/1200Vproduction ramp-upe-NVM and RF/Analog•90nm e-Flash highvolume production•Optimized130nmRF SOI in productionramp-upInnovationTime to VolumeQuality ExcellenceLean ManufacturingProductivityCost reduction。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

9

MEMS的科学

力学 材料学 生物学 物理学 电子学

MEMS

光学

化学

MEMS is a Interdisciplinary Science which involves mechanics, electronics, chemistry, optics, physics, biology, material science etc.

90nm

22nm

memory

65nm

32nm技术

SoC

System on chip

Higher higher value

SiP

System in Package

40

超越摩尔定律

MEMS

41

3D IC技术的类型

42

基本结构

43

TSV(深硅通孔)工艺

44

TSV 3D IC技术的挑战

• 成本

– TSV制造技术的成本较高

• 散热

– 垂直和水平方向的散热通道设计

• 可靠性

– 应力,电迁移,热退化

• 供应链

– 谁来做TSV? – 谁需要TSV?

45

微电子系统的未来

MEMS CMOS Solar Cell

Flexible electronics

All in Si

RF

Bio-Chip

Storage

Memory

46

小结

• MEMS是微电子系统与外界互动的纽带,是 一种微型化和集成化的机械系统。 • 信息系统缩小的最终瓶颈在于MEMS的尺寸. • 三维IC技术可以在第三维度上集成不同的芯 片,从而扩展系统的功能,继续维持摩尔 定律。 • TSV是三维IC技术的关键。 • 全硅集成也许是将来微电子发展的终极形 态。

10

MEMS的好处

• 尺寸小

– 可将系统缩小

• 智能

– 能够将力、热、磁和化学信息转换为电子信号

• 集成

– 可采用微电子工艺集成在芯片上

• 可靠性

– 安全

• 功耗低

– 绿色环保

11

MEMS的分类

• 机械

– 加速度计,陀螺仪,马达,机器人,喷气发动机,泵, 扬声器,环振,阀门,开关

• 热

– 温度、红外成像

微机电系统(MEMS)

----超越摩尔定律(More than moore)

1

• 半导体技术在摩尔定律上似乎走入了瓶颈 期,而超越摩尔定律的新兴技术却受到了 众多公司的青睐,其中以MEMS无处不在的 应用潜力攫取了业界大大小小公司的眼球

2

费曼预言了微机电系统的出现以及它的基本原则。

3

提纲

• • • • 什么是MEMS MEMS的制造技术 几种主要的MEMS器件 三维集成—超越摩尔定律

4

智能系统需要感知世界的信号

水

空气

硬度

情绪

磁场

5

智能系统与真实世界的传感纽带:微机电系统(MEMS)

终极微电子系统

6

什么是微机电系统

• MEMS:

Micro-Electro-Mechanical System

Micro-Machine Micro-System

MEMS Micro-Machine Micro-System

MEMS first

23

MEMS 器件

24

非常重要的几类MEMS器件

• 惯性传感器

– 加速度计 – 陀螺仪 – 压力传感器

• 光学MEMS传感器

– 微光开关 – 微光学台面

• 微执行器

– 微喷管 – 微马达

• 生物MEMS器件

25

电容式加速度计

26

电容式加速度计(放大图)

27

微镜面

28

微光栅

自底向上

20

LIGA 工艺

21

MEMS工艺

• 各向异性腐蚀

• 深槽刻蚀

• 键合

22

未来3D IC的CMOS-MEMS集成技术

• 牺牲层技术

IC first

– – – – – – – 独立的MEMS系统 很高的传感灵敏度 较低的寄生效应 体积小 封装简单 复杂的制造过程 缺少兼容的材料

IC and MEMS mixed

• 化学

– 酸碱传感器,成分传感器,浓度传感器

• 光

– 镜面,光栅,通讯,CCD

• 生物

– 生命探测器,机器人,智能注射器,DNA芯片

12

世界第一支静电加速度计

ADI制造

13

固态硅微卫星

14

微马达

15

MEMS的挑战

Surface tension

MEMS

微观世界中物理法则

16

MEMS的挑战

深谷

微型喷嘴

组成: 由5到6片芯片叠在 一起,内有混合燃烧室、喷 口喷管、两个泵和两个阀以 及冷却管道的多器件集成系 统。用液态氧和乙醇作燃料 性能:能产生15N的推力, 推力重量比达 1500:1,是 大火箭推进器的10~100倍, 反映了微系统的潜力

新概念的微型双组元火箭发动机结构图

37

3D IC – 超越摩尔定律

35

微型喷嘴

美国喷气推进实验室 (JPL)展示的采用 MEMS技术的电阻电热式 微推进器样机(固体升华方式)。微推进器由推进剂存贮箱、微 阀、微过滤器、微型喷口等组成,微型喷口利用MEMS技术中的 体硅工艺制作。其性能目标为:比冲50~75s,推力0.5mN,功 率 <2W/mN,质量为几克,大小为1cm2。 36

47

29

微透镜

30

微型光学台面

31

微光开光

1x4 optical switch

1x8 optical switch

32

便携式化学传感器

33

微马达

34

微型喷嘴

美国喷气推进实验室 (JPL) 展示的采用 MEMS 技术的电阻电热式微推 进器样机(液体气化方 式)。微推进器由薄膜 加热器、微型喷口等组 成。其性能目标为:比 冲 75 ~ 125s , 推 力 0.5mN ,功率 <5W ,效 率≥50% ,质量为几克, 大小为1cm2。

7

为什么需要MEMS

• 信息系统不断追求小型化

– 体积缩小 – 性能和可靠性提高 – 功耗和成本降低

• 系统缩小的主要途径

– 遵循摩尔定律的IC缩小技术

– MEMS用来缩小非IC的部分

8

什么是MEMS?

• MEMS > IC

– 集成了微传感器,微执行器,信号处理器,控 制器,输入输出电路,通讯系统以及电源的系 统

高深宽比刻蚀

微加工

17

MEMS的挑战

sensor Integrated System

Controller

Execution

系统设计和集成

18

型机械制造微机械 (日本) 微电子半导体加工工艺 紫外光刻微电铸模制 造技术(德国)

微机械

LIGA

MEMS

怎样将MEMS和其他非电子系统以及复 杂电子系统在一个三维的芯片中集成?

38

二维平面上的摩尔定律

Higher value

RF

X node

0.7X node

logic

analog memory

Scaling down

SoC ?

39

三维空间上的摩尔定律

MEMS

RF logic

analog memory