lvds接口标准

LVDS屏接口定义解析

常见LVDS 屏接口定义讲解很多初学者对于如何区分屏的接口类型很是头疼,是LVDS 屏,TTL 屏还是RS DS 屏?总是很难搞清出。

如何快速识别出液晶屏的接口类型则需要一些经历的,下面从屏的屏线接口的样式来对接口类型做出分类的介绍,帮助大家快速识别屏的接口类型。

以下方法是个人认识,缺乏之处请大家谅解。

〔1〕TTL 屏接口样式:D6T 〔单6位TTL 〕:31扣针,41扣针。

对应屏的尺寸主要为笔记本液晶屏〔8寸,10寸,11寸,12寸〕,还有局部台式机屏15寸为41扣针接口。

S6T 〔双6位TTL 〕:30+45针软排线,60扣针,70扣针,80扣针。

主要为台式机的14寸,15寸液晶屏。

D8T 〔单8位TTL 〕:很少见S8T 〔双8位TTL 〕:有,很少见80扣针〔14寸,15寸〕 〔2〕LVDS 屏接口样式:D6L 〔单6位LVDS 〕:14插针,20插针,14片插,30片插〔屏显基板100欧姆电阻的数量为4个〕主要为笔记本液晶屏〔12寸,13寸,14寸,15寸〕 D8L 〔单8位LVDS 〕:20插针〔5个100欧姆〕〔15寸〕S6L 〔双6位LVDS 〕:20插针,30插针,30片插〔8个100欧姆〕〔14寸,15寸,17寸〕S8L 〔双8位LVDS 〕:30插针,30片插〔10个100欧姆电阻〕〔17寸,18寸,19寸,20寸,21寸〕 〔3〕RSDS 屏接口样式:50排线,双40排线,30+50排线。

主要为台式机〔15寸,17寸〕液晶屏。

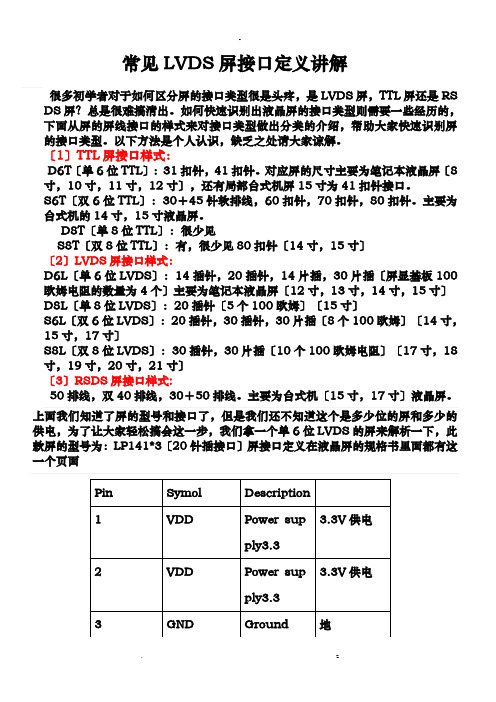

上面我们知道了屏的型号和接口了,但是我们还不知道这个是多少位的屏和多少的供电,为了让大家轻松搞会这一步,我们拿一个单6位LVDS 的屏来解析一下,此款屏的型号为:LP141*3〔20针插接口〕屏接口定义在液晶屏的规格书里面都有这一个页面在屏的接口定义中我们看出液晶屏的供电为3.3这里面出现了两组数据每组中都有一对时钟信号,这个屏我们就能看出这是一个30针双8位屏,屏的供电为5V。

常见液晶屏LVDS接口定义

常见液晶屏LVDS接口定义20PIN单6定义:1:电源2:电源3:地 4:地 5:R0- 6:R0+ 7:地 8:R1- 9:R1+ 10:地 11:R2- 12:R2+ 13:地 14:CLK- 15:CLK+ 16空17空 18空 19 空 20空每组信号线之间电阻为(数字表120欧左右)20PIN双6定义:1:电源2:电源3:地4:地5:R0- 6:R0+ 7:R1- 8:R1+ 9:R2- 10:R2+ 11:CLK- 12:CLK+ 13:RO1- 14:RO1+ 15:RO2- 16:RO2+ 17:RO3- 18:RO3+19:CLK1- 20:CLK1+每组信号线之间电阻为(数字表120欧左右)20PIN单8定义:1:电源2:电源3:地 4:地 5:R0- 6:R0+ 7:地 8:R1- 9:R1+ 10:地11:R2- 12:R2+ 13:地14:CLK- 15:CLK+ 16:R3- 17:R3+每组信号线之间电阻为(数字表120欧左右)30PIN单6定义:1:空2:电源3:电源4:空5:空6:空7:空8:R0- 9:R0+ 10:地 11:R1- 12:R1+ 13:地 14:R2- 15:R2+ 16:地 17:CLK- 18:CLK+ 19:地 20:空- 21:空 22:空 23:空 24:空 25:空 26:空 27:空 28空 29空 30空每组信号线之间电阻为(数字表120欧左右)30PIN单8定义:1:空2:电源3:电源4:空5:空6:空7:空8:R0- 9:R0+ 10:地 11:R1- 12:R1+ 13:地 14:R2- 15:R2+ 16:地 17:CLK- 18:CLK+ 19:地20:R3- 21:R3+ 22:地23:空24:空25:空 26:空 27:空 28空 29空 30空每组信号线之间电阻为(数字表120欧左右)30PIN双6定义:1:电源2:电源3:地 4:地 5:R0- 6:R0+ 7:地 8:R1- 9:R1+ 10:地 11:R2- 12:R2+ 13:地 14:CLK- 15:CLK+ 16:地 17:RS0- 18:RS0+ 19:地 20:RS1- 21:RS1+ 22:地 23:RS2- 24:RS2+ 25:地 26:CLK2- 27:CLK2+ 每组信号线之间电阻为(数字表120欧左右)30PIN双8定义:1:电源2:电源3:电源 4:空 5:空 6:空 7:地 8:R0- 9:R0+ 10:R1- 11:R1+ 12:R2- 13:R2+ 14:地15:CLK- 16:CLK+ 17:地 18:R3- 19:R3+ 20:RB0-21:RB0+ 22:RB1- 23:RB1+ 24:地25:RB2- 26:RB2+ 27:CLK2- 28:CLK2+ 29:RB3- 30:RB3+每组信号线之间电阻为(数字表120欧左右)一般14PIN、20PIN、30PIN为LVDS接口。

LVDS标准及介绍-(2)

LVDS1.0 LVDS简介LVDS(Low Voltage Differential Signaling)是一种低摆幅的差分信号技术,它使得信号能在差分PCB线对或平衡电缆上以几百Mbps的速率传输,其低压幅和低电流驱动输出实现了低噪声和低功耗.1.1 LVDS信号传输组成LVDS信号传输一般由三部分组成,如图1所示:差分信号发送器,差分信号互联器,差分信号接收器.图1 简单的单工LVDS接口连接图差分信号发送器:将非平衡传输的TTL信号转换成平衡传输的LVDS信号.通常由一个IC来完成.差分信号接收器:将平衡传输的LVDS信号转换成非平衡传输的TTL信号。

通常由一个IC来完成.差分信号互联器:包括联接线(电缆或者PCB走线),终端匹配电阻。

1.2 LVDS的工作原理图2 LVDS接口电路图如图2所示,LVDS驱动器由一个驱动差分线对的电流源组成(通常电流为3。

5mA),LVDS 接收器具有很高输入阻抗,因此驱动器输出的电流大部分都流过100Ω的匹配电阻,并在接收器的输入端产生生大约350mV的电压。

驱动器的输入为两个相反的电平信号,四个nMOS管的尺寸工艺是完全相同的.当输入为“1”时,标号IN+的一对管子导通,另一对管子截止,电流方向如图2,并产生大约350mV的压降;反之,输入为“0”时,电流反向,产生大约350mV的压降.这样根据流经电阻的电流方向,就把要传输的数字信号(CMOS信号)转换成了电流信号(LVDS信号)。

接受端可以通过判断电流的方向就得到有效的逻辑“1”和逻辑“0"状态。

从而实现数字信号的传输过程。

由于MOS管的开关速度很高,并且LVDS的电压摆幅低(350mV),因此可以实现高速传输.其电平特性如下图所示1.3 LVDS的国际标准LVDS是目前高速数字信号传输的国际通用接口标准,国际上有两个工业标准定义了LVDS:ANSI/TIA/EIA(American National Standards Institute/Telecommunications Industry Association/Electronic Industries Association)和IEEE(Institute for Electrical and Electronics Engineering)。

LVDS接口设计

LVDS接⼝设计1 LVDS概述LVDS(Low Voltage Differential Signaling)是⼀种⼩振幅差分信号技术,它使⽤⾮常低的幅度信号(100Mv~450mV)通过⼀对平⾏的PCB⾛线或平衡电缆传输数据。

在两条平⾏的差分信号线上流经的电流及电压振幅相反,噪声信号同时耦合到两条线上,⽽接受端只关⼼两信号的差值,于是噪声被抵消。

由于两条信号线周围的电磁场也相互抵消,故差分信号传输⽐单线信号传输电磁辐射⼩得多。

此外,该传输标准采⽤电流模式驱动输出,不会产⽣振铃和信号切换所带来的尖峰信号,具有良好的EMI特性。

由于LVDS差分信号技术降低了对噪声的关注,所以可以采⽤较低的信号电压幅度。

这个特性⾮常重要,它使提⾼数据传输率和降低功耗成为可能。

低驱动振幅意味着数据可更块地反转。

由于驱动器是恒流源模式,功耗⼏乎不会随频率⽽变化,⽽且单路的功耗⾮常低(LVDS25标准2mAx250mV=0.5mW)。

因此,采⽤这种技术后,只要保证⼀对平⾏传输线的长度⾜够⼀致,并在接受端提供良好的匹配端接阻抗技术,以减⼩反射信号的产⽣,就可以提供⾮常⾼的数据传输率。

⽬前,不⽤经⾏复杂和特殊的处理,提供840MHz的数据传输速率已经⾮常容易。

由于LVDS具有这些优良的特性,使得其应⽤越来越普及。

特别是在器件与器件之间以及器件与板级之间的⾼速串⾏数据通信中,已作为⾸选的标准。

⽬前,Xilinx FPGA的每个输⼊输出引脚都⽀持这种信号标准。

2 LVDS的使⽤LVDS的发送和接受通常为点到点结构,如下图所⽰:在芯⽚与芯⽚之间交换数据时,传统的应⽤是采⽤TTL,LVCMOS等单端接⼝标准,这种通信⽅式不仅易受⼲扰,⽽且数据传输率⽆法提⾼。

如果要提⾼带宽(数据传输速率),必须提供⾜够的数据通道。

这样,不仅提⾼了系统成本,⽽且需要处理复杂和棘⼿的数据同步问题。

然⽽,如果采⽤LVDS标准,可有效地解决这些问题。

实现的⽅法是,利⽤可编程逻辑器件的特性,将寄存器的数据输出经过串化处理,并由LVDS接⼝输出,在接受端再将数据利⽤解串流程恢复,如下图所⽰:采⽤上述⽅法处理后,将原有的32条数据线变成了4对差分输出线,并可达到或超过单端输出的带宽,且更容易实现,功率更低。

LVDS常规接口定义

常规LVDS接口液晶屏定义20PIN单6定义:1:电源2:电源3:地 4:地 5:R0- 6:R0+ 7:地 8:R1- 9:R1+ 10:地 11:R2- 12:R2+ 13:地 14:CLK- 15:CLK+ 16空 17空 18空 19 空 20空每组信号线之间电阻为(数字表120欧左右)20PIN双6定义:1:电源2:电源3:地 4:地 5:R0- 6:R0+ 7:R1- 8:R1+ 9:R2- 10:R2+ 11:CLK- 12:CLK+ 13:RO1- 14:RO1+ 15:RO2- 16:RO2+ 17:RO3- 18:RO3+ 19:CLK1- 20:CLK1+每组信号线之间电阻为(数字表120欧左右)20PIN单8定义:1:电源2:电源3:地 4:地 5:R0- 6:R0+ 7:地 8:R1- 9:R1+ 10:地 11:R2- 12:R2+ 13:地 14:CLK- 15:CLK+ 16:R3- 17:R3+每组信号线之间电阻为(数字表120欧左右)30PIN单6定义:1:空2:电源3:电源 4:空 5:空 6:空 7:空 8:R0- 9:R0+ 10:地 11:R1- 12:R1+ 13:地 14:R2- 15:R2+ 16:地 17:CLK- 18:CLK+ 19:地 20:空- 21:空 22:空 23:空 24:空 25:空 26:空 27:空 28空 29空 30空每组信号线之间电阻为(数字表120欧左右)30PIN单8定义:1:空2:电源3:电源 4:空 5:空 6:空 7:空 8:R0- 9:R0+ 10:地 11:R1- 12:R1+ 13:地 14:R2- 15:R2+ 16:地 17:CLK- 18:CLK+ 19:地 20:R3- 21:R3+ 22:地 23:空 24:空 25:空 26:空 27:空 28空 29空 30空每组信号线之间电阻为(数字表120欧左右)30PIN双6定义:1:电源2:电源3:地 4:地 5:R0- 6:R0+ 7:地 8:R1- 9:R1+ 10:地 11:R2- 12:R2+ 13:地 14:CLK- 15:CLK+ 16:地 17:RS0- 18:RS0+ 19:地 20:RS1- 21:RS1+ 22:地 23:RS2- 24:RS2+ 25:地 26:CLK2- 27:CLK2+每组信号线之间电阻为(数字表120欧左右)30PIN双8定义:1:电源2:电源3:电源 4:空 5:空 6:空 7:地 8:R0- 9:R0+ 10:R1- 11:R1+ 12:R2- 13:R2+ 14:地 15:CLK- 16:CLK+ 17:地 18:R3- 19:R3+ 20:RB0-21:RB0+ 22:RB1- 23:RB1+ 24:地 25:RB2- 26:RB2+ 27:CLK2- 28:CLK2+ 29:RB3- 30:RB3+每组信号线之间电阻为(数字表120欧左右)一般14PIN、20PIN、30PIN为LVDS接口。

(完整版)LVDS接口详解

1.LVDS输出接口概述液晶显示器驱动板输出的数字信号中,除了包括RGB数据信号外,还包括行同步、场同步、像素时钟等信号,其中像素时钟信号的最高频率可超过28MHz。

采用TTL接口,数据传输速率不高,传输距离较短,且抗电磁干扰(EMI)能力也比较差,会对RGB数据造成一定的影响;另外,TTL 多路数据信号采用排线的方式来传送,整个排线数量达几十路,不但连接不便,而且不适合超薄化的趋势。

采用LVDS输出接口传输数据,可以使这些问题迎刃而解,实现数据的高速率、低噪声、远距离、高准确度的传输。

那么,什么是LVDS输出接口呢?LVDS,即Low Voltage Differential Signaling,是一种低压差分信号技术接口。

它是美国NS公司(美国国家半导体公司)为克服以TTL电平方式传输宽带高码率数据时功耗大、EMI电磁干扰大等缺点而研制的一种数字视频信号传输方式。

LVDS输出接口利用非常低的电压摆幅(约350mV)在两条PCB走线或一对平衡电缆上通过差分进行数据的传输,即低压差分信号传输。

采用LVDS输出接口,可以使得信号在差分PCB线或平衡电缆上以几百Mbit/s的速率传输,由于采用低压和低电流驱动方式,因此,实现了低噪声和低功耗。

目前,LVDS输出接口在17in及以上液晶显示器中得到了广泛的应用。

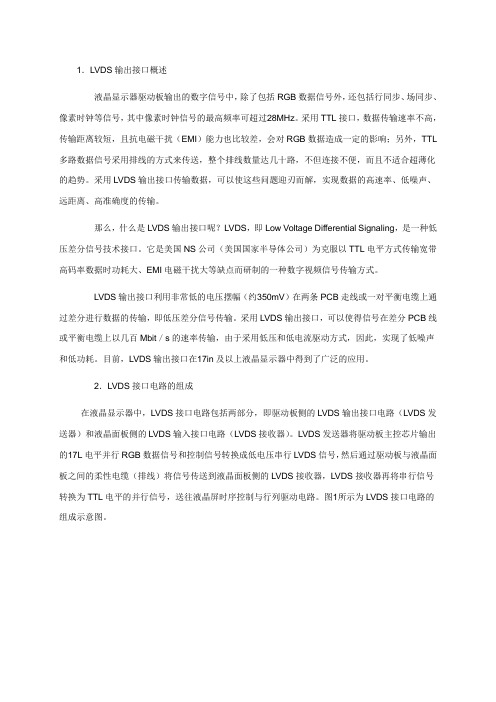

2.LVDS接口电路的组成在液晶显示器中,LVDS接口电路包括两部分,即驱动板侧的LVDS输出接口电路(LVDS发送器)和液晶面板侧的LVDS输入接口电路(LVDS接收器)。

LVDS发送器将驱动板主控芯片输出的17L电平并行RGB数据信号和控制信号转换成低电压串行LVDS信号,然后通过驱动板与液晶面板之间的柔性电缆(排线)将信号传送到液晶面板侧的LVDS接收器,LVDS接收器再将串行信号转换为TTL电平的并行信号,送往液晶屏时序控制与行列驱动电路。

图1所示为LVDS接口电路的组成示意图。

图1 LVDS接口电路的组成示意图在数据传输过程中,还必须有时钟信号的参与,LVDS接口无论传输数据还是传输时钟,都采用差分信号对的形式进行传输。

LVDS接口标准

LVDS接口标准:LVDS接口是LCD Panel通用的接口标准,以8-bit Panel为例,包括5组传输线,其中4组是数据线,代表Tx0+/Tx0-... Tx3+/Tx3-。

还有一组是时钟信号,代表TxC+/TxC-。

相应的在Panel一端有5组接收线。

如果是6-bit Panel则只有3组数据线和一组时钟线。

LVDS接口又称RS-644总线接口,是20世纪90年代才出现的一种数据传输和接口技术。

LVDS即低电压差分信号,这种技术的核心是采用极低的电压摆幅高速差动传输数据,可以实现点对点或一点对多点的连接,具有低功耗、低误码率、低串扰和低辐射等特点,其传输介质可以是铜质的PCB连线,也可以是平衡电缆。

LVDS在对信号完整性、低抖动及共模特性要求较高的系统中得到了越来越广泛的应用。

目前,流行的LVDS技术规范有两个标准:一个是TIA/EIA(电讯工业联盟/电子工业联盟)的ANSI/TIA/EIA-644标准,另一个是IEEE 1596.3标准。

1995年11月,以美国国家半导体公司为主推出了ANSI/TIA/EIA-644标准。

1996年3月,IEEE公布了IEEE 1596.3标准。

这两个标准注重于对LVDS接口的电特性、互连与线路端接等方面的规范,对于生产工艺、传输介质和供电电压等则没有明确。

LVDS可采用CMOS、GaAs或其他技术实现,其供电电压可以从+5V到+3.3V,甚至更低;其传输介质可以是PCB 连线,也可以是特制的电缆。

标准推荐的最高数据传输速率是655Mbps,而理论上,在一个无衰耗的传输线上,LVDS的最高传输速率可达1.923Gbps。

---- OpenLDI标准在笔记本电脑中得到了广泛的应用,绝大多数笔记本电脑的LCD显示屏与主机板之间的连接接口都采用了OpenLDI标准。

OpenLDI接口标准的基础是低压差分信号(Low Voltage Differential Signaling,LVDS)接口,它具有高效率、低功耗、高速、低成本、低杂波干扰、可支持较高分辨率等特点。

LVDS接口定义及标准

LVD LVD 低電對多線,廣泛盟)199公佈範,現,纜。

高傳LVD 成,很高mV 在有的M 理很輸入1)S 接口定義DS 接口又稱電壓差分信多點的連接,也可以是平泛的應用。

)的ANSI/T 95年11月佈了IEEE ,對於生產工,其供電電。

標準推薦傳輸速率可DS 接口的原一個簡單,如圖1所高,驅動器電V 。

通過驅有些最新生MAX9121/9在LVDS 很簡單,因為入端產生的來傳送信號表1是LV 表2是接義及標準稱RS-644信號,這種技接,具有低功平衡電纜。

目前,流行TIA/EIA -6,以美國國1596.3標準工藝、傳輸電壓可以從+薦的最高數據可達1.923G 原理及電特單的LVDS 傳所示。

驅動器電流大部分驅動器的開關生產的LVDS 9122等。

系統中,採為一對差分效果是相互號,從而可VDS 驅動器接收器的主要4總線接口技術的核心是功耗、低誤。

LVDS 在對行的LVDS 技644標準,國家半導體準。

這兩個輸介質和供電+5V 到+3.3據傳輸速率Gbps 。

特性傳輸系統由器的電流源分直接流過關,改變直S 接收器中採用差分方分線對上的電互抵消的,可以大大提高器的主要電要電特性參,是20世紀是採用極低誤碼率、低串對信號完整技術規範有另一個是體公司為主推個標準注重於電電壓等則3V ,甚至更率是655Mbp 一個驅動器源(通常為3100Ω的終直接流過電阻中,100Ω左方式傳送數據電流方向是因而對信號高數據傳輸電特性參數參數。

紀90年代低的電壓擺幅串擾和低輻整性、低抖動有兩個標準IEEE 159推出了ANS 於對LVDS 則沒有明確更低;其傳輸ps ,而理論器和一個接3.5mA )來終端電阻,從阻的電流的左右的電阻直據,有著比是相反的,當號的影響很輸速率和降低才出現的一幅高速差動輻射等特點動及共模特:一個是T 96.3標準。

SI/TIA/EIA S 接口的電。

LVDS 可輸介質可以論上,在一收器通過一來驅動差分線從而在接收的有無,從而直接集成在比單端傳輸方當共模方式很小。

LVDS视频传输数据接口

LVDS视频传输数据接口LVDS(Low Voltage Differential Signaling)即低压差分信号传输,是一种满足当今高性能数据传输应用的新型技术。

由于其可使系统供电电压低至 2V,因此它还能满足未来应用的需要。

此技术基于ANSI/TIA/EIA-644 LVDS 接口标准。

LVDS 技术拥有 330mV 的低压差分信号 (250mV MIN and 450mV MAX) 和快速过渡时间。

这可以让产品达到自 100 Mbps 至超过 1 Gbps 的高数据速率。

此外,这种低压摆幅可以降低功耗消散,同时具备差分传输的优点。

由多个数据位和时钟组成的源同步接口已成为电子系统中移动图像数据的一种常用方法。

比较流行的标准是7:1LVDS接口(用于通道链路、平面链路和摄像机链路),它已经成为许多电子产品的通用标准,包括消费设备、工业控制、医疗和汽车远程信息处理。

在这些应用中,使用低成本FPGA进行图像处理的做法已经变得相当普遍。

7:1 LVDS接口是一个源同步LVDS接口。

如图1所示,为低速时钟的每个周期序列化7个数据位。

通常,接口由四个(三个数据,一个时钟)或五个(四个数据,一个时钟)LVDS差分对组成。

四对转换为21个并行数据位,五对转换为28个并行数据位。

注意,在时钟上升沿和字边界之间有一个2位偏移。

每个字节有7位长。

图1 7:1LVDS接口每个通道包括一个串行LVDS数据对和一个源同步LVDS时钟对。

接收方接收到该串行LVDS数据,对其进行反序列化,并将其对齐到原始单词边界,生成7个并行LVTTL数据位。

7:1发送器将7个LVTTL 并行数据位串行化为一个LVDS数据位,并将该串行数据通道与LVDS时钟一起传输。

图2显示7:1接收方接收4个LVDS数据通道。

当反序列化时,它生成28位宽的并行数据。

类似地,7:1发送器序列化28位并行数据,生成4个LVDS数据通道。

图2 7:1接收方与发送方基于FPGA的通道链接和平面链接样式接口的需求包括四个关键组件:高速LVDS缓冲区、用于生成反序列化时钟的锁相环、输入数据捕获和传动装置以及数据格式化。

lvds液晶屏幕接口详解

1.LVDS输出接口概述液晶显示器驱动板输出的数字信号中,除了包括RGB数据信号外,还包括行同步、场同步、像素时钟等信号,其中像素时钟信号的最高频率可超过28MHz。

采用TTL接口,数据传输速率不高,传输距离较短,且抗电磁干扰(EMI)能力也比较差,会对RGB数据造成一定的影响;另外,TTL 多路数据信号采用排线的方式来传送,整个排线数量达几十路,不但连接不便,而且不适合超薄化的趋势。

采用LVDS输出接口传输数据,可以使这些问题迎刃而解,实现数据的高速率、低噪声、远距离、高准确度的传输。

那么,什么是LVDS输出接口呢?LVDS,即Low Voltage Differential Signaling,是一种低压差分信号技术接口。

它是美国NS公司(美国国家半导体公司)为克服以TTL电平方式传输宽带高码率数据时功耗大、EMI电磁干扰大等缺点而研制的一种数字视频信号传输方式。

LVDS输出接口利用非常低的电压摆幅(约350mV)在两条PCB走线或一对平衡电缆上通过差分进行数据的传输,即低压差分信号传输。

采用LVDS输出接口,可以使得信号在差分PCB线或平衡电缆上以几百Mbit/s的速率传输,由于采用低压和低电流驱动方式,因此,实现了低噪声和低功耗。

目前,LVDS输出接口在17in及以上液晶显示器中得到了广泛的应用。

2.LVDS接口电路的组成在液晶显示器中,LVDS接口电路包括两部分,即驱动板侧的LVDS输出接口电路(LVDS发送器)和液晶面板侧的LVDS输入接口电路(LVDS接收器)。

LVDS发送器将驱动板主控芯片输出的17L电平并行RGB数据信号和控制信号转换成低电压串行LVDS信号,然后通过驱动板与液晶面板之间的柔性电缆(排线)将信号传送到液晶面板侧的LVDS接收器,LVDS接收器再将串行信号转换为TTL电平的并行信号,送往液晶屏时序控制与行列驱动电路。

图1所示为LVDS接口电路的组成示意图。

图1 LVDS接口电路的组成示意图在数据传输过程中,还必须有时钟信号的参与,LVDS接口无论传输数据还是传输时钟,都采用差分信号对的形式进行传输。

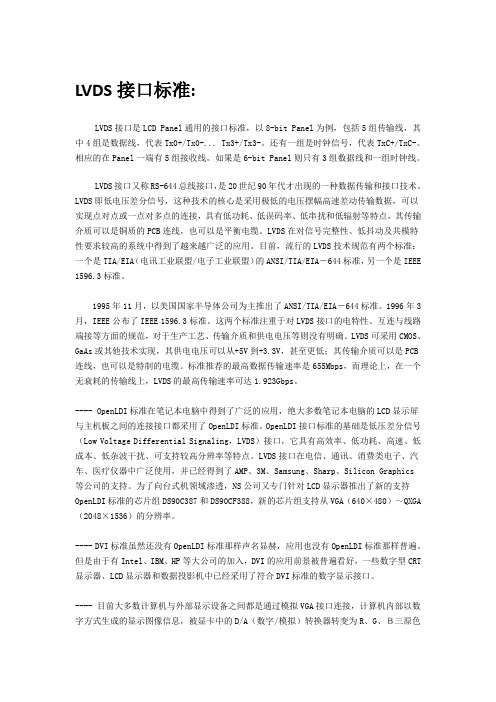

LVDS VS Mini-LVDS

LVDS驱动器 的主要电特性参数

接收器 的主要电特性参数

Mini-LVDS

► ► ► ► ►

雙邊緣Clock觸發; 4 組串行信號線; 1 組 Clock; Termination Resistor = 100 Ω DC 參數

偏壓 1.2 V 擺幅 200 mV 電流 4 mA

►

AC 參數

LVDS接口又称RS-644总线接口,是20世纪90年代 才出现的一种数据传输和接口技术。LVDS即低电压差 分信号,这种技术的核心是采用极低的电压摆幅高速 差动传输数据,可以实现点对点或一点对多点的连接, 具有低功耗、低误码率、低串扰和低辐射等特点,其 传输介质可以是铜质的PCB连线,也可以是平衡电缆。 LVDS在对信号完整性、低抖动及共模特性要求较高的 系统中得到了越来越广泛的应用。

D05 D15 D04 D14 D03 D13 D23 D11 D02 D12 D22 D10 DEN B01 G00 HS B00 R05 VS G05 R04 B05 G04 R03 B04 G03 R02 B03 G02 R01 B02 G01 R00

D25

D01 D21

D24

D00 D20

6 bit 數據 & 控制信號

Mini LVDS Data Clock Control Signal

10 (5 pairs)

LVDS

8 (4 pairs)

2 (1 pair)

2 (1 pair)

2 CD control

NO

Total

14

10

Fmax = 146 MHz (Input Clock = 73 MHz). 需要 PLL

lvds液晶屏幕接口详解51276

1.LVDS输出接口概述液晶显示器驱动板输出的数字信号中,除了包括RGB数据信号外,还包括行同步、场同步、像素时钟等信号,其中像素时钟信号的最高频率可超过28MHz。

采用TTL接口,数据传输速率不高,传输距离较短,且抗电磁干扰(EMI)能力也比较差,会对RGB数据造成一定的影响;另外,TTL 多路数据信号采用排线的方式来传送,整个排线数量达几十路,不但连接不便,而且不适合超薄化的趋势。

采用LVDS输出接口传输数据,可以使这些问题迎刃而解,实现数据的高速率、低噪声、远距离、高准确度的传输。

那么,什么是LVDS输出接口呢?LVDS,即Low Voltage Differential Signaling,是一种低压差分信号技术接口。

它是美国NS公司(美国国家半导体公司)为克服以TTL电平方式传输宽带高码率数据时功耗大、EMI电磁干扰大等缺点而研制的一种数字视频信号传输方式。

LVDS输出接口利用非常低的电压摆幅(约350mV)在两条PCB走线或一对平衡电缆上通过差分进行数据的传输,即低压差分信号传输。

采用LVDS输出接口,可以使得信号在差分PCB线或平衡电缆上以几百Mbit/s的速率传输,由于采用低压和低电流驱动方式,因此,实现了低噪声和低功耗。

目前,LVDS输出接口在17in及以上液晶显示器中得到了广泛的应用。

2.LVDS接口电路的组成在液晶显示器中,LVDS接口电路包括两部分,即驱动板侧的LVDS输出接口电路(LVDS发送器)和液晶面板侧的LVDS输入接口电路(LVDS接收器)。

LVDS发送器将驱动板主控芯片输出的17L电平并行RGB数据信号和控制信号转换成低电压串行LVDS信号,然后通过驱动板与液晶面板之间的柔性电缆(排线)将信号传送到液晶面板侧的LVDS接收器,LVDS接收器再将串行信号转换为TTL电平的并行信号,送往液晶屏时序控制与行列驱动电路。

图1所示为LVDS接口电路的组成示意图。

图1 LVDS接口电路的组成示意图在数据传输过程中,还必须有时钟信号的参与,LVDS接口无论传输数据还是传输时钟,都采用差分信号对的形式进行传输。

lvds线束的标准和要求

lvds线束的标准和要求LVDS(低电压差分信号)线束是一种用于高速数据传输的电气接口标准。

LVDS线束通常用于连接显示器、摄像头、传感器等设备,以实现高速数据传输和抗干扰能力。

LVDS线束的标准和要求涉及到多个方面,我将从以下几个方面进行详细解释:1. 标准,LVDS线束的标准主要包括电气特性、传输速率、连接器类型等方面。

电气特性方面,LVDS线束通常要求工作电压低(一般为 3.3V)、差分信号传输、高抗干扰能力等。

传输速率方面,LVDS线束通常支持高达数百兆至数千兆的数据传输速率,以满足高速数据传输的需求。

连接器类型方面,LVDS线束通常采用特定的连接器标准,如Molex、JST等,以确保连接的稳定性和可靠性。

2. 要求,LVDS线束在设计和制造过程中需要满足一系列要求,包括信号完整性、传输距离、EMI(电磁干扰)等方面的要求。

信号完整性要求线束在高速传输过程中保持信号的稳定性和准确性,避免信号失真和抖动。

传输距离要求线束能够在一定距离内保持数据传输的可靠性和稳定性。

EMI要求线束在传输过程中能够有效抑制电磁干扰,确保数据传输的稳定性和可靠性。

3. 制造和测试,在制造LVDS线束时,需要严格控制线束的布线、绝缘、屏蔽等工艺要求,以确保线束的质量和可靠性。

同时,对于制造出的线束需要进行严格的测试,包括传输速率测试、信号完整性测试、抗干扰能力测试等,以确保线束符合设计要求和标准。

总的来说,LVDS线束的标准和要求涉及到多个方面,包括电气特性、连接器类型、制造工艺、测试要求等,这些方面都对线束的质量和性能起着重要作用。

制造和应用LVDS线束时,需要严格遵循相关标准和要求,以确保线束的可靠性和稳定性。

LVDS线的设计规范

LVDS线的设计规范

为规范LVDS线的设计,保证其性价比达到最佳。

另一方面,统一各供应商的生产工艺,保证产品的一致性,以满足设计要求。

设计规范如下:

1、LVDS线采用散线制作。

2、连接到数字板上插座的端子采用镀锡的。

3、连接到显示屏上插座的端子采用镀金的。

4、采用双绞线,而且特性阻抗控制在100 OH M±10%。

影响阻抗的因素主要

是双绞的绞距。

具体绞距多少根据仪器测量后决定。

认可规格书要体现阻

抗的大小。

5、线材:UL15711 28AWG,为提高颜色识辨性,电源PIN采用红色,地PIN

采用黑色,其他功能PIN的颜色没有要求。

(每对差分对线的颜色也可以

不同)

6、屏蔽编织网线的要求:直径0.12mm,168根.

7、长度标准化:长度的选择主要考虑安装工艺和EMC的要求。

取值:200,

250,300,350,400,450,500,550,600等50一个步进,容易记忆。

8、LVDS线外包的绝缘体用热缩套管。

9、LVDS线上的金属接地夹子材料使用不锈钢,而且与线体良好接触。

(铝

容易氧化)

10、工艺要注意:屏蔽编织网线离插座的距离越短越好,要求少于15mm;同

样,双绞线一直绞到插座端;各线之间不能相互交叉,缠在一起。

包扎后

线体不能出现有拉紧状态。

(插座两边连接线的长度可比中间梢长一点)以上是基本要求,其他的要求以各图纸要求为准!

按以上要求做出的LVDS线大概如下:用散线做出来的双绞线外套上屏蔽编织线,在屏蔽编织线再套热缩套管。

教你区分LVDS屏线及屏接口定义:

教你区分LVDS屏线及屏接口定义:教你区分LVDS屏线及屏接口定义:现在碰到液晶屏大多是LVDS屏线,经常碰到什么单6,双6 单8双8.如何区分呢? 我以前也不知道,后在网上收集学习后才弄明白。

方法1数带“ -”的这种信号线一共有几对,有10对的减2对就是双8,有8对的减2对就是双6。

有5对的减掉1对是单8,有4对的减掉1对是单6,数 /-线一共有多少对。

说通俗点就是4对————单6 5对————单8 8对————双6 10对————双8方法2 拧开螺丝看看主板里面的电路,一般每对数据线之间都有一个100欧姆的电阻,看到4个的话就是单6位的屏,看到8个的话就是双六位,5个的话一般是单8位,有10个一般就是双8位,当然有资料的话就不用这么麻烦,也有TMDS也用这种20PIN的连接头的,比如LG的LP141X1,不过基本上很少lvds的接口的定义 20PIN单6定义:1:电源2:电源3:地 4:地 5:R0- 6:R0 7:地 8:R1- 9:R1 10:地 11:R2- 12:R2 13:地 14:CLK- 15:CLK 16空 17空18空19 空20空每组信号线之间电阻为(数字表120欧左右),20PIN双6定义 1:电源2:电源3:地4:地5:R0- 6:R0 7:R1- 8:R1 9:R2- 10:R2 11:CLK- 12:CLK 13:RO1- 14:RO1 15:RO2- 16:RO2 17:RO3- 18:RO3 ; 19:CLK1- 20:CLK1每组信号线之间电阻为(数字表120欧左右)20PIN单8定义:1:电源2:电源3:地 4:地 5:R0- 6:R0 7:地 8:R1- 9:R1 10:地 11:R2- 12:R2 13:地 14:CLK- 15:CLK 16:R3- 17:R3每组信号线之间电阻为(数字表120欧左右)30PIN单6定义:1:空2:电源3:电源 4:空 5:空 6:空 7:空 8:R0- 9:R0 10:地 11:R1- 12:R1 13:地 14:R2- 15:R2 16:地 17:CLK- 18:CLK 19:地 20:空- 21:空 22:空 23:空 24:空 25:空 26:空 27:空 28空 29空 30空每组信号线之间电阻为(数字表120欧左右)30PIN单8定义:1:空2:电源3:电源 4:空 5:空 6:空 7:空 8:R0- 9:R0 10:地 11:R1- 12:R1 13:地 14:R2- 15:R2 16:地 17:CLK- 18:CLK 19:地 20:R3- 21:R3 22:地 23:空 24:空 25:空 26:空 27:空 28空 29空 30空每组信号线之间电阻为(数字表120欧左右)30PIN双6定义:1:电源2:电源3:地 4:地 5:R0- 6:R0 7:地 8:R1- 9:R1 10:地 11:R2- 12:R2 13:地 14:CLK- 15:CLK 16:地 17:RS0- 18:RS0 19:地20:RS1- 21:RS1 22:地23:RS2- 24:RS2 25:地 26:CLK2- 27:CLK2每组信号线之间电阻为(数字表120欧左右)30PIN双8定义:1:电源2:电源3:电源 4:空 5:空 6:空 7:地 8:R0- 9:R0 10:R1- 11:R1 12:R2- 13:R2 14:地 15:CLK- 16:CLK 17:地 18:R3- 19:R3 20:RB0-21:RB0 22:RB1- 23:RB1 24:地25:RB2- 26:RB2 27:CLK2- 28:CLK2 29:RB3- 30:RB3 每组信号线之间电阻为(数字表120欧左右)。

LVDS接口详解

1.LVDS输出接口概述液晶显示器驱动板输出的数字信号中,除了包括RGB数据信号外,还包括行同步、场同步、像素时钟等信号,其中像素时钟信号的最高频率可超过28MHz。

采用TTL接口,数据传输速率不高,传输距离较短,且抗电磁干扰(EMI)能力也比较差,会对RGB数据造成一定的影响;另外,TTL 多路数据信号采用排线的方式来传送,整个排线数量达几十路,不但连接不便,而且不适合超薄化的趋势。

采用LVDS输出接口传输数据,可以使这些问题迎刃而解,实现数据的高速率、低噪声、远距离、高准确度的传输。

那么,什么是LVDS输出接口呢?LVDS,即Low Voltage Differential Signaling,是一种低压差分信号技术接口。

它是美国NS公司(美国国家半导体公司)为克服以TTL电平方式传输宽带高码率数据时功耗大、EMI电磁干扰大等缺点而研制的一种数字视频信号传输方式。

LVDS输出接口利用非常低的电压摆幅(约350mV)在两条PCB走线或一对平衡电缆上通过差分进行数据的传输,即低压差分信号传输。

采用LVDS输出接口,可以使得信号在差分PCB线或平衡电缆上以几百Mbit/s的速率传输,由于采用低压和低电流驱动方式,因此,实现了低噪声和低功耗。

目前,LVDS输出接口在17in及以上液晶显示器中得到了广泛的应用。

2.LVDS接口电路的组成在液晶显示器中,LVDS接口电路包括两部分,即驱动板侧的LVDS输出接口电路(LVDS发送器)和液晶面板侧的LVDS输入接口电路(LVDS接收器)。

LVDS发送器将驱动板主控芯片输出的17L电平并行RGB数据信号和控制信号转换成低电压串行LVDS信号,然后通过驱动板与液晶面板之间的柔性电缆(排线)将信号传送到液晶面板侧的LVDS接收器,LVDS接收器再将串行信号转换为TTL电平的并行信号,送往液晶屏时序控制与行列驱动电路。

图1所示为LVDS接口电路的组成示意图。

图1 LVDS接口电路的组成示意图在数据传输过程中,还必须有时钟信号的参与,LVDS接口无论传输数据还是传输时钟,都采用差分信号对的形式进行传输。

LVDS接口定义及标准

LVDS接口定義及標準LVDS接口又稱RS-644總線接口,是20世紀90年代才出現的一種數據傳輸和接口技術。

LVDS即低電壓差分信號,這種技術的核心是採用極低的電壓擺幅高速差動傳輸數據,可以實現點對點或一點對多點的連接,具有低功耗、低誤碼率、低串擾和低輻射等特點,其傳輸介質可以是銅質的PCB連線,也可以是平衡電纜。

LVDS在對信號完整性、低抖動及共模特性要求較高的系統中得到了越來越廣泛的應用。

目前,流行的LVDS技術規範有兩個標準:一個是TIA/EIA(電訊工業聯盟/電子工業聯盟)的ANSI/TIA/EIA-644標準,另一個是IEEE 1596.3標準。

1995年11月,以美國國家半導體公司為主推出了ANSI/TIA/EIA-644標準。

1996年3月,IEEE 公佈了IEEE 1596.3標準。

這兩個標準注重於對LVDS接口的電特性、互連與線路端接等方面的規範,對於生產工藝、傳輸介質和供電電壓等則沒有明確。

LVDS可採用CMOS、GaAs或其他技術實現,其供電電壓可以從+5V到+3.3V,甚至更低;其傳輸介質可以是PCB連線,也可以是特製的電纜。

標準推薦的最高數據傳輸速率是655Mbps,而理論上,在一個無衰耗的傳輸線上,LVDS的最高傳輸速率可達1.923Gbps。

LVDS接口的原理及電特性一個簡單的LVDS傳輸系統由一個驅動器和一個接收器通過一段差分阻抗為100Ω的導體連接而成,如圖1所示。

驅動器的電流源(通常為3.5mA)來驅動差分線對,由於接收器的直流輸入阻抗很高,驅動器電流大部分直接流過100Ω的終端電阻,從而在接收器輸入端產生的信號幅度大約350 mV 。

通過驅動器的開關,改變直接流過電阻的電流的有無,從而產生「1」和「0」的邏輯狀態。

在有些最新生產的LVDS接收器中,100Ω左右的電阻直接集成在片內輸入端上了,如MAXIM公司的MAX9121/9122等。

在LVDS系統中,採用差分方式傳送數據,有著比單端傳輸方式更強的共模噪聲抑制能力。

lvds 差分阻抗范围

lvds 差分阻抗范围

LVDS(低电压差分信号)是一种常用的高速串行通信接口标准,通常用于在PCB板上传输高速数字信号。

LVDS差分信号线路的阻抗

范围通常在90欧姆左右。

在设计LVDS差分信号线路时,确保差分阻抗匹配是非常重要的。

一般来说,差分阻抗的范围应该控制在85欧姆到100欧姆之间,以

确保信号的传输质量和稳定性。

对于PCB板上的差分信号线路,通

常会采用特殊的布线技术和材料来确保阻抗匹配,比如控制线宽、

线间距和层间距等参数。

另外,还需要注意信号线的走线路径、信号线与其他线路的交叉、信号线的终端匹配等因素,这些都会对差分信号线路的阻抗产

生影响。

因此,在设计LVDS差分信号线路时,需要综合考虑布线、

材料选择、信号完整性等多个因素,以确保差分阻抗在合适的范围内,从而保证信号的传输质量和稳定性。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

LVDS接口标准LVDS接口是LCD Panel通用的接口标准,以8-bit Panel为例,包括5组传输线,其中4组是数据线,代表Tx0+/Tx0-... Tx3+/Tx3-。

还有一组是时钟信号,代表TxC+/TxC-。

相应的在Panel 一端有5组接收线。

如果是6-bit Panel则只有3组数据线和一组时钟线。

LVDS接口又称RS-644总线接口,是20世纪90年代才出现的一种数据传输和接口技术。

LVDS即低电压差分信号,这种技术的核心是采用极低的电压摆幅高速差动传输数据,可以实现点对点或一点对多点的连接,具有低功耗、低误码率、低串扰和低辐射等特点,其传输介质可以是铜质的PCB连线,也可以是平衡电缆。

LVDS在对信号完整性、低抖动及共模特性要求较高的系统中得到了越来越广泛的应用。

目前,流行的LVDS技术规范有两个标准:一个是TIA/EIA(电讯工业联盟/电子工业联盟)的ANSI/TIA/EIA-644标准,另一个是IEEE 1596.3标准。

1995年11月,以美国国家半导体公司为主推出了ANSI/TIA/EIA-644标准。

1996年3月,IEEE公布了IEEE 1596.3标准。

这两个标准注重于对LVDS接口的电特性、互连与线路端接等方面的规范,对于生产工艺、传输介质和供电电压等则没有明确。

LVDS可采用CMOS、GaAs或其他技术实现,其供电电压可以从+5V到+3.3V,甚至更低;其传输介质可以是PCB连线,也可以是特制的电缆。

标准推荐的最高数据传输速率是655Mbps,而理论上,在一个无衰耗的传输线上,LVDS的最高传输速率可达1.923Gbps。

---- OpenLDI标准在笔记本电脑中得到了广泛的应用,绝大多数笔记本电脑的LCD显示屏与主机板之间的连接接口都采用了OpenLDI标准。

OpenLDI接口标准的基础是低压差分信号(Low Voltage Differential Signaling,LVDS)接口,它具有高效率、低功耗、高速、低成本、低杂波干扰、可支持较高分辨率等特点。

LVDS接口在电信、通讯、消费类电子、汽车、医疗仪器中广泛使用,并已经得到了AMP、3M、Samsung、Sharp、Silicon Graphics等公司的支持。

为了向台式机领域渗透,NS公司又专门针对LCD显示器推出了新的支持OpenLDI标准的芯片组DS90C387和DS90CF388,新的芯片组支持从VGA(640×480)~QXGA(2048×1536)的分辨率。

---- DVI标准虽然还没有OpenLDI标准那样声名显赫,应用也没有OpenLDI标准那样普遍。

但是由于有Intel、IBM、HP等大公司的加入,DVI的应用前景被普遍看好,一些数字型CRT显示器、LCD显示器和数据投影机中已经采用了符合DVI标准的数字显示接口。

---- 目前大多数计算机与外部显示设备之间都是通过模拟VGA接口连接,计算机内部以数字方式生成的显示图像信息,被显卡中的D/A(数字/模拟)转换器转变为R、G、B三原色信号和行、场同步信号,信号通过电缆传输到显示设备中。

对于模拟显示设备,如模拟CRT显示器,信号被直接送到相应的处理电路,驱动控制显像管生成图像。

而对于LCD、DLP等数字显示设备,显示设备中需配置相应的A/D(模拟/数字)转换器,将模拟信号转变为数字信号。

在经过D/A和A/D2次转换后,不可避免地造成了一些图像细节的损失。

---- DVI标准由DDWG于1994年4月正式推出,它的基础是Silicon Image公司的PanalLink 接口技术,PanalLink接口技术采用的是最小化传输差分信号(Transition Minimized Differential Signaling,S)作为基本电气连接。

如附图所示,计算机中生成的图像信息传送到显示处理单元(显卡)中,经处理并编码成数据信号,数据信号中包含了一些像素信息、同步信息以及一些控制信息,信息通过3个通道输出。

同时还有一个通道用来传送使发送和接收端同步的时钟信号。

每一个通道中数据以差分信号方式传输,因此每一个通道需要2根传输线。

由于采用差分信号传输,数据发送和接收中识别的都是压差信号,因此传输线缆长度对信号影响较小,可以实现远距离的数据传输。

在接收端对接收到的数据进行解码,并处理生成图像信息供数字显示设备显示。

在DVI标准中对接口的物理方式、电气指标、时钟方式、编码方式、传输方式、数据格式等进行了严格的定义和规范。

对于数字显示设备,由于没有D/A和A/D转换过程,避免了图像细节的丢失,从而保证了计算机生成图像的完整再现。

在DVI接口标准中还增加了一个热插拔监测信号,从而真正实现了即插即用DVI标准一经推出立即得到了响应,不仅各图形芯片厂商纷纷推出了系列支持DVI标准的芯片组,ViewSonic、Samsung等公司也相继推出了采用DVI标准接口的数字型CRT显示器和LCD显示器。

在新近上市的一些LCD和DLP数据投影机中我们也看到了DVI标准接口。

随着数字化时代的来临,DVI标准接口取代VGA接口成为显示设备事实标准接口指日可待。

1 LVDS介绍LVDS(Low Voltage Differential Signaling)是一种低摆幅的差分信号技术,它使得信号能在差分PCB线对或平衡电缆上以几百Mbps的速率传输,其低压幅和低电流驱动输出实现了低噪声和低功耗。

几十年来,5V供电的使用简化了不同技术和厂商逻辑电路之间的接口。

然而,随着集成电路的发展和对更高数据速率的要求,低压供电成为急需。

降低供电电压不仅减少了高密度集成电路的功率消耗,而且减少了芯片内部的散热,有助于提高集成度。

减少供电电压和逻辑电压摆幅的一个极好例子是低压差分信号(LVDS)。

LVDS物理接口使用1.2V 偏置提供400mV摆幅的信号(使用差分信号的原因是噪声以共模的方式在一对差分线上耦合出现,并在接收器中相减从而可消除噪声)。

LVDS驱动和接收器不依赖于特定的供电电压,因此它很容易迁移到低压供电的系统中去,而性能不变。

作为比较,ECL和PECL技术依赖于供电电压,ECL要求负的供电电压,PECL参考正的供电电压总线上电压值(Vcc)而定。

而GLVDS是一种发展中的标准尚未确定的新技术,使用500mV的供电电压可提供250mV 的信号摆幅。

不同低压逻辑信号的差分电压摆幅示于图1。

LVDS在两个标准中定义。

IEEE P1596.3(1996年3月通过),主要面向SCI(Scalable Coherent Interface),定义了LVDS的电特性,还定义了SCI协议中包交换时的编码;ANSI/EIA/EIA-644(1995年11月通过),主要定义了LVDS的电特性,并建议了655Mbps的最大速率和1.823Gbps的无失真媒质上的理论极限速率。

在两个标准中都指定了与物理媒质无关的特性,这意味着只要媒质在指定的噪声边缘和歪斜容忍范围内发送信号到接收器,接口都能正常工作。

LVDS具有许多优点:①终端适配容易;②功耗低;③具有fail-safe特性确保可靠性;④低成本;⑤高速传送。

这些特性使得LVDS在计算机、通信设备、消费电子等方面得到了广泛应用。

图2给出了典型的LVDS接口,这是一种单工方式,必要时也可使用半双工、多点配置方式,但一般在噪声较小、距离较短的情况下才适用。

每个点到点连接的差分对由一个驱动器、互连器和接收器组成。

驱动器和接收器主要完成TTL信号和LVDS信号之间的转换。

互连器包含电缆、PCB 上差分导线对以及匹配电阻。

LVDS驱动器由一个驱动差分线对的电流源组成 通常电流为3.5mA),LVDS接收器具有很高的输入阻抗,因此驱动器输出的电流大部分都流过100Ω 的匹配电阻,并在接收器的输入端产生大约350mA 的电压。

当驱动器翻转时,它改变流经电阻的电流方向,因此产生有效的逻辑″1″和逻辑″0″状态。

低摆幅驱动信号实现了高速操作并减小了功率消耗,差分信号提供了适当噪声边缘和功率消耗大幅减少的低压摆幅。

功率的大幅降低允许在单个集成电路上集成多个接口驱动器和接收器。

这提高了PCB板的效能,减少了成本。

不管使用的LVDS传输媒质是PCB线对还是电缆,都必须采取措施防止信号在媒质终端发生反射,同时减少电磁干扰。

LVDS要求使用一个与媒质相匹配的终端电阻(100±20Ω),该电阻终止了环流信号,应该将它尽可能靠近接收器输入端放置。

LVDS驱动器能以超过155.5Mbps的速度驱动双绞线对,距离超过10m。

对速度的实际限制是:①送到驱动器的TTL数据的速度;②媒质的带宽性能。

通常在驱动器侧使用复用器、在接收器侧使用解复用器来实现多个TTL信道和一个LVDS信道的复用转换,以提高信号速率,降低功耗。

并减少传输媒质和接口数,降低设备复杂性。

LVDS接收器可以承受至少±1V的驱动器与接收器之间的地的电压变化。

由于LVDS驱动器典型的偏置电压为+1.2V,地的电压变化、驱动器偏置电压以及轻度耦合到的噪声之和,在接收器的输入端相对于接收器的地是共模电压。

这个共模范围是:+0.2V~+2.2V。

建议接收器的输入电压范围为:0V~+2.4V。

2 LVDS系统的设计LVDS系统的设计要求设计者应具备超高速单板设计的经验并了解差分信号的理论。

设计高速差分板并不很困难,下面将简要介绍一下各注意点。

2.1 PCB板(A)至少使用4层PCB板(从顶层到底层):LVDS信号层、地层、电源层、TTL信号层;(B)使TTL信号和LVDS信号相互隔离,否则TTL可能会耦合到LVDS线上,最好将TTL和LVDS 信号放在由电源/地层隔离的不同层上;(C)使LVDS驱动器和接收器尽可能地靠近连接器的LVDS端;(D)使用分布式的多个电容来旁路LVDS设备,表面贴电容靠近电源/地层管脚放置;(E)电源层和地层应使用粗线,不要使用50Ω布线规则;(F)保持PCB地线层返回路径宽而短;(G)应该使用利用地层返回铜线(gu9ound return wire)的电缆连接两个系统的地层;(H)使用多过孔(至少两个)连接到电源层(线)和地层(线),表面贴电容可以直接焊接到过孔焊盘以减少线头。

2.2 板上导线(A)微波传输线(microstrip)和带状线(stripline)都有较好性能;(B)微波传输线的优点:一般有更高的差分阻抗、不需要额外的过孔;(C)带状线在信号间提供了更好的屏蔽。

2.3 差分线(A)使用与传输媒质的差分阻抗和终端电阻相匹配的受控阻抗线,并且使差分线对离开集成芯片后立刻尽可能地相互靠近(距离小于10mm),这样能减少反射并能确保耦合到的噪声为共模噪声;(B)使差分线对的长度相互匹配以减少信号扭曲,防止引起信号间的相位差而导致电磁辐射;(C)不要仅仅依赖自动布线功能,而应仔细修改以实现差分阻抗匹配并实现差分线的隔离;(D)尽量减少过孔和其它会引起线路不连续性的因素;(E)避免将导致阻值不连续性的90°走线,使用圆弧或45°折线来代替;(F)在差分线对内,两条线之间的距离应尽可能短,以保持接收器的共模抑制能力。