单片机上拉电阻 下拉电阻的详解和选取

单片机上拉电阻、下拉电阻的详解和选取

单片机上拉电阻、下拉电阻的详解和选取一、定义1、上拉就是将不确定的信号通过一个电阻嵌位在高电平!“电阻同时起限流作用”!下拉同理!2、上拉是对器件注入电流,下拉是输出电流3、弱强只是上拉电阻的阻值不同,没有什么严格区分4、对于非集电极(或漏极)开路输出型电路(如普通门电路)提升电流和电压的能力是有限的,上拉电阻的功能主要是为集电极开路输出型电路输出电流通道。

二、拉电阻作用1、一般作单键触发使用时,如果IC本身没有内接电阻,为了使单键维持在不被触发的状态或是触发后回到原状态,必须在IC外部另接一电阻。

2、数字电路有三种状态:高电平、低电平、和高阻状态,有些应用场合不希望出现高阻状态,可以通过上拉电阻或下拉电阻的方式使处于稳定状态,具体视设计要求而定!3、一般说的是I/O端口,有的可以设置,有的不可以设置,有的是内置,有的是需要外接,I/O端口的输出类似与一个三极管的C,当C接通过一个电阻和电源连接在一起的时候,该电阻成为上C拉电阻,也就是说,如果该端口正常时为高电平;C通过一个电阻和地连接在一起的时候,该电阻称为下拉电阻,使该端口平时为低电平,作用吗:比如:“当一个接有上拉电阻的端口设为输入状态时,他的常态就为高电平,用于检测低电平的输入”。

4、上拉电阻是用来解决总线驱动能力不足时提供电流的。

一般说法是拉电流,下拉电阻是用来吸收电流的,也就是我们通常所说的灌电流5、接电阻就是为了防止输入端悬空6、减弱外部电流对芯片产生的干扰7、保护cmos内的保护二极管,一般电流不大于10mA8、通过上拉或下拉来增加或减小驱动电流9、改变电平的电位,常用在TTL-CMOS匹配10、在引脚悬空时有确定的状态11、增加高电平输出时的驱动能力。

12、为OC门提供电流三、上拉电阻应用原则1、当TTL电路驱动COMS电路时,如果TTL电路输出的高电平低于COMS电路的最低高电平(一般为3。

上拉下拉电阻的选择原理

上拉下拉电阻的选择原理上拉下拉电阻是在数字电路设计和微控制器中经常用到的一种元件,用于设置输入端的状态或者确保信号的稳定性。

它们在很多场景中都起到了关键作用,包括开关、计数器、数据总线的驱动等等。

下面,我将详细解释上拉下拉电阻的选择原理。

首先,我们需要明确上拉和下拉的概念。

上拉电阻是将输入端拉高到高电平,而下拉电阻则是将输入端拉低到低电平。

它们的目的是确保输入端在不受外部信号时也能保持在所需的状态,以免发生误操作或干扰。

选择上拉或下拉电阻的原理主要取决于具体的应用场景和需求。

下面将详细介绍几个常见的选择原则。

1. 输入信号的逻辑级别:当输入信号处于低电平时,可以选择使用上拉电阻将其拉高到高电平。

同样,当输入信号处于高电平时,可以使用下拉电阻将其拉低到低电平。

这样可以确保输入信号在正常工作范围内,并且遵循逻辑规则。

2. 信号的稳定性和噪声抑制:如果输入信号在没有外部信号时需要保持在一定的状态,可以使用上拉或下拉电阻。

这样可以防止输入端的浮动,避免干扰信号的干扰或误操作。

3. 电路驱动能力:上拉和下拉电阻的大小也会影响到电路的驱动能力。

较大的电阻值会降低电路的驱动能力,而较小的电阻值则会提高电路的驱动能力。

因此,在选择电阻值时,需要根据电路的要求和输入信号的特性来确定。

4. 电源电压级别:在一些情况下,上拉或下拉电阻的选择还要考虑电源电压级别。

例如,如果电源电压较低,可能需要选择较大的上拉或下拉电阻值来确保输入端稳定在正确的状态。

在实际应用中,为了提高系统的稳定性和抗干扰能力,有时候还会结合使用上拉和下拉电阻。

例如,可以在一个输入端同时连接上拉和下拉电阻,以确保信号在不受外界干扰时仍能保持在正确的状态,同时能够快速响应外部信号变化。

总结起来,上拉下拉电阻的选择原理主要包括输入信号的逻辑级别、信号的稳定性和噪声抑制、电路驱动能力和电源电压级别等因素。

根据具体的应用需求,可以选择合适的电阻值和连接方式来确保输入端在不受外界干扰时能够正常工作。

单片机上拉电阻和下拉电阻做作用和接线方法图解

单片机上拉电阻和下拉电阻做作用和接线方法图解

摘要: 是不是经常听别人讲,加个试试看,加个下拉电阻试试看,是不是还在疑惑上下拉电阻是什幺,该怎幺用,什幺时候用,有什幺用途? 1.什幺是上下拉电阻:把一个不确定的信号通过电阻连接到高电平,使该信号...

是不是经常听别人讲,加个试试看,加个下拉电阻试试看,是不是还在疑惑上下拉电阻是什幺,该怎幺用,什幺时候用,有什幺用途?

1.什幺是上下拉电阻

:把一个不确定的信号通过电阻连接到高电平,使该信号初始为高电平;

下拉电阻:把一个不确定的信号通过电阻连接到低电平,使该信号初始为低电平;

2.上下拉电阻的接线方法

如下图所示:

电阻R12 将KEY1 网络标识上拉到高电平,在按键S2 没有按下的情况下KEY1 将被钳制在高电平,从而避免了引脚悬空而引起的误动作;

下拉电阻如下图所示:

电阻R29 将DIR 网络标识下拉到低电平,在光耦没有导通的情况下DIR

将被钳制在低电平,从而避免了引脚悬空而引起的误动作;

3.上下拉电阻的作用

提高电路稳定性,避免引起误动作。

第一图中的按键如果不通过电阻上拉到高电平,那幺在上电瞬间可能就发生误动作,因为在上电瞬间的引脚电平。

电阻之上拉电阻与下拉电阻详解(转)

电阻之上拉电阻与下拉电阻详解(转)上拉(Pull Up )或下拉(Pull Down)电阻(两者统称为“拉电阻”)最基本的作⽤是:将状态不确定的信号线通过⼀个电阻将其箝位⾄⾼电平(上拉)或低电平(下拉),⽆论它的具体⽤法如何,这个基本的作⽤都是相同的,只是在不同应⽤场合中会对电阻的阻值要求有所不同,从⽽也引出了诸多新的概念,本节我们就来⼩谈⼀下这些内容。

如果拉电阻⽤于输⼊信号引脚,通常的作⽤是将信号线强制箝位⾄某个电平,以防⽌信号线因悬空⽽出现不确定的状态,继⽽导致系统出现不期望的状态,如下图所⽰:在实际应⽤中,10K欧姆的电阻是使⽤数量最多的拉电阻。

需要使⽤上拉电阻还是下拉电阻,主要取决于电路系统本⾝的需要,⽐如,对于⾼有效的使能控制信号(EN),我们希望电路系统在上电后应处于⽆效状态,则会使⽤下拉电阻。

假设这个使能信号是⽤来控制电机的,如果悬空的话,此信号线可能在上电后(或在运⾏中)受到其它噪声⼲扰⽽误触发为⾼电平,从⽽导致电机出现不期望的转动,这肯定不是我们想要的,此时可以增加⼀个下拉电阻。

⽽相应的,对于低有效的复位控制信号(RST#),我们希望上电复位后处于⽆效状态,则应使⽤上拉电阻。

⼤多数具备逻辑控制功能的芯⽚(如单⽚机、FPGA等)都会集成上拉或下拉电阻,⽤户可根据需要选择是否打开,STM32单⽚机GPIO模式即包含上拉或下拉,如下图所⽰(来⾃ST数据⼿册):根据拉电阻的阻值⼤⼩,我们还可以分为强拉或弱拉(weak pull-up/down),芯⽚内部集成的拉电阻通常都是弱拉(电阻⽐较⼤),拉电阻越⼩则表⽰电平能⼒越强(强拉),可以抵抗外部噪声的能⼒也越强(也就是说,不期望出现的⼲扰噪声如果要更改强拉的信号电平,则需要的能量也必须相应加强),但是拉电阻越⼩则相应的功耗也越⼤,因为正常信号要改变信号线的状态也需要更多的能量,在能量消耗这⼀⽅⾯,拉电阻是绝不会有所偏颇的,如下图所⽰:对于上拉电阻R1⽽⾔,控制信号每次拉低L都会产⽣VCC/R1的电流消耗(没有上拉电阻则电流为0),相应的,对于下拉电阻R2⽽⾔,控制信号每次拉⾼H也会产⽣VCC/R2R 电流消耗(本⽂假设⾼电平即为VCC)。

单片机上下拉电阻使用

单片机上下拉电阻使用1. 前言嘿,朋友们!今天我们来聊聊单片机里的一个小角色——上下拉电阻。

别看它小,实际可是一位默默无闻的幕后英雄!如果没有它,单片机可能会闹出不少笑话。

准备好了吗?我们就从头开始说说这位电阻的故事。

2. 什么是上下拉电阻?2.1 上拉电阻首先,上拉电阻就像是个调皮的小孩,时不时就要把信号拉到高电平。

简单来说,当我们把上拉电阻连接到单片机的引脚上时,这个引脚就会被“强制”拉到高电平。

这样一来,电路中的“静默”状态就能避免产生误操作。

想象一下,如果你有一个朋友总是给你发信息问“你在吗?”而你又不想理他,那你可能就需要这个上拉电阻来帮忙,让他保持安静。

2.2 下拉电阻接下来是下拉电阻,它就像是一个温柔的守护者,静静地把信号拉到低电平。

比如,当我们需要确保某个引脚在没有输入时不会浮动,就可以用下拉电阻来把它“牵引”到地。

这就像是你给你的植物浇水,不管天气多干旱,它总能保持湿润。

这样一来,我们的单片机在接受信号时就不会变得迷茫,确保它的表现始终如一。

3. 为什么要用上下拉电阻?3.1 防止浮动在单片机的世界里,浮动状态就像是个迷路的小孩,随时可能发生意外。

你说它有多麻烦?一会儿高电平,一会儿低电平,搞得程序员们哭笑不得。

上下拉电阻就像是“导航仪”,把它们拉到一个固定的状态,让程序员们能放心工作。

3.2 提高稳定性除此之外,上下拉电阻还能提高整个电路的稳定性。

我们都知道,电路就像是一场合唱,大家必须齐心协力才能唱出美妙的乐曲。

如果某个引脚不听话,可能就会影响到整个电路的运行。

使用上下拉电阻可以确保每个引脚都能稳稳当当地发声,避免发生“走音”的尴尬。

4. 实际应用中的小技巧4.1 选择电阻值说到上下拉电阻的选择,很多人可能会觉得复杂。

但其实,这就像挑选衣服一样,主要看场合和个人喜好。

一般来说,1kΩ到10kΩ的电阻是比较常见的选择。

你可以根据实际的电流需求和系统的特点来决定,别担心,试试就好!4.2 注意布局此外,电路的布局也很重要哦!电阻的位置直接影响信号的传输。

上拉下拉电阻

上拉和下拉电阻阻值选择(2009-7-25 13:16)上拉电阻:1、当TTL电路驱动COMS电路时,如果TTL电路输出的高电平低于COMS电路的最低高电平(一般为3.5V),这时就需要在TTL的输出端接上拉电阻,以提高输出高电平的值。

2、OC门电路必须加上拉电阻,才能使用。

3、为加大输出引脚的驱动能力,有的单片机管脚上也常使用上拉电阻。

4、在COMS芯片上,为了防止静电造成损坏,不用的管脚不能悬空,一般接上拉电阻产生降低输入阻抗,提供泄荷通路。

5、芯片的管脚加上拉电阻来提高输出电平,从而提高芯片输入信号的噪声容限增强抗干扰能力。

6、提高总线的抗电磁干扰能力。

管脚悬空就比较容易接受外界的电磁干扰。

7、长线传输中电阻不匹配容易引起反射波干扰,加上下拉电阻是电阻匹配,有效的抑制反射波干扰。

上拉电阻阻值的选择原则包括:1、从节约功耗及芯片的灌电流能力考虑应当足够大;电阻大,电流小。

2、从确保足够的驱动电流考虑应当足够小;电阻小,电流大。

3、对于高速电路,过大的上拉电阻可能边沿变平缓。

综合考虑以上三点,通常在1k到10k之间选取。

对下拉电阻也有类似道理对上拉电阻和下拉电阻的选择应结合开关管特性和下级电路的输入特性进行设定,主要需要考虑以下几个因素:1.驱动能力与功耗的平衡。

以上拉电阻为例,一般地说,上拉电阻越小,驱动能力越强,但功耗越大,设计是应注意两者之间的均衡。

2.下级电路的驱动需求。

同样以上拉电阻为例,当输出高电平时,开关管断开,上拉电阻应适当选择以能够向下级电路提供足够的电流。

3.高低电平的设定。

不同电路的高低电平的门槛电平会有不同,电阻应适当设定以确保能输出正确的电平。

以上拉电阻为例,当输出低电平时,开关管导通,上拉电阻和开关管导通电阻分压值应确保在零电平门槛之下。

4.频率特性。

以上拉电阻为例,上拉电阻和开关管漏源级之间的电容和下级电路之间的输入电容会形成RC延迟,电阻越大,延迟越大。

上拉电阻的设定应考虑电路在这方面的需求。

【硬件设计】上拉电阻和下拉电阻用法

【硬件设计】上拉电阻和下拉电阻的用法一、什么是上拉电阻?什么是下拉电阻?上拉就是将不确定的信号通过一个电阻嵌位在高电平!电阻同时起限流作用!下拉同理!上拉是对器件注入电流,下拉是输出电流;弱强只是上拉电阻的阻值不同,没有什么严格区分;对于非集电极(或漏极)开路输出型电路(如普通门电路)提升电流和电压的能力是有限的,上拉电阻的功能主要是为集电极开路输出型电路输出电流通道。

二、上拉电阻及下拉电阻作用:1、提高電壓准位:a.当TTL电路驱动COMS电路时,如果TTL电路输出的高电平低于COMS电路的最低高电平(一般为3.5V),这时就需要在TTL的输出端接上拉电阻,以提高输出高电平的值。

b.OC门电路必须加上拉电阻,以提高输出的搞电平值。

2、加大输出引脚的驱动能力,有的单片机管脚上也常使用上拉电阻。

3、N/A pin防靜電、防干擾:在COMS芯片上,为了防止静电造成损坏,不用的管脚不能悬空,一般接上拉电阻产生降低输入阻抗,提供泄荷通路。

同時管脚悬空就比较容易接受外界的电磁干扰。

4、电阻匹配,抑制反射波干扰:长线传输中电阻不匹配容易引起反射波干扰,加上下拉电阻是电阻匹配,有效的抑制反射波干扰。

5、預設空閒狀態/缺省電位:在一些 CMOS 输入端接上或下拉电阻是为了预设缺省电位. 当你不用这些引脚的时候, 这些输入端下拉接 0 或上拉接 1。

在I2C 总线等总线上,空闲时的状态是由上下拉电阻获得。

6. 提高芯片输入信号的噪声容限:输入端如果是高阻状态,或者高阻抗输入端处于悬空状态,此时需要加上拉或下拉,以免收到随机电平而影响电路工作。

同样如果输出端处于被动状态,需要加上拉或下拉,如输出端仅仅是一个三极管的集电极。

从而提高芯片输入信号的噪声容限增强抗干扰能力。

三、上拉电阻阻值的选择原则包括:1、从节约功耗及芯片的灌电流能力考虑应当足够大;电阻大,电流小。

2、从确保足够的驱动电流考虑应当足够小;电阻小,电流大。

上拉与下拉电阻讲解

数字电路的应用中,时常会听到上拉电阻、下拉电阻这两个词,上拉电阻、下拉电阻在电路中起着稳定电路工作状恣的作用。

1.下拉电阻电路

图1-107所示是下拉电阻电路,这是数字电路中的反相器,输入端U通过下拉电阻R1接地,这样在没有高电平输入时,可以使输入端稳定地处于低电平状态,防止了可能出现的高电平干扰使反相器误动作。

如果没有下拉电阻Rl,反相器输入端悬空,为高阻抗,外界的高电平干扰很容易从输入端加入到反相器中,从而引起反相朝输出低电平方向翻转的误动作。

在接入下拉电阻R1后,电源电压为+5V时,下拉电阻Rl一般取值在100~470Ω,由于Rl阻值很小,所以将输入端的各种高电平干扰短接到地,达到抗干扰的目的。

2.上拉电阻电路

图1-108所示是上拉电阻电路,这是数字电路中的反相器,当反相器输入端U没有输入低电平时,上拉电阻R可以使反相器输入端稳

定地处于高电平状态,防止了可能出现的低电平干扰使反相器出现误动作。

如果没有上拉电阻Rl,反相器输入端悬空,KI661- KI662外界的低电平干扰很容易从输入端加入到反相器中,从而引起反相器朝输出高电平方向翻转的误动作。

在接入上拉电阻R1后,电源电压为+5V时,上拉电阻R1一般取值在4.7~10kΩ之间,上拉电阻Rl使输入端为高电平状态,没有足够的低电平融发,反相器不会翻转,达到抗干扰的目的。

上拉电阻、下拉电阻详细解读

上拉电阻、下拉电阻详细解读电阻在电路中起限制电流的作用。

上拉电阻和下拉电阻是经常提到也是经常用到的电阻,在每个系统的设计中都用到了大量的上拉电阻和下拉电阻。

在上拉电阻和下拉电阻的电路中,经常有的疑问是:上拉电阻为何能上拉?下拉电阻为何能下拉?下拉电阻旁边为何经常会串一个电阻?简单概括为:●电源到器件引脚上的电阻叫上拉电阻,作用是平时使该引脚为高电平;●地到器件引脚上的电阻叫下拉电阻,作用是平时使该引脚为低电平。

●低电平在IC内部与GND相连接;●高电平在IC内部与超大电阻相连接。

上拉就是将不确定的信号通过一个电阻钳位在高电平,电阻同时起限流作用,下拉同理。

对于非集电极(或漏极)开路输出型电路(如普通门电路,其提升电流和电压的能力是有限的,上拉和下拉电阻的主要功能是为集电极开路输出型电路提供输出电流通道。

上拉是对器件注入电流,下拉是输出电流;强弱只是上拉或下拉电阻的阻值不同,没有什么严格区分。

当IC的I/O端口,节点为高电平时:节点处和GND之间的阻抗很大,可以理解为无穷大,这个时候通过上拉电阻(如4.7K欧,10K欧电阻)接到VCC上,上拉电阻的分压几乎可以忽略不计;当I/O端口节点需要为低电平时:直接接GND就可以了,这个时候VCC与GND 是通过刚才的上拉电阻(如4.7K欧,10K欧电阻)连接的,通过的电流很小,可以忽略不计。

电平值的大小、高低是相对于地电平来说的,因此在看电平值的大小时要参考地的电平值来看。

看看那些引脚是否接到地上,与自己是否连接外围器件没有关系,因为其实高电平还是低电平是相对于地平面来说的。

在节点与+5V之间接10K欧或4.7K欧的上拉电阻,能够把这个节点的电位拉上来,往往这个节点要求应用单片机或其它控制器来控制它(及这个节点与I/O连接)为高电平或低电平。

如果单纯的想要使这个节点成为高电平,并且输出阻抗非常大,则直接接电源也无妨,但是如果单片机要使这个节点拉低,即单片机内部使节点接地,这样5V电源和地之间就短路了。

单片机中的上拉、下拉电阻

单片机中的上拉、下拉电阻

大学的时候接触过单片机,当时纯粹是为了应付考试,发现学完之后对单片机还是一窍不通。

一直以来以为单片机是个神秘的东西,要弄明白需要花费不少的时间和精力,几次想研究单片机都被这种想法阻扰。

而本人博士生实践的项目却恰好是单片机编程,真实怕什么来什么。

没办法,只能硬着头皮上了,潜心专研了一个月,终于不再是门外汉了。

费话就不说了,下面写一点自己对单片机上拉、下拉电阻的理解,供有缘人看。

一、关于拉电流与灌电流拉即泄,主动输出电流,是从输出口输出电流。

灌即充,被动输入电流,是从输出端口流入。

吸则是主动吸入电流,是从输入端口流入拉电流和灌电流是衡量电路输出驱动能力(注意:拉、灌都是对输出端而言的,所以是驱动能力)的参数,这种说法一般用在数字电路中。

吸收电流是对输入端(输入端吸入)而言的;而拉电流(输出端流出)和灌电流(输出端被灌入)是相对输出端而言的。

输出低电平可以将某输出电位点看成电阻与地相连,输出高电平可以将某输出电位点看成电阻与电源VDD 相连。

灌电流越大,输出低电平越高,拉电流

越大,输出高电平越低。

二、关于上拉与下拉电阻增强驱动能力

主要作用:1、上拉就是将不确定的信号通过一个电阻嵌位在高电平,以此

来给芯片引脚一个确定的电平,以免使芯片引脚悬空发生逻辑错乱。

2、为加

大输出引脚的驱动能力下拉同理。

上拉是对(往)器件注入电流,下拉是输出。

上拉电阻与下拉电阻的概念与用法解释

上拉电阻定义:上拉就是将不确定的信号通过一个电阻嵌位在高电平!电阻同时起限流作用!下拉同理!上拉是对器件注入电流,下拉是输出电流;弱强只是上拉电阻的阻值不同,没有什么严格区分;对于非集电极(或漏极)开路输出型电路(如普通门电路)提升电流和电压的能力是有限的,上拉电阻的功能主要是为集电极开路输出型电路输出电流通道。

上拉:1TTL驱动CMOS时,如果TTL输出最低高电平低于CMOS最低高电平时,提高输出高电平值2 OC门必须加上拉,提高电平值3 加大输出的驱动能力(单片机较常用)4 CMOS芯片中(特别是门的芯片),为防静电干扰,不用的引脚也不悬空,一般上拉,降低阻抗,提供泄荷通路5 提高输出电平,提高芯片输入信号的噪声容限,增强抗干扰6 提高总线抗电磁能力,空脚易受电磁干扰7 长线传输中加上拉,是阻抗匹配抑制反射干扰原则:1 从节约功耗和芯片的电流、能力应是电阻尽量大,R大,I小啊2 从确保驱动能力,应当电阻足够小,R小,I大啊3 对高速电路,加上拉可能边沿平缓(上升时间延长)建议可以在1K---10K之间选(可根据实际情况)信号输入端上拉电阻的工作原理(从电路原理的角度分析输入端口电压为何会被提高)假如信号输入端是外界电路送来的低电平,那么输入端的电压不是应该被锁定在低电平吗,为什么加了个上拉电阻和电源,输入端的电压就被提高了呢?这个问题一直很困惑,希望能耐心解答。

问题补充:我想问的是上拉电阻如何实现电压上拉的,而不是问的上拉电阻的使用目的和必要性,我很清楚上拉电阻的作用和目的。

提问者:michael6810 - 二级其实你不清楚上拉电阻的作用和目的。

否则你不会困惑。

你的困惑,yao311yan805 已经说出来了。

只是你没有细心看,或者没有想到你该专著的重点。

yao311yan805 :最后一句话--“一般大家都习惯默认无信号为低电平,所以下拉电阻一般的应用较为普遍”,好像应该改一下吧。

回答者:562738047 - 九级2008-11-7 22:24上拉电阻的目的是为了保证在无信号输入时输入端的电平为高电平。

困惑已久?单片机上拉电阻、下拉电阻详解

困惑已久?单片机上拉电阻、下拉电阻详解

是不是经常听别人讲,加个上拉电阻试试看,加个下拉电阻试试看,是不是还在疑惑上下拉电阻是什么,该怎么用,什么时候用,有什么用途?

1.什么是上下拉电阻

上拉电阻:把一个不确定的信号通过电阻连接到高电平,使该信号初始为高电平;

下拉电阻:把一个不确定的信号通过电阻连接到低电平,使该信号初始为低电平;

2.上下拉电阻的接线方法

上拉电阻如下图所示:

电阻R12将KEY1网络标识上拉到高电平,在按键S2没有按下的情况下KEY1将被钳制在高电平,从而避免了引脚悬空而引起的误动作;

下拉电阻如下图所示:

电阻R29将DIR网络标识下拉到低电平,在光耦没有导通的情况下DIR将被钳制在低电平,从而避免了引脚悬空而引起的误动作;

3.上下拉电阻的作用

提高电路稳定性,避免引起误动作。

第一图中的按键如果不通过电阻上拉到高电平,那么在上电瞬间可能就发生误动作,因为在上电瞬间单片机的引脚电平是不确定的,上拉电阻R12的存在保证了其引脚处于高电平状态,而不会发生误动作。

提高输出管脚的带载能力。

受其他外围电路的影响单片机在输出高电平时能力不足,达不到VCC状态,这会影响整个系统的正常工作,上拉电阻的存在就可以使管脚的驱动能力增强。

这里特别强调如下:带片上I2C资源的单。

通俗易懂地讲解一下上拉电阻和下拉电阻的原理是什么

通俗易懂地讲解一下上拉电阻和下拉电阻的原理是什么

上拉电阻和下拉电阻在设计电路的时候经常遇到,上拉电阻可以在初始状态把信号牵制在确定的高电平,下拉电阻可以把信号牵制在确定的低电平。

下面举例详细介绍。

1.上拉电阻介绍

所谓上拉,就是端口通过电阻接至VCC电源端。

比如在设计按键电路时,按键的一端接GND,另一端接单片机的GPIO,同时会在GPIO口上接一个电阻到VCC,这个电阻就是上拉电阻。

如下图所示。

有了上拉电阻,在没有按键发生时,单片机会检测到确定的高电平,如果没有该上拉电阻的话,单片机检测到的可能是一个浮空的电平而不是确定的高电平,在检测按键的时候可能会误判。

再以PNP三极管驱动继电器为例,在基极端接一个上拉电阻,在单片机初始化阶段,端口初始化时可能电平不是确定的高电平,容易误触发PNP三极管导通,加了上拉电阻后,在单片机端口不确定的时候基极是高电平,不会让继电器无动作。

2.下拉电阻介绍

所谓下拉,就是端口通过电阻接到GND,在端口输出信号不确定的时候把信号牵制在确定的低电平。

以NPN三极管驱动继电器为例,如下图所示。

单片机作为输出端口控制三极管,输出高电平时三极管导通继电器动作;单片机输出低电平时三极管截止继电器复位。

但是在单片机的初始化阶段,端口的输出状态可能不是确定的,不是确定的高电平也不是确定的低电平,有可能使继电器误动作。

由于下拉电阻的存在,即使单片机初始化时,基极被下拉电阻牵制在低电平状态,不会发生误动作。

上拉下拉电阻计算

上拉下拉电阻计算上拉下拉电阻是数字电路中常用的一种电路,它的作用是为MCU输入引脚提供稳定的电平,使得MCU能够识别输入状态。

在实际使用中,上拉下拉电阻的数值的选择是比较关键的,需要根据具体的应用需求进行合理的计算,本文将对上拉下拉电阻的计算方法进行详细介绍。

1.上拉下拉电阻的定义上拉下拉电阻分别指连接在输入端上的上拉电阻和下拉电阻。

上拉电阻一般从输入引脚接到正电源,下拉电阻一般从输入引脚接到地。

上拉下拉电阻的作用是为了使得输入引脚能够保持一个确定的电平,当输入端未连接任何外部电路时,引脚的电平就会由上拉电阻或下拉电阻决定。

当外部电路与引脚连接时,外部电路的电平就会决定输入引脚的电平。

2.上拉下拉电阻的计算方法2.1上拉电阻的计算方法对于上拉电阻,我们需要根据输入引脚的电流来计算电阻的大小。

假设输入引脚电位为高电位时的电流为I,上拉电阻的阻值为R,那么上拉电阻的计算公式如下:R = (Vcc - Vih) / I其中Vcc为电源电压,Vih为MCU规定的高电平电压,I为输入引脚电流。

例如:对于一块5V的Arduino板子,输入引脚的高电平电压为4.2V,假设输入电流为1mA,则上拉电阻的计算公式为:R = (5 - 4.2) / 0.001 = 800Ω一般情况下,上拉电阻的阻值会选择与最近的几个电阻值中最小的一个,例如选择820Ω的电阻。

2.2下拉电阻的计算方法对于下拉电阻,我们同样需要根据输入引脚的电流来计算电阻的大小。

假设输入引脚电位为低电位时的电流为I,下拉电阻的阻值为R,那么下拉电阻的计算公式如下:R = Vih / I其中Vih为MCU规定的高电平电压,I为输入引脚电流。

例如:对于一块5V的Arduino板子,输入引脚的高电平电压为4.2V,假设输入电流为1mA,则下拉电阻的计算公式为:R = 4.2 / 0.001 = 4200Ω同样,一般情况下,下拉电阻的阻值会选择与最近的几个电阻值中最小的一个。

51单片机P0口上拉电阻的选择

51单片机P0口上拉电阻的选择作为I/O口输出的时候时,输出低电平为0 输出高电平为高组态(并非5V,相当于悬空状态,也就是说P0 口不能真正的输出高电平)。

给所接的负载提供电流,因此必须接(一电阻连接到VCC),由电源通过这个上拉电阻给负载提供电流。

P0作输入时不需要上拉电阻,但要先置1。

因为P0口作一般I/O口时上拉场效应管一直截止,所以如果不置1,下拉场效应管会导通,永远只能读到0。

因此在输入前置1,使下拉场效应管截止,端口会处于高阻浮空状态,才可以正确读入数据。

由于P0口内部没有上拉电阻,是开漏的,不管它的驱动能力多大,相当于它是没有电源的,需要外部的电路提供,绝大多数情况下P0口是必需加上拉电阻的。

1.一般的P0口在作为地址/数据复用时不接上拉电阻。

2.作为一般的I/O口时用时,由于内部没有上拉电阻,故要接上上拉电阻!!3.当p0口用来驱动PNP管子的时候,就不需要上拉电阻,因为此时的低电平有效;4.当P0口用来驱动NPN管子的时候,就需要上拉电阻的,因为此时只有当P0为1时候,才能够使后级端导通。

简单一点说就是它要驱动LCD显示屏显示就必须要有电源驱动,否则亮不了,而恰好P0口没有电源,所以就要外接电源,接上电阻是起到限流的作用;如果接P1、P2、P3端口就不用外接电源和电阻了。

P0口是开漏的,不管它的驱动能力多大,相当于它是没有电源的,需要外部的电路提供,绝大多数情况下P0口是必需加上拉电阻的;5、51单片机的P0口用作数据和地址总线时不必加上拉电阻。

有些IC的驱动能力并不强,如果P0口作为输入而加了不必要的上拉,有可能驱动IC无法将其拉回到低电平,从而使输入失败!如果是驱动led,那么用1K左右的就行了。

如果希望亮度大一些,电阻可减小,最小不要小于200欧姆,否则电流太大;如果希望亮度小一些,电阻可增大,增加到多少呢,主要看亮度情况,以亮度合适为准,一般来说超过3K以上时,亮度就很弱了,但是对于超高亮度的LED,有时候电阻为10K 时觉得亮度还能够用。

上拉电阻和下拉电阻的选型和计算

上拉电阻和下拉电阻的选型和计算1.上拉电阻的选型和计算:上拉电阻是指在输入信号引脚与Vcc之间连接一个电阻,用于将输入信号拉高到高电平。

选型和计算上拉电阻时,需要考虑以下几个因素:-输入电流需求:根据输入引脚的规格书或芯片数据手册,确定输入电流的最小要求。

一般情况下,使用的上拉电阻的电阻值应小于输入电流要求。

-电阻范围:根据所使用的电阻范围选择合适的上拉电阻。

一般而言,常用的电阻值为1kΩ到10kΩ,但在一些特殊应用中,也可能需要其他电阻值。

- 上拉电阻计算:上拉电阻的计算可以根据公式R = (Vcc - Vih) / Iin 得到。

其中,R为上拉电阻的电阻值,Vcc为供电电压,Vih为输入高电平阈值,Iin为输入电流。

根据具体输入信号的电压要求和设计要求,可以计算得到合适的上拉电阻值。

2.下拉电阻的选型和计算:下拉电阻是指在输入信号引脚与地之间连接一个电阻,用于将输入信号拉低到低电平。

选型和计算下拉电阻时,需要考虑以下几个因素:-输入电流需求:根据输入引脚的规格书或芯片数据手册,确定输入电流的最大要求。

在选择下拉电阻时,要确保电流不会超过引脚的最大输入电流。

-电阻范围:根据所使用的电阻范围选择合适的下拉电阻。

一般而言,常用的电阻值为1kΩ到10kΩ,但在一些特殊应用中,也可能需要其他电阻值。

- 下拉电阻计算:下拉电阻的计算可以根据公式R = Vil / Iin 得到。

其中,R为下拉电阻的电阻值,Vil为输入低电平阈值,Iin为输入电流。

根据具体输入信号的电压要求和设计要求,可以计算得到合适的下拉电阻值。

需要注意的是,选型和计算上拉电阻和下拉电阻时,还需要考虑输入电流对电路性能的影响,以及电阻功率和稳定性的要求等因素。

总结:上拉电阻和下拉电阻的选型和计算需要根据具体的输入电流和电压要求、电阻范围以及电路设计需求等因素进行考虑。

通过使用适当的电阻值,可以将输入信号拉升或拉低到期望的电平,从而实现电子电路的正常工作。

上拉电阻与下拉电阻详解

上拉电阻:1、当TTL电路驱动COMS电路时,如果TTL电路输出的高电平低于COMS电路的最低高电平(一般为3.5V),这时就需要在TTL的输出端接上拉电阻,以提高输出高电平的值。

2、OC门电路必须加上拉电阻,才能使用。

3、为加大输出引脚的驱动能力,有的单片机管脚上也常使用上拉电阻。

4、在COMS芯片上,为了防止静电造成损坏,不用的管脚不能悬空,一般接上拉电阻产生降低输入阻抗,提供泄荷通路。

5、芯片的管脚加上拉电阻来提高输出电平,从而提高芯片输入信号的噪声容限增强抗干扰能力。

6、提高总线的抗电磁干扰能力。

管脚悬空就比较容易接受外界的电磁干扰。

7、长线传输中电阻不匹配容易引起反射波干扰,加上下拉电阻是电阻匹配,有效的抑制反射波干扰。

上拉电阻阻值的选择原则包括:1、从节约功耗及芯片的灌电流能力考虑应当足够大;电阻大,电流小。

2、从确保足够的驱动电流考虑应当足够小;电阻小,电流大。

3、对于高速电路,过大的上拉电阻可能边沿变平缓。

综合考虑以上三点,通常在1k到10k之间选取。

对下拉电阻也有类似道理对上拉电阻和下拉电阻的选择应结合开关管特性和下级电路的输入特性进行设定,主要需要考虑以下几个因素:1.驱动能力与功耗的平衡。

以上拉电阻为例,一般地说,上拉电阻越小,驱动能力越强,但功耗越大,设计是应注意两者之间的均衡。

2.下级电路的驱动需求。

同样以上拉电阻为例,当输出高电平时,开关管断开,上拉电阻应适当选择以能够向下级电路提供足够的电流。

3.高低电平的设定。

不同电路的高低电平的门槛电平会有不同,电阻应适当设定以确保能输出正确的电平。

以上拉电阻为例,当输出低电平时,开关管导通,上拉电阻和开关管导通电阻分压值应确保在低电平门槛之下。

4.频率特性。

以上拉电阻为例,上拉电阻和开关管漏源级之间的电容和下级电路之间的输入电容会形成RC延迟,电阻越大,延迟越大。

上拉电阻的设定应考虑电路在这方面的需求。

下拉电阻的设定的原则和上拉电阻是一样的。

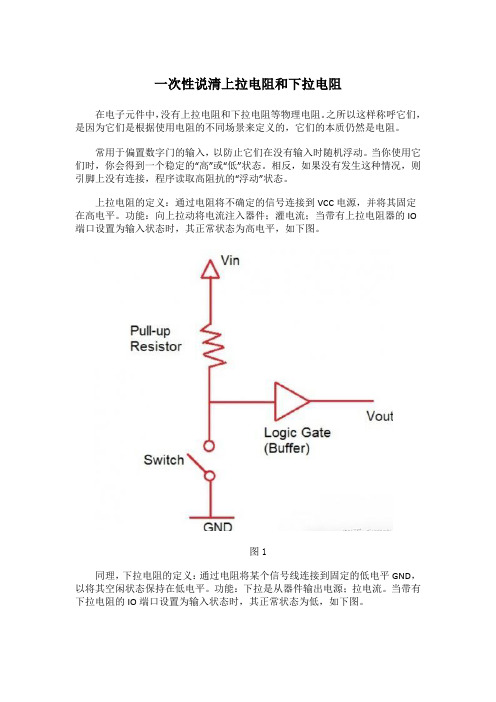

一次性说清上拉电阻和下拉电阻

一次性说清上拉电阻和下拉电阻在电子元件中,没有上拉电阻和下拉电阻等物理电阻。

之所以这样称呼它们,是因为它们是根据使用电阻的不同场景来定义的,它们的本质仍然是电阻。

常用于偏置数字门的输入,以防止它们在没有输入时随机浮动。

当你使用它们时,你会得到一个稳定的“高”或“低”状态。

相反,如果没有发生这种情况,则引脚上没有连接,程序读取高阻抗的“浮动”状态。

上拉电阻的定义:通过电阻将不确定的信号连接到VCC电源,并将其固定在高电平。

功能:向上拉动将电流注入器件;灌电流;当带有上拉电阻器的IO 端口设置为输入状态时,其正常状态为高电平,如下图。

图1同理,下拉电阻的定义:通过电阻将某个信号线连接到固定的低电平GND,以将其空闲状态保持在低电平。

功能:下拉是从器件输出电源;拉电流。

当带有下拉电阻的IO端口设置为输入状态时,其正常状态为低,如下图。

图2上拉电阻和下拉电阻2者共同的作用是:避免电压的“悬浮”,造成电路的不稳定。

如下图所示,R1为上拉电阻,R2为下拉电阻。

当R1的电阻在数百K时,它可以向信号线提供非常小的负载电流,负载电容器的充电相对较慢。

在这一点上,电阻被称为弱上拉。

同样,如果下拉电阻很大,下拉速度相对较慢,此时的电阻称为弱下拉。

如果上拉和下拉电平可以为芯片提供大电流,则此时的电阻称为强上拉或强下拉图3上拉电阻的作用1、提高输出的高电平:当TTL电路驱动COMS电路时,当TTL电路的输出电平低于COMS电路的最低高电平(通常为3.5V)时,必须在TTL的输出端连接上拉电阻,以提高输出值的输出电平。

2、OC(集电极开路,TTL)门电路必须加上拉电阻,才能使用,因为管子没有电源就不能输出高电平了。

3、为了提高输出引脚的驱动能力,一些MCU通常在引脚上使用上拉电阻。

4、在COMS芯片上,为了避免静电造成的损坏,不用的管脚不能悬空,通常,连接上拉电阻以降低输入阻抗并提供放电路径。

同时,当引脚悬空时,相对容易接受外部电磁干扰(MOS器件具有高输入阻抗,非常容易受到外部干扰)。

【干货】上拉电阻、下拉电阻知多少

【干货】上拉电阻、下拉电阻知多少一、应用1、当TTL电路驱动COMS电路时,如果TTL电路输出的高电平低于COMS电路的最低高电平(一般为3、5V),这时就需要在TTL 的输出端接上拉电阻,以提高输出高电平的值。

2、OC门电路必须加上拉电阻,以提高输出的搞电平值。

3、为加大输出引脚的驱动能力,有的单片机管脚上也常使用上拉电阻。

4、在COMS芯片上,为了防止静电造成损坏,不用的管脚不能悬空,一般接上拉电阻产生降低输入阻抗,提供泄荷通路。

5、芯片的管脚加上拉电阻来提高输出电平,从而提高芯片输入信号的噪声容限增强抗干扰能力。

6、提高总线的抗电磁干扰能力。

管脚悬空就比较容易接受外界的电磁干扰。

7、长线传输中电阻不匹配容易引起反射波干扰,加上下拉电阻是电阻匹配,有效的抑制反射波干扰。

上拉电阻阻值的选择原则包括:1、从节约功耗及芯片的灌电流能力考虑应当足够大;电阻大,电流小。

2、从确保足够的驱动电流考虑应当足够小;电阻小,电流大。

3、对于高速电路,过大的上拉电阻可能边沿变平缓。

综合考虑以上三点,通常在1k到10k之间选取。

对下拉电阻也有类似道理。

二、原理:上拉电阻实际上是集电极输出的负载电阻。

不管是在开关应用和模拟放大,此电阻的选则都不是拍脑袋的。

工作在线性范围就不多说了,在这里是讨论的是晶体管是开关应用,所以只谈开关方式。

找个TTL器件的资料单独看末级就可以了,内部都有负载电阻根据不同驱动能力和速度要求这个电阻值不同,低功耗的电阻值大,速度快的电阻值小。

但芯片制造商很难满足应用的需要不可能同种功能芯片做许多种,因此干脆不做这个负载电阻,改由使用者自己自由选择外接,所以就出现OC、OD输出的芯片。

由于数字应用时晶体管工作在饱和和截止区,对负载电阻要求不高,电阻值小到只要不小到损坏末级晶体管就可以,大到输出上升时间满足设计要求就可,随便选一个都可以正常工作。

但是一个电路设计是否优秀这些细节也是要考虑的。

集电极输出的开关电路不管是开还是关对地始终是通的,晶体管导通时电流从负载电阻经导通的晶体管到地,截止时电流从负载电阻经负载的输入电阻到地,如果负载电阻选择小点功耗就会大,这在电池供电和要求功耗小的系统设计中是要尽量避免的,如果电阻选择大又会带来信号上升沿的延时,因为负载的输入电容在上升沿是通过无源的上拉电阻充电,电阻越大上升时间越长,下降沿是通过有源晶体管放电,时间取决于器件本身。

上拉电阻和下拉电阻的选型和设计计算

上拉电阻和下拉电阻的选型和设计计算上拉就是将不确定的信号通过一个电阻钳位在高电平,电阻同时起限流作用。

下拉同理。

也是将不确定的信号通过一个电阻钳位在低电平。

上拉是对器件输入电流,下拉是输出电流;强弱只是上拉电阻的阻值不同,没有什么严格区分;对于非集电极(或漏极)开路输出型电路(如普通门电路)提升电流和电压的能力是有限的,上拉电阻的功能主要是为集电极开路输出型电路输出电流通道。

常见各类技术资料上,有些技术规范写道“无用的管脚不允许悬空状态,必须接上拉或下拉电阻以提供确定的工作状态”。

这个提法基本是对的,但也不全对。

下面详细加以说明。

管脚上拉下拉电阻设计出发点有两个:一个是在正常工作或单一故障状态下,管脚均不应出现不定状态,如接头脱落后导致的管脚悬空;二是从功耗的角度考虑,就是在长时间的管脚等待状态下,管脚端口的电阻上不应消耗太多电流,尤其是对电池供电设备。

从抗扰的角度,信号端口优选上拉电阻。

上拉电阻时,在待机状态下,源端输入常为高阻态,如果没有上拉电阻或下拉电阻,输入导线呈现天线效应,一旦管脚受到辐射干扰,管脚输入状态极容易被感应发生变化。

所以,这个电阻是肯定要加的。

下一个问题就是加上拉还是下拉。

如果加了下拉,在平常状态下,输入表现为低电平,但辐射干扰进来后,会通过下拉电阻泻放到地,就会发生从Low—High的一个跳变,产生误触发。

相当于一个乞丐,你给了他10万元,他的生活方式就会从穷人到富人发生一个改变。

但如果加了上拉电阻,在平常状态下,输入表现为高电平,辐射干扰进来后,如果低也没关系,上拉电阻会将输入端钳位在高电平,如果辐射干扰强,超过了Vcc的电平,导线上的高电平干扰会通过上拉电阻泻放到Vcc上去,无论怎样干扰,都只会发生High—Higher的变化,不会产生误触发。

相当于人家本来是一个富豪,你给了他10万元,他的生活方式不会发生任何的改变。

图1和图2是干扰状态下的电平示意图。

图2中的低电平由VL变为VL+ΔV时,产生了从低电平到高电平的跳变,有可能使后级电路误动作的风险。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

单片机上拉电阻下拉电阻的详解和选取

一、定义

1、上拉就是将不确定的信号通过一个电阻嵌位在高电平!“电阻同时起限流作用”!下拉同理!

2、上拉是对器件注入电流,下拉是输出电流

3、弱强只是上拉电阻的阻值不同,没有什么严格区分

4、对于非集电极(或漏极)开路输出型电路(如普通门电路)提升电流和电压的能力是有限的,上拉电阻的功能主要是为集电极开路输出型电路输出电流通道。

二、拉电阻作用

1、一般作单键触发使用时,如果IC本身没有内接电阻,为了使单键维持在不被触发的状态或是触发后回到原状态,必须在IC外部另接一电阻。

2、数字电路有三种状态:高电平、低电平、和高阻状态,有些应用场合不希望出现高阻状态,可以通过上拉电阻或下拉电阻的方式使处于稳定状态,具体视设计要求而定!

3、一般说的是I/O端口,有的可以设置,有的不可以设置,有的是内置,有的是需要外接,I/O端口的输出类似与一个三极管的C,当C接通过一个电阻和电源连接在一起的时候,该电阻成为上C拉电阻,也就是说,如果该端口正常时为高电平;C通过一个电阻和地连接在一起的时候,该电阻称为下拉电阻,使该端口平时为低电平,作用吗:比如:“当一个接有上拉电阻的端口设为输入状态时,他的常态就为高电平,用于检测低电平的输入”。

4、上拉电阻是用来解决总线驱动能力不足时提供电流的。

一般说法是拉电流,下拉电阻是用来吸收电流的,也就是我们通常所说的灌电流

5、接电阻就是为了防止输入端悬空

6、减弱外部电流对芯片产生的干扰

7、保护cmos内的保护二极管,一般电流不大于

10mA

8、通过上拉或下拉来增加或减小驱动电流

9、改变电平的电位,常用在TTL-CMOS匹配

10、在引脚悬空时有确定的状态

11、增加高电平输出时的驱动能力。

12、为OC门提供电流

三、上拉电阻应用原则

1、当TTL电路驱动COMS电路时,如果TTL电路输出的高电平低于COMS电路的最低高电平(一般为3。

5V),这时就需要在TTL的输出端接上拉电阻,以提高输出高电平的值。

……………………..

2、OC门电路“必须加上拉电阻,才能使用”。

3、为加大输出引脚的驱动能力,有的单片机管脚上也常使用上拉电阻。

4、在COMS芯片上,为了防止静电造成损坏,不用的管脚不能悬空,一般接上拉电阻产生降低输入阻抗,提供泄荷通路。

5、芯片的管脚加上拉电阻来提高输出电平,从而提高芯片输入信号的噪声容限增强抗干扰能力。

6、提高总线的抗电磁干扰能力。

管脚悬空就比较容易接受外界的电磁干扰。

7、长线传输中电阻不匹配容易引起反射波干扰,加上下拉电阻是电阻匹配,有效的抑制反射波干扰。

8、在数字电路中不用的输入脚都要接固定电平,通过1k电阻接高电平或接地。

四、上拉电阻阻值选择原则

1、从节约功耗及芯片的灌电流能力考虑应当足够大;电阻大,电流小。

2、从确保足够的驱动电流考虑应当足够小;电阻小,电流大。

3、对于高速电路,过大的上拉电阻可能边沿变平缓。

综合考虑

以上三点,通常在1k到10k之间选取。

对下拉电阻也有类似道理。

对上拉电阻和下拉电阻的选择应“结合开关管特性和下级电路的输入特性进行设定,主要需要考虑以下几个因素”:

1。

驱动能力与功耗的平衡。

以上拉电阻为例,一般地说,上拉电阻越小,驱动能力越强,但功耗越大,设计是应注意两者之间的均衡。

2。

下级电路的驱动需求。

同样以上拉电阻为例,当输出高电平时,开关管断开,上拉电阻应适当选择以能够向下级电路提供足够的电流。

3。

高低电平的设定。

不同电路的高低电平的门槛电平会有不同,电阻应适当设定以确保能输出正确的电平。

以上拉电阻为例,当输出低电平时,开关管导通,上拉电阻和开关管导通电阻分压值应确保在零电平门槛之下。

4。

频率特性。

以上拉电阻为例,上拉电阻和开关管漏源级之间的电容和下级电路之间的输入电容会形成“RC 延迟”,电阻越大,延迟越大。

上拉电阻的设定应考虑电路在这方面的需求。

下拉电阻的设定的原则和上拉电阻是一样的。

OC门输出高电平时是一个高阻态,其上拉电流要由上拉电阻来提供,设输入端每端口不大于100uA,设输出口驱动电流约500uA,标准工作电压是5V,输入口的高低电平门限为0.8V(低于此值为低电平);2V(高电平门限值)。

选上拉电阻时:500uA x 8.4K= 4.2即选大于8.4K时输出端能下拉至0.8V以下,此为最小阻值,再小就拉不下来了。

如果输出口驱动电流较大,则阻值可减小,保证下拉时能低于0.8V即可。

当输出高电平时,忽略管子的漏电流,两输入口需200uA,200uA x15K=3V即上拉电阻压降为3V,输出口可达到2V,此阻值为最大阻值,再大就拉不到2V了。

选10K可用。

【最大压降/最大电流、最小压降/最小电流】

COMS门的可参考74HC系列设计时管子的漏电流不可忽略,IO口实际电流在不同电平下也是不同的,上述仅仅是原理,一句话概括为:“输出高电平时要喂饱后面的输入口,输出低电平不要把输出口喂撑了”(否则多余的电流喂给了级联的输入口,高于低电平门限值就不可靠了)

此外,还应注意以下几点:

A、要看输出口驱动的是什么器件,如果该器件需要高电压的话,而输出口的输出电压又不够,就需要加上拉电阻。

B、如果有上拉电阻那它的端口在默认值为高电平,你要控制它必须用低电平才能控制如三态门电路三极管的

集电极,或二极管正极去控制把上拉电阻的电流拉下来成为低电平。

反之,

C、尤其用在接口电路中,为了得到确定的电平,一般采用这种方法,以保证正确的电路状态,以免发生意外,比如,在电机控制中,逆变桥上下桥臂不能直通,如果它们都用同一个单片机来驱动,必须设置初始状态。

防止直通!

驱动尽量用灌电流。

电阻在选用时,选用经过计算后与标准值最相近的一个!

P0为什么要上拉电阻原因有:

1。

P0口片内无上拉电阻

2。

P0为I/O口工作状态时,上方FET被关断,从而输出脚浮空,因此P0用于输出线时为开漏输出。

3。

由于片内无上拉电阻,上方FET又被关断,P0输出1时无法拉升端口电平。

P0是双向口,其它P1,P2,P3是准双向口。

准双向口是因为在读外部数据时要先“准备”一下,为什么要准备一下呢?

单片机在读准双向口的端口时,先应给端口锁存器赋1,目的是使FET关断,不至于因片内FET导通使端口钳制在低电平。

上下拉一般选10k!。