循环码二步大数逻辑译码原理实验

循环码的编码和译码

信息编码技术实验艮告三题目:循环码的编码和译码院系:计算机科学与工程学院班级:姓名:学号:【实验目的】1. 通过实验了解循环码的工作原理。

2. 了解生成多项式g(x)与编码、译码的关系。

3. 了解码距d 与纠、检错能力之间的关系。

【实验条件】仪器设备:PC 机,应用软件:Matlab 。

【实验内容]1、编程实现(7,4)系统循环码的编、译码。

已知(7, 4)循环码的生成多项式和校验多项式分别为:£(/)=疋+兀+ 1, h(x) = x 4+x 2+x + U 其生成矩阵和校验矩阵分别为:2、计算出所有的码字集合,可纠错误图样E (X 〉表和对应的错误伴随式表。

【程序代码】% (7,4)系统循环码编码.译码 clc;clear all;close all;n=7;k=4;r=n-k;mx=input ('请输入信息码字:m=\n' ) ; %输入信息码字 gx=[l Oil];x_nk=[l, zeros (1, r)];messg=conv(x.nk> mx); [qx, rxO] =deconv(messg, gx); %模 gx> qx 为所得除式,rxO 为余式 rx=mod (rxO, 2); %将余式rxO 转换为二进制cx=me ssg+rx;%编码码字多项式 c=cx瀚出编码码字 %=====绘图======== fs=1000;ts=l/fs;%fs 为一个单位内的样点 for i=l :n%以方波形式输出编码码字,一个单位内一个码字for j=l :fscx.wave ((i-1) *fs+j) =c (i);end endt=O :ts :n-ts;1 0 1 1000 0 10 1 1 00 G= 00101 1 0000 10 11 1110100 H = 0 1110 10 0011001%循环码生成多项式 %x* (n-k)> %x*(n-k)*mxplot (t, cx_wave); %以方波形式输出编码码字xlabel ('时间');ylabel C 幅度');title C (7,4)循环码编码输出波形');axis([0 7 0 1. 2]);%==^ 码===============S=zeros (1, r); 颂始化校验子gx=[l Oil]; %循环码生成多项式Rx=input (*请输入接收码字:R=\n ) ;%接收码字多项式% Rx=[l 0 1 0 1 1 1];R=Rx;繊收码字[nx, SxO]=deconv(Rx, gx); %接收码字多项式除以gx, SxO为余式(十进制) Sx=mod(SxO, 2); %将SxO转换为G (2)域下多项式S=Sx(5:7); %SxO最后3位为检验子if S=[0 0 0] 燈验子二0disp('There is no wrong!'); % 显示接收码字无错E=[0 0 0 0 0 0 0]; %査表得出错误图样为0C=R; %译码输出为接收码字elseif S=[0 0 1] %接收码字第一位r0错dispC1 r0 is wrong!'); % 显示rO 错E=[0 0 0 0 0 0 1]; %査表得出错误图样C=xor (R, E); %译码输出C=R+Eelseif S=[0 1 0] %rl 错disp('rl is wrong!');E=[0 0 0 0 0 1 0];C=xor (R, E);elseif S=[l 0 0] 紐2 错disp('ir2 is wrong!');E=[0 0 0 0 1 0 0];C=xor(R, E);elseif S=[0 1 1] %r3 错dispC1 r3 is wrong!');E=[0 0 0 1 0 0 0];C=xor (R, E);elseif S=[l 1 0] %r4 错disp('r4 is wrong!');E=[0 0 1 0 0 0 0];C=xor (R, E);elseif S=[l 1 1] %r5 错dispC r5 is wrong!');E=[0 1 0 0 0 0 0];C=xor (R, E);elseif S=[l 0 1] %r6 错dispC* r6 is wrong!1);E=[l 0 0 0 0 0 0]; C=xor (R, E);endC %输出译码码字【实验结果】请输入信息码字:[10 110 10]10 110 1 0 1 1请输入接收码字:R 二 [10 11010 110] There is no wrong!C =10 11 0 1 0 1 1 0【实验心得】通过本次实验,我加深了对循环码的1:作原理的理解,也了解了生成多项式 g(x)与编码、译码的关系和码距d 与纠、检错的关系,在动手实验过程中,对知 识点的印象更加清晰,让我的理解更加深刻了。

循环编译码实验报告

一、实验目的1. 理解循环编译码的基本原理和实现方法;2. 掌握循环编译码的编译过程和性能评估方法;3. 分析循环编译码在不同场景下的应用效果。

二、实验环境1. 操作系统:Windows 102. 编译器:Visual Studio 20193. 实验语言:C++三、实验内容1. 循环编译码的基本原理循环编译码是一种特殊的线性编译码,具有循环结构,可以将信息以循环的方式存储在码字中。

循环编译码具有以下特点:(1)循环结构:码字中的信息以循环的方式存储,即码字的前n个比特与后n个比特相对应;(2)线性结构:码字中的比特之间满足线性关系;(3)性能优越:循环编译码具有较好的纠错性能和抗干扰能力。

2. 循环编译码的编译过程循环编译码的编译过程主要包括以下步骤:(1)码字生成:根据信息比特和校验比特的线性关系,生成码字;(2)码字循环:将码字中的信息比特以循环的方式存储,实现循环结构;(3)码字传输:将码字传输到接收端;(4)码字检测:对接收到的码字进行检测,判断是否存在错误;(5)错误校正:对检测到的错误进行校正,恢复原始信息。

3. 循环编译码的性能评估循环编译码的性能评估主要包括以下指标:(1)纠错能力:循环编译码能够纠正的最大错误数量;(2)误码率:在给定信道条件下,码字中错误比特的比例;(3)抗干扰能力:循环编译码在信道干扰下的性能。

四、实验步骤1. 设计循环编译码的结构:确定码长、信息比特数、校验比特数等参数;2. 编写码字生成函数:根据信息比特和校验比特的线性关系,生成码字;3. 编写码字循环函数:将码字中的信息比特以循环的方式存储;4. 编写码字传输函数:模拟码字在信道中的传输过程;5. 编写码字检测函数:对接收到的码字进行检测,判断是否存在错误;6. 编写错误校正函数:对检测到的错误进行校正,恢复原始信息;7. 评估循环编译码的性能:在不同信道条件下,对循环编译码的纠错能力、误码率和抗干扰能力进行评估。

第六讲——循环码的译码1

第六讲——循环码的译码译码概述基本原则:最小错误概率,最大似然,最大后验概率按处理方法,可分时域译码和变换域译码 时域处理中,又可分为代数译码和概率译码循环码的代数译码一般方法:对收到的R(x)=C(x)+E(x),找到最可能发生的错误图案E(x)。

(1) 根据接收多项式R(x)计算伴随式S(x)(2) 计算错误图案)(x E ∧,即形成伴随式S(x)的最轻图案。

(3) )()()(x E x R x C ∧∧-=伴随式的循环移位令S(x)为R(x)的伴随式,则R(x)的循环移位xR(x) mod x n-1的伴随式S1(x)是S(x)的模g(x)移位运算的结果:S1(x)=xS(x) mod g(x)。

因此有:x j R(x) mod x n-1 => S j(x)=x j S(x) mod g(x);a(x)R(x) mod x n-1 => S a(x)=a(x)S(x) mod g(x)。

循环码的伴随式译码算法将常数项(或最高项)非零的可纠错误图案E(x)组成一个集合,计算它们的伴随式,构成一张表。

译码时,先计算出S(x),然后对其做0, 1, …, n-1次模g(x)移位,得到S j(x)。

比较S j(x)是否在可译表中,若在,则得到循环移位j次后的错误图案。

举例:纠一个错的循环码:汉明码。

共有n种可纠的错误图案,而它们都是000…001(伴随式为S0(x))的循环移位。

因此它们可以归为一类,即对计算出的S(x)做0~n-1次模g(x)移位,直到出现S0(x)为止,将R(x)做相应次移位后最后一位反转,再做剩余的移位,即得到正确的译码结果。

可见伴随式表可以大大缩小。

循环码的捕错译码能纠t个错的GF(q)上的(n,k)循环码,不多于t个错误全在最低的n-k位中的充要条件是w(S(x)) ≤t。

若这些错不全落在低n-k位中,则E(x)-S(x)≠0,其重量≥d=2t+1,则w(E(x)) + w(-S(x)) ≥d,而w(E(x)) ≤t,=> w(S(x)) ≥ t + 1。

循环码编译码实验报告

Harbin Institute of Technology信息论与编码报告题目:循环码编译码实验院(系)电子与信息工程学院班级通信1班学生学号序号哈尔滨工业大学循环码编译码实验1 设计内容循环码是线性分组码中最重要的一类码,它的结构完全建立在有限域多项式的基础上,它具有两个基本特点:一是编码电路与译码电路非常简单,易于实现;二是其代数性质好,分析方便,有一定的成熟的译码方法。

一个(n ,k )线性分组码C ,如果码组中的一个码字的循环移位也是这个码组中的一个码字,则称C 为循环码。

本实验主要完成以下四项内容:(1)利用(7,4)系统循环码的生成多项式为:3()1g x x x =++,请设计该循环码的编码器。

(2)随机产生重量为0或1的八种错误图样中的一种,得到实际接收码字。

(3)根据接收到的码字进行译码,译码方式分为校验子译码和梅吉特译码两种。

(4)对于在BSC 信道传输时的情形进行讨论,验证(7,4)系统循环码的纠错能力。

2 编程环境本实验采用Matlab 作为编程工具,所有代码均在Matlab 软件中运行,此软件功能强大,应用广泛,在此不再赘述。

3 各模块设计3.1 编码器模块利用(7,4)系统循环码的生成多项式为:3()1g x x x =++,请设计该循环码的编码器。

流程图为:图1 (7,4)循环码编码流程图图2 4位信息码元编码流程图在学生设计的演示工具中输入的信息码元可以为任意多个,系统自动按每4个连续的码字一组进行编码,当输入的信息码元不是4的倍数时,自动补零到与信息码元长度最接近的4的倍数。

译码时也是按照每7个连续的码字一组进行译码。

但是为了流程图的清晰明了,在本文的流程图除流程图1以外,其余均按一个循环码码字(即7位)来描述。

编码器模块源程序如下:%%%函数功能:(7,4)系统循环码编码器%%%编程时间:2013-11-29%%%该系统循环码编码器的生成多项式是g(x) = x^3 + x + 1;% %%系统循环码编码的原理是,首先用x^r乘以信息码字多项式m(x),这里r = 3;然后用x^r*m(x)除以生成多项式g(x),% %%得余式r(x);最后得系统循环码多项式c(x) = x^r*m(x) + r(x)function [code_out,code_in_L] = coder(code_in)%%code_in:输入信息码字%%code_out:输出编码后的码字%%L:输入的信息码元的长度n=7;%%每个码字长度k=4;%%每个码字中信息码元长度code_in_L=length(code_in);a=rem(code_in_L,k);%信息码元的长度除以k后的余数if a~=0 %%%信息码元长度不是k的整数倍,则补0array_0=zeros(1,k-a);%%%补零个数code_in=[code_in ,array_0];endcode_in_4=(reshape(code_in,k,length(code_in)/k))';%%%将补零后的码元变成length(code_in)/4行,4列矩阵for loop=1:length(code_in)/kmes_code = [code_in_4(loop,:),zeros(1,3)]; % 在信息码字后面补上三个零,相当于乘上x^rgen = [1 0 1 1]; % 生成多项式向量% 在二元域进行运算,必须把信息码字多项式向量和生成多项式向量转到二元域GF(2)上% 函数gf(X,M)用于从向量X生成GF(2^M)上对应的向量mes_g = gf(mes_code,1);gen_g = gf(gen,1);% 用x^r*m(x)除以生成多项式g(x)[Q,rem_g] = deconv(mes_g,gen_g); % 多项式除法其实就是解卷积运算,得到除法的商式Q,余式rem_g%%相应的,多项式乘法其实是系数的卷积code_rem = rem_g.x; % rem_g.x表示二元域向量rem_g的一个属性,即多项式的系数。

通信原理二--循环码

实验报告学科:通信原理(二)题目:数字信号基带传输系统仿真实验设备:安有matlab仿真软件的计算机学院:光电信息与通信工程学院系别:通信工程学号:姓名:指导教师:一、实验目的与要求1. 学习并理解信道编码的根本目的、技术要求与基本目标等基本概念;2. 掌握循环码、miller码的物理涵义、数学基础及检纠错原理;3. 掌握循环码、miller码的码型特点、检纠错能力、编译码方法及基本技术;4. 学会使用MATLAB 实现循环码及miller码的编译码及检纠错模拟与分析。

二、实验仪器与设备1. 安装了matlab程序的计算机 1 台三、实验原理(一)循环码循环码是线性分组码的一个重要子集,是目前研究得最成熟的一类码,它有许多特殊的代数性质,例如,循环码中任一许用码组经过循环移位后,所得到的码组仍然是许用码。

循环码A= a n−1+a n−2+…+a 1+a 0可以表示为如下的码多项式:1.生成多项式g (x)定义:若一个循环码的所有码字多项式都是一个次数最低的、非零的、首一多项式g (x)的倍式,则称g (x)为生成该码,并称g (x) 为该码的生成元或生成多项式。

可以证明生成多项式g (x)具有以下特性:(1)g (x) 是一个常数项为1 的r=n −k 次多项式;(2)g (x) 是x n+1 的一个因式;(3)该循环码中其它码多项式都是g (x)的倍式。

为了保证构成的生成矩阵G的各行线性不相关,通常用g (x) 来构造生成矩阵。

因此,一旦生成多项式g (x) 确定以后,该循环码的生成矩阵就可以确定。

设则有:2.监督多项式h(x)定义:若g (x) 是(n,k) 循环码的生成多项式,则有x n+1= g (x )h (x) 。

其中,h(x) 是k 次多项式,称为监督多项式。

也称校验多项式。

监督矩阵可表示为:其中:3.伴随式发送码C(x) 通过含噪信道时,会因各种扰而产生误码。

例如发送码为:00000000001111111111接收码为:01101001001111001001产生错误序列:01101001000000110110可见,发生了两个长度分别为7和5的突发差错,其错误图样分别为1101001 和11011。

循环码实验报告

循环码实验报告循环码实验报告引言:循环码是一种常用的纠错码,具有很好的纠错能力和编码效率。

本实验旨在通过编码和解码实验,深入了解循环码的原理和应用。

一、实验目的通过实验,掌握循环码的编码和解码过程,了解循环码的纠错能力和编码效率。

二、实验原理循环码是一种线性块码,其编码和解码过程基于生成多项式和校验多项式。

生成多项式决定了编码过程,校验多项式用于纠错。

循环码的编码过程是将信息位按照生成多项式进行除法运算,得到余数作为校验位。

解码过程是将接收到的码字进行除法运算,若余数为0,则认为接收正确;若余数不为0,则认为接收错误,并通过校验多项式进行纠错。

三、实验步骤1. 编码实验:(1)选择生成多项式和校验多项式,如生成多项式为g(x)=x^3+x+1,校验多项式为h(x)=x^3。

(2)选择一组信息位,如信息位为1011。

(3)将信息位对应的二进制数与生成多项式进行除法运算,得到余数,即编码后的码字。

如:1011除以生成多项式g(x),余数为010。

(4)将信息位和余数拼接成码字,即编码完成。

如:码字为1010010。

2. 解码实验:(1)选择一组接收到的码字,如接收到的码字为1010010。

(2)将接收到的码字与校验多项式进行除法运算,得到余数。

若余数为0,则认为接收正确;若余数不为0,则认为接收错误。

(3)若接收错误,则通过余数定位错误位置,并进行纠错。

如:接收到的码字1010010除以校验多项式h(x),余数为010。

根据余数的位置,确定错误位为第2位。

(4)将错误位取反,即可得到纠错后的码字。

如:纠错后的码字为1000010。

四、实验结果与分析通过编码实验,我们成功将信息位1011编码为码字1010010。

通过解码实验,我们成功纠错了接收到的码字,将其从1010010纠正为1000010。

循环码具有很好的纠错能力,能够在一定范围内纠正接收到的错误码字。

通过校验多项式进行纠错,可以定位错误位并进行纠正。

循环码编译码实验ppt课件

SE•HT

CP K1 K2

1 1 1 1 0 0 1 0 0 0 0 0 0 0 0

0 1 1 1 1 0 0 1 0 0 0 0 0 0 0

0 0 1 1 1 1 0 0 1 0 0 0 0 0 0

2、封锁性:循环码中任两个码组之和〔模2〕必定为该码组集合中的一个码组。 如 0100110+ 0010010=0110100也为一个码组

〔二〕生成多项式与编译码电路的关系

编码:循环码的码多项式可表示为 到的余式,代表监视位。结论:只需知道

,其中 为 就能构造编码器。

与 相除得

译码:由于 就可以构造一个除法电路,把接纳码组除以 字没有错码,否那么有错码。

数字通讯原理实验 循环码编、译码实

验

指点教师:李冰、梁仕文

一、实验目的

❖ 1. 了解生成多项式g(x)在循环码编码器和译码器之间的关系。 ❖ 2.了解码距与纠、检错才干之间的关系。

二、循环码引见

〔一〕循环码是一类很重要的线性码,具有循环性和封锁性。

1、循环性:循环码中任一码组循环一位〔将最右端的码移至左端〕以后,仍为该 码中一个码组。如0100110为一个码组,那么0010011也为一个码组。

随

发生2个错码

其中一个错码在正交位(e14)上 A3 A2 A1 A0中有三个“1”

式

两个错码均在非正交位上

A3 A2 A1 A0中有两个“1”或0个“1”

修

发生3个错码

超出纠错范围,不研究

正

结论:当三个或以上的正交方程为1时,正交位有 错码,需求纠错;当三个以下的正交方程为1时,

循环码实验报告

循环码实验报告循环码实验报告引言:循环码是一种在信息传输和存储中广泛应用的编码技术。

其具有纠错能力强、编码效率高等优点,因此在通信领域得到了广泛的应用。

本实验旨在通过实际操作,探索循环码的原理、编码和解码过程,并对其性能进行评估。

一、实验目的1. 了解循环码的基本原理和编码过程;2. 掌握循环码的解码方法;3. 评估循环码的纠错能力和编码效率。

二、实验步骤1. 生成循环码通过给定的生成多项式,使用编码器生成循环码。

生成多项式是循环码的重要参数,它决定了编码和解码的方式。

2. 添加错误位为了评估循环码的纠错能力,我们需要在生成的循环码中添加一定数量的错误位。

通过改变错误位的位置和数量,可以观察到循环码的纠错效果。

3. 解码使用循环码的解码器对添加错误位的循环码进行解码。

解码过程中,通过计算校验位和检测错误位的位置,可以进行纠错。

4. 评估性能根据解码结果,评估循环码的纠错能力和编码效率。

纠错能力可以通过计算纠错率来衡量,而编码效率可以通过计算编码后的码字长度与原始数据长度的比值来评估。

三、实验结果与分析在实验中,我们选择了一个生成多项式为G(x)=x^3+x+1的循环码进行测试。

通过编码器生成了一组循环码,并添加了不同数量的错误位。

然后,使用解码器对添加错误位的循环码进行解码。

在纠错能力方面,我们发现当错误位数量较少时,解码器可以有效地纠正错误,并恢复原始数据。

然而,当错误位数量超过循环码的纠错能力时,解码器无法正确恢复原始数据。

在编码效率方面,我们发现循环码的编码效率较高。

通过计算编码后的码字长度与原始数据长度的比值,我们可以得出编码效率为80%。

这意味着在传输或存储数据时,循环码可以有效地减少数据的长度。

四、实验总结通过本次实验,我们深入了解了循环码的原理、编码和解码过程,并对其性能进行了评估。

实验结果表明,循环码具有较强的纠错能力和高效的编码效率,适用于各种通信和存储场景。

然而,循环码也存在一些限制。

循环码实验报告

课程名称:信息论与编码课程设计题目:循环码的编码和译码程序设计指导教师:系别:专业:学号:姓名:合作者完成时间:成绩:评阅人:一、实验目的:1、通过实验了解循环码的工作原理。

2、深刻理解RS 码构造、RS 编译码等相关概念和算法。

二、实验原理1、RS 循环码编译码原理与特点设C 使某线性分组码的码字集合,如果对任C c c c C n n ∈=--),,,(021 ,它的循环移位),,,(1032)1(---=n n n c c c c C 也属于C ,则称该码为循环码。

该码在结构上有另外的限制,即一个码字任意循环移位的结果仍是一个有效码字。

其特点是:(1)可以用反馈移位寄存器很容易实现编码和伴随式的计算;(2)由于循环码有很多固有的代数结构,从而可以找到各种简单使用的译码办法。

如果一个线性码具有以下的属性,则称为循环码:如果n 元组},,,{110-=n c c c c 是子空间S 的一个码字,则经过循环移位得到的},,,{201)1(--=n n c c c c 也同样是S 中的一个码字;或者,一般来说,经过j 次循环移位后得到的},,,,,,,{11011)(---+--=j n n j n j n j c c c c c c c 也是S 中的一个码字。

RS 码的编码系统是建立在比特组基础上的,即字节,而不是单个的0和1,因此它是非二进制BCH 码,这使得它处理突发错误的能力特别强。

码长:12-=mn信息段:t n k 2-= (t 为纠错符号数)监督段:k n t -=2最小码段:12+=t d最小距离为d 的本原RS 码的生成多项式为:g(x)=(x-α)(x -α2)(x -α3)…(x -αd -2)信息元多项式为::m(x)=m0+m1x+m2x2+…+mk -1xk-1循环码特点有:1)循环码是线性分组码的一种,所以它具有线性分组的码的一般特性,且具有循环性,纠错能力强。

2)循环码是一种无权码,循环码编排的特点为相邻的两个数码之间符合卡诺中的邻接条件,即相邻数码间只有一位码元不同,因此它具有一个很好的优点是它满足邻接条件,没有瞬时错误(在数码变换过程中,在速度上会有快有慢,中间经过其他一些数码形式,即为瞬时错误)。

(完整)循环码的编码与译码

循环码是线性分组码中一个重要的子类,具有检错纠错能力强,实现方便等特点.它具有严密的代数学理论,封闭性与循环性.(n,k)循环码表示信息位为k位,监督位为(n-k)位.本次设计实验首先分析了(7,4)循环码的编码与译码原理,然后,用C语言实现其编码与译码功能。

通过C语言平台运行所编写的程序,观察了在输入信息码情况下输出对应的编码结果以及相反的译码功能。

通过多组的对比验证了该(7,4)循环码的编译码程序的正确性。

最后,在程序运行的过程中进一步分析循环码的编译码原理,并通过比较仿真模型与理论计算的性能,证明了仿真模型的可行性。

关键词:循环码,编码与译码,C程序。

现代通信的发展趋势为数字化,随着现代通信技术的不断开发,差错控制技术已日趋成熟,在各个领域都得到了广泛的应用和认同。

本文就(7,4)循环码的编码与译码原理进行C语言的编程及运行仿真。

现代社会发展要求通信系统功能越来越强,可靠性越来越高,构成也越来越复杂;这就要借助于功能强大的计算机辅助分析设计技术和工具才能实现。

现代计算机科学技术快速发展,已经研发出了新一代的可视化的仿真软件。

这些功能强大的仿真软件,使得通信系统仿真的设计和分析过程变得相对直观和便捷,由此也使得通信系统仿真技术得到了更快的发展。

本文使用的是功能强大的C语言软件。

C语言是一种使用简便的、特别适用于科学研究和工程计算的高级语言,与其他计算机语言相比,它的特点是简洁和智能化,具有极高的编程和调试效率.通过使用C工具箱函数对数字调制进行仿真,更能直观彻底的掌握循环码的编码与译码原理。

有助于我们的学习和研究,加深对知识的理解和运用. C的便利性还体现在它的仿真结果还可以存放到的工作空间里做事后处理。

方便我们修改参数对不同情况下的输出结果进行对比。

目录第1章概述 (1)第2章计算机通信与纠错码 (2)2。

1 计算机通信技术 (2)2.1.1 通信的概念 (2)2。

1。

2 通信的发展史简介 (2)2。

数据库系统原理实验 循环码

数据库系统原理实验循环码

循环码是一种纠错码,可以检测和纠正数据传输中的错误。

它由一组位组成,其中一些位被称为“校验位”,用于检测数据传输中是否出现错误。

循环码最常用于数字通信系统中,如计算机网络和通信协议。

循环码的原理是在数据流中添加一定数量的校验位,以检测数据流中的错误。

这些校验位是根据数据流的特定算法生成的,其中包括数据的异或操作、位移和除法等。

循环码具有自纠错能力,可以在数据流中检测并纠正一个或多个错误。

这是通过将错误位的值与校验位的值进行异或操作实现的。

循环码的一个重要特性是“循环不变性”。

如果将数据流的任何部分循环移位,其校验位值将不变。

这是因为循环码算法基于位移、异或和除法等操作,这些操作均符合循环不变性。

在数字通信系统中,循环码通常用于数据传输中的“帧同步”和“差错检测”等任务。

帧同步是指在数据传输中,需要解决如何

确定连续的数据位组成一个帧的问题。

循环码通常被用来解决这个问题,通过在数据流中添加特殊的标志位或同步位来实现。

这些标志位可以被看作是循环码的一种形式,用于检测和纠正数据传输中的错误。

循环码还被广泛用于数据存储和备份系统中,如硬盘和光盘等。

在硬盘中,数据被编码为一系列磁性区域,循环码可以用来纠

正由于磁性区域受损而导致的数据错误。

总之,循环码是一种通用的、有效的差错检测和纠正算法。

它被广泛应用于数字通信、数据存储和备份等领域,是数字技术的重要组成部分。

循环编码实验报告

一、实验目的1. 理解循环编码的概念和原理;2. 掌握循环编码的实现方法;3. 通过实验验证循环编码的效率和性能;4. 分析循环编码在实际应用中的优势和局限性。

二、实验原理循环编码是一种将数据序列转换为循环序列的编码方法。

在循环编码中,数据序列按照一定的规则进行排列,形成一个循环序列。

循环序列具有以下特点:1. 循环性:序列中的元素按照一定的顺序排列,形成一个循环;2. 压缩性:循环序列可以减少数据序列中的冗余信息,提高数据传输效率;3. 可逆性:循环编码具有可逆性,可以通过解码算法将循环序列还原为原始数据序列。

循环编码的基本原理如下:1. 对数据序列进行预处理,提取出数据序列中的关键信息;2. 将提取出的关键信息按照一定的规则进行排列,形成一个循环序列;3. 对循环序列进行编码,生成编码后的数据序列;4. 通过解码算法将编码后的数据序列还原为原始数据序列。

三、实验设备与软件1. 实验设备:计算机、编程软件(如C++、Python等);2. 实验软件:循环编码算法实现代码。

四、实验步骤1. 编写循环编码算法实现代码;2. 生成测试数据序列;3. 对测试数据序列进行循环编码;4. 计算编码后的数据序列的压缩比;5. 分析循环编码的性能;6. 编写实验报告。

五、实验结果与分析1. 编写循环编码算法实现代码以下是一个简单的循环编码算法实现代码示例(以Python为例):```pythondef encode(data):length = len(data)for i in range(length):for j in range(i+1, length):if data[i] > data[j]:data[i], data[j] = data[j], data[i]return datadef decode(encoded_data):return encoded_data[::-1]# 测试数据序列data = [5, 2, 9, 1, 5, 6]# 循环编码encoded_data = encode(data)# 解码decoded_data = decode(encoded_data)# 输出结果print("Original data:", data)print("Encoded data:", encoded_data)print("Decoded data:", decoded_data)```2. 计算编码后的数据序列的压缩比在本实验中,我们以数据序列的长度作为压缩比的参考指标。

通信原理实验_循环码编译码

学生实验报告系别电子工程系课程名称通信原理实验班级实验名称循环码编译码实验姓名实验时间2010年12月14 日学号指导教师报告内容一、实验目的了解生成多项式g(x)与编、译码器之间的关系,码距与纠、检错能力之间的关系。

二、实验内容1.根据编码规则验证循环码的生成多项式。

2.通过实验了解循环码的工作原理。

(1)了解生成多项式g(x)与编码及译码的关系。

(2)了解生成多项式g(x)与码距d的关系。

(3)了解码距d与纠、检错能力之间的关系。

(4)观察该码能纠几个错误码元。

(5)观察循环码的循环性以及封闭性。

3.通过实验了解编、译码器的组成方框图及其主要波形图。

4.了解信道中的噪声对该系统的影响。

三、实验原理总原理方框图如图6.1所示。

图6.1循环码的编、译码系统由下列五部分组成:定时单元、信码发生器及显示部分、编码器、模拟信道部分(虚线部分,包括错码发生器及其显示)和译码器。

(1)定时单元本单元提供编码器及译码器所需的时序信号。

其时钟重复频率(CP)为2MHZ。

(2)信码发生器本单元给编码器提供一个信号源,手控开关(板上CDIN)置于+5V时,发光二极管亮,代表输出“1”码元。

若开关置于“0”,代表输出“0”码元。

(3)循环码编码器编码器是本实验的主要部分。

根据生成多项式,采用5个异或门和D触发器组成编码器。

在K1信号的控制下,输入6位信息码元CDIN,一方面串行输入信道,另一方面通过与门送入除法电路进行计算。

第6位输入码元结束时,K1信号也为零,在CP脉冲作用下,移位寄存器将计算的结果(CDOUT)送往信道,即在6位信息码元后附加了9位监督码,使码长(n=K+r)为15(64个编码输出信号见附表1)。

(4)模拟信道传输错误部分严格说编码输出的基带信号发往信道,若信道为有线的,需加均衡设备;若为无线信号,需加调制设备。

本实验的目的是观察编码输出波形及该波形经过信道后纠错能力,尽量省去附加设备。

本实验设计了一个15位错码发生器(板上ECD框内)可在不同位置使用开关任加“1”码,并使相应的发光二极管发光,显示错码产生的位置(如图6.2所示)。

二进制(7,4)循环码编码器与译码器的仿真

二进制(7,4)循环码编码器与译码器的仿真(实用版)目录1.引言2.二进制 (7,4) 循环码编码器的原理与实现3.二进制 (7,4) 循环码译码器的原理与实现4.仿真过程与结果分析5.结论正文1.引言二进制 (7,4) 循环码是一种在数字电路中广泛应用的编码方式,其具有码字短、纠错能力强等特点。

在数字电路的设计中,编码器和译码器是必不可少的组成部分。

本文将对二进制 (7,4) 循环码编码器和译码器的原理进行介绍,并借助仿真工具对编码器和译码器进行仿真实验,以验证其正确性。

2.二进制 (7,4) 循环码编码器的原理与实现二进制 (7,4) 循环码编码器是一种将输入的二进制数据转换为对应的循环码输出的电路。

其工作原理是将输入的二进制数据按照 4 位一组进行分组,然后将每组数据转换为对应的循环码。

为了实现这一功能,我们需要设计一个具有 4 个输入端和 4 个输出端的编码器电路。

3.二进制 (7,4) 循环码译码器的原理与实现二进制 (7,4) 循环码译码器是一种将输入的循环码转换为对应的二进制数据的电路。

其工作原理是将输入的循环码按照 4 位一组进行分组,然后根据循环码的值转换为对应的二进制数据。

为了实现这一功能,我们需要设计一个具有 4 个输入端和 4 个输出端的译码器电路。

4.仿真过程与结果分析为了验证二进制 (7,4) 循环码编码器和译码器的正确性,我们借助仿真工具对它们进行了仿真实验。

在实验过程中,我们分别对编码器和译码器的输入端施加了不同的输入信号,并观察了输出端的信号变化。

实验结果表明,编码器和译码器的输出信号与理论预期相符,说明它们具有正确的逻辑功能。

5.结论本文通过对二进制 (7,4) 循环码编码器和译码器的原理进行介绍,并借助仿真工具对它们进行了仿真实验。

实验结果表明,编码器和译码器的输出信号与理论预期相符,说明它们具有正确的逻辑功能。

实验BCH循环码的编码与译码

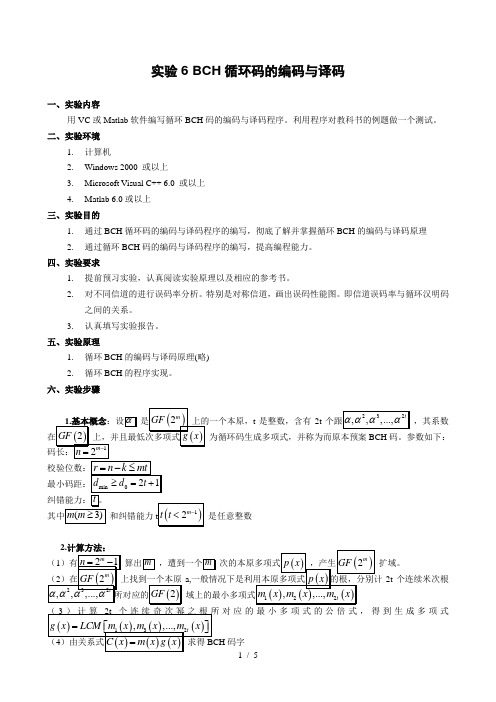

实验6 BCH循环码的编码与译码一、实验内容用VC或Matlab软件编写循环BCH码的编码与译码程序。

利用程序对教科书的例题做一个测试。

二、实验环境1.计算机2.Windows 2000 或以上3.Microsoft Visual C++ 6.0 或以上4.Matlab 6.0或以上三、实验目的1.通过BCH循环码的编码与译码程序的编写,彻底了解并掌握循环BCH的编码与译码原理2.通过循环BCH码的编码与译码程序的编写,提高编程能力。

四、实验要求1.提前预习实验,认真阅读实验原理以及相应的参考书。

2.对不同信道的进行误码率分析。

特别是对称信道,画出误码性能图。

即信道误码率与循环汉明码之间的关系。

3.认真填写实验报告。

五、实验原理1.循环BCH的编码与译码原理(略)2.循环BCH的程序实现。

六、实验步骤t是整数,含有2t,其系数为循环码生成多项式,并称为而原本预案BCH码。

参数如下:是任意整数扩域。

a,2t个连续米次根对应的最小多项式的公倍式,得到生成多项式码字3.程序实现:对于BCH(15,5),有matlab实现程序如下:①BCH编码enbch155.mfunction coded = bch155(msg_seq) %定义函数bch编码% 输入为msg_seq信息位% 输出为编码后的码元codedg=[1 0 1 0 0 1 1 0 1 1 1]; %生成多项式系数n=15;k=5; %默认为BCH(15,5)%% 从输入msg_seq中提取信息位msgdisplay('信息位:')if nargin<1 %判断输入信息,若未输入,系统自动产生5组信息码,并显示出信息位nmsg=5;msg=randi([0,1],[nmsg,k])elselmsg = length(msg_seq);nmsg = ceil(lmsg/k);msg = [msg_seq(:);zeros(nmsg*k-lmsg,1)];msg = reshape(msg,k,nmsg).'endxx = [msg zeros(nmsg,n-k)]; %将输入信息码msg拓展为矩阵形式的xx%% 进行编码,将xx编码为codedcoded =zeros(nmsg,n);for i=1:nmsg[q,r]=deconv(xx(i,:),g); %产生余式r=abs(rem(r,2));coded(i,:)=r;endcoded = coded + xx; %产生信息码end②BCH解码debch155.mM=4;code = gf(code,M);[m , n]=size(code);decode=[];code1=[];T2=6;N=15;mat=gf(2,M,code.prim_poly).^([N-1:-1:0]'*([1:T2]));Tx = [0 1 zeros(1,T2-1)];for i=1:m ;code1=code(i,:);M=code1.m;T2=6;N=15;S = code1* ((gf(2,M,code1.prim_poly)).^([N-1:-1:0]'*([1:T2])));LambdaX = gf([1 zeros(1,T2)],M,code1.prim_poly);Tx = [0 1 zeros(1,T2-1)];L=0;for k = 1:T2;LambdaXTemp = LambdaX;Delta = S(k) - LambdaXTemp(1+[1:L])*(S(k-[1:L]))';if Delta.x;LambdaX = LambdaXTemp - Delta*Tx;if 2*L < k;L = k-L;Tx = LambdaXTemp/Delta;end;end;Tx = [0 Tx(1:T2)];end;LambdaXValue = LambdaX.x;LambdaX = gf(LambdaXValue(1:max(find(LambdaXValue))), M, code1.prim_poly);errLoc_int = roots(LambdaX);errLoc = log(errLoc_int);for i = 1:length(errLoc);errorMag = 1;code1(N-errLoc(i)) = code1(N-errLoc(i)) - errorMag;end;decode=[decode;code1];end;ccode = double(decode.x);decode = ccode(:,1:5);end③测试文件 bch_en_decode.mfunction bch_en_decode(msg) %编码if nargin<1code=enbch155();else code=enbch155(msg); %编码endcode=code+randerr(5,15,1:3); %模拟信道产生错误,每行有1-3个随机错误display('信道传输中干扰后,接收到的信息');coder=rem(code,2) %对2取余,使范围是0、1display('解码后');decode=debch155(coder)end4.进行测试法一:不输入信息位,让系统自动产生信息位,在matlab中输入下面一行代码,得到结果>> bch_en_decode()信息位:msg =0 0 1 1 11 1 1 0 01 1 1 1 11 0 0 0 10 0 0 0 0编码后码元:coded =0 0 1 1 1 1 0 1 0 1 1 0 0 1 01 1 1 0 0 0 0 1 0 1 0 0 1 1 01 1 1 1 1 1 1 1 1 1 1 1 1 1 11 0 0 0 1 1 1 1 0 1 0 1 1 0 00 0 0 0 0 0 0 0 0 0 0 0 0 0 0 信道传输中干扰后,接收到的信息coder =0 0 0 1 1 1 0 1 0 1 1 0 0 1 00 1 1 0 0 0 0 1 0 1 1 0 1 1 01 1 1 1 1 1 1 1 0 0 1 0 1 1 11 0 0 0 0 0 1 1 0 1 0 1 1 0 00 0 0 0 0 0 1 1 0 0 0 0 0 1 0 解码后decode =0 0 1 1 11 1 1 0 01 1 1 1 11 0 0 0 10 0 0 0 0法二:输入信息位在matalb中输入下面两行代码,得到结果如下>> msg=[1 1 0 1 1 1 1 1 1 1 0 0 0 0 1 0 0 0 1 0 0 0 0 0 1];>> bch_en_decode(msg)信息位:msg =1 1 0 1 11 1 1 1 10 0 0 0 10 0 0 1 00 0 0 0 1编码后码元:coded =1 1 0 1 1 1 0 0 0 0 1 0 1 0 01 1 1 1 1 1 1 1 1 1 1 1 1 1 10 0 0 0 1 0 1 0 0 1 1 0 1 1 10 0 0 1 0 1 0 0 1 1 0 1 1 1 00 0 0 0 1 0 1 0 0 1 1 0 1 1 1 信道传输中干扰后,接收到的信息coder =1 1 0 1 1 1 0 0 0 0 1 0 1 0 11 1 1 1 0 0 1 1 1 1 1 1 0 1 10 0 0 0 1 0 1 1 0 1 1 0 1 1 10 0 1 1 0 1 1 0 1 0 0 1 1 1 00 0 1 1 1 0 1 0 0 1 1 0 1 1 1 解码后decode =1 1 0 1 11 1 1 1 10 0 0 0 10 0 0 1 00 0 0 0 1。

(7,4)循环码的编码和译码(精品WORD文档)

(7,4)循环码的编码译码编码的实验原理:根据循环码的代数性质建立系统编码的过程,可以把消息矢量用如下多项式表示:m(x) = m k」x k' + m k/X k,十…十m i x 十m°要编码成系统循环码形式,把消息比特移入码字寄存器的最右边k 位,而把监督比特加在最左边的n-k个中,则要用x n」乘以m(x)得到n _kx m(x)= mk」x n_l m k-2x n-2…m1x nJ^ 1m0x nJ<nx m(x)= q(x) g(x)+ p(x),其中p(x)可以表示为n _k _1 Er n -kp(x)= P n 上」X …Pi X P o ,贝y p(x)+ x m(x)nd 丄n _2 丄丄n _k H i 丄n _k n _k A= m k」x m k/x …mi x m o x + p n」_i x …pi x p o另U(x)= p(x)+ x m(x),贝卩U=( p o , p i , p2,•…,P n_k」,m o , m i,•…, m k 1 ) o本实验根据以上原理,用matlab实现书上例6.8系统形式的循环3码,生成多项式为g(x)= x x(7,4)循环码的编码的程序如下:clear;clc;a=[1 0 1 1];%高次项系数在前的生成多项式Gx=[1 0 1 1];%将数组a的高位依次放在数组Data的低位Data二zeros(1,7);Data(1)=a(4);Data(2)=a(3);Data(3)=a(2);Data(4)=a(1);%Data除以Gx得到余数Rx[Qx,Rx]=deconv(Data,Gx); b=Rx+Data; %将数组b 的高位放在后面c=b(1);b(1)=b(7);b(7)=c;c=b(2);b(2)=b(6);b(6)=c;c=b(3);b(3)=b(5);b(5)=c;%将数组b 校正for i=1:7if rem(abs(b(i)),2)==0b(i)=0;endendfor i=1:7if rem(abs(b(i)),2)==1b(i)=1;endenddisp(输入序列:');disp('编码输出序列:');b程序运行结果为:输入序列:a =110 0编码输出序列:b =10 1110 0改变输入序列a=[1 0 1 1],运行结果:输入序列:a =10 11编码输出序列:b =10 0 10 11运行结果的编码如下:译码的实验原理g(x)= 1 x x3,在(n, k)循环码中,由于g(x)能除尽,因此x n T可分解成g(x)和其他因式的乘积,记为x n V g(x)h(x)x n 1g (x)即 h (x) = x 4 X 2 X 〔则h *(x)=x 4 x 3 x 1,其中h *(x)式h(x)的逆多项式。

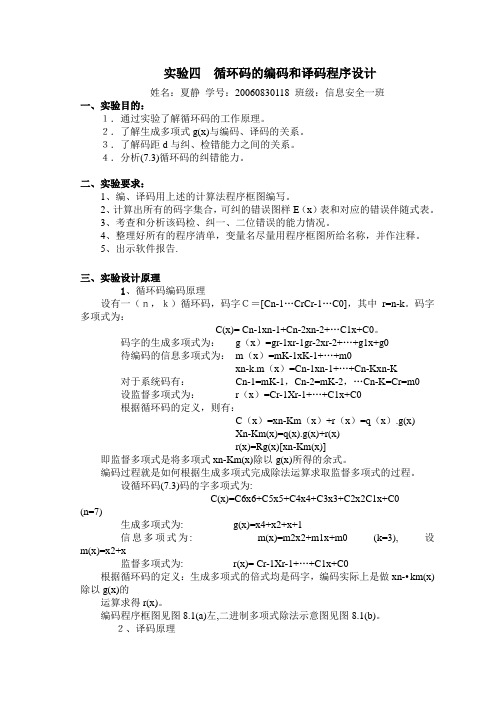

实验三 循环码的编码和译码程序设计

实验四循环码的编码和译码程序设计姓名:夏静学号:20060830118 班级:信息安全一班一、实验目的:1.通过实验了解循环码的工作原理。

2.了解生成多项式g(x)与编码、译码的关系。

3.了解码距d与纠、检错能力之间的关系。

4.分析(7.3)循环码的纠错能力。

二、实验要求:1、编、译码用上述的计算法程序框图编写。

2、计算出所有的码字集合,可纠的错误图样E(x)表和对应的错误伴随式表。

3、考查和分析该码检、纠一、二位错误的能力情况。

4、整理好所有的程序清单,变量名尽量用程序框图所给名称,并作注释。

5、出示软件报告.三、实验设计原理1、循环码编码原理设有一(n,k)循环码,码字C=[Cn-1…CrCr-1…C0],其中r=n-k。

码字多项式为:C(x)= Cn-1xn-1+Cn-2xn-2+…C1x+C0。

码字的生成多项式为:g(x)=gr-1xr-1gr-2xr-2+…+g1x+g0待编码的信息多项式为:m(x)=mK-1xK-1+…+m0xn-k.m(x)=Cn-1xn-1+…+Cn-Kxn-K 对于系统码有:Cn-1=mK-1,Cn-2=mK-2,…Cn-K=Cr=m0设监督多项式为:r(x)=Cr-1Xr-1+…+C1x+C0根据循环码的定义,则有:C(x)=xn-Km(x)+r(x)=q(x).g(x)Xn-Km(x)=q(x).g(x)+r(x)r(x)=Rg(x)[xn-Km(x)]即监督多项式是将多项式xn-Km(x)除以g(x)所得的余式。

编码过程就是如何根据生成多项式完成除法运算求取监督多项式的过程。

设循环码(7.3)码的字多项式为:C(x)=C6x6+C5x5+C4x4+C3x3+C2x2C1x+C0(n=7)生成多项式为: g(x)=x4+x2+x+1信息多项式为: m(x)=m2x2+m1x+m0 (k=3), 设m(x)=x2+x监督多项式为: r(x)= Cr-1Xr-1+…+C1x+C0根据循环码的定义:生成多项式的倍式均是码字,编码实际上是做xn-•km(x)除以g(x)的运算求得r(x)。

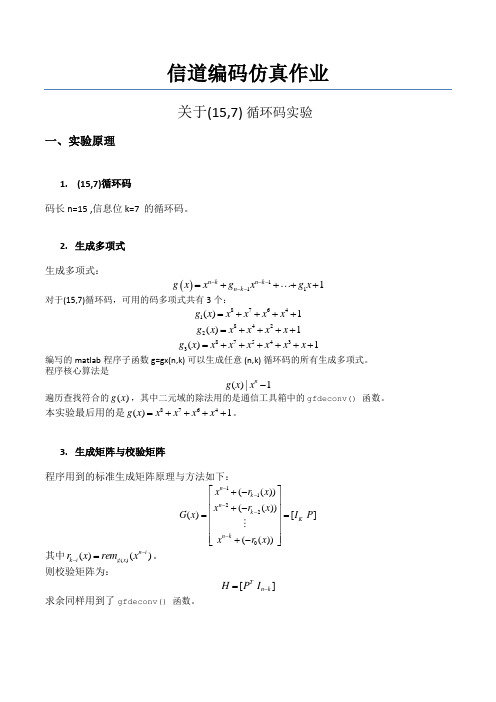

循环码matlab实验报告

信道编码仿真作业关于(15,7) 循环码实验一、实验原理1. (15,7)循环码码长 n=15 ,信息位 k=7 的循环码。

2. 生成多项式生成多项式:()1111n k n k n k g x x g x g x -----=++++对于(15,7)循环码,可用的码多项式共有3个: 87641()1g x x x x x =++++8422()1g x x x x x =++++875433()1g x x x x x x x =++++++编写的matlab 程序子函数 g=gx(n,k) 可以生成任意 (n,k) 循环码的所有生成多项式。

程序核心算法是()|1n g x x -遍历查找符合的()g x ,其中二元域的除法用的是通信工具箱中的 gfdeconv() 函数。

本实验最后用的是8764()1g x x x x x =++++。

3. 生成矩阵与校验矩阵程序用到的标准生成矩阵原理与方法如下:11220(())(())()[](())n k n k K n k x r x x r x G x I P x r x -----⎡⎤+-⎢⎥+-⎢⎥==⎢⎥⎢⎥⎢⎥+-⎣⎦其中()()()n i k i g x r x rem x --=。

则校验矩阵为:[]T n k H P I -=求余同样用到了gfdeconv() 函数。

4.最小距离与纠错能力通过校验矩阵H分析最小距离d,程序的算法是:取遍H的任意2列相加,若结果为0,则d=2;否则取遍H的任意3列相加,若结果为0,则d=3;以此类推,直到找到最小的d,使存在H的某d列相加结果为0。

5.编码器r级编码器采用g(x)k级编码器采用h(x).具体算法见之后的程序说明6. 译码器译码器为能纠正两个错误的梅吉特电路。

我分别编写了了2n 拍和3n 拍的译码电路,具体验证了修正线的作用。

7. 调制本实验所谓的调制只是将 1 变换为 -1,将 0 变换为 1。

循环码实验报告

基于MATLAB的循环码实验报告————————————————————————————————作者:————————————————————————————————日期:课程名称:信息论与编码课程设计题目:循环码的编码和译码程序设计指导教师:系别:专业:学号:姓名:合作者完成时间:成绩:评阅人:一、实验目的:1、通过实验了解循环码的工作原理。

2、深刻理解RS 码构造、RS 编译码等相关概念和算法。

二、实验原理1、RS 循环码编译码原理与特点设C 使某线性分组码的码字集合,如果对任C c c c C n n ∈=--),,,(021 ,它的循环移位),,,(1032)1(---=n n n c c c c C也属于C ,则称该码为循环码。

该码在结构上有另外的限制,即一个码字任意循环移位的结果仍是一个有效码字。

其特点是:(1)可以用反馈移位寄存器很容易实现编码和伴随式的计算;(2)由于循环码有很多固有的代数结构,从而可以找到各种简单使用的译码办法。

如果一个线性码具有以下的属性,则称为循环码:如果n 元组},,,{110-=n c c c c 是子空间S 的一个码字,则经过循环移位得到的},,,{201)1(--=n n c c c c 也同样是S 中的一个码字;或者,一般来说,经过j 次循环移位后得到的},,,,,,,{11011)(---+--=j n n j n j n j c c c c c c c 也是S 中的一个码字。

RS 码的编码系统是建立在比特组基础上的,即字节,而不是单个的0和1,因此它是非二进制BCH 码,这使得它处理突发错误的能力特别强。

码长:12-=mn信息段:t n k 2-= (t 为纠错符号数) 监督段:k n t -=2 最小码段:12+=t d最小距离为d 的本原RS 码的生成多项式为:g(x)=(x-α)(x -α2)(x -α3)…(x -αd -2) 信息元多项式为::m(x)=m0+m1x+m2x2+…+mk -1xk-1循环码特点有:1)循环码是线性分组码的一种,所以它具有线性分组的码的一般特性,且具有循环性,纠错能力强。

循环码二步大数逻辑译码原理实验

H a r b i n I n s t i t u t e o f T e c h n o l o g y信息论与编码实验报告实验名称:循环码二步大数逻辑译码原理实验院系:电子与信息工程学院通信工程系班级:10硕通信一班姓名:学号:设计时间:2010-11-20哈尔滨工业大学一、 实验内容已知一个(7,4)系统循环码的生成多项式为g x =x 3+x +1,设计基于此生成多项式的大数逻辑译码器。

二、 实验原理2.1 多项式的除法电路本实验的输入为串行数据,因而只考虑串行数据的除法电路。

假设多项式r x =r n x n +r n −1x n−1+⋯+r 1x +r 0,g x =g r x r +g r−1x r−1+⋯+g 1x +g 0,且有r ≤n ,则r x 除以g x 的除法电路的一般形式如图1。

图1多项式除法的一般电路图1中,输入序列按r n −1r n …r 0的顺序输入,右上方的输出为商多项式,待r 0输入结束后,各寄存器中的数据为余式多项式。

在二进制的情况下,模2加法等效于模2减法,且g x 的系数只可能为0或1,因而除法电路可进一步简化,例如,g x =x 3+x +1对应的除法电路如图2所示。

图2 除式为g x =x 3+x +1的除法电路在本实验中,只对余式感兴趣,在输入序列完毕后,余式为s x =s 2x 2+s 1x +s 0。

2.2 循环码的译码原理假设系统循环码的生成多项式为g x =g r x r +g r−1x r−1+⋯+g 1x +g 0,接收到的一组循环码字的多项式表示为r x =r n x n +r n −1x n−1+⋯+r 1x +r 0,则按照以下方法译码:i) 求r x 除以g x 的余式s x ,定义此余式为校验子多项式。

ii) 根据校验子多项多生成错误图样e x 。

iii) e x+r x=c x即为译码结果。

这里不讨论循环码的纠检错能力,(7,4)系统循环码可以纠正一位错。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

H a r b i n I n s t i t u t e o f T e c h n o l o g y信息论与编码实验报告实验名称:循环码二步大数逻辑译码原理实验院系:电子与信息工程学院通信工程系班级:10硕通信一班姓名:学号:设计时间:2010-11-20哈尔滨工业大学一、 实验内容已知一个(7,4)系统循环码的生成多项式为g x =x 3+x +1,设计基于此生成多项式的大数逻辑译码器。

二、 实验原理2.1 多项式的除法电路本实验的输入为串行数据,因而只考虑串行数据的除法电路。

假设多项式r x =r n x n +r n −1x n−1+⋯+r 1x +r 0,g x =g r x r +g r−1x r−1+⋯+g 1x +g 0,且有r ≤n ,则r x 除以g x 的除法电路的一般形式如图1。

图1多项式除法的一般电路图1中,输入序列按r n −1r n …r 0的顺序输入,右上方的输出为商多项式,待r 0输入结束后,各寄存器中的数据为余式多项式。

在二进制的情况下,模2加法等效于模2减法,且g x 的系数只可能为0或1,因而除法电路可进一步简化,例如,g x =x 3+x +1对应的除法电路如图2所示。

图2 除式为g x =x 3+x +1的除法电路在本实验中,只对余式感兴趣,在输入序列完毕后,余式为s x =s 2x 2+s 1x +s 0。

2.2 循环码的译码原理假设系统循环码的生成多项式为g x =g r x r +g r−1x r−1+⋯+g 1x +g 0,接收到的一组循环码字的多项式表示为r x =r n x n +r n −1x n−1+⋯+r 1x +r 0,则按照以下方法译码:i) 求r x 除以g x 的余式s x ,定义此余式为校验子多项式。

ii) 根据校验子多项多生成错误图样e x 。

iii) e x+r x=c x即为译码结果。

这里不讨论循环码的纠检错能力,(7,4)系统循环码可以纠正一位错。

根据第ii步所用的方法不同,循环码的译码方法有梅吉特译码、捕错译码及大数译码等方法。

2.3大数译码原理实际上,无论是梅吉特译码器,捕错译码器还是大数译码器,都用到了循环码的一个重要性质:如果s x为接收码字多项式r x的校验子多项式,则xs x[模g x]也必然是xr x[模x n+1]的校验子多项式。

每个校验子多项式对应一种错误图样。

循环码本身的定义就表明了xr x[模x n+1]也对应一个许用码字(在无错的情况下),这就意味着,如果一个校验子对应的错误图样可以纠正一位错,那么就可以通过上述运算纠正这个码字中的所有一位错的情况。

下面以本实验的实验内容来构造大数逻辑译码器。

(7,4)系统循环码的码字长度为7,收到的码字为r x。

错误图样e=[1000000]可以纠正码字r6,假设此错误图样对应的校验子多项式为s6x,则可以通过以下运算来纠正码字r5(假设只有一位错):i) 通过除法电路得到校验子多项式s x。

ii) 做运算s5x=xs x[模g x]。

iii) 如果s5x等于s6x,则证明码字r5有错,否则无错。

依照这样的方法可以依次纠正其余码字。

在图2中,当输入为零时,就相当进行了运算xs x[模g x]。

现在问题转化为,如何根据验子多项式为s6x纠正码字r6?亦即如何根据s6x的系数s0s1s2纠正码字r6?考虑循环码一致监督矩阵与校验子向量、错误图样之间的关系:S T=H R T=H E T式中S为校验子向量,H为监督矩阵,E错误图样向量。

生成多项式为g x=x3+x+1的一致监督矩阵为:H=1110100 0111010 1101001代入上式,并将S及E展开可得:s2s1 s0=111010001110101101001e6e5e4e3e2e1e0于是,得到以下关系式:s2=e6+e5+e4+e2s1=e5+e4+e3+e1s0=e6+e5+e3+e0记A11=s1+s0=e6+e4+e1+e0A12=s2=e6+e4+e5+e2A21=s2=e6+e5+e4+e2A22=s0=e6+e5+e3+e0上式中用到了模二加的性质e+e=0。

再记A1=A11 & A12=e6+e4A2=A21 & A22=e6+e5式中符号&表示与操作,并且假设e i,i=0…6最多只能有一位等于1,即接收码字只可能为无错或有一位错。

显然,只有当A1与A2均为1的情况下,可以知道e6=1,否则一定有e6=0,但不能确定e i,i=0…5的情况。

最后,结合图2的除法电路及上面的分析,可以得到生成多项式为g x=x3+x+ 1的(7,4)系统循环码的大数逻辑译码电路图,如图3所示。

图3 生成多项式为g x=x3+x+1的循环码大数逻辑译码电路图3中,各寄存器的初始状态为零,在前7个时钟周期,接收码字序列r6r5 0次进入系统,输出为7个零。

寄存器S0、S1、S2保存此时的校验子多项式的系数,如果A1、A2与操作结果为1,表明接收到的码字最高位即r6有错,在下一个时钟周期就可以对r6进行纠错。

在后7个时间周期,电路输入为7个零,输出为译码结果。

因此,整个系统需要14个时钟周期才能完成一个码字的译码。

因为经过两级逻辑运算才得到错误结果,因此称上面的电路为二步大数逻辑译码电路。

为了达到连续译码的目的,图中增加了虚线所示的反馈,在检测到错误后,这个反馈可以将寄存器S0、S1、S2清零,虚线只在后7个时钟周期有效。

此外需要说明的是寄存器D的作用:在第7个时钟周期后,A1、A2相与的结果已经出现,标志着r6的错误情况,但此时r6在7级移位寄存器中,因此将A1、A2相与的结果延时一个时钟周期方可正确译码。

另一种解决方法是将7级移位寄存器改为6级。

事实上,图3中,只有当S0=1,S1=0,S2=1时,组合逻辑电路部分才输出1,即有错误发生,如果将组合逻辑电路部分换为一个“101”识别器,就构成了梅吉特译码器。

三、实验环境及设计工具3.1 实验环境操作系统:Windows XP SP2简体中文版运行环境:.NET Framework 2.03.2设计工具本实验程序使用C#语言编写译码过程及交互界面,所用开发工具为SharpDevelop 3.2;使用gnuplot 4.4绘制码元的波形图。

四、设计方法4.1模块/单元设计二步大数逻辑译码器实验程序由三部分组成:界面及控制模块、译码器单元和波形生成模块。

各部分关系如图4。

图4 二步大数逻辑译码器实验程序组成由于采用了面向对象的设计方法,因而用类来描述程序更为方便。

图4中,界面显示及主控制对应的类为MainForm,除负责整个程序的逻辑控制外,还要读取用户输入的数据及指令、显示译码结果。

在良好的程序设计中各模块之间是松耦合的,为此,MainForm并不涉及对译码过程的任何操作,它将收到的码字R x传递给译码器单元执行,然后从译码器单元读取操作结果。

译码器单元对应的类为Decoder,该类完成(7,4)循环码序列的译码。

Decoder类存储译码过程中各寄存器及组合电路输出的状态,供MainForm类查询。

此外,MainForm 类每下一次译码指令,Decoder就进行一位码元的输入,也就对应时序电路中的一次时钟输入。

(7,4)循环码的一个码字长度为7,根据大数逻辑译码的电路原理图可知,在14个时间周期后,方可完成一个码字的译码,因而Decoder在接收14次指令后将标志本次结果有效。

波形生成器对应的类为GnuplotWrapper。

这个类对工具gnuplot进行简单的封装,根据输入的接收码字R x、译码结果C x及错误图样E x,生成二进制码元波形图,结果以png图形格式存储。

MainForm类负责显示该波形图。

4.2译码器单元设计译码器的工作过程为:接收任意长度的(7,4)循环码码字序列,在每7个码元后插入7个0码;然后,每接收到一条来自MainForm的译码指令,就将一位码元输入到程序所模拟的电路中;在第14个指令后,译码器修改其状态,表明此时一个码字译码完毕,结果有效。

图5 Decoder类的属性、方法图5给出了类Decoder的组成。

在这个类中,用整型变量模拟二进制码元0或1(C#语言中没有位类型)。

属性S0、S1、S2分别保存某一时刻寄存器S0、S1、S2的状态;属性A11、A12、A21、A22、A1、A2也分别对应第2.3节对校验子系数S0、S1、S2进行逻辑运算的结果;一个IsResultV alid属性指示当前结果是否有效。

Decoder类用先进先出(FIFO)的队列模拟移位寄存器,输入和输出也可以用移位寄存器来保存数据,因此输入与输出也有相应的队列。

队列的操作包含入列和出列,这两个操作的组合就可以模拟移位寄存器的一次移位操作。

buffer队列保存图3中7级移位寄存器的值;currentCode保存当前正在被翻译的码字;receivedCode保存输入的任意长度的码字序列;result队列保存译码结果;error队列保存错误图样。

Decoder类的方法包括Received,reset,Next和Calculate,最后一个Decoder为构造函数。

本程序的核心方法为Next与Calculate,两者的联合工作流程如图6所示,它对应2.3节讨论的译码过程。

图5 Decoder类的译码过程流程图Calculate方法中进行译码运算,Next方法维护一个计数器,也维护一个状态来指示当前译码的阶段。

本程序将译码过程分为两个阶段,第一个阶段为Buffering阶段,此时输入为接收码元,输出为零,且无反馈输入;第二个阶段为Decoding阶段,此时输入为零,且有反馈输入,输出为译码结果。

4.3界面设计界面使用Windows Forms框架设计,如图6所示。

用户输入接收到的循环码字序列,然后点击“开始译码”开始单步译码。

左方显示各寄存器级组合电路的状态,在译码完成后,右下方显示接收码字、译码结果及错误情况的波形图。

本实验程序支持连续译码。

图6 循环码译码实验程序界面五、部分程序代码5.1Decoder类源代码1using System;2using System.Collections.Generic;34namespace CCDecoder5{6/// <summary>7/// (7,4)循环码二步大数逻辑译码器,可连续译码8/// </summary>9public class Decoder10{11#region constructors12public Decoder() { }13#endregion1415#region properties16public Queue<int> receivedCode{private set;get;}//接收到的码字,长度可大于7 17public Queu e<in t> buffe r{private se t;ge t;} //7级移位寄存器18public Queue<int> result{private set;get;} //译码结果,长度为719public Queue<int> error{private set;get;} //错误图样,长度为720public Queue<int> currentCode{private set;get;}//当前被译的码字,长度为7 21public bool IsResultValid{private set;get;} //C(x),E(x)有效标志22public int S0 {private set;get;} //寄存器S023public int S1 {private set;get;} //寄存器S124public int S2 {private set;get;} //寄存器S225public int A11 {private set;get;} //A11=S1'+S0'26public int A12 {private set;get;} //A12=S2'27public int A21 {private set;get;} //A21=S2'28public int A22 {private set;get;} //A22=S0'29public int A1 {private set;get;} //A1=A11+A1230public int A2 {private set;get;} //A2=A21+A2231#endregion3233#region private fields34int counter; //内部计数器35DecodingPhase phase; //当前译码的状态,分为两个阶段:Buffering和Decoding 36#endregion3738#region public methods39public void reset() //程序复位,将各个寄存器及中间结果清零40{41counter = 0;42IsResultValid = false;43receivedCode = new Queue<int>();44currentCode = new Queue<int>();45result = new Queue<int>(new int[]{0,0,0,0,0,0,0});46error = new Queue<int>(new int[]{0,0,0,0,0,0,0});47buffer = new Queue<int>(new int[]{0,0,0,0,0,0,0});48A11 = 0;49A12 = 0;50A21 = 0;51A22 = 0;52A1 = 0;53A2 =0;54S0 = 0;55S1 = 0;56S2 = 0;57}5859public bool Next() //进行一次译码操作60{61counter = counter + 1;6263if (counter == 1)64{65IsResultValid = false;66currentCode.Clear();67}6869if (counter <= 7) //译码第一阶段:Buffering70{71phase = DecodingPhase.Buffering;72if (receivedCode.Count == 0) return false; //译码完毕73}74else //译码第二阶段:Decoding75{76phase = DecodingPhase.Decoding;77}78Calculate(receivedCode.Dequeue());7980if (counter == 14) //译完一个码字,标志结果有效81{82counter = 0;83IsResultValid = true;84}85return true;86}8788public void Received(List<int> Code) //接收到码字,进行初始化处理89{90reset();91receivedCode=new Queue<int>();92int i;93for(i=0;i<Code.Count;i++) //在每7个码元后添加7个零94{95if(i!=0 && i%7==0)96for(int j=0;j<7;j++) receivedCode.Enqueue(0);97receivedCode.Enqueue(Code[i]);98}99if(i!=0 && i%7==0)100for(int j=0;j<7;j++) receivedCode.Enqueue(0);101}102103private void Calculate(int input) //一个时钟周期所需要的操作104{105int S0_p,S1_p,S2_p,E_p; //暂存S0,S1,S2,A1&A2的值106107S0_p = S0;108S1_p = S1;109S2_p = S2;110E_p = A1 & A2;111112if(phase == DecodingPhase.Buffering)113{114S0 = input ^ S2_p; //在Buffering阶段115currentCode.Enqueue(input); //S0=input+S2'116}117else118{ //在Decoding阶段119S0 = S2_p ^ E_p; //S0=S2+(A1+A2)120}121122S1 = S0_p ^ S2_p; //S1=S0'+S2'123S2 = S1_p; //S2=S1'124A11 = S1 ^ S0; //A11=S1'+S0'125A12 = S2; //A12=S2'126A21 = S2; //A21=S2'127A22 = S0; //A22=S0'128A1 = A11 & A12; //A1=A11+A12129A2 = A21 & A22; //A2=A21+A22130131buffer.Enqueue(input); //7级移位寄存器移出一位码元132result.Enqueue(buffer.Dequeue() ^ E_p);//移出的码元与(A1+A2)模2加133result.Dequeue();134error.Enqueue(E_p); //错误图样寄存器移入一位码元135error.Dequeue(); //错误图样寄存器移出一位码元136}137#endregion138139public enum DecodingPhase{Buffering,Decoding}140}141}5.2GnuplotWrapper类源代码1using System;2using System.IO;3using System.Collections.Generic;4using System.Diagnostics;56namespace CCDecoder7{8/// <summary>9/// gnuplot封装类10/// </summary>11public class GnuplotWrapper12{13public GnuplotWrapper(Decoder decoder)14{15this.decoder=decoder;16}1718private Decoder decoder;1920public string GetImagePath() //获取所生成图形的文件名21{22GenerateDataFile(); //生成波形图23Process process=new Process();24process.StartInfo.FileName=@"gnuplot\gnuplot.exe";25process.StartInfo.Arguments="script.txt";26process.Start();27process.WaitForExit();28return "result.png";29}3031private void GenerateDataFile()32{33List<int> code=new List<int>(decoder.currentCode);34List<int> result=new List<int>(decoder.result);35List<int> error=new List<int>(decoder.error);3637using(StreamWriter sw=new StreamWriter("data.txt",false)) 38{39sw.Write("{0} {1} {2}\n\r",code[0].ToString(),result[0].ToString(),error[0].ToString()); //写入文件40for(int i=0;i<7;i++)41{42sw.Write("{0} {1}{2}\n\r",code[i].ToString(),result[i].ToString(),error[i].ToString());43}44}45}46}47}5.3Gnuplot生成波形所用的脚本1#Gnuplot生成码元图形的脚本2reset3set terminal png #设置输出格式为png图形格式4set output "result.png" #设置输出文件名为result.png5set multiplot6set noborder7set grid xtics8set size 1,0.3333910#画R(x)波形图11set origin 0.0,0.666612unset label13unset key14set ylabel "R(x)"15set ytics 0,1,116set xtics ("" 0,"" 1,"" 2,"" 3,"" 4,"" 5,"" 6,"" 7)17plot "data.txt" using 1 linetype 7 linewidth 4 with fsteps1819#画C(x)波形图20set origin 0.0,0.333321unset label22unset key23set ytics 0,1,124set ylabel "C(x)"25plot "data.txt" using 2 linetype 10 linewidth 4 with fsteps2627#画E(x)波形图28set origin 0.0,0.029unset label30unset key31set ytics 0,1,132set ylabel "E(x)"33plot "data.txt" using 3 linetype 11 linewidth 4 with fsteps3435unset multiplot36reset六、运行结果6.1R x无错的测试码字0011101及0001011都是本实验所用的(7,4)循环许用码字,其输出结果如图7所示。