K-SYNC同步器使用说明

同步控制器使用手册

安全须知无论在任何情况下,如操作、清洁或保养,请务必遵守以下所规定的安全守则,若有因违反,而造成超出原设计、制造的安全顾虑,本公司将不予以负责。

当地若另有其它的安全规范,则请一起遵守。

警告:请在本设备允许的操作和储存环境条件下使用。

·任何情况下,无专业人员指导,切勿拆卸或碰触内部零部件;·维修设备时,严禁带电操作;·切勿使金属、液体等异物掉入设备内,以免设备损坏;·设备安装尽量远离干扰源(例如:接触器、变频器等)或采取相应的屏蔽措施;·信号线、电源线最好分开走线,以免产生干扰;·本设备与接触器不可共享一个电源,否则会有干扰产生;·本设备专门为本公司生产的VFD系列变频器配套使用而设计,使之能够发挥最佳性能,但不能保证与其它品牌变频器的匹配。

储存本品在安装之前必须置于其包装箱内,若该机暂不使用,为了使该品能够在本公司的保修范围内以及日后的维护,储存时务必注意下列事项:☞必须置于无尘垢、干燥之位置。

☞储存位置的环境温度必须在0℃到+65℃范围内。

☞储存位置的相对湿度必须在5%到90%范围内,且无结露。

☞避免储存于含有腐蚀性气、液体之环境中。

☞最好适当包装并存放在架子或台面上。

操作环境☞环境温度0℃-+50℃,若环境温度超过40℃以上时,请置于通风良好之场所。

☞相对湿度15%-+95%RH,避免安装与任何发生结露、冰冻或要接触任何液体之场所。

☞不要安装一任何有以下情况的场所:阳光直晒、浓灰尘、腐蚀性气体或油雾、易燃性气体、液体。

☞震动小于5.9米/妙(0.6g)。

SLC系列同步控制器拥有完善的功能,在技术上处于国内领先水平,在性能上可与国外同类产品相媲美。

广泛适用于由多台调速系统组成的各种机械设备上,如电力、钢铁、造纸、纺织、印染、电缆光纤、塑料等行业。

可对线速度、位移、张力、距离等进行控制,是机器设备的最佳选择。

一、型号说明SLC 04C22 (A)B 为反馈电压为0-10VA 为反馈电压为±5V控制器输出路数4路控制器系列号1、主要特点A、数字化SLC04C22A(B)控制器采用单片计算机控制,可对控制器进行多种参数设置,设置参数时通过数码显示。

同步器使用技巧

第二篇:提高篇第六章:同步器使用技巧本书已经介绍过同步器的作用和使用方法,这里详细介绍同步器的使用技巧。

第一节:同步器的应用范围操作同步器可以达到和操作网络表相同的效果,就是通过同步器,把原理图元件对应的封装放置到PCB图里,并且相同的网络用网络线表示连接,根据这些网络线,就可以自动布线或者手工布线。

1、网络表生成的网络名称是顺序编号的网络名称,同步器生成的网络名称是以管脚号为基础的网络名称,这两种不同的网络名称可以达到相同的自动布线或者手工布线效果。

2、引入网络表放置的PCB元件是堆在一起的,还需要弹开元件的操作,降低了绘图速度,用同步器放置的PCB元件是顺序排列的,这就加快了绘图速度。

3、同步器生成网络有两种方法,一种是更新放置,一种是更新添加,下面就以电路图1.sch为例,介绍同步器生成网络的两种方法:更新放置,是指绘制好原理图之后,原理图元件也添加了对应PCB的封装,PCB文件里没有元件,在原理图里执行菜单命令Design设计/Update Pcb更新PCB,弹出更新设计的同步器对话框,用鼠标点Preview Changes按钮,这时候的更新设计的信息如图6-1-1,更新添加是指绘制好原理图之后,原理图元件添加了对应PCB的封装,PCB文件里已经放置了原理图元件对应的PCB 的封装,这时候在原理图里更新PCB会弹出如图6-1-2的元件匹配对话框,用鼠标点Apply(应用)按钮,弹出更新设计的同步器对话框,用鼠标点Execute按钮就可以添加网络。

第二节:同步器的使用原理在原理图方面,只要原理图里有元件,不管这个元件是从元件库管理器里放置的还是直接从库里放置的,或者从别的图纸复制来的,只要原理图元件添加了该元件对应的PCB 正确的封装,就可以进行同步设计了。

在PCB方面,如果是用同步器放置原理图元件对应的PCB封装,这个封装在当前使用的库里必须有这个元件,新自制的元件必须在元件库管理器里看到这个元件,这一点很容易忽视,使得刚自制好的元件一使用同步器就出错,解决的方法很简单,在自制完原理图元件或者PCB元件保存元件之后,回到原理图或PCB图文件,用鼠标点一下自制元件所在的库名称,自制的元件就出现在库管理器里了,这个操作相当于确认新自制的元件。

【2017年整理】英博BKR简单操作说明

英博BKR-12T型补偿控制器简单操作说明⏹菜单界面介绍控制器液晶屏最上部左上角显示目标功率因数值,i代表感性,c代表容性;右上角区显示☺则表示预设正确(功能正确),显示☹则表示有异常,需检查原因。

控制器液晶屏左右两侧垂直四方条显示电容步数,即每路电容投切情况,左侧从上至下是1~6路,右侧从上到下是7~12路,当该路电容投入时对应路会反显(该区域变黑)。

控制器液晶屏中央是控制器菜单、设置、测量值的主显示区,全为英文显示,选择进入相应的菜单会有相应的显示或设定,手动投切、参数设置、测量数值等都能从本区看到。

控制器液晶屏最下部是菜单导航功能符号,▲/▼表示上翻/下翻菜单,►表示进入子菜单,◄表示退出子菜单,◄►表示更改设置,+/-表示增加/减小选定参数值,回车键表示确认或保存值。

⏹菜单设置MEASUREMENT V ALUES---------显示测量值(参数)在液晶屏上简写为“MEAS.V ALUES”;HARMONICS----------显示谐波测量值;STEPINFO--------------显示关于电容器步的信息(每步电容设置参数值);SETUP-------------------显示控制器设置,需密码进入:密码为:2402(升级版本以后的不需密码) DEVICE INFO---------显示控制器信息,如控制器类型、版本等。

如需选择进入控制器设置,通过按▲/▼来翻动主菜单,使左右箭头指中的即 >SETUP<时即为选中SETUP 菜单,再按►即进入该子菜单,会提示输入密码,除了SETUP需要密码,其余菜单不需要输入密码,特别说明:在之后的新版本中,进入SETUP也不需要输入密码,直接进入即可。

◆MEASUREMENT V ALUES测量值:按▲/▼键选择值,测量值会依次显示出来,可显示ULL、ULN、THD OF Voltage、P、Q、S、F、I、等等。

◆HARMONICS谐波值:按◄►键切换不同显示值,按▲/▼键翻动菜单,可依次查看跟谐波有关数值。

键盘鼠标同步器怎么用

键盘鼠标同步器怎么用有许多网友为了工作或者游戏需要,购买了键盘鼠标同步器,但却不知道怎么使用。

没关系,小编在这里为大家详细讲解键盘鼠标同步器的使用方法。

一.简介键盘鼠标同步器主要实现将键盘鼠标信号同步的传输到各个受控的计算机,为了保证数据同步性,以纯硬件的方式将键盘鼠标并行发送到受控的计算机,达到精确的同步效果。

同步器支持PS2键盘鼠标输入,USB信号输出,USB输出接到各个受控计算机,受控计算机可以独立的关机,冷启,热启。

同步器电源直接由计算机提供,同步器在使用时不需要安装任何额外的软件或驱动。

同步器键盘支持连发功能,可以同时设置小于7个连发键。

支持键盘的两种切换功能,通过切换,可以实现控制任意单台或几台计算机。

同步器鼠标支持三种工作模式。

安装方法:请务必按照这个顺序安装开机状态--》必须先连接键鼠到同步器--》最后再连接同步器到电脑二.键盘功能:切换功能一这种方式切换可以实现任一台可控电脑有效,或全部都有效。

切换方法:小键盘上的*按键盘+ 小键盘上的0-6 (以一控六为例) 按住小键盘上的* 键,再按一下小键盘上的 1键,切换到第一台电脑,键盘鼠标只对第一台电脑有效。

按住小键盘上的* 键,再按一下小键盘上的 2键,切换到第一台电脑,键盘鼠标只对第二台电脑有效。

按住小键盘上的* 键,再按一下小键盘上的 3键,切换到第一台电脑,键盘鼠标只对第三台电脑有效。

按住小键盘上的* 键,再按一下小键盘上的 4键,切换到第一台电脑,键盘鼠标只对第四台电脑有效。

按住小键盘上的* 键,再按一下小键盘上的 5键,切换到第一台电脑,键盘鼠标只对第五台电脑有效。

按住小键盘上的* 键,再按一下小键盘上的 6键,切换到第一台电脑,键盘鼠标只对第六台电脑有效。

按住小键盘上的* 键,再按一下小键盘上的0 键,键盘鼠标对所有电脑都有效。

注:切换时可以看对应的指示灯,对应路的指示灯点亮的电脑控制有效。

c. 切换功能二(此功能专门用户才有!)这种方式切换可以实现控制任意接入的多台电脑同步控制,可以配合切换功能一,灵活控制多台电脑同步。

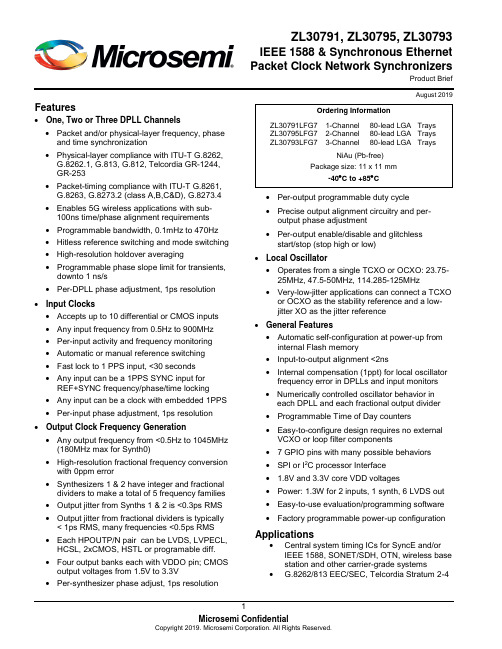

ZL系列Sync网络同步器产品简介说明书

ZL30791, ZL30795, ZL30793IEEE 1588 & Synchronous EthernetPacket Clock Network SynchronizersProduct BriefAugust 2019 Features•One, Two or Three DPLL Channels•Packet and/or physical-layer frequency, phaseand time synchronization•Physical-layer compliance with ITU-T G.8262,G.8262.1, G.813, G.812, Telcordia GR-1244,GR-253•Packet-timing compliance with ITU-T G.8261,G.8263, G.8273.2 (class A,B,C&D), G.8273.4•Enables 5G wireless applications with sub-100ns time/phase alignment requirements •Programmable bandwidth, 0.1mHz to 470Hz•Hitless reference switching and mode switching •High-resolution holdover averaging•Programmable phase slope limit for transients, downto 1 ns/s•Per-DPLL phase adjustment, 1ps resolution•Input Clocks•Accepts up to 10 differential or CMOS inputs•Any input frequency from 0.5Hz to 900MHz•Per-input activity and frequency monitoring•Automatic or manual reference switching•Fast lock to 1 PPS input, <30 seconds•Any input can be a 1PPS SYNC input for REF+SYNC frequency/phase/time locking •Any input can be a clock with embedded 1PPS •Per-input phase adjustment, 1ps resolution•Output Clock Frequency Generation•Any output frequency from <0.5Hz to 1045MHz (180MHz max for Synth0)•High-resolution fractional frequency conversion with 0ppm error•Synthesizers 1 & 2 have integer and fractional dividers to make a total of 5 frequency families •Output jitter from Synths 1 & 2 is <0.3ps RMS •Output jitter from fractional dividers is typically < 1ps RMS, many frequencies <0.5ps RMS •Each HPOUTP/N pair can be LVDS, LVPECL, HCSL, 2xCMOS, HSTL or programable diff.•Four output banks each with VDDO pin; CMOS output voltages from 1.5V to 3.3V•Per-synthesizer phase adjust, 1ps resolution•Per-output programmable duty cycle•Precise output alignment circuitry and per-output phase adjustment•Per-output enable/disable and glitchlessstart/stop (stop high or low)•Local Oscillator•Operates from a single TCXO or OCXO: 23.75-25MHz, 47.5-50MHz, 114.285-125MHz •Very-low-jitter applications can connect a TCXO or OCXO as the stability reference and a low-jitter XO as the jitter reference•General Features•Automatic self-configuration at power-up from internal Flash memory•Input-to-output alignment <2ns•Internal compensation (1ppt) for local oscillator frequency error in DPLLs and input monitors •Numerically controlled oscillator behavior in each DPLL and each fractional output divider •Programmable Time of Day counters•Easy-to-configure design requires no external VCXO or loop filter components•7 GPIO pins with many possible behaviors•SPI or I2C processor Interface• 1.8V and 3.3V core VDD voltages•Power: 1.3W for 2 inputs, 1 synth, 6 LVDS out •Easy-to-use evaluation/programming software •Factory programmable power-up configuration Applications•Central system timing ICs for SyncE and/or IEEE 1588, SONET/SDH, OTN, wireless basestation and other carrier-grade systems •G.8262/813 EEC/SEC, Telcordia Stratum 2-4Ordering InformationZL30791LFG7 1-Channel 80-lead LGA TraysZL30795LFG7 2-Channel 80-lead LGA TraysZL30793LFG7 3-Channel 80-lead LGA TraysNiAu (Pb-free)Package size: 11 x 11 mm-40︒C to +85︒C1. Block DiagramFigure 1 - Functional Block Diagram2. Application ExampleFigure 2 - Synchronous Ethernet and IEEE 1588 Central Timing ApplicationPACKET_REF[2:0]Register A ccessFracDiv IntDiv FracDivIntDivHP Synthesizer 2low-jitterHPOUT6P HPOUT6N HPOUT7P HPOUT7NDIVREF0P DPLL0R S T _BC S _B _A S E L 0S C K _S C LS O _A S E L 1S I _S D AG P I O [8:0]Microprocessor Port SPI or I2C I/F & GPIO Pins One Diff / Two Single-Ended REF0N REF1P One Diff / Two Single-Ended REF1N REF2P One Diff / Two Single-EndedREF2NREF3P One Diff / Two Single-Ended REF3N REF4P One Diff / Two Single-EndedREF4NReference Monitors & State MachinesDPLL1DPLL2HP Synthesizer 1low-jitterGP Synthesizer 0general purpos eGPOUT0GPOUT1DIV DIVXO Optional x2O S C IO S C OMaster Clock M C L K I N _PDIVHPOUT4P HPOUT4N HPOUT5P HPOUT5N DIV DIVHPOUT0P HPOUT0N HPOUT1P HPOUT1N DIVDIV HPOUT2P HPOUT2N HPOUT3P HPOUT3NDIVDIVM C L K I N _NS R S T _BGPS (1PPS)BITS/SSU Line Extracted Clocks[7:0]TCXODPLL0T4 pathSynth01.544 or2.048MHz CMOS to BITS/SSU1 PPSDPLL1SyncESynth12x 156.25MHz 2x 125MHz155.52MHz, 161.1328125MHz or other frequencyDPLL21588Control info from IEEE 1588 algorithmSynth225MHz 1 PPS or clock w/ embedded PPS 1588 signals to system componentsSyncE signals to system componentsto BITS/SSU systemDPLL1 only present on ZL30795 and ZL30793 DPLL2 only present on ZL307933. Detailed Features3.1 Input Block Features•Ten input reference pins; each can accept a CMOS signal or the POS side of a differential pair; or two can be paired to accept both sides of a differential pair•Any input can be a SYNC signal for REF+SYNC frequency/phase/time locking•Any input can be a clock signal with embedded PPS signal (duty cycle distortion indicates PPS location) •Input clocks can be any frequency from 0.5Hz up to 900MHz (180MHz max for CMOS inputs)•Supported telecom frequencies include PDH, SDH, Synchronous Ethernet, OTN, wireless•Inputs constantly monitored by programmable frequency and single-cycle monitors•Single-cycle monitor can quickly disqualify a reference when measured period is incorrect•Frequency measurement (ppb or Hz) and monitoring (coarse, fine, and frequency-step monitors)•Optional input clock invalidation on GPIO assertion to react to LOS signals from PHYs•Input-to-input phase measurement, 1ps resolution•Input-to-DPLL phase measurement, 1ps resolution•Per-input phase adjustment, 1ps resolution3.2 DPLL Features•One, two or three full-featured DPLLs•Very high-resolution DPLL architecture•State machine automatically transitions among freerun, tracking and holdover states•Revertive or nonrevertive reference selection algorithm•Programmable bandwidth from 0.1mHz to 470Hz•Less than 0.1dB gain peaking•Fast frequency/phase/time lock capability for 1PPS or clock+1PPS input references•Programmable phase-slope limiting (PSL)•Programmable frequency rate-of-change limiting (FCL)•Programmable tracking range (i.e. hold-in range)•Truly hitless reference switching and mode switching•Physical-to-physical reference switching•Physical-to-packet reference switching•Packet-to-physical reference switching•Packet-to-packet reference switching•Per-DPLL phase adjustment, 1ps resolution•High-resolution frequency and phase measurement•Fast detection of input clock failure and transition to holdover mode•High-resolution holdover frequency averaging, better than 0.01ppb when using <10mHz filter•Time-of-Day registers: 48-bit seconds, 32-bit nanoseconds, writeable on input PPS edge3.3 Synthesizer Features•Any-to-any frequency conversion with 0ppm error•Two low-jitter synthesizers (Synth1, Synth2) with very high-resolution fractional scaling (i.e. non-integer multiplication)•Two output dividers per low-jitter synthesizer: one integer (4 to 15 plus half divides 4.5 to 7.5) and one 40-bit fractional•One general-purpose synthesizer (Synth0)• A total of five output frequency families•Easy-to-configure, completely encapsulated design requires no external VCXO or loop filter components3.4 Low-Jitter Output Clock Features•Up to 16 single-ended outputs (up to 8 differential outputs) from Synth1 and Synth2•Each output can be one differential output or two CMOS outputs•Output clocks can be any frequency from 1Hz to 1045MHz (250MHz max for CMOS and HSTL outputs)•Output jitter from Synth1 and Synth2 integer dividers is <0.3ps RMS•Output jitter from fractional dividers is <1ps RMS, many frequencies <0.5ps RMS•In CMOS mode, the HPOUTxN frequency can be an integer divisor of the HPOUTxP frequency (Example 1: HPOUT3P 125MHz, HPOUT3N 25MHz. Example 2: HPOUT2P 25MHz, HPOUT2N 1Hz) •Outputs directly interface (DC coupled) with LVDS, LVPECL, HSTL, HCSL and CMOS components •Supported telecom frequencies include PDH, SDH, Synchronous Ethernet, OTN•Can produce clock frequencies for microprocessors, ASICs, FPGAs and other components•Can produce PCIe clocks•Sophisticated output-to-output phase alignment•Per-synthesizer phase adjustment, 1ps resolution•Per-output phase adjustment•Per-output duty cycle / pulse width configuration•Per-output enable/disable•Per-output glitchless start/stop (stop high or low)3.5 General-Purpose Output Clock Features•Two CMOS outputs from Synth0•Any frequency from 0.5Hz to 180MHz•Output jitter is typically 20-30ps•Useful for applications where the component or system receiving the signal has low bandwidth such asa central timing IC•Can output a clock signal with embedded PPS (ePPS) (duty cycle distortion indicates PPS location) 3.6 Local Oscillator•Operates from a single TCXO or OCXO. Acceptable frequencies: 23.75MHz to 25MHz, 47.5MHz to 50MHz, 114.285MHz to 125MHz. Best jitter: ≥48MHz.•Very-low-jitter applications can connect a TCXO or OCXO (any frequency, any output jitter) as the stability reference and a low-cost low-jitter XO as the jitter reference•This ability to have separate jitter and stability references greatly reduces the cost of the TCXO or OCXO (no jitter requirement, no high-frequency-requirement) and allows reuse of already-qualifiedTCXO and OCXO components3.7 General Features•Automatic self-configuration at power-up from internal Flash memory•Input-to-output alignment <200ps with external feedback•Fast REF+SYNC locking for frequency and 1PPS phase alignment with lower-cost oscillator•Generates output SYNC signals: 1PPS (IEEE 1588), 2kHz or 8kHz (SONET/SDH) or other frequency •JESD204B clocking: device clock and SYSREF signal generation with skew adjustment•Internal compensation for local oscillator frequency error in DPLLs and input monitors, 1ppt resolution •Numerically controlled oscillator (NCO) behavior allows system software to steer DPLL frequency or fractional output divider frequency with resolution better than 0.005ppt•Spread-spectrum modulation available in each fractional output divider (PCIe compliant)•Seven general-purpose I/O pins each with many possible status and control options•SPI or I2C serial microprocessor interface3.8 Evaluation Software•Simple, intuitive Windows-based graphical user interface•Supports all device features and register fields•Makes lab evaluation of the device quick and easy•Generates configuration scripts to be stored in internal Flash memory•Generates full or partial configuration scripts to be run on a system processor•Works with or without an evaluation board4. Software FeaturesThe following figure shows the Time Synchronization Algorithm system environment. The subsections below list the features of the Time Synchronization Algorithm.Host ProcessorTransport Layer ProtocolsMicrosemi ZLS30390IEEE 1588-2008Protocol EngineMicrosemi ZLS30380Time Sync AlgorithmMicrosemiPLLSyncE/Stratum 3/GNSS/IEEE 1588Microsemi Ethernet MAC & PHY(Timestamp)Operating SystemApplication LayerControl, Configuration, Stats & AlarmsPacket NetworkClockPPSTimestamp Reference Clock4.1 Time Synchronization AlgorithmThe Time Synchronization Algorithm is responsible to accurately synchronize the local clock to a selected Server. The Time Synchronization Algorithm is synchronizing the Client to the Server to meet a variety of specifications or applications related to frequency accuracy (FFO), frequency (MTIE, TDEV), phase (1 Hz or 1PPS) and time (UTC & GNSS/GPS).The Time Synchronization Algorithm can run on a variety of host processor architectures, whether embedded into an SoC or on a dedicated small scale CPU (such as Microsemi’s SmartFusion2 SoC FP GA). The Time Synchronization Algorithm will interconnect with a wide array of software-programmable clock generators (such as Microsemi’s Network Synchronizer PLLs), protocol engines (such as Microsemi’s ZLS30390 IEEE 1588-2008 Protocol Engine) and underlying Ethernet MACs and PHYs that perform hardware timestamping.4.2 End Application Target PerformanceThe Time Synchronization Algorithm is suitable for many end application targets, including:• Frequency offset accuracy performance for GSM, WCDMA-FDD, LTE-FDD femtocell, small cell (residential, urban, rural, enterprise), picocell and macrocell applications, with target performance less than ± 15 ppb• Frequency performance for ITU-T G.823 and G.824 synchronization interface, as well as G.8261 PNT EEC, PNT PEC and CES interface specifications•Phase Synchronization performance for WCDMA-TDD, Mobile WiMAX, TD-SCDMA, CDMA2000, LTE-TDD, LTE-A, LTE-A Pro and 5G NR femtocell, small cell (residential, urban, rural, enterprise), picocell and macrocell applications with target performance less than ± 1 μs phase alignment •Time Synchronization for TAI, UTC-traceability and GNSS/GPS replacement4.3 Packet NetworksThe Time Synchronization Algorithm is suitable for high performance over a variety of packet networks including:• ITU-T G.8261 Appendix VI• ITU-T G.8261.1 network limit compliant• ITU-T G.8271.1 network limit compliant without SyncE •ITU-T G.8271.2 network limit compliant•Native Ethernet (switched) & IP (routed) networks•xDSL•Microwave•Fully aware, partially aware and unaware timing supported networks•Networks including intermediate Boundary Clocks and Transparent Clocks•Networks with and without SyncE or frequency physical layer support4.4 Clock SpecificationsThe Time Synchronization Algorithm meets the performance requirements from ITU-T packet clock specifications, or draft packet clock specifications, including:•ITU-T G.8261 Appendix VI•ITU-T G.8263 PEC-S•ITU-T G.8273.2 T-BC full on-path without SyncE•ITU-T G.8273.2 T-BC full on-path with SyncE•ITU-T G.8273.2 T-TSC full on-path without SyncE•ITU-T G.8273.2 T-TSC full on-path with SyncE•ITU-T G.8273.4 T-BC-A (draft)•ITU-T G.8273.4 T-BC-P (draft)•ITU-T G.8273.4 T-TSC-A (draft)•ITU-T G.8273.4 T-TSC-P (draft)4.5 ProfilesThe Time Synchronization Algorithm is suitable for use in a wide variety of markets and applications, including the following IEEE 1588-2008 Profiles:•IEEE 1588 Annex J.3 Delay Request-Response Default Profile (2008)•IEEE 1588 Annex J.4 Peer-to-peer Default Profile (2008)•ITU-T G.8265.1 Telecom Profile for Frequency Synchronization (Edition 1)•ITU-T G.8275.1 Telecom Profile for Phase with Full Timing Support Networks (Edition 1)•ITU-T G.8275.1 Telecom Profile for Phase with Full Timing Support Networks (Edition 2)•ITU-T G.8275.2 Telecom Profile for Phase with Partial Timing Support Networks (Edition 1)•CableLabs CM-SP-RDTI Remote DTI Profile (Edition I0x)•AES 67 Standard for Audio Applications of Networks – High-Performance Streaming Audio-over-IP interoperability: PTP Profile for Media Applications•SMPTE 2095-2 Profile for Use of IEEE-1588 Precision Time Protocol in Professional Broadcast Applications•AES R16 Project Report – PTP parameters for AES67 and SMPTE ST 2059-2 interoperability•IEEE C37.238 Standard Profile for Use of IEEE 1588 Precision Time Protocol in Power System Applications (Edition 2011)•IEEE C37.238 Standard Profile for Use of IEEE 1588 Precision Time Protocol in Power System Applications (Edition 2017)•IEC 61850-9-3 Precision time protocol profile for power utility automation (Edition 1.0)•IEC 62439-3 PTP profiles for high-availability automation networks (Edition 3.0)•IEEE802.1as AVB-TSN gPTP•IEEE 1588-2018 Annex J.5 High Accuracy Profile (based on White Rabbit)•IETF TICTOC Enterprise Profile4.6 Monitoring & RedundancyThe Time Synchronization Algorithm includes monitoring and redundancy for high availability synchronization, including:•Synchronization to the best available server•Client monitoring of secondary server referenceso Monitoring includes full time synchronization reporting of secondary servero Supports a programmable number of secondary server connections•Hitless reference switching between multiple servers•Holdover when server packet connectivity is lost•TIE-clear option to build out, or clear, phase offsets between server references4.7 GeneralThe Time Synchronization Algorithm includes many advanced features to aide in the high-accuracy & high-stability applications, including:•Full PLL state machine (Freerun, Holdover, Frequency Lock Acquiring, Frequency Lock Acquired, Phase Lock Acquired), with programmable thresholds for state transitions•Programmable, non-linear packet selection with PDV suppression•Programmable bandwidth configurability from sub-mHz to 100s of mHz.•Programmable packet rates from 1 packet/second to over 128 packets/second•Programmable phase slope limiting, down to 1 ns/s•Programmable frequency change limiting, down to 1 ppb/s•Warm-start to initialize or seed the Time Synchronization Algorithm from a stored or last-known-good frequency offset to improve convergence•Programmable thresholds for management of phase errors: when to adjust with frequency offsets and when to adjust with phase jumps•User ability to manually add frequency offsets due to temperature or ageing (especially during holdover state)4.8 ReportingThe Time Synchronization Algorithm includes user reporting to aide in performance debugging, including: •Set of user notifications about packet network events, such as packet loss, small transient phase jumps, large transient phase jumps, outliers, network path re-routes•Set of metrics related to the synchronization, such as frequency stability and phase stability•Independent reporting of the forward path and reverse path lock status•Oscillator stability analysis for excessive ageing or temperature variation•Server tracking impairments such as pull-in range exceeded4.9 Product Number SupportThere are several Time Synchronization Algorithm products. The following table provides a summary of support with the ZL3079x devices. Refer to ZLS30380 API User Guide section 1.0 “Products”.Product Number Product Name SupportedZLS30387 Basic Frequency and Phase Support NoZLS30384 IntermediateNoFrequency & PhaseSupportZLS30383 QualcommNoSmall Cell CustomZLS30380 Advanced YesMicrosemi Corporate Headquarters One EnterpriseAliso Viejo, CA 92656 USAWithin the USA: +1 (800) 713-4113 Outside the USA: +1 (949) 380-6100 Sales: +1 (949) 380-6136Fax: +1 (949) 215-4996E-mail: ***************************©2019 Microsemi Corporation. All rights reserved. Microsemi and the Microsemi logo are trademarks of Microsemi Corporation. All other trademarks and service marks are the property of their respective owners. Microsemi Corporation (Nasdaq: MSCC) offers a comprehensive portfolio of semiconductor and system solutions for communications, defense & security, aerospace and industrial markets. Products include high-performance and radiation-hardened analog mixed-signal integrated circuits, FPGAs, SoCs and ASICs; power management products; timing and synchronization devices and precise time solutions, setting the world’s standard for time; voice processing devices; RF solutions; discrete components; security technologies and scalable anti-tamper products; Power-over-Ethernet ICs and midspans; as well as custom design capabilities and services. Microsemi is headquartered in Aliso Viejo, Calif., and has approximately 3,400 employees globally. Learn more at .Microsemi makes no warranty, representation, or guarantee regarding the information contained herein or the suitability of its products and services for any particular purpose, nor does Microsemi assume any liability whatsoever arising out of the application or use of any product or circuit. The products sold hereunder and any other products sold by Microsemi have been subject to limited testing and should not be used in conjunction with mission-critical equipment or applications. Any performance specifications are believed to be reliable but are not verified, and Buyer must conduct and complete all performance and other testing of the products, alone and together with, or installed in, any end-products. Buyer shall not rely on any data and performance specifications or parameters provided by Microsemi. It is the Buyer’s responsibility to independently determine suitability of any products and to test and verify the same. The information provided by Microsemi hereunder is provided “as is, where is” and with all faults, and the entire risk associated with such information is entirely with the Buyer. Microsemi does not grant, explicitly or implicitly, to any party any patent rights, licenses, or any other IP rights, whether with regard to such information itself or anything described by such information. Information provided in this document is proprietary to Microsemi, and Microsemi reserves the right to make any changes to the information in this document or to any products and services at any time without notice.。

K-SYNC同步器使用说明

Synchronizing unit

Sync status for each installed echo sounder.

Echo sounders may be disabled

Disabled echo sounders will not be triggered, even if they are member of a group.

SU16 Synchronizing unit

Synchronizing unit

Synchronizing unit

The SU 16 Synchronizing Unit provides highly configurable timing of pinging when multiple echo sounders are employed on a vessel.

Approximate sound speed: Used for travel time calculations.

Synchronizing unit

Settings->Installation->Installation settings

Password: simrad0

To add or remove echo sounders from this list:

Not used 6 5 4 Trig In (CTS/RTT) 3 2 1 Transmitting (input) Trig Out

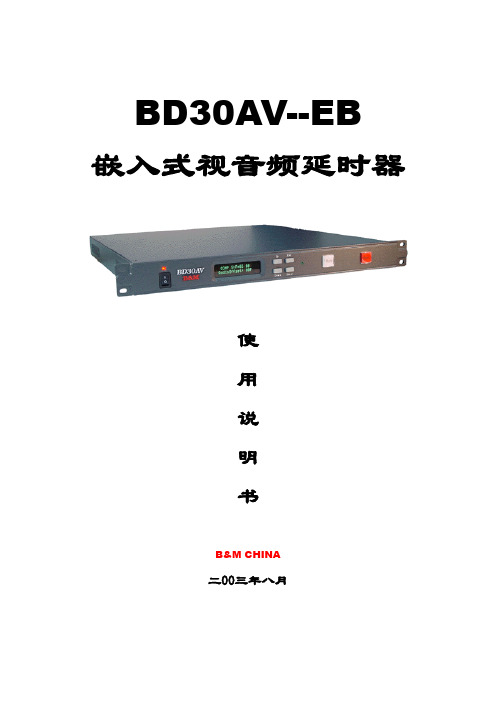

嵌入式视音频延时器

BD30AV--EB 嵌入式视音频延时器使用说明书B&M CHINA二00三年八月前言恭喜你决定使用BD30AV—EB嵌入式视音频同步延时器,BD30AV—EB嵌入式视音频同步延时器的设计为专业视频用户带来了无法比拟的性能,方便直观的操作,以及可信赖的稳定性。

本手册将会教你安装和使用BD30AV—EB嵌入式视音频同步延时器,并说明了BD30AV—EB嵌入式视音频同步延时器和其它设备的联接方法。

BD30AV—EB嵌入式视音频同步延时器是一个宽频带的具有时基校正和帧同步功能的延时器,它的延时时间可由零到三十秒调整。

BD30AV--EB采用最新芯片设计,指标高、性能好,广泛应用于卫星转播及现场直播等场合。

BD30AV--EB的面板使用 VFD 液晶显示板,使用户更容易精确控制。

BD30AV--EB所有按键选用进口轻触型开关,使用舒适。

BD30AV--EB控制面板一目了然,产品易学易用,在下一部分中,将介绍BD30AV--EB的安装、操作和具体应用。

和所有的BM系列产品一样,BD30AV--EB为你提供多年的保修服务。

本公司保证提供优质的产品设计、生产和售后服务,如有问题和建议,请与我们联系。

安全信息电源本产品使用的电源,不能超过255Vrms(在火线与零线之间或者火线与地线之间)。

电源接地保护对于安全操作十分重要。

接地本产品通过电源线中的地线接地。

为了防止遭到电击,在将本产品接到电源之前,要先将电源线插入正确的插座中。

不接地的危险若没有接地保护,所有产品的部件,包括把手和旋钮,都将是未绝缘的,这样很容易使人遭到电击。

使用环境不要在下列的环境中使用本产品:高温、潮湿、恶劣的气候、未知的电源电压或装有不恰当的保险丝。

产品的外壳和面板为避免受到人身伤害,请不要拿掉产品的外壳或面板。

在没有正确安装外壳和面板之前,请不要操作设备。

产品说明本章对BD30AV—EB嵌入式视音频同步延时器作了基本的概述。

介绍了输入输出视音频连接、电源连接、操作控制和面板 VFD 显示器。

[讲解]轩氏同步器使用说明

![[讲解]轩氏同步器使用说明](https://img.taocdn.com/s3/m/cc9bd3eb900ef12d2af90242a8956bec0975a57e.png)

轩氏同步器使用说明键盘鼠标同步器说明书1.串屏功能:关于同步器串屏功能设置方法:小键盘“*”+S 打开串屏并默认第一台电脑控制有效小键盘“*”+E 或小键盘“*”+0关闭串屏并默认全部电脑控制有效说明:1).单个同步器有串屏功能,多个同步器级联没有串屏功能, 多个设备级联串屏没有意义。

2).在串屏模式下,支持键盘切换功能。

3). 串屏模式下不支持退出同步的切换。

3). 鼠标串屏到某一台电脑后,键盘也在对应的电脑有效。

功能实现:以6台电脑串屏为例:要求可以从左向右串屏1->2->3->4->5->6->1,也可以从右向左串屏6->5->4->3->2->1->6,串屏时,比如由PC1串到PC2,光标从PC1的最右边开始串到PC2的最左边,依次类推。

2.退出功能:同步器在同步控制过程中,可以把指定的电脑退出同步控制退出方法:空格右边的win键(也就是空格右边的窗口键)+小键盘的 1~8键切换方法:按住小键盘 * 组合 1~8键,在8台电脑之间切换按住小键盘 * 组合 0键,8台电脑同步(开机默认同步)鼠标工作模式:1.正常工作模式:(同步器加电默认工作方式)切换方法:按住鼠标左键,中键,右键,松开中键,松开左键和右键进入正常工作模式2.3D模式:切换方法:按住鼠标中键,再按一下鼠标左键,进入3D模式,3D 模式用鼠标移动人物视角时能保持完全同步(此模式有很多技巧,有经验的用户可以尝试)。

3.DN(龙之谷)模式:切换方法:按住鼠标中键,再按一下鼠标右键,进入DN模式。

一、功能介绍1、同步功能:来自同一套键盘鼠标的动作指令通过同步器分出多路完全相同的信号,同步传送给多台电脑,以实现多台电脑的动作完全一致!例如,按“A”则几台显示器上同出现“A”,按“1”则同时出现“1”;鼠标也一样,几台电脑的鼠标箭头以相同的轨迹移动。

2、切换功能(单手切换):通过切换功能可以选择任意一台电脑单独控制。

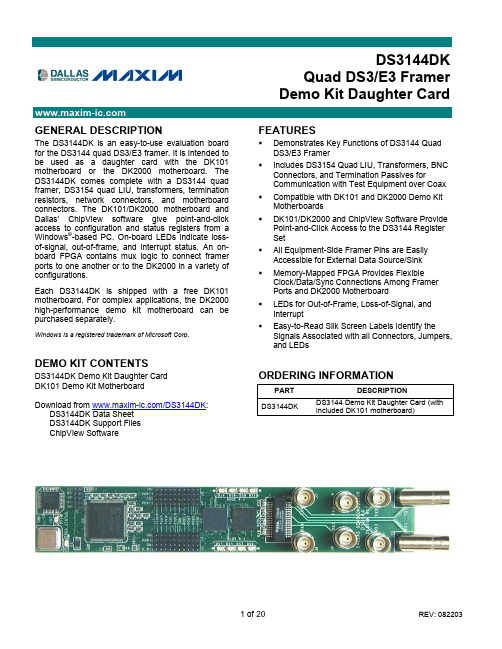

德拉斯DS3144DK E3 DS3 四路帧同步器开发套件说明书

GENERAL DESCRIPTIONThe DS3144DK is an easy-to-use evaluation board for the DS3144 quad DS3/E3 framer. It is intended to be used as a daughter card with the DK101 motherboard or the DK2000 motherboard. The DS3144DK comes complete with a DS3144 quad framer, DS3154 quad LIU, transformers, termination resistors, network connectors, and motherboard connectors. The DK101/DK2000 motherboard and Dallas’ ChipView software give point-and-click access to configuration and status registers from a Windows®-based PC. On-board LEDs indicate loss-of-signal, out-of-frame, and interrupt status. An on-board FPGA contains mux logic to connect framer ports to one another or to the DK2000 in a variety of configurations.Each DS3144DK is shipped with a free DK101 motherboard. For complex applications, the DK2000 high-performance demo kit motherboard can be purchased separately.Windows is a registered trademark of Microsoft Corp.DEMO KIT CONTENTSDS3144DK Demo Kit Daughter CardDK101 Demo Kit MotherboardDownload from /DS3144DK: DS3144DK Data SheetDS3144DK Support FilesChipView Software FEATURES§ Demonstrates Key Functions of DS3144 Quad DS3/E3 Framer§ Includes DS3154 Quad LIU, Transformers, BNC Connectors, and Termination Passives forCommunication with Test Equipment over Coax§ Compatible with DK101 and DK2000 Demo Kit Motherboards§ DK101/DK2000 and ChipView Software Provide Point-and-Click Access to the DS3144 RegisterSet§ All Equipment-Side Framer Pins are EasilyAccessible for External Data Source/Sink§ Memory-Mapped FPGA Provides FlexibleClock/Data/Sync Connections Among FramerPorts and DK2000 Motherboard§ LEDs for Out-of-Frame, Loss-of-Signal, and Interrupt§ Easy-to-Read Silk Screen Labels Identify the Signals Associated with all Connectors, Jumpers,and LEDsORDERING INFORMATIONPART DESCRIPTION DS3144DKDS3144 Demo Kit Daughter Card (withincluded DK101 motherboard)DS3144DKQuad DS3/E3 Framer Demo Kit Daughter CardCOMPONENT LISTDESIGNATION QTY DESCRIPTION SUPPLIER PARTC1, C2, C15 3 0.1m F 10%, 16V ceramic capacitors (0805) Panasonic ECJ-2VB1C104K C3–C9, C11–C14, C16, C20, C22, C23, C25–C32 23 0.1m F 10%, 16V ceramic capacitors (0603) Phycomp 06032R104K7B20D C10, C17, C18, C24 4 1m F 10%, 16V ceramic capacitors (1206) Panasonic ECJ-3YB1C105K C19, C21 2 10m F 20%, 10V ceramic capacitors (1206)Panasonic ECJ-3YB1A106MDS1, DS3–DS109 LED, red, SMDPanasonic LN1251CDS2 1 LED, green, SMD Panasonic LN1351C J1 1 10-pin connector, dual-row vertical Digi-Key S2012-05-ND J2–J5 4 20-pin headers, dual-row verticalSamtecHDR-TSW-110-14-T-D J6–J1165-pin BNC connectors, right-angle verticalCambridge CP-BNCPC-004 J12, J13 2 5-pin BNC connectors, right-angle Kruvand UCBJR220J14, J15 2 50-pin connectors, dual-row vertical SamtecTFM-125-02-S-D-LCR1–R5, R7–R18,R23, R28–R5949 30W 5%, 1/16W resistors (0603)Panasonic ERJ-3GEYJ300V R6 1 470W 5%, 1/10W resistor (0805)Panasonic ERJ-6GEYJ471V R19–R22, R69–R72 8 332W 1%, 1/10W resistors (0805)Panasonic ERJ-6ENF3320V R24 1 10k W 5%, 1/10W resistor (0805) Panasonic ERJ-6GEYJ103V R25, R26 2 330W 5% 1/10W MF resistors (0805) Panasonic ERA-6YEB331V R27 1 Not populated — —R60 1 10k W 5%, 1/10W resistor (0805) Panasonic ERJ-6ENF1002V R61–R68 8 100W 1/16W 5% resistors (0603)Panasonic ERJ-3GEYJ101V T1 1 XFMR, XMIT/RCV, 1 to 2, SMT 32-pinPulse Engineering T3049 U1 1Serial configuration EEPROM for Xilinx, 65kB 8-pin DIP. Socketed (not populated) AtmelAT17LV65EUA and61499-30831007000-NDU2 11M PROM for FPGA44-pin TQFP (not populated) Xilinx XC18V01VQ44C_U U3 18-Pin m MAXV OUT = 2.5V or Adj Maxim MAX1792EUA25 U4 1Xilinx Spartan 2.5V FPGA, 20mm X 20mm 144-pin TQFP Xilinx XC2S50-5TQ144C U5 1Quad DS3/E3 framer144-pin BGA, 0°C to +70°C DallasSemiconductor DS3144 U6 1Quad DS3/E3/STS-1 LIU144-pin BGA DallasSemiconductor DS3154Y113.3V, 34.368MHz crystal clock oscillatorSaRonixNTH089AA3-34.368BOARD FLOORPLANLINE-SIDE CONNECTIONSThe DS3144DK implements the transmit (Tx) and receive (Rx) line interface networks recommended in the DS3154 data sheet. The BNC connectors are labeled TX1 through TX4 and RX1 through RX4. Note that the purpose of the DS3144DK is to evaluate the DS3144 framer, not the DS3154 LIU. The DS3144DK is not an impedance-matched board and therefore has not been designed to have transmit waveforms with optimal template fit. To evaluate the analog performance of the DS3154, request a DS3154DK demo kit.INTERFACE CONNECTORSTwo 50-pin connectors (J14, J15) on the bottom of the DS3144DK daughter card provide the processor interface, DS3 clock, and power supply from the DK101 or DK2000 motherboards. These connectors also provide a bidirectional clock/data/sync connection with the DK2000.CONNECTION TO A COMPUTERRefer to the DK101 data sheet or the DK2000 data sheet for information. After power is applied, if the DS3144DK is working correctly, the FPGA status LED (green) is lit, the INT LED (red) on the DS3144DK is not lit, and the RLOS and ROOF LEDs (red) may or may not be lit.QUICK SETUP (REGISTER VIEW)1) Connect the DS3144DK daughter card to the DK101 motherboard or the DK2000 motherboard.2) Connect the motherboard to a PC and a power supply as described in the motherboard data sheet.3) Install and run the ChipView software, as described in the motherboard data sheet.4) ChipView offers a choice between Register View, Demo, and Terminal Mode. Select Register View.5) In the Definition File Assignment window, select the file DS3144DC_FPGA.def. This definition file will, in turn,load DS3154DC.def, DS3144_1_DC.def, DS3144_2_DC.def, DS3144_3_DC.def, and DS3144_4_DC.def.6) Next the Register View Screen appears, showing the register names, acronyms, and values for the DS3144,DS3154, and the FPGA. Select among the register views using the pulldown menu box on the right.Several register initialization (.INI) files are available for the DS3144DK. Initialization files are loaded by selecting the menu option File®Register .INI File®Load .INI File.7) Load the .INI file DS3144_1_txPRBS215-1_Cbit.ini.8) Switch to the DS3154 register view (DS3154DC.def) and set TCR1 = 0 and RCR1 = 0 on the DS3154 (thisclears the transmit tri-state and receive tri-state bits that are set on power-up in the DS3154).9) Loopback port 1 by either (a) connecting a length of coax cable between the TX1 BNC and the RX1 BNC, or(b) setting the GCR1:LLB (local loopback) bit in the DS3154.10) Switch to the DS3144 port 1 register view (DS3144_1_DC.def). Toggle BCR1:TC high then low to begintransmitting a 215 - 1 PRBS pattern. Toggle BCR1:RESYNC high then low to resynchronize the BERT receiver.11) At this point the following may be observed:· Port 1 RLOS and ROOF LEDs are not lit, meaning the port 1 framer has acquired frame sync. This can also be observed in the port 1 T3E3SR status register.· The port 1 BSR:SYNC bit is set, indicating the BERT receiver is receiving the 215 - 1 PRBS pattern.This is a very basic setup designed to build familiarity with the DS3144DK. Many other configurations are possible. Consult the DS3144 data sheet and the remainder of this data sheet for further information.MEMORY MAPDK101 daughter card address space begins at 0x81000000.DK2000 daughter card address space begins at:0x30000000 for slot 00x40000000 for slot 10x50000000 for slot 20x60000000 for slot 3All offsets in Table 1 below are relative to the beginning of the daughter card address space.Table 1. Daughter Card Address MapDS3/E3DS3144 OFFSET DS3154 OFFSET FPGA OFFSETPORT NUMBER1 0x1300 to 0x13FF 0x2030 to 0x203F 0x0010 to 0x001F2 0x1000 to 0x10FF 0x2010 to 0x201F 0x0020 to 0x002F3 0x1100 to 0x11FF 0x2020 to 0x202F 0x0030 to 0x003F4 0x1200 to 0x12FF 0x2000 to 0x200F 0x0040 to 0x004FAll offsets in Table 2 below are relative to the daughter card address space plus the DS3/E3 port offset in Table 1. Table 2. DS3144DK FPGA Register MapOFFSET REGISTER TYPE DESCRIPTIONIDBoard0x0000 BID Read-Only0x0002 XBIDH Read-Only High Nibble Extended Board ID0x0003 XBIDM Read-Only Middle Nibble Extended Board ID0x0004 XBIDL Read-Only Low Nibble Extended Board ID0x0005 BREV Read-Only Board Fab Revision0x0006 AREV Read-Only Board Assembly Revision0x0007 PREV Read-Only PLD Revision0x000A PCTC_SR Control PCM_TXCLK SourceSource0x000B PCTS_SR Control PCM_TSYNCSource0x000C PCRX_SR Control PCM_RXDSource0x000D PCRC_SR Control PCM_RXCLKSource0x000E PCRS_SR Control PCM_RSYNC0x00100x0020TDAT_SR Control DS3144 TDAT Source0x00300x00400x00110x0021TICK_SR Control DS3144 TICLK Source0x00310x00410x00120x0022TSOF_SR Control DS3144 TSOF Source0x00320x0042Registers in the FPGA can be easily modified using the ChipView software and the definition file named DS3144DC_FPGA.def. Registers 0x00 through 0x07 (excluding register 0x01, which has no function on the DS3144DK) are read-only and are programmed at the factory to document board identification and revision information. The remaining registers in the FPGA control the connection of the DS3144’s equipment-side framer pins. With these control registers, the framers within the DS3144 can be looped back on themselves externally, connected to each other back-to-back, or connected to the DK2000 motherboard.In Table 2 and the control register descriptions below, PCM_TXCLK, PCM_TXD, and PCM_TSYNC areclock/data/sync lines over which the DS3144 can transmit a DS3/E3 data stream to the DK2000 motherboard orother daughter cards plugged into the DK2000. PCM_RXCLK, PCM_RXD, and PCM_RSYNC are clock/data/synclines over which the DS3144DK can receive a DS3/E3 data stream from the DK2000 or a daughter card pluggedinto the DK2000. See the DS3144DK schematics for additional details.Note that the DS3/E3 port numbers of the DS3144DK (as silk-screened on the board) do not match the DS3144port numbers and the DS3154 port numbers. Table 3 details the mapping of device port numbers to board port numbers. This mapping is reflected in the address ranges shown in Table 1.Table 3. Relationship of Silk-Screened Port Numbers to IC Ports NumbersSILK-SCREENED PORT NUMBERDS3144 PORT DS3154 PORTON BNCs AND RLOS/ROOF LEDs41 42 1233 214 3From this it can be seen that, for example, the BNCs and LEDs for DS3144DK port 4 are associated with port 3 ofthe DS3144 and port 1 of the DS3154.CONTROL REGISTERSRegister Name: PCTC_SRRegister Description: PCM_TXCLK SourceRegister Address Offset: 0x0A# 7 6 5 4 3 2 1 0 BitPCS0PCS1Name — — — — — PCS2Default — — — — — 0 0 0 Bits 2 to 0: PCM_TXCLK Source (PCS[2:0])000 = Tri-state PCM_TXCLK001 = Drive PCM_TXCLK with TDEN/TGCLK1010 = Drive PCM_TXCLK with TDEN/TGCLK2011 = Drive PCM_TXCLK with TDEN/TGCLK3100 = Drive PCM_TXCLK with TDEN/TGCLK4Register Name: PCTS_SRRegister Description: PCM_TSYNC SourceRegister Address Offset: 0x0BBit# 7 6 5 4 3 2 1 0PSS0 Name — — — — — PSS2PSS1Default — — — — — 0 0 0 Bits 2 to 0: PCM_TSYNC Source (PSS[2:0])000 = Tri-state PCM_TSYNC001 = Drive PCM_TSYNC with TSOF1010 = Drive PCM_TSYNC with TSOF2011 = Drive PCM_TSYNC with TSOF3100 = Drive PCM_TSYNC with TSOF4Note: Only use non-zero settings of PSS[2:0] when the TSOFx pin is configured as an output by settingMC3:TSOFC = 1 in the corresponding DS3144 framer.Register Description: PCM_RXD SourceRegister Address Offset: 0x0C# 7 6 5 4 3 2 1 0 BitPRXS0PRXS1Name — — — — —PRXS2Default — — — — — 0 0 0 Bits 2 to 0: PCM_RXD Source (PRXS[2:0])000 = Tri-state PCM_RXD001 = Drive PCM_RXD with RDAT1010 = Drive PCM_RXD with RDAT2011 = Drive PCM_RXD with RDAT3100 = Drive PCM_RXD with RDAT4Register Name: PCRC_SRRegister Description: PCM_RXCLK SourceRegister Address Offset: 0x0D# 7 6 5 4 3 2 1 0 BitPRCS1PRCS0 Name — — — — —PRCS2Default — — — — — 0 0 0 Bits 2 to 0: PCM_RXCLK Source (PRCS[2:0])000 = Tri-state PCM_RXCLK001 = Drive PCM_RXCLK with RDEN/RGCLK1010 = Drive PCM_RXCLK with RDEN/RGCLK2011 = Drive PCM_RXCLK with RDEN/RGCLK3100 = Drive PCM_RXCLK with RDEN/RGCLK4Register Name: PCRS_SRRegister Description: PCM_RSYNC SourceRegister Address Offset: 0x0E# 7 6 5 4 3 2 1 0 BitPRSS0 Name — — — — —PRSS1PRSS2Default — — — — — 0 0 0 Bits 2 to 0: PCM RSYNC Source (PRSS[2:0])000 = Tri-state PCM_RSYNC001 = Drive PCM_RSYNC with RSOF1010 = Drive PCM_RSYNC with RSOF2011 = Drive PCM_RSYNC with RSOF3100 = Drive PCM_RSYNC with RSOF4Register Description: DS3144 TDATx SourceRegister Address Offset: 0x10, 0x20, 0x30, 0x40# 7 6 5 4 3 2 1 0 BitTDS1TDS0 Name — — — — — TDS2SeenotenotenoteDefault — — — — —SeeSeeBits 2 to 0: TDATx Source (TDS[2:0])000 = Tri-state TDATx001 = Drive TDATx with RDAT1010 = Drive TDATx with RDAT2011 = Drive TDATx with RDAT3100 = Drive TDATx with RDAT4101 = Drive TDATx with PCM_TXDNote: Initial values are such that TDAT1¬RDAT1, TDAT2¬RDAT2, TDAT3¬RDAT3, TDAT4¬RDAT4, which corresponds to address 0x10 = 001, address 0x20 = 010, address 0x30 = 011, and address 0x40 = 100.Register Name: TICK_SRRegister Description: DS3144 TICLKx SourceRegister Address Offset: 0x11, 0x21, 0x31, 0x41Bit# 7 6 5 4 3 2 1 0TCS0 Name — — — — — TCS2TCS1Default — — — — — 1 0 1Bits 2 to 0: TICLKx Source (TCS[2:0])000 = Tri-state TICLKx001 = Drive TICLKx with ROCLK1010 = Drive TICLKx with ROCLK2011 = Drive TICLKx with ROCLK3100 = Drive TICLKx with ROCLK4101 = Drive TICLKx with DS3_CLK110 = Drive TICLKx with E3_CLKRegister Name: TSOF_SRRegister Description: DS3144 TSOFx SourceRegister Address Offset: 0x12, 0x22, 0x32, 0x42# 7 6 5 4 3 2 1 0 BitName — — — — — TSS2TSS0TSS1Default — — — — — 0 0 0Bits 2 to 0: TICLKx Source (TSS[2:0])000 = Tri-state TSOFx001 = Drive TSOFx with RSOF1010 = Drive TSOFx with RSOF2011 = Drive TSOFx with RSOF3100 = Drive TSOFx with RSOF4Note: Only use non-zero settings of TSS[2:0] when the TSOFx pin is configured as an input by settingMC3:TSOFC = 0 in the corresponding DS3144 framer.FPGA CONTROL EXAMPLESThe control registers in the DS3144DK’s FPGA support a number of different connection scenarios. Figure 1 shows three example scenarios, and Table 4 lists the FPGA control registers settings required to implement them.Figure 1. Example Connection ScenariosTable 4. Register Settings for Sample ConfigurationsOFFSET(S) REGISTERSCENARIO #1 (PORT 1 ONLY) SCENARIO #2 (ALL PORTS) SCENARIO #3(ALL PORTS)0x000A PCTC_SR 001 N/A N/A 0x000B PCTS_SR 001 N/A N/A 0x000C PCRX_SR 001 N/A N/A 0x000D PCRC_SR 001 N/A N/A 0x000E PCRS_SR 001 N/A N/A 0x0010 101 001 000 0x0020 N/A 010 0000x0030 N/A 011 000 0x0040 TDAT_SRN/A 100 000 0x0011 101 001 000 0x0021 N/A 010 0000x0031 N/A 011 000 0x0041 TICK_SRN/A 100 000 0x0012 000 001 000 0x0022 N/A 010 0000x0032 N/A 011 000 0x0042 TSOF_SRN/A 100 000DS3144 INFORMATIONFor more information about the DS3144 quad DS3/E3 framer, please consult the DS3144 data sheet, available on our website at /DS3144.DS3154 INFORMATIONFor more information about the DS3154 quad DS3/E3/STS-1 LIU, please consult the DS3154 data sheet, available on our website at /DS3154.DS3144DK INFORMATIONFor more information about the DS3144DK—including the ChipView software, the latest support files (.DEF, .INI, etc.), and the latest data sheet—please visit our website at /DS3144DK.DK101/DK2000 INFORMATIONFor more information about the DK101 or DK2000, please consult their respective data sheets, available on our website at /DK101 or /DK2000.TECHNICAL SUPPORTFor additional technical support, please email your questions to ***************************.Maxim/Dallas Semiconductor cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Maxim/Dallas Semiconductor product. No circuit patent licenses are implied. Maxim/Dallas Semiconductor reserves the right to change the circuitry and specifications without notice at any time.Maxim Integr ated Products, 120 San Gabri el Drive, Sunnyval e, CA 94086 408-737-7600© 2003 Maxim Integrated Products · Printed USA。

Protools SYNC HD中文使用手册

時間碼偏置補償 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 40 生成與再生成時間碼 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 40 生成 Window Dub. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 45

SYNC 週邊裝置特性. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2 系統要求和相容性 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3 註冊 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3 關於本手冊 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4 關於 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4

微小电子同步器说明书

1Features•Frequency and Phase Sync over Packet Networks •Frequency accuracy performance for WCDMA-FDD, GSM, LTE-FDD and femtocell applications •Frequency performance for ITU-T G.823 and G.824 synchronization interface, as well as G.8261 PNT PEC and CES interfaces•Phase Synchronization performance forWCDMA-TDD, Mobile WiMAX, TD-SCDMA and CDMA2000 applications•Client holdover and reference switching between multiple Servers•Physical Layer Equipment Clocks Synchronizatin •ITU-T G.8262 for SyncE EEC option 1 and 2•ITU-T G.813 for SONET/SDH SEC option 1 and 2•Telcordia GR-1244 and GR-253 Stratum 3 and SMC•Support for G.781 SETS•Any input clock rate from 1Hz to 750MHz •Automatic hitless reference switching and digital holdover on reference fail•Flexible two-stage architecture translates between arbitrary data, line coding and FEC rates •Digital PLL with programmable bandwidth from 0.1mHz up to 1kHz•Programmable synthesizers•Any output clock rate from 1Hz to 750MHz •Output jitter below 0.62 ps rms•Operates from a single crystal resonator or clock oscillator•Configurable via SPI/I 2C interfaceMay 2013Figure 1 - Functional Block DiagramZL30361IEEE 1588 and Synchronous Ethernet PacketClock Network SynchronizerShort Form Data SheetOrdering InformationZL30361GDG2 144 Pin LBGA TraysPb Free Tin/Silver/Copper-40o C to +85o CPackage size: 13 x 13 mmDetailed FeaturesGeneral•One clock channel•Operates from a single crystal resonator or clock oscillator•Configurable via its SPI/I2C interfaceTime Synchronization Algorithm•External algorithm controls software digital PLL to adjust frequency and phase alignment•Frequency, Phase and Time Synchronization over IP, MPLS and Ethernet Packet Networks•Frequency accuracy performance for WCDMA-FDD, GSM, LTE-FDD and femtocell applications, with target performance less than ± 15 ppb.•Frequency performance for ITU-T G.823 and G.824 synchronization interface, as well as G.8261 PNT EEC, PNT PEC and CES interface specifications.•Phase Synchronization performance for WCDMA-TDD, Mobile WiMAX, TD-SCDMA and CDMA2000 applications with target performance less than ± 1 s phase alignment.•Time Synchronization for UTC-traceability and GPS replacement.•Client reference switching between multiple Servers•Client holdover when Server packet connectivity is lostElectrical Clock Inputs•Nine input references configurable as single ended or differential and two single ended input references •Synchronize to any clock rate from 1Hz to 750MHz on differential inputs•Synchronize to any clock rate from 1Hz to 177.75MHz on singled-ended inputs•Any input reference can be fed with sync (frame pulse) or clock.•Synchronize to sync pulse and sync pulse/clock pair.•Flexible input reference monitoring automatically disqualifies references based on frequency and phase irregularities•LOS•Single cycle monitor•Precise frequency monitor•Coarse frequency monitor•Guard soak timer•Per input clock delay compensationElectrical Clock Engine•Digital PLL filters jitter from 0.1 mHz up to 1 kHz•Flexible two-stage architecture translates between arbitrary data rates, line coding rates and FEC rates •Internal state machine automatically controls mode of operation (free-run, locked, holdover)•Automatic hitless reference switching and digital holdover on reference fail•Physical-to-physical reference switching•Physical-to-packet reference switching•Packet-to-physical reference switching•Packet-to-packet reference switching•Support for wide variety of Equipment Clock specifications•SyncE•ITU-T G.8262 option 1 EEC (Europe/China)•ITU-T G.8262 option 2 (USA)•SONET/SDH•ITU-T G.813 option 1 SEC (Europe/China)•ITU-T G.813 option 2 (USA)•ANSI T1.105/Telcordia GR-253 Stratum 3 for SONET•Telcordia GR-253 SMC•PDH•ITU-T G.812 Type I SSU•ITU-T G.812 Type III, ANSI T1.101/Telcordia GR-1244 Stratum 3E, including phase build out•ANSI T1.101/Telcordia GR-1244 Stratum 3•ANSI T1.101/Telcordia GR-1244 Stratum 4E/4•Selectable phase slope limiting•Holdover better than 1 ppb (when using < 0.1 Hz filter)•Supports ITU-T G.823, G.824 and G.8261 for 2048kbit/s and 1544kbit/s interfaces•Supports G.781 SETSElectrical Clock Generation•Three programmable synthesizers•Six LVPECL outputs•Two LVPECL outputs per synthesizer•Generate any clock rate from 1Hz to 750MHz•Maximum jitter below 0.62ps rms•Meets OC-192, STM-64, 1 GbE and 10 GbE interface jitter requirements•Six LVCMOS outputs•Two LVCMOS outputs per synthesizer•Generate any clock rate from 1 Hz to 177.75MHz•Programmable output advancement/delay to accommodate trace delays or compensate for system routing paths•Outputs may be disabled to save powerAPI Software•Interfaces to 1588-capable PHY and switches with integrated timestamping•Abstraction layer for independence from OS and CPU, from embedded SoC to home-grown•Fits into centralized, highly integrated pizza box architectures as well as distributed architectures with multiple line cards and timing cardsApplications•ITU-T G.8262 System Timing Cards which support 1GbE and 10GbE interfaces•Telcordia GR-253 Carrier Grade SONET/SDH Stratum 3 System Timing Cards•System Timing Cards which supports ITU-T G.781 SETS (SDH Equipment Timing Source)•Integrated basestation reference clock for air interface for GSM, WCDMA, LTE and WiMAX macro, micro or femtocells•Mobile Backhaul NID, edge router, or access aggregation node•EPON/GE-PON and GPON OLT•EPON/GE-PON and GPON ONU/OLT•DSLAM and RT-DSLAM•10Gigabit line cards•Synchronous Ethernet, 10GBASE-R, and 10GBASE-W•SONET/SDH, Fibre Channel, XAUIInformation relating to products and services furnished herein by Microsemi Corporation or its subsidiaries (collectively “Microsemi”) is believed to be reliable. However, Microsemi assumes no liability for errors that may appear in this publication, or for liability otherwise arising from the application or use of any such information, product or service or for any infringement of patents or other intellectual property rights owned by third parties which may result from such application or use. Neither the supply of such information or purchase of product or service conveys any license, either express or implied, under patents or other intellectual property rights owned by Microsemi or licensed from third parties by Microsemi, whatsoever. Purchasers of products are also hereby notified that the use of product in certain ways or in combination with Microsemi, or non-Microsemi furnished goods or services may infringe patents or other intellectual property rights owned by Microsemi.This publication is issued to provide information only and (unless agreed by Microsemi in writing) may not be used, applied or reproduced for any purpose nor form part of any order or contract nor to be regarded as a representation relating to the products or services concerned. The products, their specifications, services and other information appearing in this publication are subject to change by Microsemi without notice. No warranty or guarantee express or implied is made regarding the capability, performance or suitability of any product or service. Information concerning possible methods of use is provided as a guide only and does not constitute any guarantee that such methods of use will be satisfactory in a specific piece of equipment. It is the user’s responsibility to fully determine the performance and suitability of any equipment using such information and to ensure that any publication or data used is up to date and has not been superseded. Manufacturing does not necessarily include testing of all functions or parameters. These products are not suitable for use in any medical and other products whose failure to perform may result in significant injury or death to the user. All products and materials are sold and services provided subject to Microsemi’s conditions of sale which are available on request.For more information about all Microsemi productsvisit our website at/timing-and-synchronizationTECHNICAL DOCUMENTATION – NOT FOR RESALE© 2013 Microsemi Corporation. All rights reserved. Microsemi and the Microsemi logo are trademarks of Microsemi Corporation. All other trademarks and service marks are the property of their respective owners.Microsemi Corporation (NASDAQ: MSCC) offers a comprehensive portfolio of semiconductor solutions for: aerospace, defense and security; enterprise and communications; and industrial and alternative energy markets. Products include high-performance, high-reliability analog and RF devices, mixed signal and RF integrated circuits, customizable SoCs, FPGAs, and complete subsystems. Microsemi is headquartered in Aliso Viejo, Calif. Learn more at .Microsemi Corporate HeadquartersOne Enterprise, Aliso Viejo CA 92656 USA Within the USA: +1 (949) 380-6100Sales: +1 (949) 380-6136Fax: +1 (949) 215-4996。

韩国SEOHO变频器-同步控制功能说明书

同步控制摘要:本文主要讲述了同步控制的相关应用方法。

同步控制以RS422总线作为硬件载体。

文中具体描述了硬件安装、通信配置、应用实例等内容。

简介在大多数应用中,通常有多台电机同时运行,同步控制就是一个非常好的选择。

同步控制可以在多台驱动器之间以主/从模式运行。

随着数字电子技术的发展,系统中的主/从控制方式可以很方便的基于通信技术来实现。

对于同步控制中的主/从站,主站负责通信和控制信号。

主站和从站都必须被正确的配置。

RS-422作为同步控制的物理层,它允许总线中接入多台驱动设备。

为了保证通信速度,数据流仅仅从主站流向从站。

也就是说,从站并没有向主站发送数据。

主站和从站之间的数据,是随着时钟信号发送和接收的。

这样,就保证了较高的通信质量。

在第二章中,我们将讲述通信的配置;第三章中,将介绍同步控制;最后我们将讲解一个实际的应用例子。

通讯设置A.硬件安装图1所示为通讯卡,卡由3mm螺丝固定。

安装正确上电后,2个绿色LED发光。

左边LED表示RS42 2通讯卡与控制卡通讯正常,右LED表示外接+24V电源供电正常。

在整个运行过程中,2个LED灯一直发光。

J8J7LED+5V _1+5V LED+24VR ED : +24V B l ack: G ND3m m B ol t图1 通讯卡安装B. 通讯电缆连接双绞线(8线)作为RS422同步串行通信介质。

为了保证稳定性,通信总线两端必须添加终端段子。

对于多台驱动器系统,主站使用一个端子,最后一台从站插入另外一个端子。

在通信卡上有两个连接插头(J7,J8),一个用于连接双绞线,另一个用于连接终端端子(或者用于连接通向下一个驱动器的双绞线)。

具体接法见图2。

D r i ve #1D r i ve #2D r i ve #3D r i ve #N图2 驱动器之间的通讯连接C. 参数列表通信设置如下表所示:代码名称说明P28.0 Sync_Ctrl_Config[0] Disabled 通信功能取消[1] Sync_Slave 设置为从站[2] Sync_Master 设置为主站P28.1 Baud_Rate [0] 4.0Mbps设定通信速度[1] 2.875 Mbps[2] 2.0 Mbps[3] 1.0 Mbps[4] 0.5 Mbps[0] None 未设定P28.2 Message[1][1] Spd_Set_Value 转速设定值[2] Actual-Speed 实际转速值[3] Freq_Set_Value 输出频率设定值P28.3 Message[2][4] Trq_Set_Value 转矩设定制[5] Trq_Limit 转矩限制值[6] Active_I_Set_Value 有功电流设定P28.4 Message[3][7] Reactive_I_Set_Value 无功电流设定[8] V olt_Output_Magnitude 输出电压值[9] V olt_Output_Phase 输出相电压值P28.5 Err_Time_Over [ms] 通信出错时间设置[0] Normal_STOP 正常停车P28.6 Err_Action[1] E_STOP 紧急停车[2] Free_RUN 驱动输出立即停止。

键盘鼠标同步器怎么用

三一文库()〔键盘鼠标同步器怎么用〕*篇一:键盘鼠标同步器说明书键盘鼠标同步器说明书一.简介键盘鼠标同步器主要实现将键盘鼠标信号同步的传输到各个受控的计算机,为了保证数据同步性,以纯硬件的方式将键盘鼠标并行发送到受控的计算机,达到精确的同步效果。

同步器支持PS2键盘鼠标输入,USB信号输出,USB输出接到各个受控计算机,受控计算机可以独立的关机,冷启,热启。

同步器电源直接由计算机提供,同步器在使用时不需要安装任何额外的软件或驱动。

同步器键盘支持连发功能,可以同时设置小于7个连发键。

支持键盘的两种切换功能,通过切换,可以实现控制任意单台或几台计算机。

同步器鼠标支持三种工作模式。

***安装方法:请务必按照这个顺序安装开机状态--》必须先连接键鼠到同步器--》最后再连接同步器到电脑二.键盘功能:切换功能一这种方式切换可以实现任一台可控电脑有效,或全部都有效。

切换方法:小键盘上的*按键盘+小键盘上的0-6(以一控六为例)按住小键盘上的*键,再按一下小键盘上的1键,切换到第一台电脑,键盘鼠标只对第一台电脑有效。

按住小键盘上的*键,再按一下小键盘上的2键,切换到第一台电脑,键盘鼠标只对第二台电脑有效。

按住小键盘上的*键,再按一下小键盘上的3键,切换到第一台电脑,键盘鼠标只对第三台电脑有效。

按住小键盘上的*键,再按一下小键盘上的4键,切换到第一台电脑,键盘鼠标只对第四台电脑有效。

按住小键盘上的*键,再按一下小键盘上的5键,切换到第一台电脑,键盘鼠标只对第五台电脑有效。

按住小键盘上的*键,再按一下小键盘上的6键,切换到第一台电脑,键盘鼠标只对第六台电脑有效。

按住小键盘上的*键,再按一下小键盘上的0键,键盘鼠标对所有电脑都有效。

注:切换时可以看对应的指示灯,对应路的指示灯点亮的电脑控制有效。

c.切换功能二(此功能专门用户才有!)这种方式切换可以实现控制任意接入的多台电脑同步控制,可以配合切换功能一,灵活控制多台电脑同步。

跨时钟域信号同步解决方案

跨时钟域信号同步解决⽅案为了确保拥有多个异步时钟域的系统级芯⽚(SoC)能够可靠运⾏,设计⼈员必须使这些跨越了多个域的时钟和数据信号保持同步。

尽管这并不属于新提出的要求,但随着多时钟域越来越常见和复杂化,使得这⼀要求具备了新的重要意义。

⼤规模集成加上对性能的严格要求以及频率调节都导致在许多不同频率下发⽣了很多时钟域跨越现象-就像⼀场数字化的“完美风暴”。

跨时钟域(CDC)问题会以许多种形式出现,其评估难度相当⾼。

幸好,Synopsys DesignWare库产品提供了许多卓越的CDC解决⽅案,这些⽅案应⽤简便,设计⼈员只需掌握在何时以及何处应⽤它们即可。

本⽂解释了在时钟和数据信号从⼀个时钟域跨越到另⼀个时钟域时所发⽣的许多类型的同步问题。

在任何情况下,本⽂所包含的问题都涉及到相互异步的时钟域。

随着每⼀个问题的提出,本⽂将概述⼀个或多个DesignWare解决⽅案。

这些主题和解决⽅案包括:●基本同步—DW_sync●临时事件同步—DW_pulse_sync, DW_pulseack_sync●简单数据传输同步—DW_data_sync, DW_data_sync_na,DW_data_sync_1c●数据流同步—DW_fifo_s2_sf, DW_fifo_2c_df,DW_stream_sync●复位排序—DW_reset_sync●相关时钟系统数据同步—DW_data_qsync_hl,DW_data_qsync_lh1基本同步问题当来⾃⼀个时钟系统的信号将⽤作另⼀个与其不同步的时钟系统的输⼊时,就需要对信号进⾏同步以达成。

⽽不进⾏同步就⽆法达成时序收敛。

图1所⽰为采⽤⼀个单寄存器来同步⾄⽬的时钟域的异步输⼊。

伴随这种⽅法会出现的⼀个问题是,当⼀个触发器的数据输⼊处于逻辑0⾄逻辑1之间的过渡过程当中时,发给这个触发器时钟信号时有可能产⽣亚稳态现象。

亚稳态现象也有可能发⽣在触发器的建⽴时间或保持时间出现违反现象时。

boogie sync使用方法

boogie sync使用方法Boogie Sync使用方法Boogie Sync是一款功能强大的同步工具,它可以帮助用户在不同设备之间同步文件和数据。

下面将介绍Boogie Sync的使用方法,以帮助用户更好地利用这个工具。

1. 下载和安装Boogie Sync在使用Boogie Sync之前,首先需要下载并安装它。

用户可以在官方网站或应用商店中找到适合自己设备的版本,然后按照提示进行安装即可。

2. 注册和登录账号安装完成后,用户需要注册一个Boogie Sync账号。

在注册过程中,用户需要提供一些个人信息,并设置一个安全的密码。

注册完成后,用户可以使用注册的账号登录Boogie Sync。

3. 创建同步任务登录后,用户可以开始创建同步任务。

在Boogie Sync中,同步任务是指将文件或数据从一个设备同步到另一个设备的操作。

用户可以根据自己的需求选择不同的同步方式,如将文件从电脑同步到手机,或将数据从手机同步到平板电脑等。

4. 设置同步源和目标在创建同步任务时,用户需要设置同步的源和目标。

源是指要同步的文件或数据所在的位置,而目标则是文件或数据将要同步到的位置。

用户可以选择本地文件夹、云存储服务或其他设备作为源或目标。

5. 选择同步方式Boogie Sync提供了多种同步方式供用户选择。

用户可以选择实时同步,这样在文件或数据发生改变时,同步会立即进行;用户也可以选择定期同步,这样同步会在设定的时间间隔内进行;此外,用户还可以选择手动同步,这样需要手动触发同步操作。

6. 设置同步规则在创建同步任务时,用户还可以设置同步规则。

同步规则是指用户对同步过程进行的一些限制和要求。

例如,用户可以设置只同步特定类型的文件,或者只同步特定大小的文件等。

这样可以避免不必要的同步操作,提高同步效率。

7. 启动同步任务设置完成后,用户可以点击“开始同步”按钮来启动同步任务。

Boogie Sync会根据用户的设置,自动进行文件或数据的同步操作。

BenQS830C同步软件使用说明书说明书

同步Q同步Q(SyncQ)是一套搭配手機使用的同步程式。

同步的意思,就是讓兩端的資料一致。

因此,我們不僅可以透過同步Q,讓手機上的通訊錄或是行事曆等等的資料,和電腦上的Outlook一致,更可以讓電腦上心愛的圖片,或是音樂鈴聲,藉由同步的方式傳輸到手機中。

同步的方便性,在於不管你是在手機上,或是在電腦上將資料作了修正,你只要執行同步的動作,兩端的資料就會自動更新到另一端去,省去使用者自行檢查異動,與匯入匯出的繁瑣動作。

系統需求•作業系統Windows 98SE, ME, 2000, XP。

8本軟體可能無法完全支援Windows ME作業系統,若您所使用的作業系統為Windows ME,將可能發生相容性的問題。

•Outlook版本Outlook 98, 2000, 2002。

(選配)•傳輸方式序列埠,紅外線裝置任一。

安裝將同步Q安裝光碟放入光碟機後,安裝程式會自行啟動,按照安裝程式的步驟即可安裝好同步Q。

設定•傳輸方式同步Q有兩種傳輸方式,一種是透過手機所附之連接線。

另外一種是透過紅外線的方式。

如果您的個人電腦有紅外線裝置的話,我們建議您使用紅外線的傳輸方式,省去接線的不便。

A.連接線連接線兩端的接頭為一大一小,大的接頭接在電腦上的序列阜(9 pin),小的接頭接在手機上方左側的免持聽筒耳機孔中。

B.紅外線手機的紅外線裝置位於手機下方左側。

開始同步時,請確認紅外線裝置是否有對準電腦端的紅外線裝置。

8S820C無紅外線裝置。

•手機設定選擇好使用哪種傳輸方式後,請進入手機的同步功能選單中:娛樂→同步傳輸→傳輸方式,選擇您所用的傳輸方式。

•同步Q設定電腦端的同步Q也必須設定所使用的傳輸方式。

請先從桌面或「開始」選單中啟動同步Q,然後切換到「設定」頁面中,用滑鼠選擇您所採用的傳輸方式。

(如下圖)當您選擇「傳輸線」的傳輸方式時,您可以設定使用電腦端哪一個序列埠。

(如下圖)圖片功能您可以新增自己喜愛的圖片檔案到同步Q中,然後同步到手機上。

NCsentry2K操作说明

NCsentry软件操作说明一、软件的安装点击“NCSentry2kBS.exe”,输入授权码,如下:二、程序的传输1.接线通信电缆一端连接PC机9针串口,另一端连接CNC系统主机(232)插座。

2.通信协议设定CNC与PC要使用相同的通信协议才能正常通信。

标准设置为:7位数据位(DATA:7),2位停止位(STOP:2),偶校验(Parity:EVEN),波特率4800(Baud:4800)。

其中波特率可在NC参数#311进行选择。

确认以下CNC的设置:1)[设定]页面,PUNCH CODE=1,INPUT DEVICE 2=1。

2)[参数]页面,NC参数#311=10011001(对应波特率4800)。

3.程序的存贮(PC→CNC)1)打开要存入CNC的程序。

注意:程序是以%起始和结束,英文冒号代表程序号O。

2)进入Utilities|send…,点击Settings进行以下设定:3)设定完毕,点击START发送。

信息框提示等待CNC接收(Send is waiting machine to receive)。

4)打开程序锁开关。

5)CNC切换到编辑方式,在[程序]页面下,输入[O]+[程序号],按[数据输入]键接收。

如果存贮所有程序,则输入[O]+[-9999]。

传输过程中显示闪烁的“EDIT”标记。

4.程序的输出(CNC→PC)1)进入Utilities|Receive…,点击Settings进行以下设定:2)点击START准备接收。

3)CNC切换到编辑方式,在[程序]页面下,输入[O]+[程序号],按[数据输出]键输出选择的程序。

如果输出存贮器内的所有程序,则输入[O]+[-9999]。

通信过程中将显示闪烁的“EDIT”标记。

4)删除文件头的“@018”和文件尾的“ٱ”字符,保存文件。

三、参数的传输接线和通信协议设定与程序传输一样,只是CNC的操作有点不同。

1.参数的输入(PC→CNC)1)打开备份的NC参数文件。

sync键正确使用方法

sync键正确使用方法Sync键正确使用方法。

Sync键是现代电子设备中常见的一个功能键,它可以帮助用户在不同设备之间同步数据,方便用户在不同设备上都能够获取到最新的信息。

正确地使用Sync键可以提高工作效率,避免信息丢失和混乱。

下面将介绍一些关于Sync键正确使用的方法,希望能够帮助到大家。

首先,确保你的设备已经连接到互联网。

Sync功能需要设备能够连接到互联网才能正常工作,因此在使用Sync功能之前,确保你的设备已经连接到了可靠的网络,并且能够正常访问互联网。

如果你的设备无法连接到互联网,那么Sync功能将无法正常工作。

其次,登录你的账号并启用Sync功能。

大多数设备都需要用户登录自己的账号才能够使用Sync功能,因此在使用Sync功能之前,确保你已经登录了自己的账号,并且已经启用了Sync功能。

如果你还没有登录账号或者没有启用Sync功能,那么你需要先进行这些操作,才能够正常使用Sync功能。

接下来,选择你需要同步的数据。

在启用了Sync功能之后,你需要选择你希望同步的数据。

不同的设备和应用程序可能提供不同的同步选项,你可以根据自己的需求进行选择。

通常来说,你可以选择同步你的文件、联系人、日历、书签等数据,确保这些数据能够在不同设备之间同步更新。

然后,定期检查同步状态。

一旦你启用了Sync功能并选择了需要同步的数据,那么你需要定期检查同步状态,确保数据能够正常同步。

有时候,由于网络问题或者其他原因,数据可能无法正常同步,这时你需要及时发现并解决这些问题,确保数据能够正常同步更新。

最后,注意同步过程中的安全性。

在使用Sync功能的过程中,你需要注意数据的安全性。

确保你的设备和网络都是安全的,避免数据被盗取或篡改。

另外,你还需要注意隐私保护,确保你同步的数据不会被泄露给未经授权的人。

总之,Sync功能可以帮助我们在不同设备之间同步数据,提高工作效率。

正确地使用Sync功能可以避免信息丢失和混乱,确保我们能够随时随地获取到最新的信息。

宏基笔记本鼠标和键盘工作频率如何同步

我们必须让USB接收器与无线电鼠标和键盘的工作频率同步才能正常使用,宏基笔记本鼠标和键盘工作频率同步的方法1、将USB接收器插入其中一个可用的USB端口。

2、按下USB接收器上的按钮打开同步模式。

当进入同步模式时,LED指示灯闪烁蓝色。

3、按下鼠标的同步按钮,使鼠标和USB接收器同步。

4、再次按下USB接收器上的同步按钮,指示灯闪烁蓝色,按下键盘同步按钮,使其与接收器同步。

5、现在,您的鼠标和键盘应该与您的计算机同步了,应该已经可以正常使用了。

宏基是谁?宏碁公司由斯坦·施于1976年创立,时名“多技术国际公司”,当时该公司主要在台湾当地市场进行微处理机的开发和商业化。

现在,该公司制造和销售一系列桌式和笔记本个人电脑,以及相关设备与软件,它不仅面向台湾市场,而且面向全世界。

我们着重分析考察宏基跃入国际市场后的发展情况,并介绍一些重大的个人电脑革新情况。

宏基1997年收入为607亿元新台币(相当于22亿美元)。

宏基已成为台湾最大的名牌出口商,它还是世界第八大个人电脑公司。

在中东、东南亚、非洲以及南美地区,宏基是排名老大的 PC品牌。

该公司的业务范围遍及44个国家,产品出口到100多个国家,雇佣员工达2300人。

宏基就是单纯做电脑的吗?宏基公司[1]由斯坦.施于1976年创立,时名“多技术国际公司”,当时该公司主要在台湾当地市场进行微处理机的开发和商业化。

现在,该公司制造和销售一系列桌式和笔记本个人电脑,以及相关设备与软件,它不仅面向台湾市场,而且面向全世界。

我们着重分析考察宏基跃入国际市场后的发展情况,并介绍一些重大的个人电脑革新情况。

宏基1997年收入为607亿元新台币(相当于22亿美圆)。

宏基已成为台湾最大的名牌出口商,它还是世界第八大个人电脑公司。

在中东、东南亚、非洲以及南美地区,宏基是排名老大的 PC品牌。

该公司的业务范围遍及44个国家,产品出口到100多个国家,雇佣员工达2300人。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

Network interface

Synchronizing unit

External depth for trigger period calculations may be input

Synchronizing unit

The Synchronizing unit provides one output and two inputs for each echo sounder: • Trigger signal (output): tells the echo sounder when to transmit.. • Ready to transmit signal (input): communicates when the echo sounder is ready for the next ping • Transmitting signal (input): tells the Synchronizing Unit when the echo sounder is transmitting.

Synchronizing unit

Software: • Network based SU operator SW may be run on any PC. • System setup • System monitoring When setup, SU will continue to trig the echo sounders if the operator SW is closed.

Synchronizing unit

System setup

To be able to change any installation settings: Press “Allow modification” and input correct password

Synchronizing unit

Synchronizinபைடு நூலகம் unit

The Synchronizing Unit system consists of two main components: • A Workstation PC running the Synchronizing Unit (SU) application. • A Synchronizing Unit that interfaces with the echo sounders.

Synchronizing unit

Inside SU16

One pr echo sounder

O01-

I00 I01 I02 I03 I04 I05

-O15

Synchronizing unit

Inside SU16 cabinet

Main fuse

Synchronizing unit

W249A SU 16 synchronization interface

Approximate sound speed: Used for travel time calculations.

Synchronizing unit

Settings->Installation->Installation settings

Password: simrad0

To add or remove echo sounders from this list:

For each echo sounder to be connected: • • • • Read their manuals and find info: Which output signals are available, Trig, CTS and On/OFF Signal level: TTL or RS232 Impedance

Synchronizing unit

CAUTION! Always power up the Synchronizing Unit before other echo sounders are turned on to avoid accidental pinging. Trigger outputs are undefined during power-up (first 20 seconds) and signal levels could potentially be interpreted as trigger pulse by the echo sounders until signal levels have settled.

Settings->System settings…

Depth datagrams from echo sounder

Sync units‟s IP address and port number

Supported depth datagram formats: • NMEA depth (DBS, input datagram) • NMEA DPT (input datagram) • EAx: Single beam depth (EA 500 input datagram) • EM Depth „D‟: Multibeam depth (e.g. EM 120, EM 1002, EM 3000, EM 3002) • EM Depth „X‟: Multibeam depth (e.g. EM 122, EM 710) • EM Depth „E‟: Single beam depth (e.g. EA 600)

Synchronizing unit

Realtime trigger display

Trigger Transmit and busy Trigger

Ready

Yellow line separates the trigger groups

OS38 is busy much longer than EM 710 and determines the ping rate

Synchronizing unit

Operation: • • • SU controls pinging of each echo sounder. SU receives ready signals from echo sounders, but, if no status signals from echo sounders, SU may estimated ping time period.

Synchronizing unit

How to assign echo sounders to trigger groups

If some echo sounders shall ping several times before next instrument, make many equal groups

Synchronizing unit

Settings->Installation->Installation settings

Mark the echo sounders that are actually connected to the SU. Add new echo sounder if it is not already in the list.

• •

• • • • •

Avoid interference. Schedules the echo sounders transmit times.

16 trigger groups. Groups are triggered consecutively. Any number of echo sounders in a group (zero or more). Echo sounders in a group are triggered simultaneously. Optimizes timing: Transmit duration of each group is dependent on the measured active period for each echo sounder.

Synchronizing unit

Diagnostic tool

Shows signal level and pulses on each input and output signal. (Green = 5v(high)) Module and pin numbers refer to physical connections inside the SU. Terminal ID refer to selections in the installation settings.

Synchronizing unit

System control Push to pause sync.

Synchronizing unit

System status

Incoming depth status Override incoming depth

Depth is available

Synchronizing unit

Is signal active high or low?

Output trigger pulse setup: Check echo sounder manual.

Synchronizing unit

Not used 6 5 4 Trig In (CTS/RTT) 3 2 1 Transmitting (input) Trig Out

Gnd

Synchronizing unit

W249A SU 16 synchronization interface explanation

Synchronizing unit

Which group is active at the moment Empty groups are skipped