Xilinx-FPGA配置的一些细节

Xilinx spartan3e FPGA掉电配置及应用程序引导

Xilinx spartan3e FPGA掉电配置及应用程序引导Xilinx公司的spartan3e开发板上面有丰富的外围器件,就存储器来说有一个16M并行flash,一个4Mbits串行flash,还又一个64M的DDR,在嵌入式开发中,一般我们可能会在FPGA中嵌入cpu软核,让C语言程序在里面运行。

这就涉及到FPGA配置文件的引导,如果C语言程序太大,需要在DDR里面运行的话也涉及到应用程序的引导的问题。

我刚接触到xinlinx的spartan3e开发板时,只会将FPGA配置文件(.bit)直接通过JTAG口下载到芯片里。

后来编写的程序大了,如果将程序直接放到内部的RAM里面就装不下了,这时就只有将程序放到DDR里面运行,如果仅仅是调试应用程序不需要重启开发板后程序也可以运行,那么可以直接用EDK里面的XDM工具通过dow命令直接下载到DDR里面,然后就可以执行了。

但是但我们的应用程序和硬件配置调试通过,达到了我们的要求以后我们就想到可不可以将让程序在板子上电时就可以自动运行呢。

因为FPGA是掉电要丢失的,重新上电就必须重新配置。

我们通过查找相关资料,找到了解决烧写问题的解决办法。

首先是配置文件的烧写。

spartan3e提供了3个掉电不丢失的外部存储器,就是上面提到的并行flash,串行flash和Flash PROM。

配置文件都可以烧写到其中任何一个储存器里面。

但是,在我看来,一般的配置问件都是烧写到Flash PROM里面。

烧写方法有很多,可以用Xilinx公司的专门的烧写.mcs文件的工程烧写,也可以用iMPACT烧写。

一般用iMPACT工具烧写,烧写过程如下:打开iMPACT,弹出新建工程时选择Cancle,然后双击窗口左边的PROM File Formater如下图:弹出的窗口中选择Xilinx PROM文件格式选择mcs,PROM File name为:test.mcs,选择好保存路径点击下一步如下图:上步中点击Next,Select a PROM(bits)选择xcf->xcf04s,点击Add,然后点下一步如下图:上图中点击Next后出现窗口中点击filinsh,弹出消息框点OK,会有一个选择bit问件的窗口,选择一个已经编写好的EDK或者ISE工程生成的.bit文件,OK后提示是否加入其他器件,选择NO,然后双击窗口右边的Generate File,生成.mcs文件如下图所示:然后,双击Boundary Scan,在中间空白处,点击鼠标右键,选择Initialize chain,弹出的第一个窗口中选择Bypass,第二个选择刚才生成的.mcs文件,第三个也选择Bypass,然后选中中间那个模块,点击窗口左下角的program如下图:弹出窗口中选中OK就可以了,烧写完后会看到,Program Successful 提示。

fpga主要参数

fpga主要参数FPGA(Field-Programmable Gate Array)是一种可编程逻辑器件,具有灵活可重新配置的硬件特性。

它可以被程序员用于实现特定的电路功能,适用于各种不同的应用领域。

在选择使用FPGA时,有一些主要参数需要考虑。

以下是一些重要的FPGA参数及其详细说明。

1.逻辑单元数量:逻辑单元是FPGA的基本构建块,用于实现不同的逻辑功能。

逻辑单元的数量决定了FPGA的运算能力和复杂性。

当应用需要进行大规模的并行计算时,逻辑单元数量是一个关键参数。

2. 查找表数量:查找表(Look-Up Table,LUT)是FPGA中最小的逻辑单元。

它可以存储逻辑函数,并在需要时提供输出。

查找表数量越大,FPGA的灵活性就越高,可以实现更复杂的逻辑功能。

3.存储单元数量:存储单元用于存储数据和程序。

它可以是寄存器、存储器或分布式RAM等形式。

存储单元的数量决定了FPGA的数据处理能力和存储容量。

对于需要大量数据存储的应用,存储单元数量是一个重要的考虑因素。

4.I/O接口数量:输入/输出(I/O)接口用于与其他外部设备进行数据交互。

I/O接口数量决定了FPGA连接外部设备的能力,如传感器、存储设备、网络接口等。

对于需要大量连接的应用,例如通信系统或数据采集系统,I/O接口数量是一个重要的指标。

5.时钟频率:时钟频率表示FPGA在单位时间内完成的操作次数。

它决定了FPGA的工作速度和响应性能。

高时钟频率可以使FPGA更快地执行计算任务,但对电路设计和功耗管理提出了更高的要求。

适当选择时钟频率可以平衡FPGA的性能和功耗。

6.资源利用率:资源利用率是指FPGA上实际使用的逻辑资源占总资源的比例。

对于系统设计,资源利用率越高,系统的性能就越好。

低资源利用率可能意味着设计不充分或存在冗余。

因此,在选择FPGA时,需要考虑资源利用率,以确保最佳性能和资源利用。

7.功耗:功耗是FPGA运行时所消耗的能量。

FPGA上电配置过程及状态分析

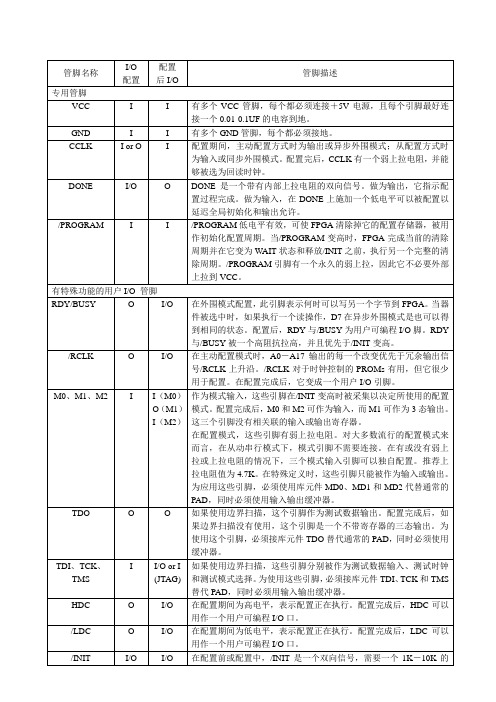

FPGA上电配置过程及状态分析1 概述在进行FPGA硬件设计时,引脚分配是非常重要的一个环节,特别是在硬件电路上需要与其他芯片通行的引脚。

Xilinx FPGA从上电之后到正常工作整个过程中各个阶段引脚的状态,会对硬件设计、引脚分配产生非常重要的影响。

这篇专题就针对FPGA从上电开始 ,配置程序,到正常工作整个过程中所有IO的状态进行分析。

从时间阶段可以分为两部分,第一阶段是从FPGA上电开始直到配置(Configuration)完成之前。

第二个阶段是配置完成之后,FPGA开始正常工作开始。

从引脚类型上分,可以分为三大类:第一类是普通的IO,其中又分为程序设计中使用到的IO和程序设计中没有使用的IO(即在ucf或者XDC文件中没有进行约束的IO);第二类是专用下载配置引脚(Dedicated Pins),这类引脚只用于专用的功能,包括有M[2:0]、TCK、TMS、PROGRAM_B、INIT_B等。

第三类为功能复用引脚,这类引脚在使用特定的功能时使用,例如在使用BPI配置模式时,D[00-31]和A[00-28]需要使用。

如果使用SYSMON 时,I2C_SDA和I2C_SCL需要使用。

但在当前没有使用该功能的情况下,功能复用引脚可以看成普通IO。

2 FPGA IO的基本结构在《IO输入输出的各种模式》介绍了处理器IO的各种输入输出模式以及原理,那么FPGA的IO是什么样的结构和原理?图 1为Xilinx文档中提供的IOB的内部结构,可以看出:在FPGA IOB内部,Pad输出之前,内置上下拉电阻。

且可以通过Passive Pull-up/Pull-down模块控制两个MOS管的导通与否来控制是否使能上下拉电阻。

内部连接Pad的分别有一个Input Buffer和Output Buffer。

其中Input Buffer对外应该始终呈现高阻状态,同时可以将Pad上的电平通过Input Buffer传到I1和I2,或者是下部的FF。

vivado布线参数

vivado布线参数

Vivado是Xilinx公司推出的一款集成化的FPGA设计软件,其中包含了布线功能。

在Vivado中,布线参数通常包括了一系列设置和选项,用于控制FPGA的布线过程以达到设计的性能、功耗和面积等要求。

以下是一些常见的Vivado布线参数:

1. 约束文件,约束文件是描述设计约束的文件,其中包括时序约束、布局约束等。

在Vivado中,可以通过约束文件来指定布线的一些参数,如时钟频率、时序要求等。

2. 布线策略,Vivado提供了多种布线策略,如快速布线、综合布线、时序驱动布线等。

不同的布线策略会影响到布线的速度和质量,设计者可以根据实际需求选择合适的布线策略。

3. 布线优化选项,Vivado中还提供了一些布线优化选项,如时序优化、布局优化、功耗优化等。

这些选项可以帮助设计者在布线过程中优化设计的性能和功耗。

4. 布线约束,除了约束文件外,Vivado还提供了一些布线约束选项,如布线分区约束、时序分组约束等。

这些约束可以帮助设

计者更精细地控制布线的过程。

5. 布线报告,Vivado会生成布线报告,其中包括了布线结果、时序分析、资源利用情况等信息。

设计者可以通过布线报告来评估

设计的性能和资源利用情况,从而调整布线参数以达到更好的设计

效果。

总的来说,Vivado的布线参数涵盖了约束文件、布线策略、布

线优化选项、布线约束和布线报告等方面,设计者可以通过合理设

置这些参数来控制和优化FPGA的布线过程,从而达到设计的性能和

功耗要求。

Xilinx-FPGA器件管脚说明doc

弱上拉

I/O

内部有弱上拉。可以随逻辑需要配置成输入或输出。在配置完成前,这些引脚有内部上拉电阻(25K-100K)至高电平。

在配置模式,这些引脚有弱上拉电阻。对大多数流行的配置模式来而言,在从动串行模式下,模式引脚不需要连接。在有或没有弱上拉或上拉电阻的情况下,三个模式输入引脚可以独自配置。推荐上拉电阻值为4.7K。在特殊定义时,这些引脚只能被作为输入或输出。为应用这些引脚,必须使用库元件MD0、MD1和MD2代替通常的PAD,同时必须使用输入输出缓冲器。

管脚名称

I/O

配置

配置

后I/O

管脚描述

专用管脚

VCC

I

I

有多个VCC管脚,每个都必须连接+5V电源,且每个引脚最好连接一个0.01-0.1UF的电容到地。

GND

I

I

有多个GND管脚,每个都必须接地。

CCLK

I or O

I

配置期间,主动配置方式时为输出或异步外围模式;从配置方式时为输入或同步外围模式。配置完后,CCLK有一个弱上拉电阻,并能够被选为回读时钟。

HDC

O

I/O

在配置期间为高电平,表示配置正在执行。配置完成后,HDC可以用作一个用户可编程I/O口。

/LDC

O

I/O

在配置期间为低电平,表示配置正在执行。配置完成后,LDC可以用作一个用户可编程I/O口。

/INIT

I/O

I/O

在配置前或配置中,/INIT是一个双向信号,需要一个1K-10K的外部上拉电阻。作为一个低电平有效输出,/INIT在电源稳定和清除内部配置内存期间保持低电平。作为一个低电平有效输入,/INIT能在开始配置前保持FPGA在内部WAIT状态。主动模式下,在/INIT变高后,器件将在WAIT状态保持30+300US。在配置期间,输出为低表示配置数据错误。当I/O有效后,/INIT为一个用户可编程I/O引脚。

XilinxFPGA介绍

目前FPGA芯片仍是基于查找表技术的,但其概念和性能已经远远超出查找表技术的限制,并且整合了常用功能的硬核模块(如块RAM、时钟管理和DSP)。

图1-1所示为Xilinx公司FPGA的内部结构示意图(由于不同系列的应用场合不同,所以内部结构会有一定的调整),从中可以看出FPGA芯片主要由 6部分组成:可编程输入输出单元、基本可编程逻辑单元、完整的时钟管理、嵌入块式RAM、丰富的布线资源、内嵌的底层功能单元和内嵌专用硬件模块。

图1-1 FPGA芯片的内部结构每个模块的功能如下:1.可编程输入输出单元(IOB)可编程输入/输出单元简称I/O单元,是芯片与外界电路的接口部分,完成不同电气特性下对输入/输出信号的驱动与匹配要求,提供输入缓冲、输出驱动、接口电平转换、阻抗匹配以及延迟控制等功能,其一般示意结构如图1-2所示。

FPGA内的I/O按组分类,每组都能够独立地支持不同的I/O标准。

通过软件的灵活配置,可适配不同的电气标准与I/O物理特性,可以调整驱动电流的大小,可以改变上、下拉电阻。

目前,I/O口的频率也越来越高,一些高端的FPGA 通过DDR寄存器技术可以支持高达2Gbps的数据速率。

外部输入信号可以通过IOB模块的存储单元输入到FPGA的内部,也可以直接输入FPGA 内部。

当外部输入信号经过IOB模块的存储单元输入到FPGA内部时,其保持时间(Hold Time)的要求可以降低,通常默认为0。

为了便于管理和适应多种电器标准,FPGA的IOB被划分为若干个组(bank),每个bank的接口标准由其接口电压VCCO决定,一个bank只能有一种VCCO,但不同bank的VCCO可以不同。

只有相同电气标准的端口才能连接在一起,VCCO 电压相同是接口标准的基本条件。

2.可配置逻辑块(CLB)CLB是FPGA内的基本逻辑单元。

CLB的实际数量和特性会依器件的不同而不同,但是每个CLB都包含一个可配置开关矩阵,此矩阵由4或6个输入、一些选型电路(多路复用器等)和触发器组成。

Xilinx-FPGA配置的一些细节

Xilinx-FPGA配置的一些细节Xilinx FPGA配置的一些细节2010年07月03日星期六 14:260 参考资料(1) Xilinx: Development System Reference Guide. dev.pdf, v10.1在Xilinx的doc目录下有。

(2) Xilinx: Virtex FPGA Series Configuration and Readback. XAPP138 (v2.8) March 11, 2005在Xilinx网站上有,链接/bvdocs/appnotes/xap p138.pdf(3)Xilinx: Using a Microprocessor to Configure Xilinx FPGAs via Slave Serial or SelectMAP Mode.XAPP502 (v1.5) December 3, 2007在Xilinx网站上有,链接/bvdocs/appnotes/xap p502.pdfGTS : 激活用户IO,之前都是高阻。

EOS : 表示配置结束DCI_MATCH : 表示所有的DCI(Digitally Controlled Impedance)控制器已经把内部电阻和外部参考电阻匹配完毕。

DCM_LOCK : 表示所有的DCM已经锁定。

这个选项默认是选中的。

因此,我们可以得出如下结论:(1)FPGA最后的Startup过程有8个周期,其中DONE变高仅仅是第4个周期。

因此,在DONE 变高之后还需要再给3个CCLK。

否则DONE虽然变高了,FPGA程序并没有正确运行。

(2)ISE会在设计中搜索用户是否使用了DCI,如果是,FPGA会使用2个周期的Start Up Phase,等待DCI匹配上。

即FPGA会在那儿等待,直到DCI匹配上。

如果我们在上位机读取了配置文件,获得了文件大小,我们把它写到负责加载V4的SP3里,然后CCLK时钟就不给了。

Xilinx7系列FPGA架构之器件配置(一)

Xilinx7系列FPGA架构之器件配置(一)引言:本系列博文描述7系列FPGA配置的技术参考。

作为开篇,简要概述了7系列FPGA的配置方法和功能。

随后的博文将对每种配置方法和功能进行更详细的描述。

本文描述的配置方法和功能适用于所有7系列家族器件,只有少数例外。

1.概述Xilinx®7系列FPGA通过将特定于应用程序的配置数据(位流)加载到内存中进行配置。

7系列FPGA可以主动从外部非易失性存储设备加载,也可以通过外部智能源(如微处理器、DSP处理器、微控制器、PC或板测试仪)被动进行配置。

在任何情况下,都有两个通用配置数据路径。

第一个是串行数据路径,这种情况需要最少的硬件管脚连接。

第二个数据路径是8位、16位或32位数据路径,用于更高性能或访问(或链接)行业标准接口,非常适合外部数据源,如处理器或x8或x16并行闪存。

与处理器和处理器外围设备一样,Xilinx FPGA可以在线重新编程,编程次数无限制。

由于Xilinx FPGA配置数据存储在CMOS配置锁存器(CCL)中,因此必须在断电后对其进行重新配置。

每次通过专用配置引脚将比特流加载到FPGA器件中。

这些配置引脚可以用作多种不同配置模式的接口:•主动-串行配置模式•从(或被动)-串行配置模式•主动-并行(SelectMAP)配置模式(x8和x16)•主动-并行(SelectMAP)配置模式(x8,x16和x32)•JTAG边界扫描模式•主动-串行SPI Flas配置模式(x1,x2,x4)•主动-字节BPI Flash配置模式(x8,x16),使用并行NOR Flash这些配置模式通过输入管脚M[2:0]设置不同的电平进行模式选择。

M2,M1和M0应该连接至DC电压常量,可以直接接GND或者VCCO_0或者通过上拉或下拉电阻(≤1kΩ)连接至GND或者VCCO_0。

上述几种配置模式中主或者从是以配置时钟管脚CCLK的方向为参考的。

fpga开发板使用手册

FPGA开发板使用手册一、硬件概述FPGA开发板是一种基于可编程逻辑器件(FPGA)的嵌入式系统开发板,它为电子工程师提供了一个高度灵活和可定制的平台,可用于开发各种数字系统,如通信、控制、数据处理等。

本手册旨在帮助用户了解和使用这款FPGA开发板,充分发挥其性能和功能。

二、开发板规格本开发板规格如下:1. 尺寸:90mm x 60mm x 1.6mm。

2. FPGA型号:Xilinx XC7020。

3. 内存容量:128MB DDR3。

4. 存储器:8GB eMMC。

5. 接口类型:USB 2.0,以太网 10/100Mbps,RS232等。

6. 电源电压:5V。

7. 重量:约15克。

三、硬件连接本开发板可通过以下方式与外围设备连接:1. USB接口:用于连接电脑进行编程和调试。

2. 以太网接口:用于连接网络。

3. RS232接口:用于连接其他串口设备。

4. GPIO接口:用于连接其他数字设备。

5. I2C接口:用于连接I2C总线设备。

6. SPI接口:用于连接SPI总线设备。

7. HDMI接口:用于显示输出。

8. SRAM接口:用于高速数据存储。

9. UART接口:用于串口通信。

四、FPGA设计工具安装与使用FPGA设计工具是用于编写和调试FPGA逻辑代码的软件环境。

本开发板支持的FPGA设计工具有Xilinx Vivado和Intel Quartus等。

用户需要根据所选工具,下载并安装相应的软件,然后按照软件说明进行安装和配置。

在安装过程中,请注意选择与本开发板兼容的版本和配置。

安装完成后,用户可以使用FPGA设计工具编写逻辑代码,并通过开发板的接口将代码下载到FPGA中运行。

五、FPGA设计基本原则在FPGA设计中,需要遵循以下基本原则:1. 模块化设计:将复杂问题分解为多个简单的子问题,逐个解决,便于调试和维护。

2. 尽量使用硬件加速器:利用FPGA的并行处理能力,提高系统性能。

xilinxfpga引脚功能详细介绍

Xilinx F PGA引脚功能详细介绍注:技术交流用,希望对大家有所帮助。

IO_LXXY_# 用户10引脚XX代表某个Bank内唯一的一对引脚,Y=[PIN]代表对上升沿还是下降沿敏感,#代表bank 号2.IO_LXXY_ZZZ_#多功能引脚ZZZ代表在用户IO的基本上添加一个或多个以下功能。

Dn: I/O (在readback期间),在selectMAP或者BPI模式下,D[15:0]配置为数据口。

在从SelectMAP读反馈期间,如果RDWR_B=1,则这些引脚变成输出曰。

配置完成后,这些引脚又作为普通用户引脚。

D0_DIN_MISO_MISOl: I,在并口模式(SelectMAP/BPI)下,DO 是数据的最低位,在Bit-serial模式下,DIN是信号数据的输入;在SPI模式下,MISO是主输入或者从输出;在SPI*2或者SPI*4模式下,MISO1是SPI总线的第二位。

D1_M1SO2, D2_MISO3:I,在并口模式下,D1和D2是数据总线的低位;在SPI*4模式下,MISO2和MISO3是SPI总线的MSBsoAn: 0, A[25:0]为BPI模式的地址位。

配置完成后,变为用户I/O 口。

AWAKE: O,电源保存挂起模式的状态输出引脚。

SUSPEND是一个专用引脚,AWAKE 是一个多功能引脚。

除非SUSPEND模式被使能,AWAKE被用作用户I/O。

MOSI_CSI_B_MISOO: I/O,在SPI模式下,主输出或者从输入;在SelectMAP模式下, CSI_B 是一个低电平有效的片选信号;在SPI*2或者SPI*4的模式下,MISOO是SPI总线的第一位数据。

FCS_B: 0, BPI flash 的片选信号。

FOE_B: O, BPI flash的输出使能信号FWE_B: O, BPI flash的写使用信号LDC: O, BPI模式配置期间为低电平HDC: O, BPI模式配置期间为高电平CSO_B: O,在并口模式下,工具链片选信号。

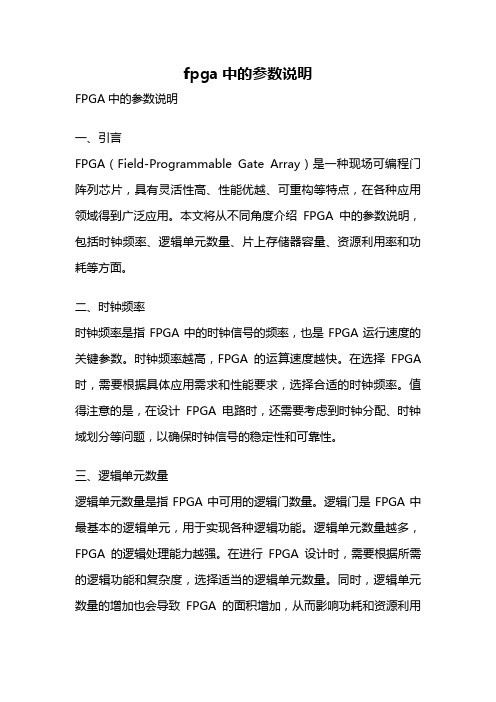

fpga中的参数说明

fpga中的参数说明FPGA中的参数说明一、引言FPGA(Field-Programmable Gate Array)是一种现场可编程门阵列芯片,具有灵活性高、性能优越、可重构等特点,在各种应用领域得到广泛应用。

本文将从不同角度介绍FPGA中的参数说明,包括时钟频率、逻辑单元数量、片上存储器容量、资源利用率和功耗等方面。

二、时钟频率时钟频率是指FPGA中的时钟信号的频率,也是FPGA运行速度的关键参数。

时钟频率越高,FPGA的运算速度越快。

在选择FPGA 时,需要根据具体应用需求和性能要求,选择合适的时钟频率。

值得注意的是,在设计FPGA电路时,还需要考虑到时钟分配、时钟域划分等问题,以确保时钟信号的稳定性和可靠性。

三、逻辑单元数量逻辑单元数量是指FPGA中可用的逻辑门数量。

逻辑门是FPGA中最基本的逻辑单元,用于实现各种逻辑功能。

逻辑单元数量越多,FPGA的逻辑处理能力越强。

在进行FPGA设计时,需要根据所需的逻辑功能和复杂度,选择适当的逻辑单元数量。

同时,逻辑单元数量的增加也会导致FPGA的面积增加,从而影响功耗和资源利用率。

四、片上存储器容量片上存储器容量是指FPGA中可用的存储器容量。

片上存储器用于存储数据和中间结果,在FPGA设计中起到关键作用。

片上存储器容量的大小直接影响到FPGA的数据处理能力和性能。

较大的片上存储器容量可以提高FPGA的数据缓存能力,减少对外部存储器的访问次数,从而提高系统的运行效率。

五、资源利用率资源利用率是指FPGA中各种资源的利用程度。

FPGA中的资源包括逻辑单元、片上存储器、DSP(Digital Signal Processing)模块等。

资源利用率越高,说明FPGA的资源利用效率越高,系统的性能也会相应提高。

在进行FPGA设计时,需要合理利用各种资源,以提高系统的性能和效率。

六、功耗功耗是指FPGA芯片在工作过程中所消耗的电能。

功耗大小直接影响到FPGA的散热需求和系统的稳定性。

xilinx_简化FPGA配置设计过程

供应来源

尽管商用 Flash 供应商很多,但却存在两个隐患:

WP253 (v1.0.1) 2006 年 8 月 7 日

/cn

3

R

配置不仅仅只是连接

增值功能

Platform Flash 提供商用 Flash 不具备的一系列增值功能:压缩、 JTAG 支持、设计修 订 (Design revisioning)、轻松访问未使用的存储空间和上电可靠性。

访问未使用的存储空间

大多数 FPGA 比特流都不会填满 PROM 的所有存储器。设计人员可通过 JTAG 接口访 问 Platform Flash PROM 内未使用的存储空间。因此,任何未使用的存储空间都可供 处理器暂存或启动代码使用(请参阅 [ 参考文件 4]、[ 参考文件 5] 和 [ 参考文件 6])。

配置不仅仅只是连接

FPGA 配置不仅仅只是连接到 PROM。这款整体解决方案涉及软件、硬件与芯片,其 成本包括在以下方面所花费的成本:电路板面积、配置速度、供应来源、其他增值功 能,当然还有易用性。如果在开始时没有充分考虑这些因素,可能会给最终设计带来 额外的成本,甚至会拖延最终产品的生产发布。

总拥有成本

将 Spartan-3E 器件与并行商用 Flash 配合使用时,最高配置速度为 6 MHz。相比之下, 使用 Spartan-3E 器件时,Platform Flash 的最大传输速率为 264 Mb/s (33 MHz x 8 I/O)。

XILINX FPGA选型详解

SLICEM中的函数生成器(LUTs)可以实现为同步RAM资源,

也称为分布式RAM。一个SLICEM中的多个LUT可以以 各种方式组合在一起,以存储每个SLICEM最多512位的 大量数据。多个切片可以组合起来创建更大的内存。

Maximum Distributed

RAM

Block RAM/FIFO w/ECC

存储的资源介绍可以参考:UG57CMT: 一个CMT包含一个混合模式时钟管理器 (MMCM)和两个锁相环;MMCM是用于 大范围频率的频率合成的主要块,并作为 外部或内部时钟的抖动滤波器,以及 deskew时钟和其他功能的广泛范围。PLL 的主要目的是为PHY I/Os提供时钟,但也 可以用于以有限的方式对设备中的其他资 源进行时钟。

基于SRAM的FPGA

这类产品是基于SRAM结构的可再配置型器件,通电时要将配 置数据读入片内SRAM中,配置完成就可进入工作状态。断电 后SRAM中的配置数据丢失,FPGA内部逻辑关机也随之消失, 这种基于SRAM的FPGA可反复使用。

01

反熔丝FPGA

采用反熔丝编程技术的FPGA内部具有反熔丝阵 列开关结构,其逻辑功能的定义由专用编程器根 据设计实现所给出的数据文件,对其内部反熔丝 真累进行烧录,从而使器件实现相应的逻辑功能。 这种器件的缺点是只能一次性编程,有点是具有 高抗干扰性和低功耗,适合于要求高可靠性、高 保密性的定型产品。

• Spartan7系列是7系列中拥有最低的价格、最低的功耗、最小的尺寸以及最低的设计难度,一些低端应用中极为合适 • Artix7系列是7系列中相对Spartan7系列则增加了串行收发器和DSP功能,其逻辑容量也更大,适合逻辑一些稍微复杂

的中低端应用

• Kintex7系列是7系列中在所有系列中拥有最佳的性价比,无论是硬核数量还是逻辑容量,都能满足中低端、以及部 分高端应用需求

FPGA开发全攻略——配置电路

FPGA开发全攻略——配置电路展开全文配置电路FPGA配置方式灵活多样,根据芯片是否能够自己主动加载配置数据分为主模式、从模式以及JTAG模式。

典型的主模式都是加载片外非易失( 断电不丢数据) 性存储器中的配置比特流,配置所需的时钟信号( 称为CCLK) 由FPGA内部产生,且FPGA控制整个配置过程。

从模式需要外部的主智能终端( 如处理器、微控制器或者DSP等) 将数据下载到FPGA中,其最大的优点就是FPGA 的配置数据可以放在系统的任何存储部位,包括:Flash、硬盘、网络,甚至在其余处理器的运行代码中。

JTAG 模式为调试模式,可将PC 中的比特文件流下载到FPGA中,断电即丢失。

此外,目前赛灵思还有基于Internet 的、成熟的可重构逻辑技术System ACE解决方案。

(1) 主模式在主模式下,FPGA上电后,自动将配置数据从相应的外存储器读入到SRAM中,实现内部结构映射;主模式根据比特流的位宽又可以分为:串行模式( 单比特流) 和并行模式( 字节宽度比特流) 两大类。

如:主串行模式、主SPI Flash 串行模式、内部主SPI Flash串行模式、主BPI 并行模式以及主并行模式,如图5-19所示。

(2) 从模式在从模式下,FPGA 作为从属器件,由相应的控制电路或微处理器提供配置所需的时序,实现配置数据的下载。

从模式也根据比特流的位宽不同分为串、并模式两类,具体包括:从串行模式、JTAG模式和从并行模式三大类,其概要说明如图5-20所示。

(3)JTAG模式在JTAG模式中,PC和FPGA通信的时钟为JTAG接口的TCLK,数据直接从TDI进入FPGA,完成相应功能的配置。

图5-19 常用主模式下载方式示意图图5-20 常用的从模式下载方式示意图目前,主流的FPGA芯片都支持各类常用的主、从配置模式以及JTAG,以减少配置电路失配性对整体系统的影响。

在主配置模式中,FPGA自己产生时钟,并从外部存储器中加载配置数据,其位宽可以为单比特或者字节;在从模式中,外部的处理器通过同步串行接口,按照比特或字节宽度将配置数据送入FPGA芯片。

ch4_1_Xilinx FPGA管脚分配要点

Xilinx FPGA管脚分配要点

特殊引脚(specific pins)

GC类管脚指诸如IO_L1P_GC_LC等带有GC的管脚。GC类全 局时钟管脚可以作为普通IO使用; 非GC类全局时钟管脚不可以作时钟使用; N类型GC全局时钟管脚不可以作为单端时钟输入管脚;

差分时钟输入时必须使用配对的(N类型和P类型)GC类全局

时钟IO管脚配置给DCM(差分时钟模块)的CLKIN_N_IN和 CLKIN_P_IN(P类型/N类型指的是例如IO_L1P_GC_LC或 IO_L1N_GC_LC,这里的L1P和L1N标识这个管脚是P类型还 是N类型。)

附:信号传输技术,区别于传统的一根信号线一根地线的做法 (后者为单端传输),差分传输在这两根线上都传输信号,这两个信号的振 幅相等,相位相反。差分传输的信号能够对外部干扰起到很强的抗干扰能力。 Xilinx FPGA的时钟输入方式有单端时钟和差分时钟两种形式。

fpga主要参数

fpga主要参数FPGA,全称为:Field Programmable Gate Array(场可编程门阵列),是一种基于可编程逻辑芯片的数字电路设计工具。

在这种芯片中,逻辑元件是可编程的,可以根据设计人员的需要进行配置和调试,以完成各种各样的数字逻辑电路功能。

因为其灵活、高效、可重构的特点,FPGA被广泛应用于各种领域,如通信、控制、嵌入式系统等。

在进行 FPGA 开发时,需要对一系列的参数进行评估和选择,以满足特定的设计需求。

下面将从 FPGA 主要参数这一话题出发,一步步阐述这些参数的意义和作用。

1. 逻辑单元数目逻辑单元(Logic Element)是 FPGA 中可编程的基本逻辑单元,通常包括器件、开关和连接的引脚。

逻辑单元数量决定了 FPGA 能够实现的逻辑电路规模和复杂度。

对于一些简单的应用,逻辑单元数目较少的 FPGA 便能胜任,但对于高级设计,需要更多、更强大的逻辑单元。

2. 存储单元数目存储单元(Memory Cell)是 FPGA 可编程的存储单元,通常用于储存数据、状态信息等,根据存储单元的数目,决定了 FPGA 能够存储的信息量和运算速度等。

3. I/O 数量I/O 即输入输出接口,通向 FPGA 的信号口数目影响着系统的输入、输出效率。

I/O 数量应适合您的应用,否则将导致信号传送瓶颈和性能下降。

4. 时钟频率和时钟延迟时钟频率和延迟用于确定 FPGA 的时序特性和数据传输速率。

时钟频率从 100MHz 到更高的数值可用于 FPGAs 的运行。

时钟延迟决定了 FPGA 系统处理许多时序信息的速度。

5. 功耗功耗取决于 FPGA 的规格、工作电压、频率和负载。

功率管理与散热都是必要的,以确保 FPGA 运作稳定而不发热或过热。

6. 资源使用率资源使用率反映了 FPGA 中可用资源使用的效率。

当资源使用率越高时,FPGA 效率越低,因此,在设计时应保持适当的资源使用率。

综上所述,FPGA 设计需要评估许多参数来满足其特定应用需要。

XilinxFPGA的PROM配置

*ilin*FPGA的P ROM配置作者:枪手2007年8月16号1. 建立工程,假设VHDL,UCF2. 生成PROM 文件。

在图中选择P repare a PROM 3文件,综合,执行。

file, 然后点ne*t.iPaCI-Prepare PROI FilesI want to target aXiling PKDM○Generic Parallel PROM〇3rd-Farty SFI PROM〇PROM Supporting Multiple Design Versions;Spartan3E MultiBootPROM File FormatMCS TEK UFP('C" format)〇EXO 〇BIN 〇ISC〇HEX Swap BitsChecksum Fill Value(2Hex Digits):FFFROM File Name:led flow|Location: E:\xilinx'lab'led flow' Browse.< Back Next>Cancel在上图中做图所显示的选择,点NE*T4在上图中选择所用开发板上的 P ROM,SP3E 用*CFO4S, 点 ADD, 添加到列表中。

然后点 ne*t,出现file generation summary!5iPhCT- Specify Xilinx PROI DeviceAuto Select PROMEnable RevisioningNumber of Revisions:Enable CompressionSelect a FROM: xcfxef ⁰4sPosition 0[524288]Part Namexef04sAddDelete All<BackNext > CanceliIPACT-File Generation Suary You have entered following information:PROM Type:File FormatFill YaluePROM filenameNumber of PFOMsPositi on Part Name [0 xcf04s Serialm cs FFled flow 1Click“Finish” to start adding device files.<Eack Finish Cancel确定是不是和所选择的一致,点finish。

FPGA管脚分配时需注意的一些事项(以xilinx xc4vsx55为例)

FPGA管脚分配时需注意的一些事项(以xilinx xc4vsx55为例)FPGA管脚分配时需注意的一些事项(以xilinx xc4vsx55为例)平台:XC4VSX55 ISE10.1设计过FPGA的原理图,看FPGA的手册,说管脚的分配问题,如时钟管脚要用GC类管脚,而且单端时钟输入时要用P类型的管脚,不能用N类型管脚等等。

一直以来都没有试验过,今天试验一把,以求各种验证。

1)GC类全局时钟管脚是否可用作普通IO使用?所谓GC类管脚,就是在管脚的称是诸如IO_L1P_GC_LC等带有GC的管脚。

其实手册中说的是GC类管脚可以用作IO的,但在《Xilinx FPGA开发实用教程》(清华出版社)574页倒数第八行提到:“所有从全局时钟管脚输入的信号必须经过IBUF元,否则在布局布线时会报错”,于是今天我试了一下,将某一GC 类管脚分配给一个普通的输入口(也试验了分配给一个普通的输出口),经布局布线后,未出错。

因此得出结论:GC类全局时钟管脚可以作为普通IO使用。

(不知道是不是我对书中提到的全局时钟管脚理解有误,如果是,请网友别拍我,敬请留言指正)2)非GC类全局时钟管脚是否可以作时钟使用?其实至于说能否作为时钟使用,这里有另一层函义。

当然,如果你把一个普通IO口配置成输入口,就把它的输入信号作为时钟,那是没问题的。

但我们一般不这么做,因为时钟信号对于我们来说是一个很重要的信号,因此FPGA在内部会有特殊照顾,如果你使用FPGA传门为时钟预留的管脚,并作一些处理,那么你的时钟对于各种模块的时延是可以忽略的,因为时钟在布线时是单独走的一层,而如果你就仅用普通IO 的话,经过FPGA内部布局布线后,从它的输到,再到各个使用时钟的地方,有的线长,有的线短,它的时延将是不一样的。

这些东西还是看一些FPGA结构的内容吧。

在xilinx里有专门的DCM IP核可供调用,在ISE中执行project——>New Source——>IP(CORE Generator & Architecture Wizard)——>FPGA Features andDesign——>Clocking——>Virtex-4——>Single DCM ADV v9.1i,可得如下界面:需要特别注意的是CLKIN Source需要选择是External还是Internal,各自生成的源文件如下:==========================选择External=========================`timescale 1ns / 1psmodule clk_test(CLKIN_IN,CLKIN_IBUFG_OUT,CLK0_OUT,LOCKED_OUT);input CLKIN_IN;output CLKIN_IBUFG_OUT;output CLK0_OUT;output LOCKED_OUT;wire CLKFB_IN;wire CLKIN_IBUFG;wire CLK0_BUF;wire GND_BIT;wire [6:0] GND_BUS_7;wire [15:0] GND_BUS_16;assign GND_BIT = 0;assign GND_BUS_7 = 7'b0000000;assign GND_BUS_16 = 16'b0000000000000000;assign CLKIN_IBUFG_OUT = CLKIN_IBUFG;assign CLK0_OUT = CLKFB_IN;IBUFG CLKIN_IBUFG_INST (.I(CLKIN_IN),.O(CLKIN_IBUFG));BUFG CLK0_BUFG_INST (.I(CLK0_BUF),.O(CLKFB_IN));DCM_ADV DCM_ADV_INST (.CLKFB(CLKFB_IN), .CLKIN(CLKIN_IBUFG),.DADDR(GND_BUS_7[6:0]),.DCLK(GND_BIT),.DEN(GND_BIT),.DI(GND_BUS_16[15:0]),.DWE(GND_BIT),.PSCLK(GND_BIT),.PSEN(GND_BIT),.PSINCDEC(GND_BIT),.RST(GND_BIT),.CLKDV(),.CLKFX(),.CLKFX180(),.CLK0(CLK0_BUF),.CLK2X(),.CLK2X180(),.CLK90(),.CLK180(),.CLK270(),.DO(),.DRDY(),.LOCKED(LOCKED_OUT),.PSDONE());defparam DCM_ADV_INST.CLK_FEEDBACK = "1X";defparam DCM_ADV_INST.CLKDV_DIVIDE = 2.0;defparam DCM_ADV_INST.CLKFX_DIVIDE = 1;defparam DCM_ADV_INST.CLKFX_MULTIPLY = 4;defparam DCM_ADV_INST.CLKIN_DIVIDE_BY_2 = "FALSE";defparam DCM_ADV_INST.CLKIN_PERIOD = 16.129;defparam DCM_ADV_INST.CLKOUT_PHASE_SHIFT = "NONE";defparam DCM_ADV_INST.DCM_AUTOCALIBRATION = "TRUE";defparam DCM_ADV_INST.DCM_PERFORMANCE_MODE = "MAX_SPEED";defparam DCM_ADV_INST.DESKEW_ADJUST = "SYSTEM_SYNCHRONOUS";defparam DCM_ADV_INST.DFS_FREQUENCY_MODE = "LOW";defparam DCM_ADV_INST.DLL_FREQUENCY_MODE = "LOW";defparam DCM_ADV_INST.DUTY_CYCLE_CORRECTION = "TRUE";defparam DCM_ADV_INST.FACTORY_JF = 16'hF0F0;defparam DCM_ADV_INST.PHASE_SHIFT = 0;defparam DCM_ADV_INST.STARTUP_WAIT = "FALSE";endmodule==========================选择Internal=========================`timescale 1ns / 1psmodule clk1_test(CLKIN_IN,CLK0_OUT,LOCKED_OUT);input CLKIN_IN;output CLK0_OUT;output LOCKED_OUT;wire CLKFB_IN;wire CLK0_BUF;wire GND_BIT;wire [6:0] GND_BUS_7;wire [15:0] GND_BUS_16;assign GND_BIT = 0;assign GND_BUS_7 = 7'b0000000;assign GND_BUS_16 = 16'b0000000000000000;assign CLK0_OUT = CLKFB_IN;BUFG CLK0_BUFG_INST (.I(CLK0_BUF),.O(CLKFB_IN));DCM_ADV DCM_ADV_INST (.CLKFB(CLKFB_IN),.CLKIN(CLKIN_IN),.DADDR(GND_BUS_7[6:0]),.DCLK(GND_BIT),.DEN(GND_BIT),.DI(GND_BUS_16[15:0]),.DWE(GND_BIT),.PSCLK(GND_BIT),.PSEN(GND_BIT),.PSINCDEC(GND_BIT),.RST(GND_BIT),.CLKDV(),.CLKFX(),.CLKFX180(),.CLK0(CLK0_BUF),.CLK2X(),.CLK2X180(),.CLK90(),.CLK180(),.CLK270(),.DO(),.DRDY(),.LOCKED(LOCKED_OUT),.PSDONE());defparam DCM_ADV_INST.CLK_FEEDBACK = "1X";defparam DCM_ADV_INST.CLKDV_DIVIDE = 2.0;defparam DCM_ADV_INST.CLKFX_DIVIDE = 1;defparam DCM_ADV_INST.CLKFX_MULTIPLY = 4;defparam DCM_ADV_INST.CLKIN_DIVIDE_BY_2 = "FALSE";defparam DCM_ADV_INST.CLKIN_PERIOD = 16.129;defparam DCM_ADV_INST.CLKOUT_PHASE_SHIFT = "NONE";defparam DCM_ADV_INST.DCM_AUTOCALIBRATION = "TRUE";defparam DCM_ADV_INST.DCM_PERFORMANCE_MODE = "MAX_SPEED";defparam DCM_ADV_INST.DESKEW_ADJUST = "SYSTEM_SYNCHRONOUS";defparam DCM_ADV_INST.DFS_FREQUENCY_MODE = "LOW";defparam DCM_ADV_INST.DLL_FREQUENCY_MODE = "LOW";defparam DCM_ADV_INST.DUTY_CYCLE_CORRECTION = "TRUE";defparam DCM_ADV_INST.FACTORY_JF = 16'hF0F0;defparam DCM_ADV_INST.PHASE_SHIFT = 0;defparam DCM_ADV_INST.STARTUP_WAIT = "FALSE";endmodule比较以上两段代码,区别在于选择是External时CLKIN经过了IBUFG才到的DCM_ADV,而选择Internal 的CLKIN则直接到了DCM_AV,而IBUFG就是原语“全局时钟缓冲”单元,我们使用时要选择External,只有当我们的级联两个DCM模块时,直接与外面相连的选External,而另一个选择Internal。

xilinx 7系列fpga ddr3硬件设计规则

xilinx 7系列fpga ddr3硬件设计规则本文档旨在为使用Xilinx 7系列FPGA的设计师提供DDR3硬件设计规则的指导,确保设计的性能和可靠性满足要求。

2.DDR3简介DDR3(Double Data Rate 3)是一种高性能、高带宽的内存接口标准。

Xilinx 7系列FPGA支持DDR3 SDRAM,它具有更高的数据传输速度和较低的功耗。

3.电源和地线设计在DDR3硬件设计中,正确的电源和地线设计是保证稳定、可靠操作的关键。

以下是一些必须考虑的要点:- 为DDR3提供稳定的电源供应,包括供电线路的降噪和绕线规则。

- 将VCCINT和VCCAUX分别与主要飞线供电器件的专用电源连接。

- 使用低噪声电源滤波器和电源剥离电感,以降低电源噪声。

4.时钟设计DDR3使用时钟信号来同步数据传输。

以下是一些关键的时钟设计注意事项:- 使用低噪声时钟源,并且确保时钟信号干净和稳定。

- 时钟信号的布线要尽量短,以降低时钟抖动和延迟。

- 时钟信号分配必须满足时钟频率要求和布线规则。

5.布线和信号完整性良好的布线和信号完整性是DDR3硬件设计中的关键要点。

以下是一些布线和信号完整性设计注意事项:- DDR3接口线长度必须匹配,以确保信号同步和正常传输。

- 使用差分布线技术来减少噪声和串扰。

- 保持信号线和差分对之间的间距足够大,以降低串扰和干扰。

- 使用终端电阻来匹配DDR3总线阻抗,并提高信号完整性。

- 严格遵守DDR3布线规则,如保持信号线的最小长度、最大长度等。

6.时序约束为确保DDR3的正确操作,必须正确设置时序约束。

以下是几个重要的时序约束要点:- 根据DDR3存储器的数据手册和Xilinx 7系列FPGA的时序规格表,确定正确的时序约束。

- 确保时钟和时钟相关信号的约束满足要求,以保证数据传输的准确性。

- 将时序约束尽可能地贴近实际硬件设计,并进行时序分析和优化。

7.布局和引脚分配良好的布局和引脚分配是确保DDR3性能和可靠性的关键。

8.1.6 高级配置模式──SPI_Xilinx可编程逻辑器件设计与开发(基础篇)_[共4页]

![8.1.6 高级配置模式──SPI_Xilinx可编程逻辑器件设计与开发(基础篇)_[共4页]](https://img.taocdn.com/s3/m/1291ed3c172ded630a1cb62b.png)

Xilinx FPGA 的配置模式277 在这个流程中,我们可以看到比较详细的配置细节。

事实上,对于普通用户而言,并不要求掌握如此详细的配置过程,我们也只是在遇到具体的配置问题时才会去分析配置的细节。

8.1.6 高级配置模式──SPI在新一代Xilinx FPGA 中,在原有配置模式的基础上,增加了SPI 与BPI 的配置模式。

串行外设接口(SPI )是一种四线同步串行数据总线。

这种数据链路最初是用作微控制器与外设之间的串行通信接口。

许多现代微控制器都包括内置的 SPI 控制器,以支持众多存储器、传感器、显示驱动器以及模数和数模转换器通信。

这种接口常见于嵌入式和消费市场,现在也可用来配置FPGA 。

SPI 系统通常由一个主器件和至少一个从器件组成。

对于 Spartan-3E 配置,FPGA 是 SPI 主器件,SPI FLASH PROM 是从器件。

SPI 接口使用表8-2所示为4个信号在主从器件之间进行通信。

表8-2 SPI 接口信号 通用 SPI 信号信号描述SCLK“串行时钟”提供串行接口的时钟 MOSI“主出从入”由主器件用来指定要执行的指令或者向从器件传送数据 MISO“主入从出”由主器件用来收集从器件传输的数据 SS_n “从器件选择”,低有效信号;当置为高时,此信号用来反选从器件并将MISO 设置为高阻抗 通用 SPI 接口是标准的全双工接口。

SPI 主器件通过 SCLK 时钟控制所有时序。

在选择信号 SS_n 转为低之后,主器件经 MOSI 引脚将数据由主器件同步输出到从器件。

在同一时钟周期内,主器件接收由从器件同步输出的数据。

数据在一个时钟沿上从源器件同步输出,在该周期内的下一个对沿(opposite edge) 上同步输入目标器件。

图8-17所示为主从器件的典型连接方式。

图8-17 Spartan-3E/A 器件SPI 模式示意图在多个FPGA 需要配置的情况下,SPI 主器件使用片选信号 SS_n 选择从器件。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

Xilinx FPGA配置的一些细节2010年07月03日星期六 14:260 参考资料(1) Xilinx: Development System Reference Guide. dev.pdf, v10.1在Xilinx的doc目录下有。

(2) Xilinx: Virtex FPGA Series Configuration and Readback. XAPP138 (v2.8) March 11, 2005在Xilinx网站上有,链接(3)Xilinx: Using a Microprocessor to Configure Xilinx FPGAs via Slave Serial or SelectMAP Mode.XAPP502 (v1.5) December 3, 2007在Xilinx网站上有,链接注:此外xapp139和xapp151也是和配置相关的。

(4)Xilinx: Virtex-4 Configuration Guide. UG071 (v1.5) January 12, 2007(5) Tell me about the .BIT .链接:1 Xilinx配置过程主要讲一下Startup Sequence。

Startup Sequence由8个状态组成.除了7是固定的之外,其它几个的顺序是用户可设置的,而且Wait for DCM和DCI是可选的。

其中默认顺序如下:这些在ISE生成bit文件时通过属性页设定。

这几个状态的具体含义如下:Release_DONE : DONE信号变高GWE : 使能CLB和IOB,FPGA的RAMs和FFs可以改变状态GTS : 激活用户IO,之前都是高阻。

EOS : 表示配置结束DCI_MATCH : 表示所有的DCI(Digitally Controlled Impedance)控制器已经把内部电阻和外部参考电阻匹配完毕。

DCM_LOCK : 表示所有的DCM已经锁定。

这个选项默认是选中的。

因此,我们可以得出如下结论:(1)FPGA最后的Startup过程有8个周期,其中DONE变高仅仅是第4个周期。

因此,在DONE变高之后还需要再给3个CCLK。

否则DONE虽然变高了,FPGA程序并没有正确运行。

(2)ISE会在设计中搜索用户是否使用了DCI,如果是,FPGA会使用2个周期的Start Up Phase,等待DCI匹配上。

即FPGA会在那儿等待,直到DCI匹配上。

如果我们在上位机读取了配置文件,获得了文件大小,我们把它写到负责加载V4的SP3里,然后CCLK时钟就不给了。

这就产生问题,因为DCI匹配需要时间,我们的问题就是,过了一段时间,DCI匹配完毕了,但是CCLK却没有了,因此FPGA一直处在Start UP的前2个Phase上,不会到DONE。

导致无法配置成功。

看xilinx Development System Reference Guide(dev.pdf)中,写到BitGen Match_cycleThe BitGen Match_cycle setting specifies a stall in the Startup cycle until digitallycontrolled impedance (DCI) match signals are asserted.DCI matching does not begin on the Match_cycle that was set in BitGen. The Startup sequence simply waits in this cycle until DCI has matched. Given that there are a number of variables in determining how long it will take DCI to match, the number of CCLK cycles required to complete the Startup sequence may vary in any given system. Ideally, the configuration solution should continue driving CCLK until DONE goes high. When the Auto setting is specified, BitGen searches the design for any DCI I/O standards.If DCI standards exist, BitGen uses Match_cycle:2. Otherwise, BitGen uses Match_cycle:NoWait.关于DCI_MATCH的设置,在生成bit文件的StartUP Options里有个Match Cycle的选项,默认是Auto。

含义是ISE会去确认用户是否使用了DCI,没有的话,Startup Sequence直接跳过这一步,否则会等待DCI匹配完毕。

2 bit文件的格式.bit是二进制文件,可以分为三个部分:头部冗余信息,配置数据,尾部冗余信息。

其中头部信息的格式可以参见《Tell me about the .BIT 》.它里面包含了当前ISE工程名字、编译时间等信息,因此头部信息的长度是不确定的,72个字节左右。

第二部分是配置数据流,以0xFF FF FF FF AA 99 55 66开头,AA 99 55 66是Xilinx指定的同步字符。

配置数据流的具体格式及含义可以参见参考文献,比如ug071.pdf的P95的Configuration Sequence,基本格式就是指令+数据,很清晰地给出哪个字节是什么命令,用来干什么。

例如bit文件中,加载数据帧之后,有CMD寄存器的命令: START 0x5(0101b) 表示开始Start-Up Sequence。

最后一部分是尾部信息,由16个32bit的空操作指令:0x20 00 00 00组成。

大家可以打开bit文件看,有很多20 00 00 00。

这些表示空操作。

这部分信息可以不用加载到FPGA。

我认为Xilinx把bit文件后面加上这些空操作,是为了在SelectMAP时能让用户多给一些CCLK,完成StartUp。

3 bit文件和bin文件的区别.bin文件和.bit的区别就在于,.bin只包含配置数据,没有前面的header inforamtion。

4 SelectMAP文件是加载.bit呢还是.bin?既然.bit和.bin仅仅是header information不一样,配置数据是一样的,所以两个文件都可以加载。

但是,当用户在ISE中调用了EDK(比如使用microblaze或者powerpc),ISE生成.bin文件并不会把用户的.elf文件初始化到FPGA内部的数据和程序存储器中,造成用户的microblaze或ppc代码不运行。

至少当前ISE版本(<=10.1)是这样的,不知道以后的版本Xilinx会不会解决这个bug。

因此,推荐使用.bit文件。

5 EDK生成的.bit和ISE生成的.bit文件有什么区别吗?我们发现,EDK的工程中,生成的.bit文件通过SelectMAP加载到FPGA,程序运行不正常,如果用JTAG加载这个.bit文件,则程序运行正常。

如果把EDK的工程作为ISE的子模块调用,生成的.bit可以通过SelectMAP加载。

那么,EDK生成的.bit和ISE生成的.bit有什么区别吗?有!原因就在于ISE和EDK的StartUp Clock默认属性设置的不一样。

在ISE-> Generate Programming File的属性-> Startup Options -> FPGA Start-Up Clock 的Value是CCLK;在EDK-> Project Files -> Bitgen Options File: etc/bitgen.ut里头写着 -g StartUpClk:JTAGCLK,把它修改为-g StartUpClk:CCLK,重新生成download.bit,SelectMAP 加载,FPGA工作正常!查Xilinx关于SelectMAP的说明(v4的配置手册ug71.pdf),发现一句话:The BitGen startup clock setting must be set for CCLK for SelectMAP configuration.6 xapp138.pdf比较详细的介绍了FPGA配置细节;(1) 在Master Serial 模式,FPGA输出的CCLK开始是2.5MHz,在同步字符后第60个字节CCLK的频率切换为用户指定的时钟。

我们可以在ISE中选择配置时钟的频率,单位是MHz,需要注意的是,CCLK的周期有-30%~+45%的偏差。

ISE不同版本、不同FPGA系列,它默认的配置时钟是不一样的。

此外,还需要注意选择的CCLK频率能被PROM支持。

我曾经遇到过这个问题:用Virtex5 SX50T作为PCI接口芯片,默认的配置时钟选择了6MHz。

完成整个加载超过1s的时间,结果是PCI设备无法识别。

解决方法就是在生成bit文件的时候,把CCLK设置为20MHz,这样SX50T很快就能完成加载。

(2)在bit文件末尾有一些关于startup的配置命令。

(3) /PROGRAM 低有效的持续时间不能小于300ns,最长时间没有限制。

所以,我们在用SelectMAP配置的时候,要注意拉低此信号的持续时间。

(4) CRC校验,在整个配置过程中会校验两次。

The first check is just before the last configuration frame is loaded, and the second is at the very end of configuration.(5) selectMAP模式,BUSY仅在CCLK频率大于50MHz时才是必需的。

(BUSY is only necessary for CCLK frequencies above 50MHz. If the CCLK frequency is less,than 50 MHz, this can be done without handshaking.)(6) Completion of the configuration process requires 8 to 16 clock cycles after the final CRC is loaded.这个参见第1节。