DSP的存储空间映射、配置

TMS320C54X系列DSP存储空间的配置方法研究

DSP存储空间配置的具体步骤,以及利用C5416片内SARAM如何扩展其程序空间。

关键词:数字信号处理器,存储机理,扩展地址,引导装入

中图分类号:TP311.53

文献标识码:B

文章编号:1001—1390(2005)06—0047—04

Study on the Configuration Method for the Memory Area in TMS320C54X Series DSP

#Oh.DP

严数据页指向0页+,

总第42卷第474期 2005年第6期

ment&Instrumentation

VoL42 N0.474 Jun.2005

II雠 ∞∞

007F

∞80

7FFF

80∞

p_鲫程序空间

保留 (OVLYffil) 映射到外部 (OVLY=O)

程序存储空间可以超过64K。一个新的7位程序计数

扩展寄存器(xPc)和原来的16位程序计数器绑定在

一起,可以支持最大可达8192K的程序空间。不过,扩 展地址只是对程序空间而言,数据空间不作扩展。DSP

还提供了一些额外的指令支持从23位远地址无条件

跳转、调用和返回。

扩展程序地址的映射模式由处理器工作方式状 态寄存器PMST的OVLY位决定。如果OVLY为0,片

号。C54X的片内ROM容量有大(28K或48K字等)有 d、(2K字等)。容量大的片内ROM可以把用户的程序 代码编写进去,但是需要r11服务商来写入,且不可自 由改动,很不方便,所以一般不用作用户程序区。片内 高2K字ROM中的内容是由r11公司定义的。这2K 字程序空间(F800h-FFFFh)包含如下内容:

一鹪一 万方数据

C5416DSP,当DROM=I时,片内高32K DARAM映射 到的高32K地址数据空间;当DROM--O时,则可用外

DSP存储空间的配置

DSP存储空间的配置在DSP的开发过程中,开发者难免会遇到DSP芯片内部存储器和片外扩展存储器的配置等问题。

本文以TMS320C54x系列DSP为例,讨论DSP存储空间的分配问题。

存储器空间'C54x系列DSP存储器分为三个独立选择的空间—程序、数据和I/O,其中程序存储器存放待执行的指令和执行中所用的系数(常数),可使用片内或片外的RAM、ROM或EPROM等来构成;数据存储器存放指令执行中产生的数据,可使用片内或片外的RAM和ROM来构成。

I/O存储器存放与映象外围接口相关的数据,也可以作为附加的数据存储空间使用。

这三个空间的寻址范围取决于DSP芯片地址线数目。

例如,'C54x系列DSP 从'C548开始,芯片有23根地址线,具有8M字节存储空间寻址能力。

'C54x通过包含在处理器工作方式的状态寄存器(PMST)中的3个状态位,选择片内存储器作为程序空间或数据空间。

这3个状态位是:1.MP/MC位。

MP/MC=0,则片内ROM安排到程序空间;MP/MC=1,则片内ROM不安排到程序空间。

2.OVLY位。

OVLY=1,则片内RAM安排到程序和数据空间;OVLY=0,则片内RAM只安排到数据存储空间。

3.DROM位。

当DROM=1,则部分片内ROM安排到数据空间;DROM=0,则片内ROM不安排到数据空间。

程序设计者可根据不同的需求,相应的配置这3个位,使系统的存储空间满足应用要求。

同时,为了扩展'C54x系列DSP的寻址空间,还增加了一个额外的存储器映像寄存器—程序计数器扩展寄存器XPC,以及6条寻址扩展程序空间的指令。

以TMS320C5410为例,它的程序空间分成128页面,每页64K字。

该64K字程序空间分为两部分:一部分是公共的32K 字,另一部分是各自独立的32K字。

公共存储器为所有页面共享,每个页面独立的32K字存储器只能按指定的页面号寻址,这个页面号由XPC寄存器设定。

DSP芯片的存储资源管理

数字信号处理

用户编写的C源程序经过C 用户编写的C源程序经过C 编译器的处理后, 编译器的处理后,转化为具 有相同功能的汇编语言代码 。之后再作为独立的汇编源 程序经过汇编处理产生COFF 程序经过汇编处理产生COFF 目标文件, 目标文件,其中包含上述的 各类程序块或数据块。 各类程序块或数据块。接下 来,链接器以这些块作为输 入将其组合起来, 入将其组合起来,并参照具 体的CMD文件, CMD文件 体的CMD文件,最终生成可执 行的COFF文件。 COFF文件 行的COFF文件。此外在链接 过程中系统将自动访问目标 文件库和运行库, 文件库和运行库,以简化链 接过程, 接过程,缩短链接过程所需 的时间。 的时间。

数字信号处理

块的链接

链接器对块的处理主要包括下面2个方面。首先,链接器将COFF目 标文件中的块建立为程序块或数据块并以这些块作为输入块,链接器 再把这些输入块组合起来以建立可执行的COFF输出模块。然后,链接 器为输出块选择存储器地址。链接器提供Memory和Sections 2个命令 来完成上述工作。其中,Memory命令定义目标系统的存储器分配,程序 员可以通过指定存储器起始地址和长度来定义每一块存储器。 Sections命令定义如何组合输入块以及在存储器何处存放输出块。若 不用这二条命令,链接器就会采用默认的分配方法;若采用这二条命令, 则需要在链接器命令文件(扩展名为.cmd)中确定。

数字信号处理

.data .sect “块名” .asect “块名”,地址 在这些命令中,.text和.data命令建立的块名称就 是.text和.data,而后二个命令建立的块是自定义的块。 其中.asect建立的块具有绝对地址,一般不要使用。当 汇编器遇到上述命令时,立即停止汇编当前块,且开始 将随后的代码或数据汇编到当前命令所对应的块中。

TMS320C54x系列DSP存储空间的设计

TMS320C54x系列DSP存储空间的设计1 引言在《DSP原理与技术》课程的教学过程中,发现学生对DSP存储空间的概念理解不透、掌握不好,教材与参考书中都没有对这一问题具体阐述,并且相关的知识点也不集中。

这进一步影响了学生的实习任务。

反应的问题集中在三点:①程序空间、数据空间及I/O空间的分配;②扩展的程序存储器、数据存储器及I/O与存储空间的映射关系;③I/O空间的访问。

这里以TMS320C54x系列DSP为例,讨论DSP存储空间的相关问题。

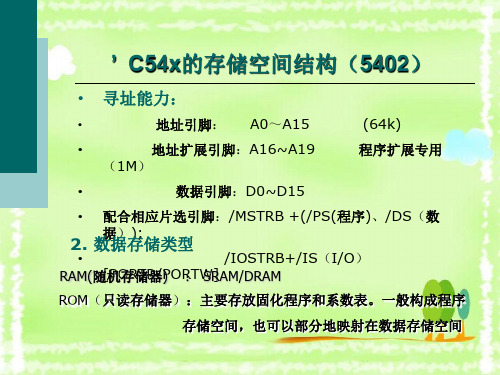

1 C54x系列DSP的存储空间安排2.1 存储空间C54x的存储空间由程序空间、数据空间与I/O空间3个独立的可选择空间组成,它们的地址采用片内与片外统一编址,范围都是0000H~FFFFH,即大小都是64K字,C54x的存储空间共计192K字。

程序空间存放用户程序代码与系统常数表,可以使用片内或片外的RAM、ROM或EPROM等类型的存储器;数据空间存放执行指令所使用的数据(需要处理的数据或数据处理的中间结果),可使用片内或片外的RAM 和ROM类型的存储器;I/O空间用于访问片外设备,也可以作为扩展的数据存储空间使用。

以C5402为例,其存储空间映射结构如图1所示。

从图1可以看出,C54x的存储空间结构与处理器工作方式状态寄存器PMST(如图2所示)有关,可以通过PMST中的3个控制位(MP/MC、OVLY与DROM)来配置存储器空间。

存储空间可以指定使用片内存储器或片外存储器来实现,并且规划了它们的位置,如果存储空间中使用了片内存储器,可以进一步定义其作为程序空间或数据空间。

PMST中3个控制位的功能如下:①MP/MC位。

MP/MC=0,则片内ROM安排到程序空间;MP/MC=1,则片内ROM 不安排到程序空间。

②OVLY位。

OVLY=1,则片内R A M安排到程序和数据空间;OVLY=0,则片内RAM 只安排到数据存储空间。

OVLY=1时,内部RAM既是数据区又是程序区,这样的设置使程序可以在片内全速运行,但是,应该注意到,程序与数据区是共用的,在链接时必须将程序与数据分开,以避免重叠,这可以在CMD文件中设置。

DSP第2章 'C54x的硬件结构2

2013年8月15日

DSP原理及应用

6

3.工作方式状态寄存器PMST

主要设定和控制处理器的工作方式和存储器的配置,反映 处理器的工作状态。

15~7 6 5 4 AVIS 3 2 1 0 SST

IPTR MP/MC OVLY

DROM CLKOFF SMUL

中 断 向 量 指 针

CPU 工 作 方 式 选 择 位

③ 暂存器SPRAM。

2013年8月15日

DSP原理及应用

14

特殊功能寄存器

功能:主要用于程序的运算处理和寻址方式的选

择和设定。地址范围:0000H~001FH。 外设寄存器 ’C5402的CPU寄存器共有27个,CPU访问这 功能:用来控制片内外设电路的状态和存放数据。 些寄存器时,不需要插入等待时间。 地址范围:0020H~005FH。 包括串行口通信控制寄存器组、定时器定时控 暂存器SPRAM 制寄存器组、时钟周期设定寄存器组等。 功能:用来暂存变量。地址范围:0060H~007FH。

中断屏蔽寄存器 10H 中断标志寄存器 11H 保留 ( 用于测试 ) 12H 保留 ( 用于测试 ) 13H 保留 ( 用于测试 ) 14H 保留 ( 用于测试 ) 15H 状态寄存器0 16H 状态寄存器1 17H 累加器A低字(15~0位) 18H 累加器A高字(31~16位) 19H 累加器A保护位(39~32位) 1AH 累加器B低字(15~0位) 1BH 累加器B高字(31~16位) 1CH 累加器B保护位(39~32位) 1DH 暂存寄存器 1EH DSP原理及应用 状态转移寄存器 1FH

2013年8月15日

存储器映像的CPU寄存器, 存储器映像的外设寄存器 特殊功能寄存器

2812DSP-03DSP流水线及存储器配置

计算机信息工程学院

DSP技术及应用

281x流水线及存储器映射

指令流水线

虽然每一条指令都有经过8个阶段,但是,对于具 体的指令来说并不是每一个阶段都有效。一些指 令在译码2阶段就完成了,其他的在执行阶段,还 有一些在写阶段

执行(E) 读2(R2)

2

写(W)

读1(R1)

• CPU执行所有 的乘法、移位 • 如果数据已经在 和ALU操作 R1阶段被寻址,

4个地址作为CPU的32个中断向量。通过CPU的ST1 寄存器中的VMAP位来将这一段地址映射到程序空 间的底部或者顶部。

2 F2812的Reserved(保留)空间,可以用来进行外部存 ◆

储器扩展。其中数据空间里面某些地址被保留作为 CPU的仿真寄存器使用,这些地址是不向用户开放 的。

计算机信息工程学院

W W W

8-stage pipeline

W W W

F1 F2 D1 D2 R1 R2 X

F1 F2 D1 D2 R1 R2 X

F1 F2 D1 D2 R1 R2 X

F1 F2 D1 D2 R1 R2 X

E & G Access same address

F1 F2 D1 D2 R1 R2 X

F1 F2 D1 D2 R X2 W R11 R2 R X W F1 F2 D1 D X2 W D R X W 22 R1 R 21 R Protected Pipeline

DSP技术及应用

281x流水线及存储器映射

Code Security Module

• 保护知识产权

0x00 8000 LO SARAM (4K) 0x00 9000 0x00 A000 0x3D 7800 0x3D 7C00 0x3D 8000

DSP的存储空间映射、配置

.sector “vectors” 表 明 中 断 向 量表代码位于vectors段 必 须 把 vectors 段放置在片内 RAM中,用以高速响应中断 在 DSP 程 序 初 始 化 时 , 若 将 IPTR=0x001,则中断向量表 初始地址为0x80 在 CMD 文件中,在 PAGE0 中 配置一块地址从 0x80 开始 , 共128 Words,并将vectors段 配置到该区域 设 计 OVLY=1 , 将 DARAM0~3 块映射到程序空 间,实现中断向量表在 DARAM中运行

TMS320VC5416 DSP的内部存储资源

64K Words的DARAM (双访问RAM) 每8K一块,被分成8块,由低地址开始记作DARAM0 -DARAM7 在同一块内一个指令周期支持两个操作 64K Words的SARAM (单访问RAM) 每8K一块,被分成8块,由低地址开始记作SARAM0- SARAM7 在同一块内一个指令周期仅支持一个操作,但支持一个指 令周期同时对不同的块完成两个操作 16K Words的ROM 掩模ROM,只能读不能写

TMS320VC5416 DSP的存储空间配置-CMD文件结构

TMS320VC5416 DSP的存储空间分配和配置综合

OVLY=1 DROM=1

以TMS320VC5416 的中断设计为例看存储空间映射和配置 1. 中断向量地址计算方法

(1)取PMST寄存器的IPTR的值(中断向量指针,9位) (2)查DSP的中断表得到中断向量序号(5位) (3)将中断向量序号左移2位 (4)将IPTR值左移7位与(3)相加,得到中断向量地址

INT0序号为16 左移两位后为 40H

1. 硬件复位 值为0x1FF。 2. 用户可以 软件设置 3. 软件复位 该值不变化

DSP-3DSP存储器配置及外设

FF7FH

外部存储器 中断矢量表

FF7FH FF7FH FF80H FF80H

FFFFH

FFFFH FFFFH

电气与信息工程学院

DSP技术及应用

程序存储空间的分页扩展

’C54x存储器及片内外 设

• 在’C54x系列芯片中,有些芯片采用分页扩展的 方法,使程序存储空间可扩展到1M-8M。 • 如:’C5409和’C5416可扩展到8M。’C5402有20 条外部程序地址总线,其程序空间只能扩展到1M。 分页扩展技术的特点:

OVLY=1 保留 OVLY=1 保留 007FH OVLY=0 外部存储器 OVLY=1 保留 OVLY=0 外部存储器

DSP技术及应用

程序存储空间

微处理器模式: MP/ MC=1

地址

0000H 0000H 007FH

’C54x存储器及片内外 设

程序存储空间

OVLY=1 OVLY=1 保留保留 留 保 OVLY=0 外部存储器 OVLY=1 保留 OVLY=0 外部存储器 OVLY=0 外部存储器 OVLY=1 内部DARAM OVLY=1 内部DARAM OVLY=0 外部存储器 OVLY=1 内部DARAM OVLY=0 外部存储器 OVLY=0 外部存储器

• ROM可以灵活地映射到程序存储空间,同时也可以部

分地映射到数据存储空间。

• 存储空间的任何一种存储器都可以驻留在片内或片外。

电气与信息工程学院

DSP技术及应用

TMS320VC5402存储器配置结构

地址

0000H 007FH 0080H 3FFFH 4000H 外部存储器 EFFFH F000H

DSP存储单元DSP存储器的基本结构

在对I/O空间访问时,除了使用数据总线和地址 总线外,还要用到IOTRB、IS和I/W控制线。

IOTRB和IS :用于选通I/O空间; I/W:用于控制访问方向。

通用I/O引脚

’C54x芯片为用户提供了两个通用的I/O引脚。 BIO:用来监控外部设备的运行状态。 在实时控制系统中,通过查询此引脚控制 程序流向,以避免中断引起的失控现象。 XF:用于程序向外设传输标志信息。 通过此引脚的置位或复位,可以控制外设 的工作。

DROM控制的 数据存储空间

程序存储空间

程序存储空间用来存放要执行的指令和执行中所需的 系数表。

’C5402共有20条地址线,可寻址1M字的外部程序存 储器。它的内部ROM和DARAM可通过软件映射到程序空 间。当存储单元映射到程序空间时,CPU可自动地按程序 存储器对它们进行寻址。

如果程序地址生成器(PAGEN)产生的地址处于外部 存储器,CPU可自动地对外部存储器寻址。

1.程序存储空间的配置 ● MP/MC控制位用来决定程序存储空间是否使用内部

存储器。 当MP/ MC=0时,称为微计算机模式。

4000H~EFFFH程序存储空间定义为外部存储器; F000H~FEFFH程序存储空间定义为内部ROM; FF00H~FFFFH程序存储空间定义为内部存储器。

当MP/ MC=1时,称为微处理器模式。 4000H~FFFFH程序存储空间定义为外部存储器 。

2D~2FH

保留

30H TRCV TDM串行口数据接收寄存器

31H TDXR TDM串行口数据发送寄存器

32H TSPC TDM串行口控制寄存器

DSP存储空间结构

外部存储器

EFFFH F000H EFFFH

F000H

外部存储器

DROM=0 外部ROM DROM=0 外部ROM DROM=1 内部ROM DROM=1 内部ROM

4K

±£Áô 中断矢量表 (外部存储器 外部存储器) 外部存储器

FEFFH DROM=1 内部ROM DROM=1 内部ROM FF00H DROM=0 DROM=0 外部存储器 FEFFH DROM=0 DROM=0 外部存储器

2.程序存储空间的分页扩展

分页扩展技术的特点: 分页扩展技术的特点: 特点

条外部程序地址线 ① 有 20或 23条外部 程序地址线 , 可寻址 或 条外部 程序地址线, 可寻址1M或8M存储 或 存储 空间; 空间; ② 有1个额外的存储器映像寄存器 程序计数器扩展寄 个额外的存储器映像 个额外的存储器映 寄存器—程序计数器扩展寄 存器XPC; ; 存器 条寻址扩展程序空间的指令, ③ 有6条寻址扩展程序空间的指令,用于寻址扩展程序 空间。 空间。

F800H

F800H~ FBFFH F900H

FA00H 00H~FCFFH FC H~FCFFH FC00 FB00H FC00H FE00H FF80H

引导程序

FD00H~FDFFH FD00H~FDFFH μ律扩展表

sin函数表 sin函数表

FD00H 00H~FEFFH FE A律扩展表 FE00H~FEFFH

程序存储空间

OVLY=1 OVLY=1 保留 (0页) 页 OVLY=0 OVLY=0 外部存储器 OVLY=1 内部DARAM OVLY=1 内部DARAM OVLY=0 OVLY=0 外部存储器 外部存储器

(整理)DSP存储空间的分配问题.

在DSP的开发过程中,开发者难免会遇到DSP芯片内部存储器和片外扩展存储器的配置等问题。

本文以TMS320C54x系列DSP为例,讨论DSP存储空间的分配问题。

存储器空间'C54x系列DSP存储器分为三个独立选择的空间—程序、数据和I/O,其中程序存储器存放待执行的指令和执行中所用的系数(常数),可使用片内或片外的RAM、ROM或EPROM等来构成;数据存储器存放指令执行中产生的数据,可使用片内或片外的RAM和ROM来构成。

I/O存储器存放与映象外围接口相关的数据,也可以作为附加的数据存储空间使用。

这三个空间的寻址范围取决于DSP芯片地址线数目。

例如,'C54x系列 DSP 从'C548开始,芯片有23根地址线,具有8M字节存储空间寻址能力。

'C54x通过包含在处理器工作方式的状态寄存器(PMST)中的3个状态位,选择片内存储器作为程序空间或数据空间。

这3个状态位是:(1)MP/MC位。

MP/MC=0,则片内ROM安排到程序空间;MP/MC=1,则片内ROM不安排到程序空间。

(2)OVLY位。

OVLY=1,则片内RAM安排到程序和数据空间;OVLY=0,则片内RAM只安排到数据存储空间。

(3)DROM位。

当DROM=1,则部分片内ROM安排到数据空间;DROM=0,则片内ROM不安排到数据空间。

程序设计者可根据不同的需求,相应的配置这3个位,使系统的存储空间满足应用要求。

同时,为了扩展'C54x系列DSP的寻址空间,还增加了一个额外的存储器映像寄存器—程序计数器扩展寄存器XPC,以及6条寻址扩展程序空间的指令。

以TMS320C5410为例,它的程序空间分成128页面,每页64K字。

该64K字程序空间分为两部分:一部分是公共的32K字,另一部分是各自独立的32K字。

公共存储器为所有页面共享,每个页面独立的32K字存储器只能按指定的页面号寻址,这个页面号由XPC寄存器设定。

DSP 存储器

程序数据空间

正弦/余弦; 641 x 32(Q30) 规格化翻转; 264 x 32(Q29) 规格化平方根;145 x32(Q30) 规格化ACTAN; 218 x32(Q30) 圆整和饱和度. 180 x 32(Q30) 保留 引导装载功能,ROM版本… 复位向量表; 2 x 16 初始化向量; 62 x 16

2812 DSP 外部 接口分区 XINTF

DSP存储器扩展 CY7C1024V33: 256K×16 位 仿真调试程序 (译码电路)

对访问时序进行配置依赖于F2812的工作频率 SYSCLKOUT和XINTF的定时时钟XTIMCLK。

时钟XTIMCLK 和SYSCLKOUT的关系示意图

� XINTF对外访问时序被分成三个阶段,即: • 起始(Lead)阶段 • • 激活(Active)阶段 收尾(Trail)阶段

. 外部存储器与扩展接口 §3-2 3-2.

,即系统由一个 F2810 DSP 芯片 � 典型的 DSP应用系统多采用 最小系统 最小系统,即系统由一个 加上相应的电源、时钟、复位、 JTAG电路及应用电路构成,这种系 单片系统方案 (Single Chip Solution)。 统也称为 统也称为单片系统方案 单片系统方案( � 在程序调试过程中,可以先将程序放入到 H0 SARAM、L0 SRAM和 仿 时比较方便。仿 L1 SARAM中运行仿真调试,对于程序长度 小于 16K时比较方便。 真调试后再通过修改链接命令文件 (. cmd )等方法,将程序烧进 Flash 中 (.cmd cmd) 运行。 � 如果程序长度大于 16K时,片内的 SARAM的空间用于仿真就不够用 了,需要扩展外部的 RAM 。当然对于编程的高手而言,也可以不经 过仿真阶段,直接将长度超过 16K的程序代码烧进 Flash 中去进行运行 调试。

DSP_CCS3.3初学调试问题汇总(免费)

DSP CCS初学调试问题汇总1.DSP/BIOS应用程序调试在CCS2.0 的emulator写dsp/bios 的程序,编译链接无错误,而点击LOAD Program下载xxx.out完成时弹出如下对话框:RTDX target application does not match emulation protocol!Loaded program was created with an rtdx library which does not match the target device这将导致RTDX(实时数据交换)不能使用分析:RTXD可以在DSP/BIOS中使用,也可以脱离DSP/BIOS使用;目前CCS Simulator不支持RTDX,故RTDX必须在Emulator下使用,即还需要硬件仿真器和DSP目标板。

故这是由于下载BIOS/DSP程序时RTDX设置错误导致的;问题解决如下:把DSP/BIOS配置窗口中的input/output-->RTDX -real-Time Exchange settings的RTDX mode 改为JTAG(原来是simulator),重新编译后LOAD,上述警告消除,可以在模拟的情况下进行BIOS调试了。

PS:虽然simulator能编译运行DSP/BIOS程序,并能提供实时查询程序运行情况(主要是CPU负荷,时序,日志以及线程等)。

但实际开发DSP/BIOS应用程序时为了真实的了解目标板的各种信息,仅有Simulator(软件仿真器)是不行的,还需要使用Emulator(硬件仿真器)和DSP/BIOS插件(安装时已装入)。

2.RTDX应用程序调试RTDX测试DSP Target传输数据到PC机:a)创建工程,编辑源代码(.c/。

asm),加入头文件(.h),库文件(.lib)以及链接命令文件(.cmd)b)添加修改具有实时数据传输的RTDX语句包括:#include <rtdx.h>; RTDX头文件(rtdx.h)RTDX_CreateOutputChannel( ochan ); 定义一个全局的PC机数据输出通道,通道名可以任取TARGET——INITIALIZE();初始化DSP目标系统;RTDX_enableOutput( &ochan ); 使能输出通道写数据;status=RTDX_write( &ochan,&data,sizeof(data) ); 传送数据至PC;RTDX_disableOutput( &ochan ); 禁止输出通道传输数据。

DSP 第2讲 存储器和IO空间

汇编语言表示为 100(十进制)、144q(八进制)、64h(十六进制); C语言表示为 100(十进制)、0144(八进制)、0x64(十六进制)。

§2.6 VC5402的存储器配置

具体内容可参考:

《C/C++语言硬件程序设计》 张勇 《TMS320C54x DSP应用程序设计教程》 清源科技 《Assembly Language Tools User’s Guide》 — SPRU102

§2.2 存储器空间—续

1

0

§2.2 存储器空间—续

需要注意的地方: 实际的物理空间只有ROM:4K,DARAM:16K; 根据状态位将物理空间映射到不同的程序空间和数据空 间; MP/MC主要影响程序区的分配;开机时MP/MC=0, 然后可改成MP/MC =1; OVLY=1时:

§2.6 VC5402的存储器配置

例:VC5402的存储器配置文件格式 设置MP//MC=0;OVLY=1;DROM=0 MEMORY { PAGE 0:PROG(RWXI):origin=0x80, length=0x3000 VECS(RXI):origin=0xFF80, length=0x80 PAGE 1:DATA(RWI):origin=0x3080, length=0xF80 } origin可以缩写为o,或org length可以缩写为l,或len

§2.5 I/O空间

I/O存储器空间是一个64K字的地址空间,并且 都在器件之外。 所有C54xDSP只有两个通用I/O,即/BIO和XF。 可以对主机通信并行接口和同步串行接口进行 配置,以用作通用I/O。 可以扩展外部I/O,但外部I/O必须使用缓冲或锁 存电路,配合外部I/O读写控制时序构成外部I/O 的控制电路。 可以使用两条指令(输入指令PORTR和输出指令 PORTW)对I/O空间进行寻址

DSP存储空间的配置

DSP存储空间的配置在DSP的开发过程中,开发者难免会遇到DSP芯片内部存储器和片外扩展存储器的配置等问题。

本文以TMS320C54x系列DSP为例,讨论DSP存储空间的分配问题。

存储器空间'C54x系列DSP存储器分为三个独立选择的空间—程序、数据和I/O,其中程序存储器存放待执行的指令和执行中所用的系数(常数),可使用片内或片外的RAM、ROM或EPROM等来构成;数据存储器存放指令执行中产生的数据,可使用片内或片外的RAM和ROM来构成。

I/O存储器存放与映象外围接口相关的数据,也可以作为附加的数据存储空间使用。

这三个空间的寻址范围取决于DSP芯片地址线数目。

例如,'C54x系列DSP 从'C548开始,芯片有23根地址线,具有8M字节存储空间寻址能力。

'C54x通过包含在处理器工作方式的状态寄存器(PMST)中的3个状态位,选择片内存储器作为程序空间或数据空间。

这3个状态位是:1.MP/MC位。

MP/MC=0,则片内ROM安排到程序空间;MP/MC=1,则片内ROM不安排到程序空间。

2.OVLY位。

OVLY=1,则片内RAM安排到程序和数据空间;OVLY=0,则片内RAM只安排到数据存储空间。

3.DROM位。

当DROM=1,则部分片内ROM安排到数据空间;DROM=0,则片内ROM不安排到数据空间。

程序设计者可根据不同的需求,相应的配置这3个位,使系统的存储空间满足应用要求。

同时,为了扩展'C54x系列DSP的寻址空间,还增加了一个额外的存储器映像寄存器—程序计数器扩展寄存器XPC,以及6条寻址扩展程序空间的指令。

以TMS320C5410为例,它的程序空间分成128页面,每页64K字。

该64K字程序空间分为两部分:一部分是公共的32K 字,另一部分是各自独立的32K字。

公共存储器为所有页面共享,每个页面独立的32K字存储器只能按指定的页面号寻址,这个页面号由XPC寄存器设定。

DSP第四章存储器与IO空间ppt课件

由两块8K×8的 RAM组成 8K×16的 程序存储器

2)与外部数据存储器的接口

(1)用两组RAM(32K X 16), 一组作为局部数据存储器, 一组作为全局数据存储器 (每组可由两块32K×8的RAM 组成), 地址均为8000h—FFFFh。

2)与外部数据存储器的接口

行时使用的数据

(2) 64K字的局部数据存储器空间:存放指令使用的数据。 (3) 32K字的全局数据存储器空间:通过扩展外部存储器得

到,用来存放与其他处理器共用的数据。

(4) 64K字的I/O空间:用于与外部的设备接口和片内外设寄 存器。

• 这224K字空间包括 片内存储器、外部存储器和I/O设备。 片内存储器操作的优点:速度快,功耗小。

TMS320C2000器件的片内存储器有4种类型:

(1)片内双访问存储器(DARAM)

➢ 电可擦除与编程的非易失性程序存

(2)片内单访问程序/数据存储器储(器SA。RAM) (3)掩模型片内ROM存储器 ➢ 适合系统应用开发。

(4)闪速存储器(Flash):

§ 3.2 程序存储器

• 程序存储器存放应用程序的代码、表格信息和固定操作数 • TMS320C2000器件可寻址的程序存储器地址有64K字。 • C2000器件的程序存储器类型:

外部存储器操作的优点:可以访问更大的地址空间。

• TMS320C2000器件设计以改进的哈佛结构为基础,存储空间可由3 组16位的并行总线访问,即 程序地址总线(PAB), 数据读地址总线(DRAB), 数据写地址总线(DWAB)。

• 3组总线的操作是独立的,因此可以同时访问程序空间和数据空间, 即在一个给定的机器周期里,中央算术逻辑单元(CALU)可执行3种 存储器操作。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

0x0000 0x007F 0x0080 0x00FF 0x0100 0x1FFF 0x2000 0x3FFF 0x4000 0x4FFF 0x5000 0x7F7F 0x7F80 0x7FFF 0x8000

MMR VECS PROM PARA_MEM STACK_MEM MCBSP0_MEM vectors VECS

以TMS320VC5416 的中断设计为例看存储空间映射和配置

vectors

vectors

OVLY=1 DROM=1

IPTR=0x001

若IPTR=0x0FF, CMD文件应怎样 编写,存储空间 如何映射?

以TMS320VC5416 的中断设计为例看存储空间映射和配置

IPTR=0x0FF 时,中断向量表首地址为 IPTR<<7+0<<2=0x7F80 修改 CMD 文件中 Memory 中 VECS 的起 始地址为0x7F80 在空间使用安全和不浪费空间的原则上, 修改PROM和MCBSP0_MEM的设计

IPTR=1 1 1 1 1 1 1 1 1(1FFh) + K= 0 0 0 0 0 0 0 1 1 1 1 1 1 1 1 1 0 0 0 0 0 0 0 F F 8 0 h 故硬件复位后的开始地址为0xFF80。

以TMS320VC5416 的中断设计为例看存储空间映射和配置 3.中断向量表程序示例

INT0序号为16 左移两位后为 40H

1. 硬件复位 值为0x1FF。 2. 用户可以 软件设置 3. 软件复位 该值不变化

以TMS320VC5416 的中断设计为例看存储空间映射和配置 2. 中断向量表程序设计

TI 54系列DSP最大支持序号0~31的32个中断(存在复用) 根据中断向量表地址计算方法,每个中断向量占4个字(序 号左移两位),整个中断向量表共占128个字 硬件复位后,其中断向量表首地址为0xFF80(0号中断地址) 软件设置IPTR后,其中断向量表地址发生变化,为使中断 高速响应,应在片内RAM中运行

.sector “vectors” 表 明 中 断 向 量表代码位于vectors段 必 须 把 vectors 段放置在片内 RAM中,用以高速响应中断 在 DSP 程 序 初 始 化 时 , 若 将 IPTR=0x001,则中断向量表 初始地址为0x80 在 CMD 文件中,在 PAGE0 中 配置一块地址从 0x80 开始 , 共128 Words,并将vectors段 配置到该区域 设 计 OVLY=1 , 将 DARAM0~3 块映射到程序空 间,实现中断向量表在 DARAM中运行

.mmregs .include "global_system.h54" .include "dsp_const.h54" .sect "vectors" _int_reset: B _main NOP NOP

;Main program

.space 72*16 _int_timer0: addm #1, *(_sTimerCounter) rete _int_rint0: st rete .space #0x0001, *(_sStateDataReady) 4*16

BUFF_MEM

0xFFFF

思考:

目前CMD文件的设计,为使DSP程序高速运行,使用片内RAM作为程序和数据空 间的物理存储器。 RAM中程序掉电丢失,不能永久存储。 若修改CMD文件,使DSP程序在片外寻址,要注意事项 DSP片内没有可写ROM,DSP程序必须存储于片外ROM 片外ROM读写速度是DSP程序运行的瓶颈,致使DSP程序不能高速运行 应考虑让DSP程序在片外ROM存储,在片内DARAM中运行 解决DSP程序永久存储和高速运行矛盾,可以采用bootloader程序 请关注TI 54系列DSP的Bootloader设计的教学! 谢谢!

有23根地址线(A0-A22)和16根数据线(D0-D15)管脚 最大访问空间是223×16bit=8M Words TMS320VC5416 数据空间 DSP 支持16位地址和16位数据宽度 的 访问空间为216×16bit=64K Words 存 程序空间 支持23位地址和16位数据宽度 储 分成27=128页 64K Words的程序空间 空 IO空间 间 支持16位地址和16位数据宽度,固定片外寻址 访问空间为216×16bit=64K Words PortR和PortW两条汇编指令用于IO空间访问

TMS320VC5416 DSP的存储空间映射 由处理器工作方式与状态寄存器PMST控制 具体由MP/MC、OVLY、DROM三个位控制

IPTR

MP/MC

OVLY

DROM

程序空间 0x0000

DARAM0~3块 (0x0000~ 0x007F保留)

数据空间 0x0000 0x007F MMR

TI 54系列DSP的存储空间映射、配置

-以TMS320VC5416 的中断设计为例

曹洪龙 苏州大学电子信息学院

为什么要对TI 54系列DSP的存储空间进行映射和配置? DSP程序运行时访问的地址是存储空间的逻辑地 址,必须通过映射才能和片内存储器或片外寻 址对应起来 通过PMST寄存器控制 DSP程序的存储和运行地址比较灵活,需要设计 人员自行配置,保证DSP程序可以高速运行 由CMD文件进行配置

TMS320VC5416 DSP的存储空间配置-CMD文件结构

TMS320VC5416 DSP的存储空间分配和配置综合

OVLY=1 DROM=1

以TMS320VC5416 的中断设计为例看存储空间映射和配置 1. 中断向量地址计算方法

(1)取PMST寄存器的IPTR的值(中断向量指针,9位) (2)查DSP的中断表得到中断向量序号(5位) (3)将中断向量序号左移2位 (4)将IPTR值左移7位与(3)相加,得到中断向量地址

DARAM0~3块 (0x0000~ 0x007F保留)

0x7FFF 0x8000

内部ROM映射到 0xFC00~ 0xFFFF

0x7FFF 0x8000

外部寻址

0xFFFF

0xFFFF

XPC OM=0

TMS320VC5416 DSP的存储空间配置 DSP可执行程序以段为单位组织代码和数据 程序设计时要命名段 采用链接配置文件(CMD文件)进行存储空间配置 将DSP程序生成的段配置到程序空间和数据空间 根据存储空间映射信息,将段和物理存储器对 应起来 原则:尽可能将段放置在片内RAM中,保证DSP 程序可以高速运行

TMS320VC5416 DSP的内部存储资源

64K Words的DARAM (双访问RAM) 每8K一块,被分成8块,由低地址开始记作DARAM0 -DARAM7 在同一块内一个指令周期支持两个操作 64K Words的SARAM (单访问RAM) 每8K一块,被分成8块,由低地址开始记作SARAM0- SARAM7 在同一块内一个指令周期仅支持一个操作,但支持一个指 令周期同时对不同的块完成两个操作 16K Words的ROM 掩模ROM,只能读不能写