什么是开漏输出、推挽输出、开集输出、OC、OD、线或线与逻辑

详细解说开漏输出和推挽输出

详细解说开漏输出和推挽输出1,开漏输出(Open-Drain)首先讲一下集电极开路输出(Open-Collector),单片机I/O常用的输出方式的开漏输出(Open-Drain),漏极开路电路概念中提到的“漏”是指MOSFET的漏极。

同理,集电极开路电路中的“集”就是指三极管的集电极。

在数字电路中,分别简称OD门和OC门。

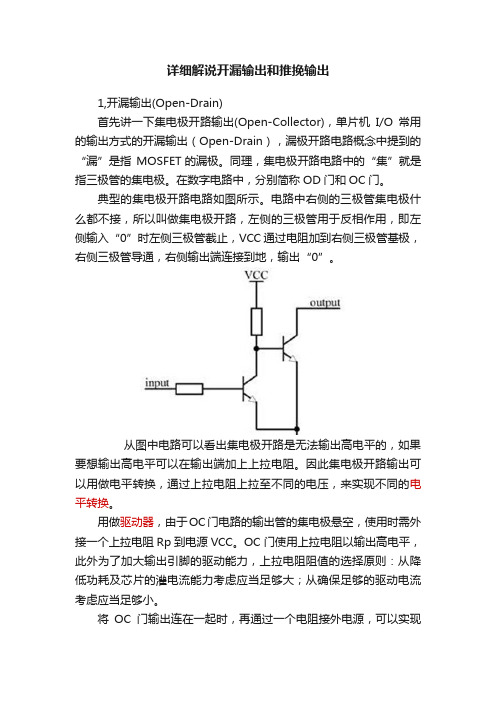

典型的集电极开路电路如图所示。

电路中右侧的三极管集电极什么都不接,所以叫做集电极开路,左侧的三极管用于反相作用,即左侧输入“0”时左侧三极管截止,VCC通过电阻加到右侧三极管基极,右侧三极管导通,右侧输出端连接到地,输出“0”。

从图中电路可以看出集电极开路是无法输出高电平的,如果要想输出高电平可以在输出端加上上拉电阻。

因此集电极开路输出可以用做电平转换,通过上拉电阻上拉至不同的电压,来实现不同的电平转换。

用做驱动器,由于OC门电路的输出管的集电极悬空,使用时需外接一个上拉电阻Rp到电源VCC。

OC门使用上拉电阻以输出高电平,此外为了加大输出引脚的驱动能力,上拉电阻阻值的选择原则:从降低功耗及芯片的灌电流能力考虑应当足够大;从确保足够的驱动电流考虑应当足够小。

将OC门输出连在一起时,再通过一个电阻接外电源,可以实现“线与”逻辑关系。

只要电阻的阻值和外电源电压的数值选择得当,就能做到既保证输出的高、低电平符合要求,而且输出三极管的负载电流又不至于过大。

集电极开路输出除了可以实现多门的线与逻辑关系外,通过使用大功率的三极管还可用于直接驱动较大电流的负载,如继电器、脉冲变压器、指示灯等。

由于现在MOS管用普遍,而且性能要比晶体管要好,所以很多开漏输出电路,和后面要讲的推挽输出电路都用MOS管实现。

再来就是开漏输出电路,和集电极开路一样,顾名思义,开漏电路就是指从MOSFET的漏极输出的电路。

典型的用法是在漏极外部的电路添加上拉电阻到电源如图所示。

完整的开漏电路应由开漏器件和开漏上拉电阻组成。

推挽输出与开漏输出的区别

推挽输出:可以输出高,低电平,连接数字器件;开漏输出:输出端相当于三极管的集电极. 要得到高电平状态需要上拉电阻才行. 适合于做电流型的驱动,其吸收电流的能力相对强(一般20ma 以内).推挽结构一般是指两个三极管分别受两互补信号的控制,总是在一个三极管导通的时候另一个截止.要实现线与需要用OC(open collector)门电路.是两个参数相同的三极管或MOSFET,以推挽方式存在于电路中,各负责正负半周的波形放大任务,电路工作时,两只对称的功率开关管每次只有一个导通,所以导通损耗小,效率高。

输出既可以向负载灌电流,也可以从负载抽取电流。

/////////////////////////////////////////////////////////////////////开漏电路特点及应用在电路设计时我们常常遇到开漏(open drain)和开集(open collector)的概念。

本人虽然在念书时就知道其基本的用法,而且在设计中并未遇的过问题。

但是前两天有位同事向我问起了这个概念。

我忽然觉得自己对其概念了解的并不系统。

近日,忙里偷闲对其进行了下总结。

所谓开漏电路概念中提到的“漏”就是指MOSFET的漏极。

同理,开集电路中的“集”就是指三极管的集电极。

开漏电路就是指以MOSFET的漏极为输出的电路。

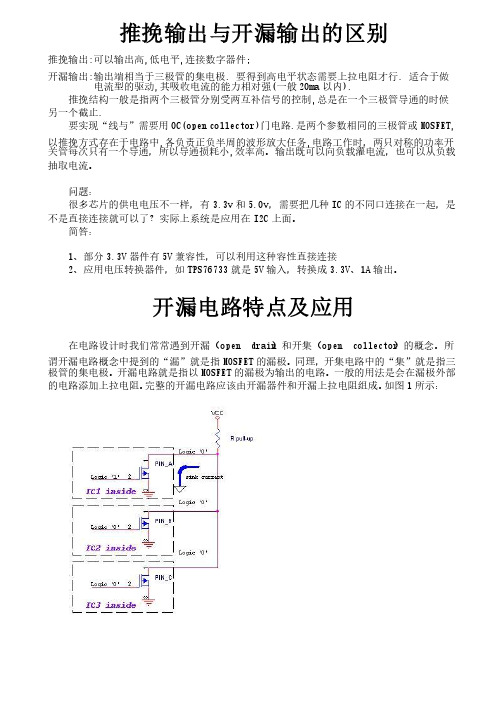

一般的用法是会在漏极外部的电路添加上拉电阻。

完整的开漏电路应该由开漏器件和开漏上拉电阻组成。

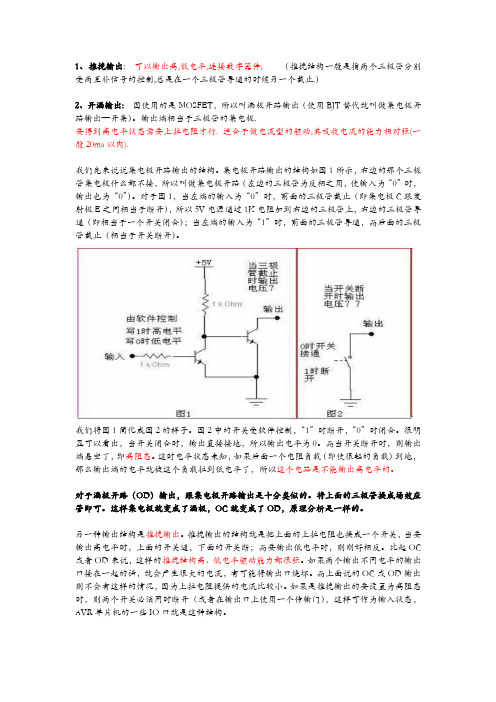

如图1所示:组成开漏形式的电路有以下几个特点:1. 利用外部电路的驱动能力,减少IC内部的驱动。

当IC内部MOSFET导通时,驱动电流是从外部的VCC流经R pull-up ,MOSFET到GND。

IC内部仅需很下的栅极驱动电流。

如图1。

2. 可以将多个开漏输出的Pin,连接到一条线上。

形成“与逻辑” 关系。

如图1,当PIN_A、PIN_B、PIN_C任意一个变低后,开漏线上的逻辑就为0了。

这也是I2C,SMBus等总线判断总线占用状态的原理。

推挽输出与开漏输出的区别

推挽输出:可以输出高,低电平,连接数字器件;开漏输出:输出端相当于三极管的集电极. 要得到高电平状态需要上拉电阻才行. 适合于做电流型的驱动,其吸收电流的能力相对强( 一般20ma 以内).推挽结构一般是指两个三极管分别受两互补信号的控制, 总是在一个三极管导通的时候另一个截止.要实现线与需要用OC(open collector) 门电路.是两个参数相同的三极管或MOSFET以推挽方式存在于电路中, 各负责正负半周的波形放大任务, 电路工作时,两只对称的功率开关管每次只有一个导通,所以导通损耗小,效率高。

输出既可以向负载灌电流,也可以从负载抽取电流。

/////////////////////////////////////////////////////////////////////开漏电路特点及应用在电路设计时我们常常遇到开漏( open drain )和开集( open collector )的概念。

本人虽然在念书时就知道其基本的用法,而且在设计中并未遇的过问题。

但是前两天有位同事向我问起了这个概念。

我忽然觉得自己对其概念了解的并不系统。

近日,忙里偷闲对其进行了下总结。

所谓开漏电路概念中提到的“漏”就是指MOSFET勺漏极。

同理,开集电路中的“集”就是指三极管的集电极。

开漏电路就是指以MOSFET勺漏极为输岀的电路。

一般的用法是会在漏极外部的电路添加上拉电阻。

完整的开漏电路应该由开漏器件和开漏上拉电阻组成。

如图1 所示:组成开漏形式的电路有以下几个特点:1.利用外部电路的驱动能力,减少IC内部的驱动。

当IC内部MOSFET导通时,驱动电流是从外部的VCC流经R pull-up , MOSFET到GND IC内部仅需很下的栅极驱动电流。

如图1。

2.可以将多个开漏输岀的Pin ,连接到一条线上。

形成“与逻辑” 关系。

如图1,当PIN_A、PIN_B、PIN_C任意一个变低后,开漏线上的逻辑就为0 了。

漏极开路输出和推挽输出

漏极开路输出和推挽输出一、漏极开路(OD)输出:漏极开路(OD)输出,跟集电极开路输出是十分类似的。

将上面的三极管换成场效应管即可。

这样集电极就变成了漏极,OC就变成了OD,原理分析是一样的。

对于漏极开路(OD)来说,输出端相当于三极管的集电极。

要得到高电平状态需要上拉电阻才行。

适合于做电流型的驱动,其吸收电流的能力相对强(一般20ma以内)。

要实现线与需要用OC(open collector)门电路。

是两个参数相同的三极管或MOSFET,以推挽方式存在于电路中,各负责正负半周的波形放大任务。

电路工作时,两只对称的功率开关管每次只有一个导通,所以导通损耗小,效率高。

输出既可以向负载灌电流,也可以从负载抽取电流。

在电路设计时我们常常遇到开漏(open drain)和开集(open collector)的概念。

所谓开漏电路概念中提到的漏就是指MOSFET的漏极。

同理,开集电路中的集就是指三极管的集电极。

开漏电路就是指以MOSFET的漏极为输出的电路。

一般的用法是会在漏极外部的电路添加上拉电阻。

完整的开漏电路应该由开漏器件和开漏上拉电阻组成。

如图1所示:组成开漏形式的电路有以下几个特点:1. 利用外部电路的驱动能力,减少IC内部的驱动(或驱动比芯片电源电压高的负载)。

当IC内部MOSFET导通时,驱动电流是从外部的VCC流经R pull-up ,MOSFET到GND。

IC内部仅需很下的栅极驱动电流。

如图1。

2. 可以将多个开漏输出的Pin,连接到一条线上。

形成与逻辑关系。

如图1,当PIN_A、PIN_B、PIN_C任意一个变低后,开漏线上的逻辑就为0了。

这也是I2C,SMBus等总线判断总线占用状态的原理。

如果作为输出必须接上拉电阻。

接容性负载时,下降延是芯片内的晶体管,是有源驱动,速度较快;上升延是无源的外接电阻,速度慢。

如果要求速度高电阻选择要小,功耗会大。

所以负载电阻的选择要兼顾功耗和速度。

开漏输出与推挽输出的比较

开漏输出与推挽输出的比较开漏输出:OC门的输出就是开漏输出;OD门的输出也是开漏输出。

TTL电路有集电极开路OC门,MOS管也有和集电极对应的漏极开路的OD门,它的输出就叫做开漏输出。

它可以吸收很大的电流,但是不能向外输出电流。

所以,为了能输入和输出电流,它使用的时候要跟电源和上拉电阻一齐用。

OC门开漏输出和OD门开漏输出都是为了同一个目的,都是为了实现逻辑器件的线与逻辑,当然选用不同的外接电阻也可以实现外围驱动能力的增加。

当你应用此电路的时候,要注意应用时要加上拉电阻接电源,这样才能保证逻辑的正确,在电阻上要根据逻辑器件的扇入扇出系数来确定,但一般mos电路带载同样的mos电路能力比较强,所以电阻通常可以选择2.2k,4.9k这样一些常用的。

推挽输出与开漏输出的区别推挽输出:可以输出高,低电平,连接数字器件;开漏输出:输出端相当于三极管的集电极. 要得到高电平状态需要上拉电阻才行. 适合于做电流型的驱动,其吸收电流的能力相对强(一般20ma以内).推挽结构一般是指两个三极管分别受两互补信号的控制,总是在一个三极管导通的时候另一个截止.要实现 线与 需要用OC(open collector)门电路.是两个参数相同的三极管或MOSFET,以推挽方式存在于电路中,各负责正负半周的波形放大任务,电路工作时,两只对称的功率开关管每次只有一个导通,所以导通损耗小,效率高。

输出既可以向负载灌电流,也可以从负载抽取电流。

所谓开漏电路概念中提到的“漏”就是指MOSFET的漏极。

同理,开集电路中的“集”就是指三极管的集电极。

开漏电路就是指以MOSFET的漏极为输出的电路。

一般的用法是会在漏极外部的电路添加上拉电阻。

完整的开漏电路应该由开漏器件和开漏上拉电阻组成。

如图1所示:组成开漏形式的电路有以下几个特点:1. 利用 外部电路的驱动能力,减少IC内部的驱动。

当IC内部MOSFET导通时,驱动电流是从外部的VCC流经R pull-up ,MOSFET到GND。

上拉输入、下了输入、推挽输出、开漏输出、复用开漏输出、复用推挽输出以及、浮空输入、模拟输入区别

上拉输入、下了输入、推挽输出、开漏输出、复用开漏输出、复用推挽输出以及、浮空输入、模拟输入区别上拉输入、下了输入、推挽输出、开漏输出、复用开漏输出、复用推挽输出以及、浮空输入、模拟输入区别有关上拉输入、下了输入、推挽输出、开漏输出、复用开漏输出、复用推挽输出以及、浮空输入、模拟输入区别最近在网上看见一些人对STM32的八种方式的解释,说了一大堆,最后看完了也不知道讲了什么,为了方便大家一目了然,本人总结如下,希望对大家有帮助。

1、上拉输入:上拉就是把电位拉高,比如拉到Vcc。

上拉就是将不确定的信号通过一个电阻嵌位在高电平!电阻同时起限流作用!弱强只是上拉电阻的阻值不同,没有什么严格区分。

2、下拉输入:就是把电压拉低,拉到GND。

与上拉原理相似。

3、浮空输入:浮空(floating)就是逻辑器件的输入引脚即不接高电平,也不接低电平。

由于逻辑器件的内部结构,当它输入引脚悬空时,相当于该引脚接了高电平。

一般实际运用时,引脚不建议悬空,易受干扰。

通俗讲就是让管脚什么都不接,浮空着。

4、模拟输入:模拟输入是指传统方式的输入.数字输入是输入PCM数字信号,即0,1的二进制数字信号,通过数模转换,转换成模拟信号,经前级放大进入功率放大器,功率放大器还是模拟的。

5、推挽输出:可以输出高,低电平,连接数字器件; 推挽结构一般是指两个三极管分别受两互补信号的控制,总是在一个三极管导通的时候另一个截止。

高低电平由IC的电源低定。

6、开漏输出:输出端相当于三极管的集电极. 要得到高电平状态需要上拉电阻才行. 适合于做电流型的驱动,其吸收电流的能力相对强(一般20ma以内).7、复用开漏输出、复用推挽输出:可以理解为GPIO口被用作第二功能时的配置情况(即并非作为通用IO口使用)。

在STM32中选用IO模式,下面是参考网上的总结一下。

(1)浮空输入_IN_FLOATING ——浮空输入,可以做KEY识别,RX(2)带上拉输入_IPU——IO内部上拉电阻输入(3)带下拉输入_IPD——IO内部下拉电阻输入(4)模拟输入_AIN ——应用ADC模拟输入,或者低功耗下省电(5)开漏输出_OUT_OD ——IO输出0接GND,IO输出1,悬空,需要外接上拉电阻,才能实现输出高电平。

推挽输出与开漏输出的区别

/////////////////////////////////////////////////////////////////////

开漏电路特点及应用

另一种是互补推挽输出,采用2只晶体管,一只在上一只在下,上面的一只是n型,下面为p型(以三极管为例),两只管子的连接为:npn(上)的c连vcc,pnp(下)的c接地,两只管子的ee,bb相连,其中ee作为输出(引出脚),bb接内部逻辑,这个电路通常用于功率放大点路的末级(音响),当bb接高电压时npn管导通输出高电压,由于三极管的ec电阻很小,因此输出的高电压有很强的驱动能力,当bb接低电压时npn截至,pnp导通,由于三极管的ec电阻很小因此输出的低电压有很强的驱动能力,简单的例子,9013导通时ec电阻不到10欧,以Vh=2.5v,vcc=5v计算,高电平输出电流最大=250MA,短路电流500ma,这个计算同时告诉我们采用推挽输出时一定要小心千万不要出现外部电路短路的可能,否则肯定烧毁芯片,特别是外部驱动三极管时别忘了在三极管的基极加限流电阻。推挽输出电路的形式很多,有些单片机上下都采用n型管,但内部逻辑提供互补输出,以上的说明仅仅为了说明推挽的原理,为了更深的理解可以参考功率放大电路。

5. 标准的开漏脚一般只有输出的能力。添加其它的判断电路,才能具备双向输入、输出的能力。

应用中需注意:

1. 开漏和开集的原理类似,在许多应用中我们利用开集电路代替开漏电路。例如,某输入Pin要求由开漏电路驱动。则我们常见的驱动方式是利用一个三极管组成开集电路来驱动它,即方便又节省成本。如图3。

如果学过三极管放大电路一定知道,前置单管放大器和功放末级放大电路的区别。单片机内部的逻辑经过内部的逻辑运算后需要输出到外面,外面的器件可能需要较大的电流才能推动,因此在单片机的输出端口必须有一个驱动电路。

单片机IO口推挽与开漏输出详解

单片机I/O口推挽与开漏输出详解推挽输出:可以输出高,低电平,连接数字器件;推挽结构一般是指两个三极管分别受两互补信号的控制,总是在一个三极管导通的时候另一个截止.开漏输出:输出端相当于三极管的集电极. 要得到高电平状态需要上拉电阻才行. 适合于做电流型的驱动,其吸收电流的能力相对强(一般20ma以内).我们先来说说集电极开路输出的结构。

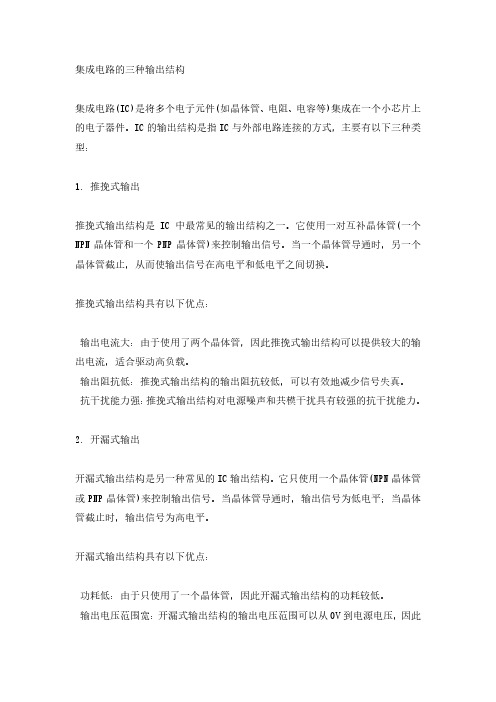

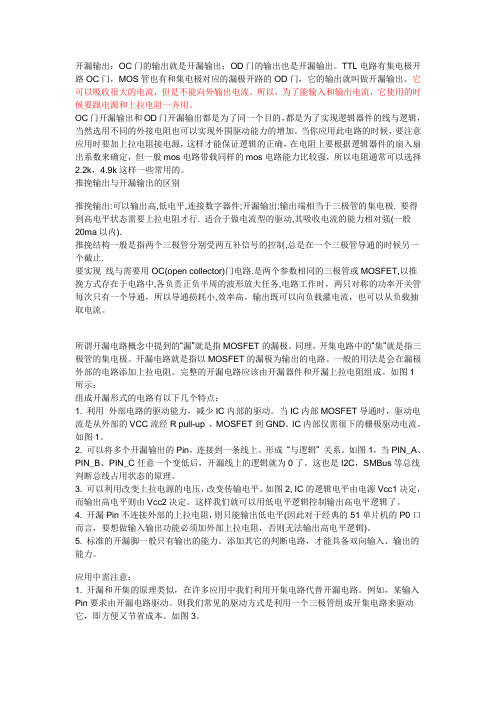

集电极开路输出的结构如图1所示,右边的那个三极管集电极什么都不接,所以叫做集电极开路(左边的三极管为反相之用,使输入为“0”时,输出也为“0”)。

对于图1,当左端的输入为“0”时,前面的三极管截止(即集电极C跟发射极E之间相当于断开),所以5V电源通过1K电阻加到右边的三极管上,右边的三极管导通(即相当于一个开关闭合);当左端的输入为“1”时,前面的三极管导通,而后面的三极管截止(相当于开关断开)。

我们将图1简化成图2的样子。

图2中的开关受软件控制,“1”时断开,“0”时闭合。

很明显可以看出,当开关闭合时,输出直接接地,所以输出电平为0。

而当开关断开时,则输出端悬空了,即高阻态。

这时电平状态未知,如果后面一个电阻负载(即使很轻的负载)到地,那么输出端的电平就被这个负载拉到低电平了,所以这个电路是不能输出高电平的。

再看图三。

图三中那个1K的电阻即是上拉电阻。

如果开关闭合,则有电流从1K电阻及开关上流过,但由于开关闭其它三个口带内部上拉),当我们要使用输入功能时,只要将输出口设置为1即可,这样就相当于那个开关断开,而对于P0口来说,就是高阻态了。

对于漏极开路(OD)输出,跟集电极开路输出是十分类似的。

将上面的三极管换成场效应管即可。

这样集电极就变成了漏极,OC就变成了OD,原理分析是一样的。

另一种输出结构是推挽输出。

推挽输出的结构就是把上面的上拉电阻也换成一个开关,当要输出高电平时,上面的开关通,下面的开关断;而要输出低电平时,则刚好相反。

比起OC或者OD来说,这样的推挽结构高、低电平驱动能力都很强。

集成电路的三种输出结构

集成电路的三种输出结构集成电路(IC)是将多个电子元件(如晶体管、电阻、电容等)集成在一个小芯片上的电子器件。

IC的输出结构是指IC与外部电路连接的方式,主要有以下三种类型:1. 推挽式输出推挽式输出结构是IC中最常见的输出结构之一。

它使用一对互补晶体管(一个NPN晶体管和一个PNP晶体管)来控制输出信号。

当一个晶体管导通时,另一个晶体管截止,从而使输出信号在高电平和低电平之间切换。

推挽式输出结构具有以下优点:输出电流大:由于使用了两个晶体管,因此推挽式输出结构可以提供较大的输出电流,适合驱动高负载。

输出阻抗低:推挽式输出结构的输出阻抗较低,可以有效地减少信号失真。

抗干扰能力强:推挽式输出结构对电源噪声和共模干扰具有较强的抗干扰能力。

2. 开漏式输出开漏式输出结构是另一种常见的IC输出结构。

它只使用一个晶体管(NPN晶体管或PNP晶体管)来控制输出信号。

当晶体管导通时,输出信号为低电平;当晶体管截止时,输出信号为高电平。

开漏式输出结构具有以下优点:功耗低:由于只使用了一个晶体管,因此开漏式输出结构的功耗较低。

输出电压范围宽:开漏式输出结构的输出电压范围可以从0V到电源电压,因此可以连接各种外部电路。

抗干扰能力强:开漏式输出结构对电源噪声和共模干扰具有较强的抗干扰能力。

3. 三态输出三态输出结构是IC中比较特殊的一种输出结构。

它使用三个晶体管来控制输出信号,可以通过控制信号将输出信号设置为高电平、低电平或高阻态。

三态输出结构具有以下优点:输出状态可控:三态输出结构可以通过控制信号将输出信号设置为高电平、低电平或高阻态,因此可以灵活地控制信号的传输。

减少功耗:当输出信号设置为高阻态时,三态输出结构的功耗很低。

便于连接:三态输出结构可以很容易地连接在一起,从而实现多个IC之间的数据传输。

集成电路的输出结构有很多种,每种结构都有其独特的优点和缺点。

在选择IC 时,需要根据实际应用需求来选择合适的输出结构。

IO口推挽与开漏输出详解

1、推挽输出: 可以输出高,低电平,连接数字器件; (推挽结构一般是指两个三极管分别受两互补信号的控制,总是在一个三极管导通的时候另一个截止.)2、开漏输出: 因使用的是MOSFET,所以叫漏极开路输出(使用BJT替代就叫做集电极开路输出—开集)。

输出端相当于三极管的集电极.要得到高电平状态需要上拉电阻才行. 适合于做电流型的驱动,其吸收电流的能力相对强(一般20ma以内).我们先来说说集电极开路输出的结构。

集电极开路输出的结构如图1所示,右边的那个三极管集电极什么都不接,所以叫做集电极开路(左边的三极管为反相之用,使输入为“0”时,输出也为“0”)。

对于图1,当左端的输入为“0”时,前面的三极管截止(即集电极C跟发射极E之间相当于断开),所以5V电源通过1K电阻加到右边的三极管上,右边的三极管导通(即相当于一个开关闭合);当左端的输入为“1”时,前面的三极管导通,而后面的三极管截止(相当于开关断开)。

我们将图1简化成图2的样子。

图2中的开关受软件控制,“1”时断开,“0”时闭合。

很明显可以看出,当开关闭合时,输出直接接地,所以输出电平为0。

而当开关断开时,则输出端悬空了,即高阻态。

这时电平状态未知,如果后面一个电阻负载(即使很轻的负载)到地,那么输出端的电平就被这个负载拉到低电平了,所以这个电路是不能输出高电平的。

对于漏极开路(OD)输出,跟集电极开路输出是十分类似的。

将上面的三极管换成场效应管即可。

这样集电极就变成了漏极,OC就变成了OD,原理分析是一样的。

另一种输出结构是推挽输出。

推挽输出的结构就是把上面的上拉电阻也换成一个开关,当要输出高电平时,上面的开关通,下面的开关断;而要输出低电平时,则刚好相反。

比起OC 或者OD来说,这样的推挽结构高、低电平驱动能力都很强。

如果两个输出不同电平的输出口接在一起的话,就会产生很大的电流,有可能将输出口烧坏。

而上面说的OC或OD输出则不会有这样的情况,因为上拉电阻提供的电流比较小。

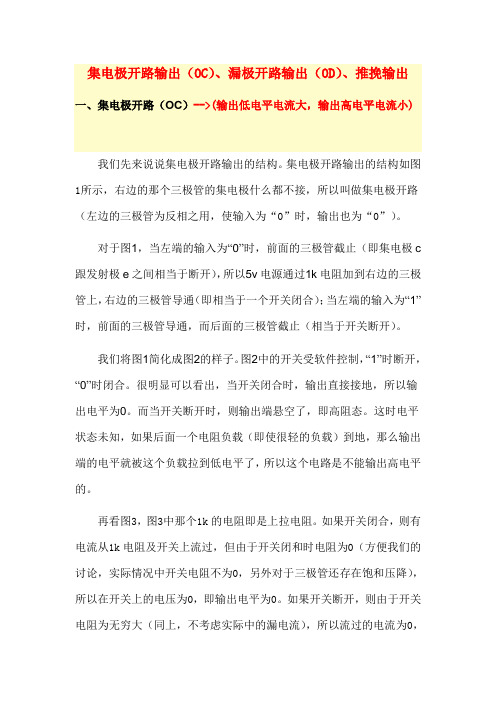

集电极开路输出(OC)、漏极开路输出(OD)、推挽输出

集电极开路输出(OC)、漏极开路输出(OD)、推挽输出一、集电极开路(OC)-->(输出低电平电流大,输出高电平电流小)我们先来说说集电极开路输出的结构。

集电极开路输出的结构如图1所示,右边的那个三极管的集电极什么都不接,所以叫做集电极开路(左边的三极管为反相之用,使输入为“0”时,输出也为“0”)。

对于图1,当左端的输入为“0”时,前面的三极管截止(即集电极c 跟发射极e之间相当于断开),所以5v电源通过1k电阻加到右边的三极管上,右边的三极管导通(即相当于一个开关闭合);当左端的输入为“1”时,前面的三极管导通,而后面的三极管截止(相当于开关断开)。

我们将图1简化成图2的样子。

图2中的开关受软件控制,“1”时断开,“0”时闭合。

很明显可以看出,当开关闭合时,输出直接接地,所以输出电平为0。

而当开关断开时,则输出端悬空了,即高阻态。

这时电平状态未知,如果后面一个电阻负载(即使很轻的负载)到地,那么输出端的电平就被这个负载拉到低电平了,所以这个电路是不能输出高电平的。

再看图3,图3中那个1k的电阻即是上拉电阻。

如果开关闭合,则有电流从1k电阻及开关上流过,但由于开关闭和时电阻为0(方便我们的讨论,实际情况中开关电阻不为0,另外对于三极管还存在饱和压降),所以在开关上的电压为0,即输出电平为0。

如果开关断开,则由于开关电阻为无穷大(同上,不考虑实际中的漏电流),所以流过的电流为0,因此在1k电阻上的压降也为0,所以输出端的电压就是5v了,这样就能输出高电平了。

但是这个输出的内阻是比较大的(即1kω),如果接一个电阻为r的负载,通过分压计算,就可以算得最后的输出电压为5*r/(r+1000)伏,即5/(1+1000/r)伏。

所以,如果要达到一定的电压的话,r就不能太小。

如果r真的太小,而导致输出电压不够的话,那我们只有通过减小那个1k的上拉电阻来增加驱动能力。

但是,上拉电阻又不能取得太小,因为当开关闭合时,将产生电流,由于开关能流过的电流是有限的,因此限制了上拉电阻的取值,另外还需要考虑到,当输出低电平时,负载可能还会给提供一部分电流从开关流过,因此要综合这些电流考虑来选择合适的上拉电阻。

推挽、开漏、强上拉、弱上拉、强下拉、弱下拉输出

lilei 6、提高总线的抗电磁干扰能力。

管脚悬空就比较容易接受外界的电磁干扰。

7、长线传输中电阻不匹配容易引起反射波干扰,加上下拉电阻是电阻匹配,有效的抑制反射波干扰。

上拉电阻阻值的选择原则包括: 1、从节约功耗及芯片的灌电流能力考虑应当足够大;电阻大,电流小。

2、从确保足够的驱动电流考虑应当足够小;电阻小,电流大。

3、对于高速电路,过大的上拉电阻可能边沿变平缓。

综合考虑 以上三点,通常在1k到10k之间选取。

对下拉电阻也有类似道理 对上拉电阻和下拉电阻的选择应结合开关管特性和下级电路的输入特性进行设定,主要需要考虑以下几个因素: 1. 驱动能力与功耗的平衡。

以上拉电阻为例,一般地说,上拉电阻越小,驱动能力越强,但功耗越大,设计时应注意两者之间的均衡。

2.下级电路的驱动需求。

同样以上拉电阻为例,当输出高电平时 ,开关管断开,上拉电阻应适当选择以能够向下级电路提供足够的电流。

3.高低电平的设定。

不同电路的高低电平的门槛电平会有不同,电阻应适当设定以确保能输出正确的电平。

以上拉电阻为例,当输出低电平时,开关管导通,上拉电阻和开关管导通电阻分压值应确保在零电平门槛之下。

4. 频率特性。

以上拉电阻为例,上拉电阻和开关管漏源级之间的电容和下级电路之间的输入电容会形成RC延迟,电阻越大,延迟越大。

上拉电阻的设定应考虑电路在这方面的需求。

下拉电阻的设定的原则和上拉电阻是一样的 OC门输出高电平时是一个高阻态,其上拉电流要由上拉电阻来提供,设输入端每端口不大于100uA,设输出口驱动电流约500uA,标准工作电压是5V,输入口的高低电平门限为0.8V(低于此值为低电平);2V (高电平门限值)。

选上拉电阻时:500uA x 8.4K= 4.2即选大于8.4K时输出端能下拉至0.8V以下,此为最小阻值,再小就拉不下来了。

如果输出口驱动电流较大,则阻值可减小,保证下拉时能低于0.8V 即可。

当输出高电平时,忽略管子的漏电流,两输入口需200uA 200uA x15K=3V 即上拉电阻压降为3V,输出口可达到2V,此阻值为最大阻值,再大就拉不到2V了。

单片机STM32学习笔记

推挽输出与开漏输出的区别推挽输出推挽输出::可以输出高可以输出高,,低电平低电平,,连接数字器件连接数字器件; ;开漏输出开漏输出::输出端相当于三极管的集电极输出端相当于三极管的集电极. . 要得到高电平状态需要上拉电阻才行要得到高电平状态需要上拉电阻才行. . 适合于做电流型的驱动电流型的驱动,,其吸收电流的能力相对强其吸收电流的能力相对强((一般20ma 以内以内). ).推挽结构一般是指两个三极管分别受两互补信号的控制推挽结构一般是指两个三极管分别受两互补信号的控制,,总是在一个三极管导通的时候另一个截止另一个截止. .要实现“线与”需要用OC(open collector)collector)门电路门电路门电路..是两个参数相同的三极管或MOSFET,以推挽方式存在于电路中以推挽方式存在于电路中,,各负责正负半周的波形放大任务各负责正负半周的波形放大任务,,电路工作时,两只对称的功率开关管每次只有一个导通,所以导通损耗小关管每次只有一个导通,所以导通损耗小,,效率高。

输出既可以向负载灌电流,也可以从负载抽取电流。

抽取电流。

问题:问题:很多芯片的供电电压不一样,有3.3v 和5.0v 5.0v,需要把几种,需要把几种IC 的不同口连接在一起,是不是直接连接就可以了?实际上系统是应用在I2C 上面。

上面。

简答:简答:1、部分3.3V 器件有5V 兼容性,可以利用这种容性直接连接兼容性,可以利用这种容性直接连接2、应用电压转换器件,如TPS76733就是5V 输入,转换成3.3V 3.3V、、1A 输出。

输出。

开漏电路特点及应用在电路设计时我们常常遇到开漏(在电路设计时我们常常遇到开漏(open drain open drain )和开集()和开集()和开集(open collector open collector )的概念。

所)的概念。

所谓开漏电路概念中提到的“漏”就是指MOSFET 的漏极。

什么是开漏输出、推挽输出、开集输出、OC、OD、线或线与逻辑

开漏输出:OC门的输出就是开漏输出;OD门的输出也是开漏输出。

TTL电路有集电极开路OC门,MOS管也有和集电极对应的漏极开路的OD门,它的输出就叫做开漏输出。

它可以吸收很大的电流,但是不能向外输出电流。

所以,为了能输入和输出电流,它使用的时候要跟电源和上拉电阻一齐用。

OC门开漏输出和OD门开漏输出都是为了同一个目的,都是为了实现逻辑器件的线与逻辑,当然选用不同的外接电阻也可以实现外围驱动能力的增加。

当你应用此电路的时候,要注意应用时要加上拉电阻接电源,这样才能保证逻辑的正确,在电阻上要根据逻辑器件的扇入扇出系数来确定,但一般mos电路带载同样的mos电路能力比较强,所以电阻通常可以选择2.2k,4.9k这样一些常用的。

推挽输出与开漏输出的区别推挽输出:可以输出高,低电平,连接数字器件;开漏输出:输出端相当于三极管的集电极. 要得到高电平状态需要上拉电阻才行. 适合于做电流型的驱动,其吸收电流的能力相对强(一般20ma以内).推挽结构一般是指两个三极管分别受两互补信号的控制,总是在一个三极管导通的时候另一个截止.要实现线与需要用OC(open collector)门电路.是两个参数相同的三极管或MOSFET,以推挽方式存在于电路中,各负责正负半周的波形放大任务,电路工作时,两只对称的功率开关管每次只有一个导通,所以导通损耗小,效率高。

输出既可以向负载灌电流,也可以从负载抽取电流。

所谓开漏电路概念中提到的“漏”就是指MOSFET的漏极。

同理,开集电路中的“集”就是指三极管的集电极。

开漏电路就是指以MOSFET的漏极为输出的电路。

一般的用法是会在漏极外部的电路添加上拉电阻。

完整的开漏电路应该由开漏器件和开漏上拉电阻组成。

如图1所示:组成开漏形式的电路有以下几个特点:1. 利用外部电路的驱动能力,减少IC内部的驱动。

当IC内部MOSFET导通时,驱动电流是从外部的VCC流经R pull-up ,MOSFET到GND。

集电极开路与漏极开路 推挽

集电极开路与漏极开路推挽漏极开路是驱动电路的输出三极管的集电极开路,可以通过外接的上拉电阻提高驱动能力。

这种输出用的是一个场效应三极管或金属氧化物管(MOS),这个管子的栅极和输出连接,源极接公共端,漏极悬空(开路)什么也没有接,因此使用时需要接一个适当阻值的电阻到电源,才能使这个管子正常工作,这个电阻就叫上拉电阻。

漏极开路输出,一般情况下都需要外接上拉电阻,以使电路输出呈现三态之高阻态,例如,在有些芯片的引脚就定义为漏极开路输出;还有一些带漏极开路输出的反向器等都需要外接上拉电阻才能正常工作。

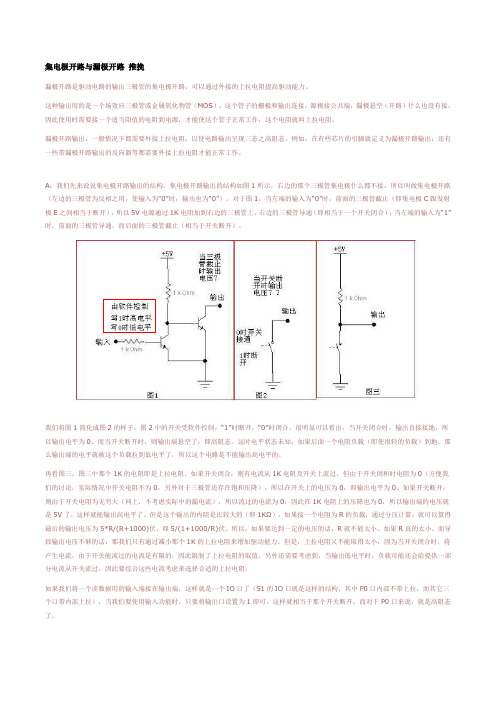

A:我们先来说说集电极开路输出的结构。

集电极开路输出的结构如图1所示,右边的那个三极管集电极什么都不接,所以叫做集电极开路(左边的三极管为反相之用,使输入为“0”时,输出也为“0”)。

对于图1,当左端的输入为“0”时,前面的三极管截止(即集电极C跟发射极E之间相当于断开),所以5V电源通过1K电阻加到右边的三极管上,右边的三极管导通(即相当于一个开关闭合);当左端的输入为“1”时,前面的三极管导通,而后面的三极管截止(相当于开关断开)。

我们将图1简化成图2的样子。

图2中的开关受软件控制,“1”时断开,“0”时闭合。

很明显可以看出,当开关闭合时,输出直接接地,所以输出电平为0。

而当开关断开时,则输出端悬空了,即高阻态。

这时电平状态未知,如果后面一个电阻负载(即使很轻的负载)到地,那么输出端的电平就被这个负载拉到低电平了,所以这个电路是不能输出高电平的。

再看图三。

图三中那个1K的电阻即是上拉电阻。

如果开关闭合,则有电流从1K电阻及开关上流过,但由于开关闭和时电阻为0(方便我们的讨论,实际情况中开关电阻不为0,另外对于三极管还存在饱和压降),所以在开关上的电压为0,即输出电平为0。

如果开关断开,则由于开关电阻为无穷大(同上,不考虑实际中的漏电流),所以流过的电流为0,因此在1K电阻上的压降也为0,所以输出端的电压就是5V了,这样就能输出高电平了。

集电极开路输出、开漏输出、推挽输出

【电子大讲堂】集电极开路输出、开漏输出、推挽输出集电极开路(OC)输出:集电极开路输出的结构如图1所示,右边的那个三极管集电极什么都不接,所以叫做集电极开路(左边的三极管为反相之用,使输入为"0"时,输出也为"0")。

对于图1,当左端的输入为“0”时,前面的三极管截止(即集电极C跟发射极E之间相当于断开),所以5V 电源通过1K电阻加到右边的三极管上,右边的三极管导通(即相当于一个开关闭合);当左端的输入为“1”时,前面的三极管导通,而后面的三极管截止(相当于开关断开)。

我们将图1简化成图2的样子。

图2中的开关受软件控制,“1”时断开,“0”时闭合。

很明显可以看出,当开关闭合时,输出直接接地,所以输出电平为0。

而当开关断开时,则输出端悬空了,即高阻态。

这时电平状态未知,如果后面一个电阻负载(即使很轻的负载)到地,那么输出端的电平就被这个负载拉到低电平了,所以这个电路是不能输出高电平的。

再看图三。

图三中那个1K的电阻即是上拉电阻。

如果开关闭合,则有电流从1K电阻及开关上流过,但由于开关闭和时电阻为0(方便我们的讨论,实际情况中开关电阻不为0,另外对于三极管还存在饱和压降),所以在开关上的电压为0,即输出电平为0。

如果开关断开,则由于开关电阻为无穷大(同上,不考虑实际中的漏电流),所以流过的电流为0,因此在1K电阻上的压降也为0,所以输出端的电压就是5V了,这样就能输出高电平了。

但是这个输出的内阻是比较大的(即1KΩ),如果接一个电阻为R的负载,通过分压计算,就可以算得最后的输出电压为5*R/(R+1000)伏,即5/(1+1000/R)伏。

所以,如果要达到一定的电压的话,R就不能太小。

如果R真的太小,而导致输出电压不够的话,那我们只有通过减小那个1K的上拉电阻来增加驱动能力。

但是,上拉电阻又不能取得太小,因为当开关闭合时,将产生电流,由于开关能流过的电流是有限的,因此限制了上拉电阻的取值,另外还需要考虑到,当输出低电平时,负载可能还会给提供一部分电流从开关流过,因此要综合这些电流考虑来选择合适的上拉电阻。

推挽输出与开漏输出结构和原理详解

推挽输出与开漏输出结构和原理详解推挽输出和开漏输出是指在数字电路中用于驱动外部负载的两种常用结构。

它们在控制信号的输出方式、应用领域和工作原理等方面有所不同。

下面将对推挽输出和开漏输出进行详解。

1.推挽输出结构及原理推挽输出结构是一种常用的数字电路输出结构,它由一个NPN型晶体管和一个PNP型晶体管组成,用于驱动负载。

推挽输出在广泛的应用领域中,如信号灯控制、音频放大器、电机驱动等。

推挽输出的结构示意图如下:```VccR1Input signal/,\NPN PNP Load_______```推挽输出的工作原理如下:(1) 当输入信号为低电平(0V)时,NPN晶体管截止,PNP晶体管饱和,输出接近Vcc电压,负载得到驱动。

(2) 当输入信号为高电平(Vcc)时,NPN晶体管饱和,PNP晶体管截止,输出接近0V,负载失去驱动。

推挽输出的特点:-输出电流能够提供相对较高的电流驱动能力;- 输出电压可以与Vcc相同,也可以与地(GND)相同;-推挽输出的集电极电阻很小,因此可以提供较低的输出电压误差;-适用于推挽驱动、电机驱动、音频放大器等需要提供大电流的应用场景。

2.开漏输出结构及原理开漏输出结构也是一种常用的数字电路输出结构,它通过NPN晶体管或MOSFET管驱动负载。

开漏输出结构广泛应用于数字IC、微控制器、I2C总线等。

开漏输出的结构示意图如下:```VccR1Input signal_____,______ LoadNPNN-MOS```开漏输出的工作原理如下:(1)当输入信号为低电平(0V)时,NPN晶体管截止或MOSFET导通,输出接近0V,负载得到驱动。

(2) 当输入信号为高电平(Vcc)时,NPN晶体管饱和或MOSFET截止,输出为高阻态(Open),负载失去驱动。

开漏输出的特点:-输出电流能够提供相对较高的电流驱动能力;-输出电压只能接近地(GND);-输出电压的高、低电平通过外部上拉电阻(R1)进行限制;-适用于非对称驱动、开关电源控制等需要较高的输出电流和开路状态的应用场景。

推挽输出和开漏输出详解

open-drain与push-pull】GPIO的功能,简单说就是可以根据自己的需要去配置为输入或输出。

但是在配置GPIO管脚的时候,常会见到两种模式:开漏(open-drain,漏极开路)和推挽(push-pull)。

对此两种模式,有何区别和联系,下面整理了一些资料,来详细解释一下:图表?1 Push-Pull对比Open-Drain常见的GPIO的模式可以配置为open-drain或push-pull,具体实现上,常为通过配置对应的寄存器的某些位来配置为open-drain 或是push-pull。

当我们通过CPU去设置那些GPIO的配置寄存器的某位(bit)的时候,其GPIO硬件IC内部的实现是,会去打开或关闭对应的top transistor。

相应地,如果设置为了open-d模式的话,是需要上拉电阻才能实现,也能够输出高电平的。

因此,如果硬件内部(internal)本身包含了对应的上拉电阻的话,此时会去关闭或打开对应的上拉电阻。

如果GPIO硬件IC内部没有对应的上拉电阻的话,那么你的硬件电路中,必须自己提供对应的外部(external)的上拉电阻。

而push-pull输出的优势是速度快,因为线路(line)是以两种方式驱动的。

而带了上拉电阻的线路,即使以最快的速度去提升电压,最快也要一个常量的R×C的时间。

其中R是电阻,C是寄生电容(parasitic capacitance),包括了pin脚的电容和板子的电容。

但是,push-pull相对的缺点是往往需要消耗更多的电流,即功耗相对大。

而open-drain所消耗的电流相对较小,由电阻R所限制,而R不能太小,因为当输出为低电平的时候,需要sink更低的transistor,这意味着更高的功耗。

(此段原文:because the lower transistor has to sink that current when the output is low; that means higher power consumption.)而open-drain的好处之一是,允许你cshort()多个open-drain的电路,公用一个上拉电阻,此种做法称为wired-OR连接,此时可以通过拉低任何一个IO的pin脚使得输出为低电平。

开漏输出与推挽输出

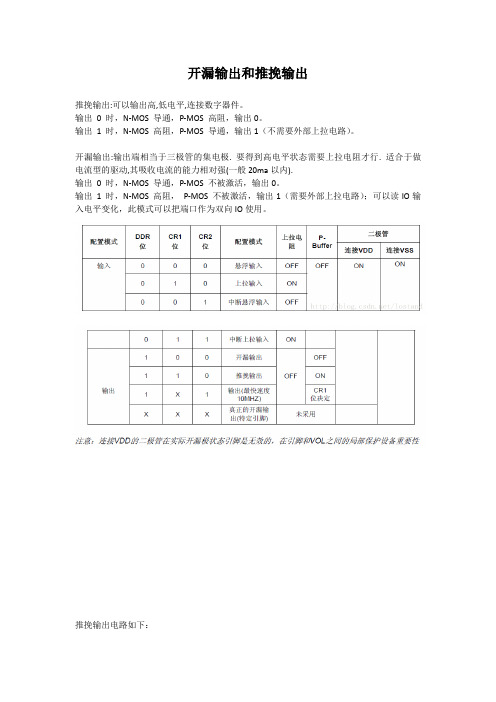

开漏输出和推挽输出推挽输出:可以输出高,低电平,连接数字器件。

输出0 时,N-MOS 导通,P-MOS 高阻,输出0。

输出1 时,N-MOS 高阻,P-MOS 导通,输出1(不需要外部上拉电路)。

开漏输出:输出端相当于三极管的集电极. 要得到高电平状态需要上拉电阻才行. 适合于做电流型的驱动,其吸收电流的能力相对强(一般20ma以内).输出0 时,N-MOS 导通,P-MOS 不被激活,输出0。

输出1 时,N-MOS 高阻,P-MOS 不被激活,输出1(需要外部上拉电路);可以读IO输入电平变化,此模式可以把端口作为双向IO使用。

推挽输出电路如下:上面的三极管是N型三极管,下面的三极管是P型三极管,请留意控制端、输入端和输出端。

当Vin电压为V+时,上面的N型三极管控制端有电流输入,Q3导通,于是电流从上往下通过,提供电流给负载。

经过上面的N型三极管提供电流给负载(Rload),这就叫「推」。

当Vin电压为V-时,下面的三极管有电流流出,Q4导通,有电流从上往下流过。

经过下面的P型三极管提供电流给负载(Rload),这就叫「挽」。

以上,这就是推挽(push-pull)电路。

那么什么是开漏呢?要理解开漏,可以先理解开集。

如图,开集的意思,就是集电极C一端什么都不接,直接作为输出端口。

如果要用这种电路带一个负载,比如一个LED,必须接一个上拉电阻,就像这样。

当Vin没有电流,Q5断开时,LED亮。

当Vin流入电流,Q5导通时,LED灭。

开漏电路,就是把上图中的三极管换成场效应管(MOSFET)。

N型场效应管各个端口的名称:场效应管是电压控制型元器件,只要对栅极施加电压,DS就会导通。

结型场效应管有一个特性就是它的输入阻抗非常大,这意味着:没有电流从控制电路流出,也没有电流进入控制电路。

没有电流流入或流出,就不会烧坏控制电路。

而双极型晶体管不同,是电流控制性元器件,如果使用开集电路,可能会烧坏控制电路。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

7.线与功能主要用于有多个电路对同一信号进行拉低操作的场合,如果本电路不想拉低,就输出高电平,因为OPEN-DRAIN上面的管子被拿掉,高电平是靠外接的上拉电阻实现的。(而正常的CMOS输出级,如果出现一个输出为高另外一个为低

时,等于电源短路。)

8.OPEN-DRAIN提供了灵活的输出方式,但是也有其弱点,就是带来上升沿的延时。因为上升沿是通过外接上拉无源电阻对负载充电,所以当电阻选择小时延时就小,但功耗大;反之延时大功耗小。所以如果对延时有要求,则建议用下降沿输出。

要实现 线与需要用OC(open collector)门电路.是两个参数相同的三极管或MOSFET,以推挽方式存在于电路中,各负责正负半周的波形放大任务,电路工作时,两只对称的功率开关管每次只有一个导通,所以导通损耗小,效率高。输出既可以向负载灌电流,也可以从负载抽取电流。

所谓开漏电路概念中提到的“漏”就是指MOSFET的漏极。同理,开集电路中的“集”就是指三极管的集电极。开漏电路就是指以MOSFET的漏极为输出的电路。一般的用法是会在漏极外部的电路添加上拉电阻。完整的开漏电路应该由开漏器件和开漏上拉电阻组成。如图1所示:

推挽电路是两个参数相同的三极管或MOSFET,以推挽方式存在于电路中,各负责正负半周的波形放大任务,电路工作时,两只对称的功率开关管每次只有一个导通,所以导通损耗小效率

高。

输出既可以向负载灌电流,也可以从负载抽取电流

at91rm9200 GPIO 模拟I2C接口时注意!!

一.什么是OC、OD

集电极开路门(集电极开路 OC 或源极开路OD)

open-drain是漏极开路输出的意思,相当于集电极开路(open-collector)输出,即ttl中的集电极开路(oc)输出。一般用于线或、线与,也有的用于电流驱动。

顺便提示如果不是 OC 或 OD 芯片的输出端是不可以连在一起的, 总线 BUS 上的双向输出端连在一起是有管理的, 同时只能有一个作输出, 而其他是高阻态只能输入.

三.什么是推挽结构

一般是指两个三极管分别受两互补信号的控制,总是在一个三极管导通的时候另一个截止.要实现线与需要用OC(open collector)门电路 .如果输出级的有两个三极管,始终处于一个导通、一个截止的状态,也就是两个三级管推挽相连,这样的电路结构称为推拉式电路或图腾柱(Totem-pole)输出电路(可惜,图无法贴上)。当输出低电平时,也就是下级负载门输入低电平时,输出端的电流将是下级门灌入T4;当输出高电平时,也就是下级负载门输入高电平时,输出端的电流将是下级门从本级电源经 T3、D1 拉出。这样一来,输出高低电平时,T3 一路和 T4 一路将交替工作,从而减低了功耗,提高了每个管的承受能力。又由于不论走哪一路,管子导通电阻都很小,使RC常数很小,转变速度很快。因此,推拉式输出级既提高电路的负载能力,又提高开关速度。供你参考。

注:个人理解:线与,接上拉电阻至电源。(~A)&(~B)=~(A+B),由公式较容易理解线与此概念的由来;

如果用下拉电阻和 PNP 或 PMOS 管就可以构成与非 NAND 逻辑, 或用负逻辑关系转换与/或逻辑.

注:线或,接下拉电阻至地。(~A)+(~B)=~(AB);

这些晶体管常常是一些逻辑电路的集电极开路 OC 或源极开路 OD 输出端. 这种逻辑通常称为线与/线或逻辑, 当你看到一些芯片的 OC 或 OD 输出端连在一起, 而有一个上拉电阻时, 这就是线或/线与了, 但有时上拉电阻做在芯片的输入端内.

开漏输出:OC门的输出就是开漏输出;OD门的输出也是开漏输出。TTL电路有集电极开路OC门,MOS管也有和集电极对应的漏极开路的OD门,它的输出就叫做开漏输出。它可以吸收很大的电流,但是不能向外输出电流。所以,为了能输入和输出电流,它使用的时候要跟电源和上拉电阻一齐用。

二.什么是线或逻辑与线与逻辑?

在一个结点(线)上, 连接一个上拉电阻到电源 VCC 或 VDD 和 n 个 NPN 或 NMOS 晶体管的集电极 C 或漏极 D, 这些晶体管的发射极 E 或源极 S 都接到地线上, 只要有一个晶体管饱和, 这个结点(线)就被拉到地线电平上.

因为这些晶体管的基极注入电流(NPN)或栅极加上高电平(NMOS), 晶体管就会饱和, 所以这些基极或栅极对这个结点(线)的关系是或非 NOR 逻辑. 如果这个结点后面加一个反相器, 就是或 OR 逻辑.

3. 可以利用改变上拉电源的电压,改变传输电平。如图2, IC的逻辑电平由电源Vcc1决定,而输出高电平则由Vcc2决定。这样我们就可以用低电平逻辑控制输出高电平逻辑了。

4. 开漏Pin不连接外部的上拉电阻,则只能输出低电平(因此对于经典的51单片机的P0口而言,要想做输入输出功能必须加外部上拉电阻,否则无法输出高电平逻辑)。

推挽输出与开漏输出的区别

推挽输出:可以输出高,低电平,连接数字器件;开漏输出:输出端相当于三极管的集电极. 要得到高电平状态需要上拉电阻才行. 适合于做电流型的驱动,其吸收电流的能力相对强(一般20ma以内).

推挽结构一般是指两个三极管分别受两互补信号的控制,总是在一个三极管导通的时候另一个截止.

组成开漏形式的电路有以下几个特点:

1. 利用 外部电路的驱动能力,减少IC内部的驱动。当IC内部MOSFET导通时,驱动电流是从外部的VCC流经R pull-up ,MOSFET到GND。IC内部仅需很下的栅极驱动电流。如图1。

2. 可以将多个开漏输出的Pin,连接到一条线上。形成 “与逻辑” 关系。如图1,当PIN_A、PIN_B、PIN_C任意一个变低后,开漏线上的逻辑就为0了。这也是I2C,SMBus等总线判断总线占用状态的原理。

OC门开漏输出和OD门开漏输出都是为了同一个目的,都是为了实现逻辑器件的线与逻辑,当然选用不同的外接电阻也可以实现外围驱动能力的增加。当你应用此电路的时候,要注意应用时要加上拉电阻接电源,这样才能保证逻辑的正确,在电阻上要根据逻辑器件的扇入扇出系数来确定,但一般mos电路带载同样的mos电路能力比较强,所以电阻通常可以选择2.2k,4.9k这样一些常用的。

3.可以利用改变上拉电源的电压,改变传输电平。例如加上上拉电阻就可以提供TTL/CMOS电平输出等。

4.开漏Pin不连接外部的上拉电阻,则只能输出低电平。一般来说,开漏是用来连接不同电平的器件,匹配电平用的。

5.正常的CMOS输出级是上、下两个管子,把上面的管子去:电平转换和线与。

5. 标准的开漏脚一般

只有输出的能力。添加其它的判断电路,才能具备双向输入、输出的能力。

应用中需注意:

1. 开漏和开集的原理类似,在许多应用中我们利用开集电路代替开漏电路。例如,某输入Pin要求由开漏电路驱动。则我们常见的驱动方式是利用一个三极管组成开集电路来驱动它,即方便又节省成本。如图3。

2. 上拉电阻R pull-up的 阻值 决定了 逻辑电平转换的沿的速度 。阻值越大,速度越低功耗越小。反之亦然。

Push-Pull输出就是一般所说的推挽输出,在CMOS电路里面应该较CMOS输出更合适,应为在CMOS里面的push-pull输出能力不可能做得双极那么大。输出能力看IC内部输出极N管P管的面积。和开漏输出相比,push-pull的高低电平由IC的电源低定,不能简单的做逻辑操作等。push-pull是现在CMOS电路里面用得最多的输出级设计方式。

open-drain是对mos管而言,open-collector是对双极型管而言,在用法上没啥区别。

开漏形式的电路有以下几个特点:

1.利用外部电路的驱动能力,减少IC内部的驱动。 或驱动比芯片电源电压高的负载.

2.可以将多个开漏输出的Pin,连接到一条线上。通过一只上拉电阻,在不增加任何器件的情况下,形成“与逻辑”关系。这也是I2C,SMBus等总线判断总线占用状态的原理。如果作为图腾输出必须接上拉电阻。接容性负载时,下降延是芯片内的晶体管,是有源驱动,速度较快;上升延是无源的外接电阻,速度慢。如果要求速度高电阻选择要小,功耗会大。所以负载电阻的选择要兼顾功耗和速度。