数字集成电路低功耗物理实现技术与UPF

5G核心网UPF硬件加速技术

5G核心网UPF硬件加速技术【摘要】5G核心网UPF硬件加速技术是当前5G网络中一个重要的技术领域。

本文首先介绍了UPF硬件加速技术的定义和作用,接着分析了其发展背景和原理实现方式。

然后详细描述了UPF硬件加速技术在5G核心网中的应用,并探讨了其优势和挑战。

在最后部分,文章提出了UPF硬件加速技术未来的发展方向,并强调了其在5G网络中的重要性。

通过本文的研究,读者可以更好地了解5G核心网UPF硬件加速技术的影响和前景,为相关领域的研究和应用提供了重要的参考依据。

【关键词】5G核心网、UPF硬件加速技术、发展背景、原理、实现方式、应用、优势、挑战、发展方向、重要性、影响。

1. 引言1.1 什么是5G核心网UPF硬件加速技术5G核心网中的User Plane Function(UPF)是负责处理数据传输和转发的关键组件。

UPF硬件加速技术是指利用专门的硬件设备加速UPF功能的实现,以提高数据处理效率和网络性能。

通过这种技术,可以加快数据包处理速度,降低延迟,提高网络吞吐量,并支持更多复杂的网络功能。

传统的软件实现方式在处理大规模数据时往往面临性能瓶颈,而UPF硬件加速技术通过利用硬件设备的并行处理能力和高速数据转发能力,能够更有效地处理大量数据流量。

这种技术可以提高数据传输的效率,降低网络负载,提升用户体验。

5G核心网UPF硬件加速技术是一种利用专门硬件加速数据处理和转发的技术,能够提高网络性能和数据处理效率。

在5G网络中,随着数据流量的不断增长和网络服务的不断丰富,UPF硬件加速技术将起到至关重要的作用,推动5G网络的发展和普及。

2. 正文2.1 UPF硬件加速技术的发展背景UPF硬件加速技术的发展背景可以追溯到以太网技术的发展。

以太网技术的不断演进使得网络速度和容量需求不断增加,传统的软件实现方式已经无法满足对速度和效率的需求。

人们开始探索使用硬件加速技术来提高网络设备的性能。

随着5G技术的不断发展,网络对速度和延迟的需求也不断增加。

数字化功率集成电路电路 和智能功率模块

数字化功率集成电路电路和智能功率模块随着科技的不断发展,电力电子技术在现代工业控制中发挥着越来越重要的作用。

数字化功率集成电路和智能功率模块作为电力电子领域的重要技术,为工业控制系统和电力系统的稳定运行提供了强大支持。

本文将从数字化功率集成电路电路和智能功率模块的技术原理、应用特点以及未来发展趋势等方面进行详细介绍。

一、数字化功率集成电路电路1. 技术原理数字化功率集成电路是一种将数字控制和功率驱动功能融合在一起的电子器件。

其核心技术是采用数字信号处理器(DSP)和功率器件相结合,实现对电力系统的精准控制和驱动。

数字化功率集成电路电路可以实现对电压、电流、温度等参数的精确监测和控制,具有高效、快速响应的特点。

2. 应用特点数字化功率集成电路在工业控制系统中具有广泛的应用。

在交流电机驱动、变频空调、工业机器人等领域,数字化功率集成电路可以实现对电机的精准控制,提高系统的效率和稳定性。

数字化功率集成电路还可以在电力系统中实现功率因数校正、无功补偿、谐波抑制等功能,提高电力系统的供电质量。

3. 未来发展趋势随着电力电子技术的不断发展,数字化功率集成电路将会朝着高性能、高集成度、多功能化的方向发展。

未来的数字化功率集成电路将更加注重对功率器件的优化设计,提高工作频率、降低损耗,实现更高效的能量转换。

数字化功率集成电路还将更加注重对通信接口的设计,实现与上层控制系统的无缝衔接,为工业控制和电力系统的智能化发展提供更强大的支持。

二、智能功率模块1. 技术原理智能功率模块是一种将智能控制技术应用于功率器件驱动的电子器件。

其核心技术是采用功率模块和智能控制单元相结合,实现对功率器件的精准控制和保护。

智能功率模块可以实现对电流、电压、温度等参数的实时监测和自适应调节,具有智能化、集成化的特点。

2. 应用特点智能功率模块在电力系统和工业控制系统中具有重要的应用价值。

在电机驱动、电力变流器、电网无功补偿等领域,智能功率模块可以实现对功率器件的优化控制,提高系统的效率和稳定性。

集成电路低功耗设计技术研究

集成电路低功耗设计技术研究随着现代科技的不断发展,人们对于集成电路的需求越来越高,同时也就要求集成电路的设计技术与日俱增。

集成电路低功耗设计技术是目前在集成电路设计领域中最为重要的一个研究方向,本文将就此探讨集成电路低功耗设计技术的研究现状以及未来发展方向。

一、什么是集成电路低功耗设计技术?集成电路低功耗设计技术可以简单理解为,在保证电路性能的同时,并且不影响电路为达成目标所需的功能运行状况的基础上,最小化电路的功耗。

主要采用的方法是降低电路并行、串行和开关频率,模块化和睡眠模式等。

二、集成电路低功耗设计技术的现状1、已有研究成果目前,许多专家学者已在集成电路低功耗设计方面做出了诸多成果。

主要包括晶体管级、电路级和架构级优化设计三个方面。

(1) 晶体管级优化设计在CMOS集成电路中,最大的功耗都在晶体管场效应器上,所以减小晶体管大小就是减低功耗最好的方法。

因此,在进行晶体管级优化设计时,还需考虑一些关键参数常用的尺寸和工艺技术等,来达到低功耗的目标。

(2) 电路级优化设计电路级的优化设计主要通过采用聚合电路(Polyphase Filter)和复合电路(Composite Circuit)等来尽量降低功耗。

具体而言,聚合电路能够使不同电路实现多带宽同时工作,从而避免多路并行的运行产生额外能量消耗;而复合电路可以增加电路输出数值的精度,从而明显的增加运行效率。

(3) 架构级优化设计在架构级的优化设计中,方法主要包括引入功耗控制单元、使用更高性能的编码器和解码器设计来提高运行速率和减低信号传递时的功耗,以及进行睡眠操作等。

2、存在的问题虽然集成电路低功耗设计技术已经取得了一些可喜的成果,但仍面临许多问题。

(1) 性能与功耗之间的平衡在进行集成电路低功耗设计时,低功耗一方面是为了减少能量的消耗,但另一方面,要保证电路的性能和处理速度,这样才能发挥电路的功效。

因此,在设计中,必须考虑功耗与性能之间的平衡。

低功耗和高性能集成电路的设计方法与优化

低功耗和高性能集成电路的设计方法与优化低功耗和高性能集成电路的设计方法与优化随着科技的不断发展,集成电路的应用范围越来越广泛,从智能手机到云计算,从物联网到人工智能,都离不开高性能和低功耗的集成电路。

因此,设计低功耗和高性能的集成电路成为了电子工程师的重要任务之一。

本文将介绍一些常见的设计方法和优化技术,帮助读者更好地理解和应用于实际设计中。

首先,我们来介绍一些常见的低功耗设计方法。

低功耗设计的目标是在满足性能要求的前提下,尽量减少功耗。

以下是一些常见的低功耗设计方法:1. 时钟门控:通过控制时钟信号的开关,可以在需要时打开电路,不需要时关闭电路,从而减少功耗。

2. 电源管理:采用适当的电源管理技术,如电压调节器、睡眠模式等,可以在不需要时降低电路的供电电压和频率,从而减少功耗。

3. 功耗优化电路:通过优化电路结构和逻辑设计,减少功耗。

例如,采用低功耗逻辑门、低功耗时钟电路等。

4. 优化数据传输:采用合适的数据传输方式,如串行传输、差分传输等,可以减少功耗。

接下来,我们来介绍一些常见的高性能设计方法。

高性能设计的目标是在满足功耗要求的前提下,提高电路的运行速度和性能。

以下是一些常见的高性能设计方法:1. 优化时钟频率:通过优化时钟信号的频率和相位,可以提高电路的运行速度。

例如,采用高速时钟发生器、时钟缓冲器等。

2. 优化电路结构:通过优化电路的结构和布局,减少信号传输路径的长度和延迟,从而提高电路的性能。

例如,采用合适的布线规则、缓冲器等。

3. 并行处理:通过采用并行处理技术,将任务分解为多个子任务并行处理,可以提高电路的运算速度和性能。

4. 优化算法:通过优化算法和逻辑设计,减少电路的延迟和功耗。

例如,采用合适的算法和数据结构,减少冗余计算和存储。

除了上述的设计方法外,还有一些常见的优化技术可以同时提高功耗和性能。

例如,采用低功耗的工艺制程、优化功耗和性能的权衡等。

此外,还可以通过仿真和优化工具,如SPICE、Cadence等,进行电路的仿真和优化,以实现更好的功耗和性能。

UPF低功耗设计

UPF低功耗设计

现代固态器件已经非常广泛地应用在各种应用领域,由于固态器件有

更小的尺寸、更低的成本和更好的可靠性,因此越来越多的应用和系统开

始使用固态器件来取代传统的继电器和继电器驱动器。

但是传统的继电器

驱动器可以确保完全断开电路,而电容固态器件(UPF)在断开电路时仍

然会消耗一些能量,从而降低电子系统的效率,这就是为什么系统设计者

需要关注UPF低功耗设计的原因。

首先,需要采用最佳工艺和低功耗的UPF元件。

关键是它能够降低系

统漏电流和电压,从而降低系统耗能,因此UPF元件的低功耗特性对系统

耗能的影响是非常重要的。

其次,需要考虑UPF元件在关断电路时消耗的能量,可以通过调整参

数来减少UPF元件断开电路时消耗的能量,包括调整供电电压、降低驱动

电流、调整电容固态的有效关断速度等。

再次,必须设计UPF元件断开电路时所用的时间,有的时候,UPF元

件的断开时间对系统的功耗和可靠性都有很大的影响。

最后,要通过使用主板和驱动器的技术来改善UPF元件的低功耗特性,比如使用高压主板,可以减少漏电流,降低系统能耗;同时使用低驱动电

流的驱动器。

Low power methodology manual for system-on-chip de

这本ARM和Synopsys合作的《Low Power Methodology Manual》算是Low Power领域的Bible了。既然Synopsys参与了,那里面自然少不了UPF。从作者的背景来看,这本书是偏重实战的,事实的确如此。如果想偏重理论的话,建议看Jan Rabaey的《Low Power Design Essentials》,这本书以后再评。这本《Low Power Methodology Manual》的受众可以涵盖IC架构师、数字前端设 计、后端设计、Custom Design等等。虽然说低功耗技术最有用的还是从算法、架构(包括软件)等high level的方面去考虑更有效,但考虑到每款芯片的服务领域并不相同,抽出共性的难度较大,而从low level一点的电路设计来考虑,就有很多共性了,这也是这本书的着重点:low power的电路的设计与物理级实现。前面我们提过,这本书偏重实战,但也是普通SOC芯片flow里的实战。之所以说“普 通”,还有一些不普通的低功耗设计技术,比如大名鼎鼎的比特币挖矿芯片,它就不适合用普通的flow去做,否则power上必定是没有什么竞争力的。这本书的重点就是power gating、level shifter和retention这些和power gating及多电压域相关的知识。其实这是其中一个维度,还有一个维度是IR drop、in rush current等问题的解决。学习这本书的时候我们可以把这两个维度结合起来,相信会加深 理解。其实我们提到普通低功耗手段,最重要的是clock gating,power gating和voltage sacaling,clock gating解决动态功耗,power gating

基于UPF的低功耗设计的逻辑综合

基于UPF的低功耗设计的逻辑综合基于UPF的低功耗设计的逻辑综合摘要:文章介绍基于UPF的低功耗设计中,各种实现低功耗的策略。

并着重介绍UPF的相关命令及其意义及使用,然后说明UPF低功耗流程中的逻辑综合及步骤。

最后给出总结,以及一些在低功耗下逻辑综合的经验。

关键词:低功耗设计;逻辑综合;UPF中图分类号:TP302文献标识码:A文章编号:1009-3044(2011)16-3955-02UPF-based Logic Synthesis of Low-Power DesignLIU Yi, WU Xiu-long, KE Lie-jin(School of Electronics and Information Engineering, Anhui University, Hefei 230601, China)Abstract: This paper introduces some implementation strategies for UPF-based low-power designs, especially significance and usage of correlative UPF commands. Then it explains UPF-based logic synthesis of low-power design and its steps. Finally given the summary and some experience of low-power logic synthesis.Key words: low-power design; logic synthesis; UPF随着SOC(片上系统)的集成度的扩大和时钟频率的提高,以及便携式的应用的需求片的功耗和面积要求越来越高。

面积制约着芯片的成本,功耗决定芯片的可靠性以及便携设备的电池寿命。

所以在便携式设备上,低功耗设计变得越来越必不可少。

集成电路低功耗设计技术

集成电路低功耗设计技术集成电路(Integrated Circuit,简称IC)是现代电子技术中的重要组成部分,在各种电子设备中广泛应用。

随着科技的进步和市场的需求不断增长,电子设备的功耗问题也日益受到关注。

在集成电路设计中,低功耗设计技术的应用显得尤为重要。

本文将讨论集成电路低功耗设计技术的原理和方法。

低功耗设计技术的背景随着移动设备和物联网技术的快速发展,对于功耗的要求越来越高。

低功耗设计技术的应用能够延长电池寿命,减少设备发热以及提高电池充电效率。

因此,低功耗设计技术已经成为集成电路设计的关键考虑因素。

低功耗设计技术的原理低功耗设计技术的原理是通过降低集成电路的功耗来实现节能的目标。

主要采用以下几种方法来实现:1. 逻辑门的优化设计:逻辑门通常是芯片中最耗电的部分。

优化逻辑门的设计可以减少功耗。

例如,采用低阈值电压晶体管和有选择地禁用部分逻辑门等方法,能有效降低功耗。

2. 时钟管理技术:芯片上的时钟频率和功耗是成反比的。

通过合理的时钟设计,可以降低芯片功耗。

例如,使用自适应时钟技术,根据芯片的工作负载动态调整时钟频率,在降低功耗的同时保持系统的性能。

3. 状态优化技术:大部分电子设备在使用过程中都存在空闲状态。

通过设计合理的状态优化技术,可以将处于空闲状态的部分电路降低功耗。

例如,采用局部时钟门控技术,只在需要时打开关键电路,延长电池寿命。

4. 电源管理技术:对于移动设备来说,电池寿命是一个重要的指标。

通过采用先进的电源管理技术,例如多电源域设计、电源适应性调整等方法,可以最大限度地降低功耗。

5. 快速快速启动和休眠技术:集成电路在启动和休眠过程中消耗较高的功耗。

采用快速启动和休眠技术可以缩短启动和休眠时间,减少功耗。

低功耗设计技术的应用低功耗设计技术在各种领域都有广泛的应用。

其中,移动设备、物联网设备和便携式电子设备是低功耗设计技术的主要应用领域。

在移动设备中,如智能手机、平板电脑等,低功耗设计技术能延长电池使用时间,用户无需频繁充电,提供更好的使用体验。

一种低功耗系统芯片的可测试性设计方案

一种低功耗系统芯片的可测试性设计方案徐太龙;鲁世斌;代广珍;孟坚;陈军宁【摘要】低功耗技术,如多电源多电压和电源关断等的应用,给现代超大规模系统芯片可测试性设计带来诸多问题。

为此,采用工业界认可的电子设计自动化工具和常用的测试方法,构建实现可测试性设计的高效平台。

基于该平台,提出一种包括扫描链设计、嵌入式存储器内建自测试和边界扫描设计的可测性设计实现方案。

实验结果表明,该方案能高效、方便和准确地完成低功耗系统芯片的可测性设计,并成功地在自动测试仪上完成各种测试,组合逻辑和时序逻辑的扫描链测试覆盖率为98.2%。

%The low power design technologies such as Multi-supply Multi-voltage(MSMV) and Power Shut-off(PSO), present many challenges for the testability design of modern very large scale integration System-on-chip(SoC). Based on the efficient implementation platform constructed by using the industrial electronic design automation tools and the widely used testability methods, a testability design scheme that includes the scan chain, memory built-in-self-test and boundary scan is proposed. Experimental results show that the scheme can efficiently, conveniently and accurately complete the testability design of low power consumption SoC, and works correctly in automation test equipment. The test coverage of combinational and sequential logic scan chains is 98.2%.【期刊名称】《计算机工程》【年(卷),期】2014(000)003【总页数】4页(P306-309)【关键词】可测试性设计;低功耗;系统芯片;内建自测试;电源关断;多电源多电压;扫描链【作者】徐太龙;鲁世斌;代广珍;孟坚;陈军宁【作者单位】安徽大学电子信息工程学院安徽省集成电路设计实验室,合肥230601;安徽大学电子信息工程学院安徽省集成电路设计实验室,合肥 230601; 合肥师范学院电子信息工程学院,合肥 230601;安徽大学电子信息工程学院安徽省集成电路设计实验室,合肥 230601;安徽大学电子信息工程学院安徽省集成电路设计实验室,合肥 230601;安徽大学电子信息工程学院安徽省集成电路设计实验室,合肥 230601【正文语种】中文【中图分类】TN47随着半导体技术的发展,芯片的集成度逐步提高,越来越多的功能模块被集成在同一个芯片上,形成系统芯片(System-on-chip, SoC)[1-2]。

基于IEEE1801(UPF)的低功耗设计流程

基于IEEE1801(UPF)的低功耗设计流程基于IEEE1801(UPF)标准的低功耗设计实现流程摘要⽬前除了时序和⾯积,功耗已经成为集成电路设计中⽇益关注的因素。

当前有很多种降低功耗的⽅法,为了在设计实现流程中更加有效的利⽤各种低功耗的设计⽅法,我们在最近⼀款芯⽚的设计实现以及验证流程中,使⽤了基于IEEE1801标准Unified Power Format(UPF)的完整技术,成功的完成了从RTL到GDSII 的全部过程,并且芯⽚制造回来成功的完成了测试。

本⽂就其中的设计实现部分进⾏了详细探讨,重点介绍如何⽤UPF把我们的低功耗意图描述出来以及如何⽤Synopsys⼯具实现整个流程,希望给⼤家以启发。

本⽂先介绍⽬前常⽤的低功耗设计的⼀些⽅法特别是⽤power-gating的⽅法来控制静态功耗以及UPF 的实现⽅法,然后阐述UPF在我们设计流程中的应⽤,并在介绍中引⼊了⼀些我们的设计经验,最后给出我们的结论。

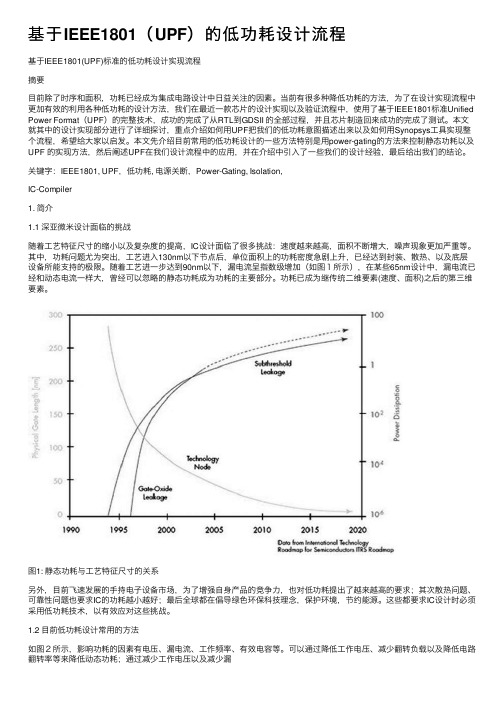

关键字:IEEE1801, UPF,低功耗, 电源关断,Power-Gating, Isolation,IC-Compiler1. 简介1.1 深亚微⽶设计⾯临的挑战随着⼯艺特征尺⼨的缩⼩以及复杂度的提⾼,IC设计⾯临了很多挑战:速度越来越⾼,⾯积不断增⼤,噪声现象更加严重等。

其中,功耗问题尤为突出,⼯艺进⼊130nm以下节点后,单位⾯积上的功耗密度急剧上升,已经达到封装、散热、以及底层设备所能⽀持的极限。

随着⼯艺进⼀步达到90nm以下,漏电流呈指数级增加(如图1所⽰),在某些65nm设计中,漏电流已经和动态电流⼀样⼤,曾经可以忽略的静态功耗成为功耗的主要部分。

功耗已成为继传统⼆维要素(速度、⾯积)之后的第三维要素。

图1: 静态功耗与⼯艺特征尺⼨的关系另外,⽬前飞速发展的⼿持电⼦设备市场,为了增强⾃⾝产品的竞争⼒,也对低功耗提出了越来越⾼的要求;其次散热问题、可靠性问题也要求IC的功耗越⼩越好;最后全球都在倡导绿⾊环保科技理念,保护环境,节约能源。

基于UPF的低功耗设计的逻辑综合

基于UPF的低功耗设计的逻辑综合作者:刘毅,吴秀龙,柯烈金来源:《电脑知识与技术》2011年第16期摘要:文章介绍基于UPF的低功耗设计中,各种实现低功耗的策略。

并着重介绍UPF的相关命令及其意义及使用,然后说明UPF低功耗流程中的逻辑综合及步骤。

最后给出总结,以及一些在低功耗下逻辑综合的经验。

关键词:低功耗设计;逻辑综合;UPF中图分类号:TP302文献标识码:A文章编号:1009-3044(2011)16-3955-02UPF-based Logic Synthesis of Low-Power DesignLIU Yi, WU Xiu-long, KE Lie-jin(School of Electronics and Information Engineering, Anhui University, Hefei 230601, China)Abstract: This paper introduces some implementation strategies for UPF-based low-power designs, especially significance and usage of correlative UPF commands. Then it explains UPF-based logic synthesis of low-power design and its steps. Finally given the summary and some experience of low-power logic synthesis.Key words: low-power design; logic synthesis; UPF随着SOC(片上系统)的集成度的扩大和时钟频率的提高,以及便携式的应用的需求片的功耗和面积要求越来越高。

面积制约着芯片的成本,功耗决定芯片的可靠性以及便携设备的电池寿命。

基于UPF的低功耗设计的逻辑综合

基于UPF的低功耗设计的逻辑综合

刘毅;吴秀龙;柯烈金

【期刊名称】《电脑知识与技术》

【年(卷),期】2011(007)016

【摘要】文章介绍基于UPF的低功耗设计中,各种实现低功耗的策略.并着重介绍UPF的相关命令及其意义及使用,然后说明UPF低功耗流程中的逻辑综合及步骤.最后给出总结,以及一些在低功耗下逻辑综合的经验.

【总页数】3页(P3955-3956,3973)

【作者】刘毅;吴秀龙;柯烈金

【作者单位】安徽大学,电子信息工程学院,安徽,合肥,230601;安徽大学,电子信息工程学院,安徽,合肥,230601;安徽大学,电子信息工程学院,安徽,合肥,230601

【正文语种】中文

【中图分类】TP302

【相关文献】

1.14nm工艺下基于CUPF的数字IC低功耗物理设计 [J], 高华;李辉

2.65纳米工艺下逻辑综合阶段的低功耗策略 [J], 刘剑婷;林平分

3.基于UPF的芯片低功耗设计实现 [J], 杨宇

4.基于UPF的低功耗设计的逻辑综合 [J], 刘毅;吴秀龙;柯烈金

5.SoC设计中的低功耗逻辑综合策略 [J], 王丽英;杨军;罗岚

因版权原因,仅展示原文概要,查看原文内容请购买。

数字集成电路低功耗物理实现技术与UPF

数字集成电路低功耗物理实现技术与UPF孙轶群sun.yiqun@国民技术股份有限公司Nationz Technologies Inc摘要本文从CMOS电路功耗原理入手,针对不同工艺尺寸下数字集成电路的低功耗物理实现方法进行描述,并着重描述了Synopsys UPF(Unified Power Format)对低功耗设计的描述方法。

UPF是Synopsys公司提出的一种对芯片中电源域设计进行约束的文件格式。

通过与UPF 格式匹配的Liberty文件,UPF约束文件可以被整套Galaxy物理实现平台的任何一个环节直接使用,并将设计者的电源设计约束传递给设计工具,由工具完成设计的实现工作,从而实现整套数字集成电路低功耗物理实现的流程。

1.0 概述本文从数字集成电路低功耗设计原理下手,对设计中低功耗的实现技术进行描述,包括完成低功耗设计需要的库资料以及常用EDA工具对低功耗技术实现的方法。

2.0 CMOS电路的低功耗设计原理CMOS电路功耗主要分3种,静态功耗主要与工艺以及电路结构相关,短路电流功耗主要与驱动电压、p-MOS和n-MOS同时打开时产生的最大电流、翻转频率以及上升、下降时间有关,开关电流功耗主要与负载电容、驱动电压、翻转频率有关。

做低功耗设计,就必须从这些影响功耗的因素下手。

3.0 低功耗设计手段及Library需求低功耗的设计手段较为复杂,但对于不同的设计,或者不同的工艺,实现的方法却各不相同。

3.1 0.18um及以上工艺0.18um及以上工艺,在低功耗设计手段上较为有限,主要原因在于,静态功耗很小,基本不用关心。

动态功耗方面,主要的功耗来自于Switching Power,即与负载电容、电压以及工作中的信号翻转频率相关。

减小负载电容,就必须在设计上下功夫,减少电路规模。

减少信号翻转频率,除了降低时钟频率外,只有在设计上考虑,能不翻转的信号就不翻转。

至于电压,由于0.18um及以上工艺的阈值电压有一定的限制,因此,供电电压降低,势必影响工作频率。

基于upf的低功耗设计方法研究与实现

摘要摘要随着集成电路设计技术的不断发展及半导体工艺的进步,芯片的集成度、复杂度不断提高并且工作频率也得到大幅度提升,这导致芯片的功率密度显著增大,其工作时产生的功耗急剧增加。

功耗的增加增大了芯片测试的难度,同时对芯片的散热和封装提出了更加严苛的要求。

另外,为了符合节能规范的要求以及迫于市场的压力,降低芯片的功耗已是大势所趋。

功耗已成为VLSI设计优化中继速度、面积之后另一个须考虑的重要因素。

本课题来源于实习期间所做的项目,研究了集成电路的低功耗设计方法并对显卡芯片中的一个接口模块进行了低功耗设计。

本文首先研究了集成电路中功耗的组成(包括静态功耗与动态功耗)和各种低功耗设计方法。

其次,本文还研究了统一功率格式UPF标准以及用UPF进行低功耗设计的流程。

通过把功耗相关信息统一描述在一个UPF文件中,并在整个集成电路设计流程中都采用这个UPF文件所提供的功耗意图,从而在很大程度上降低了低功耗设计的复杂度以及风险。

然后采用以下低功耗设计技术对接口模块进行低功耗设计:1)多阈值电压技术:用多阈值电压库进行综合,即采用one-pass流程。

2)门控时钟技术:在逻辑综合阶段,利用工具Design Compiler自动完成时钟门控单元的插入,无需修改RTL代码。

3)多电压域和门控电源技术:在逻辑功能描述正确的基础上,使用UPF来描述低功耗设计的意图、指标及参数,并且完成了基于UPF的逻辑综合。

最后,利用形式验证工具Formality对原始的RTL+ UPF文件与综合后的门级网表+新产生的UPF文件UPF’进行了等价性检查,用工具VCS对RTL和UPF进行了带电源信息的仿真(Power Aware Simulation),以此验证了低功耗设计的正确性。

此外,在低功耗设计正确的基础上,本文通过分析和比较采用不同技术进行低功耗设计前后的功耗结果,得出了以下结论:采用多阈值电压技术后明显改善了静态功耗,门控时钟技术可显著降低动态功耗,而门控电源和多电压域技术能同时降低动态功耗和静态功耗,可最大程度地节省功耗。

超深亚微米工艺下基于upf的低功耗设计方法

目录

目录

第一章 绪论 ...................................................................................................................... 1 1.1 背景介绍 ................................................................................................................. 1 1.2 数字基带芯片简介 ................................................................................................. 1 1.3 本文的主要工作和内容 ......................................................................................... 2

第三章 电压区域划分及 UPF 实现...............................................................................21 3.1 电压区域的划分 ................................................................................................... 21 3.2 UPF 的实现 ...........................................................................................................25 3.2.1 电压区域和电源网络..................................................................................... 25 3.2.2 隔离单元和电压转换单元............................................................................. 28 3.2.3 电压状态表..................................................................................................... 32 3.3 电压区域和电源网络的控制 ............................................................................... 32 3.3.1 电源控制时序................................................................................................. 32

浅谈CMOS集成电路低功耗设计

浅谈CMOS集成电路低功耗设计李名扬 20102466摘要:本文在对CMOS电路功耗来源分析的基础上,提出了降低电源电压、降低负载电容、降低开关活动性跳变率、调整晶体管的尺寸、降低MOS管的阈值电压等降低功耗的方法,然后介绍了CMOS集成电路低功耗设计中应注意的问题,最后对未来CMOS集成电路的发展进行了展望。

关键词:CMOS集成电路,低功耗,阈值电压,门控时钟1引言随着CMOS集成电路的规模越来越大,工作频率不断提高,芯片的功耗也越来越大,这就给电路的使用带来了两个负面的影响。

首先,为延长工作时间需要提高电源性能;其次,由于电路只能在一定的温度范围内工作,需要更精确的封装和良好的散热性能,这无疑会增加成本。

功耗特别是功耗密度问题变得越来越突出,将成为影响电路性能的关键问题。

功耗密度的增加将引起芯片温度升高,影响电路的可靠性,芯片温度每升高10℃,器件寿命将减少一半。

为了避免芯片发热,则要花费更多的成本解决芯片封装和冷却问题。

另外,VLSI的发展使整机体积缩小,促进了各种微小型的便携机和便携式设备的发展。

靠电池供电的便携式设备及航空航天设备都需要低功耗电路以维持更长的电池寿命。

因此,降低功耗是CMOS集成发展的需求,低功耗设计已成为一个关键的设计考虑。

以下从低功耗技术研究的意义开始,逐步介绍一下有关CMOS集成电路低功耗设计的方法及注意问题。

2低功耗技术的研究意义低功耗技术是上世纪九十年代开始由于实际应用需要受到广泛关注而迅速发展起来的,并且在集成电路设计中的重要性也随着工艺的发展越来越凸显。

促进低功耗技术研究的因素有很多,概括起来主要有以下几点:1.电路的可靠性电路的功耗将转化为热量而释放出来,过多的热量将导致期间工作温度升高,继而降低系统的可靠性,导致许多问题产生。

工作温度过高将使各种制造是的轻微物理缺陷所造成的故障显现出来,如桥接故障。

温度的提高意味着电迁移率的增加,当芯片温度上升到一定程度时,电路将无法正常工作。

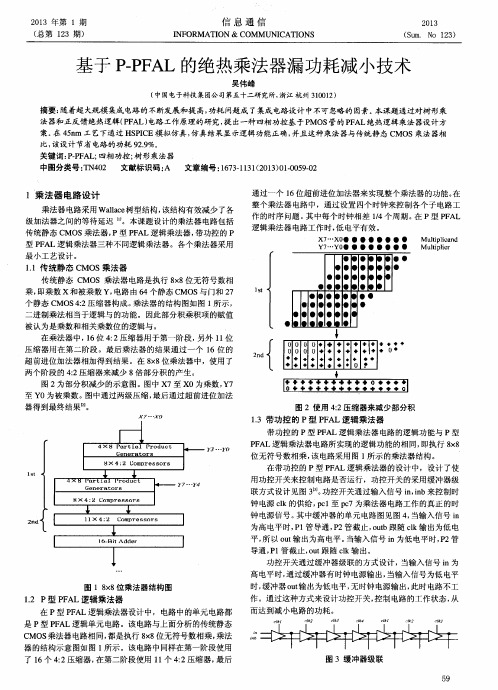

基于P-PFAL的绝热乘法器漏功耗减小技术

钟 电源信号 。 其中缓冲器 的单元 电路 图见 图 4 , 当输入信号 i n 为高 电平 时, P 1 管导通 , P 2管截止 , o u t b跟 随 c l k输 出为低 电

平, 所 以o u t 输 出为高 电平 。 当输入信号 i n为低 电平时, P 2管 导通 , P 1管截 止, o u t 跟随 c l k输出。 功控开关通过缓冲器 级联 的方式设计,当输入信号 i n为

x7- - - Xn

● 0 O 驰 4 ● 1 . + ● ● + 0 : l ◆ :

●

0●

●

I ● ●● ● ● ● ● ●● O ◆ ◆◆ l l 0●● ● 4 1 "● 4 1 .● ● ● ● ● ◆ , I b◆ Ol

图 2使 用 4 : 2压缩器来减少部分积

比, 该设 计节省电路 的功耗 9 2 . 9 %。 关键词 : P . P F AL ; 四相功控 ; 树 形乘法器

中图分类号 : T N 4 0 2 文献标识码 : A 文章编号 : 1 6 7 3 — 1 1 3 1 ( 2 0 1 3 ) 0 1 . 0 0 5 9 . 0 2 通 过一个 1 6位超前进位加 法器 来实现整个乘法器 的功能 。 在 整 个乘法器 电路 中,通过设置 四个 时钟来控制各个 子电路工

高 电平时 , 通 过缓冲器有时钟 电源输 出, 当输 入信 号为低 电平

图 1 8 x 8 位乘法器结构 图 时, 缓冲器 o u t 输 出为低 电平 , 无时钟 电源输 出, 此时电路不工

1 . 2 P型 P F A L逻辑 乘法 器

在 P型 P F A L逻辑乘法器设计 中,电路 中的单 元电路都

作的时序 问题 。 其 中每 个时钟相差 1 / 4个周期 。 在 P型 P F AL 逻 辑乘 法器 电路工作时 , 低 电平 有效。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

数字集成电路低功耗物理实现技术与UPF孙轶群sun.yiqun@国民技术股份有限公司Nationz Technologies Inc摘要本文从CMOS电路功耗原理入手,针对不同工艺尺寸下数字集成电路的低功耗物理实现方法进行描述,并着重描述了Synopsys UPF(Unified Power Format)对低功耗设计的描述方法。

UPF是Synopsys公司提出的一种对芯片中电源域设计进行约束的文件格式。

通过与UPF 格式匹配的Liberty文件,UPF约束文件可以被整套Galaxy物理实现平台的任何一个环节直接使用,并将设计者的电源设计约束传递给设计工具,由工具完成设计的实现工作,从而实现整套数字集成电路低功耗物理实现的流程。

1.0 概述本文从数字集成电路低功耗设计原理下手,对设计中低功耗的实现技术进行描述,包括完成低功耗设计需要的库资料以及常用EDA工具对低功耗技术实现的方法。

2.0 CMOS电路的低功耗设计原理CMOS电路功耗主要分3种,静态功耗主要与工艺以及电路结构相关,短路电流功耗主要与驱动电压、p-MOS和n-MOS同时打开时产生的最大电流、翻转频率以及上升、下降时间有关,开关电流功耗主要与负载电容、驱动电压、翻转频率有关。

做低功耗设计,就必须从这些影响功耗的因素下手。

3.0 低功耗设计手段及Library需求低功耗的设计手段较为复杂,但对于不同的设计,或者不同的工艺,实现的方法却各不相同。

3.1 0.18um及以上工艺0.18um及以上工艺,在低功耗设计手段上较为有限,主要原因在于,静态功耗很小,基本不用关心。

动态功耗方面,主要的功耗来自于Switching Power,即与负载电容、电压以及工作中的信号翻转频率相关。

减小负载电容,就必须在设计上下功夫,减少电路规模。

减少信号翻转频率,除了降低时钟频率外,只有在设计上考虑,能不翻转的信号就不翻转。

至于电压,由于0.18um及以上工艺的阈值电压有一定的限制,因此,供电电压降低,势必影响工作频率。

一般说来,在0.18um工艺下设计电路,主要有以下几种对低功耗设计的考虑。

3.1.1 静态功耗可以忽略根据现有项目经验可知,利用0.18um工艺Standard Cell设计出来的某芯片,数字逻辑加上Ram和Rom约40万门的电路,在完全静止的状态下,功耗约200uA左右(实测数据为400uA 左右,包括了50uA Flash,30uA的PHY,113uA的VR,其他模拟部分漏电不大,因此这里估算为200uA)。

这样的功耗,我们是可以接受的。

如果非要减少静态功耗,则可以参照90nm工艺的设计思路,专门设计高阈值电压的MOSFET,或者专门设计切断电源所需的元件,但由此带来设计的复杂性,对0.18um工艺的影响还是很大的。

如果设计规模没有那么大,且可以满足应用,往往还是可以忽略这个结果的。

3.1.2 时钟门控减小不必要的动态功耗在寄存器的电路设计中,时钟输入端都会有一个反向器负载,就算输入端不发生变化,时钟的变化也会造成该反向器的变化,由此产生动态功耗。

因此在如果该寄存器输入在某种条件下等于输出(即输出保持)时,可以将时钟门控住,以减少无效的时钟翻转。

时钟门控的实现原理如下图所示:图3-1 时钟门控原理图如上图所示,由于现在的设计方式,大多数是同步设计,设计人员只考虑数据路径,时钟往往是不做处理的。

因此如果要实现门控,只需要在设计电路时提供可以识别的控制信号,在综合的时候,EDA工具就可以自动插入时钟门控。

利用Design Compiler进行时钟门控单元插入,在读入设计以及时序约束后,需要做以下设置:1.set_clock_gating_style,设置时钟门控单元插入的约束2.insert_clock_gating –global,开始插入时钟门控单元;3.uniquify,将所有时钟门控单元做uniquify操作,以便后续PR4.hookup_testports -se_port ATPGSE_Pad -se_pin uPad/uATPGSE_Pad/C –verbose,将所有时钟门控单元的scan_enable信号与测试用SE信号连接起来。

如果没有ATPG,可以不用该句命令。

5.propagate_constraints -gate_clock,将门控单元信息传递给整个电路。

6.report_clock_gating可以查看时钟门控单元插入的情况,以便做电路修改,或插入时钟门控单元设置的修改。

完成这些设置后,只需要和平常一样做系统综合即可。

而在DC 2008.09版本以后,第2~5的步骤都可以省略,在利用compile_ultra进行优化时,第2、3步骤都会被自动执行,第4、5步骤会在insert_dft时被执行。

形式验证工具Formality,在进行形式验证,需要设置verification_clock_gatie_hold_mode为low、high或者any,Formality就可以识别出时钟门控单元,并与RTL进行形式验证了。

3.1.2.1. Clock Gating Cells这里所说的Clock Gating Cell是指专门设计的,集成式时钟门控单元(Integrated Clock Gating Cell,简称ICG),就是利用Latch和与门/或门实现的一个独立的Standard Cell,其优势在于以硬IP实现,时序易于掌握,物理实现中对布局布线有帮助。

当然如果单元库中不提供专门的时钟门控单元,EDA工具也可以利用与门、或门、Latch甚至是寄存器等进行门控单元的实现,但效果都没有ICG好用。

这里针对ICG的插入进行描述。

图3-1中的门控单元是一种典型的,利用负沿使能Latch以及与门组成的上升沿有效时钟门控单元,只有时钟下降沿后才会将时钟门控住,保证不产生时钟毛刺。

在Liberty格式文件中,某个Cell,需要有clock_gating_integrated_cell,才能让EDA工具认识到,该Cell是一种ICG。

不同的clock_gating_integrated_cell的设置,需要在DC设置set_clock_gating_style时做相应的设置,才可能被使用到,下面列举一些常用的设置:同时,在ICG的不同Pin上,必须有以下属性,来告诉DC该Pin在ICG的使用中是什么功能(这里只列举常用的信息):3.1.3 使用低电压的库进行设计由于动态功耗中,驱动电压对功耗的影响也相当大,因此,如果能有一套电压只有1V的标准单元库,进行设计,仍然可以达到降低动态功耗的目的。

但电压的降低,势必引起元件延时的增加,且由于0.18um工艺下,阈值电压一般在0.4V左右,驱动电压的稳定性需求也相当大,否则,可能会导致致命性的错误。

法国的Dolphin公司是一家致力于低功耗设计的IP提供商,在TSMC、SMIC等Foundry的0.18um工艺下都提供了1V的逻辑单元库。

下面列出Dolphin在SMIC 0.18um工艺下设计的一套1V逻辑单元库,和SMIC 0.18um工艺Metro标准单元库进行比较。

比较中Metro标准单元库使用1个门的BUFX2M,而Dolphin使用最小的Buffer ni01d1进行比较。

由比较中可以看出,当电压下降到1V后,Rise Energy下降了80%以上,除了由于电压下降引起的功耗降低外,Dolphin应该在电路结构等方面也做了处理,因此不但动态功耗减少了,而且静态功耗也减少了很多。

但延时却大了很多,因此如果设计需要翻转的频率不高时,可以考虑利用低功耗的库进行设计,达到降低功耗的目的。

如果速度要求很高,这个方法是不可行的。

3.2 90nm及以下工艺从3.1.3可以知道,降低驱动电压,可以减少动态功耗,但由于电压降低,驱动能力也同时被减弱,因此元件延时较大。

为了解决这个问题,工艺尺寸开始减小,以便在减小驱动电压的情况下,增加宽长比(aspect ratio),以达到提高驱动电流的目的,保持元件延时。

同时进入更低尺寸的工艺,氧化层厚度也随之减小,以便减少阈值电压,进一步提高速度。

但因为氧化层厚度在减小,漏电电流也变大了。

在90nm及以下工艺中,漏电电流开始被设计人员关注。

下面对在90nm工艺下进行低功耗设计及实现的一些手段结合常用EDA工具进行描述。

3.2.1 切断未使能电路的电源减小不必要的静态功耗针对SMIC 0.18um工艺Metro标准单元库以及TSMC 90nmLP工艺高密度标准单元库(dbtcbn90lphdbwptc)进行比较,以一个门的Buffer来举例:Average Incremental T ypical Rise I ncrementalleakage(nW) Energe(0.04pf,pJ)SMIC18 METRO BUFX2M 0.048 - 0.0266 -TSMC 90LP BiasedWell BUFFD1BWP 0.214 345.83% 0.00272 -89.77%可以看出,90nm工艺下的静态功耗,已经是0.18um工艺下功耗的3.5倍左右了。

根据3.1.1可知,利用0.18um设计出来的,约40万门的电路,静态功耗,大约是200uA(360uW,0.18um工艺按1.8V供电电压计算)。

如果同样规模的电路,放在90nm工艺下,则可能达到1.26mW左右,即1.05mA左右的静态功耗(90nm工艺按1.2V供电电压计算)。

既然,静态功耗这么大,那么在静止时,怎样才能将这些功耗减小呢?一个非常彻底的方法就是将静止状态电路的电源关断。

为了关断电源,就需要在电源网络和电路之间建立一个电源控制电路,他们被称为电源开关单元(Power Switching Cell),在需要关断时,控制Power Switching Cell将电路的供电关闭,否则打开,提供电源。

由于电源关断后的电路,其输出信号就没有电路驱动,对于其驱动的电路来说,就会出现输入浮空的状态。

为了解决这个问题,就需要在关闭电源的电路输出端添加一个额外的保持电路,当其电源关闭后保持输出,而电源打开时,保持电路则表现的像一个Buffer,输出等于输入即可。

同时,如果被关闭电源地电路输入固定电压,也可能产生对地的电流,就需要一个特别的单元对该部分电流进行保护。

这样的单元被称为隔离单元(Isolation Cell)。

一般来说Isolation Cell的输出部分有较大的电容负载,也就是说Isolation Cell的延时将会比较大,对时序有一定的影响,是需要注意的。

当然,对于寄存器来说,如果断电,则原有的数据就无法保存,重新打开电源后,就一定会出现原有数据丢失的情况。