第三周学习总结-CMOS反相器

COMS反相器原理

Y

VDD

B

图3-5-14 带缓冲级的与非门

A

上述电路虽然简单;但存在一些严重缺点: 1 输出电阻受输入端状态的影响; 2 当输入端数目增多时;输出低电平也随着相应提高;使低电平噪声容限降低

3 5 CMOS电路

3 5 1 CMOS反相器工作原理

3 5 2 CMOS反相器的主要特性

3 5 3 CMOS传输门

3 5 4 CMOS逻辑门电路

3 5 5 CMOS电路的锁定效应及 正确使用方法

图351 CMOS反相器

D

G

S

S

G

D

vO

VDD

TL

T0

vI

3 5 1 CMOS反相器工作原理

CMOS反相器由一个P沟道增强型MOS管和一个N沟道增强型MOS管串联组成 通常P沟道管作为负载管;N沟道管作为输入管

第一种形式: 在反相器基础上增加一对P沟道T'P和N沟道T'N MOS管 当控制端为1时;T'P和T'N同时截止;输出呈高阻态;当控制端为0时;T'P和T'N同时导通;反相器正常工作 该电路为低电平有效的三态输出门

EN

图3516 三态输出CMOS门结构之二

A

Y

VDD

≥1

TN

TP

A

Y

&

TN

当输入vI为高电平时;负载管截止;输入管导通;负载电流IOL灌入输入管;如图356 所示 灌入的电流就是N沟道管的iDS;输出特性曲线如图357 所示 输出电阻的大小与vGSNvI有关;vI越大;输出电阻越小;反相器带负载能力越强

实验三 CMOS反相器瞬态特性

实验三CMOS反相器瞬态特性姓名学号➢CMOS反相器上升、下降及延迟时间1.为实验二中新建的CMOS反相器“inv”建立逻辑符号“symbol”,“checkand save”没有error之后将其截屏粘贴复制到以下空白中:通常作为输入脉冲的上升时间和下降时间均为10ps,除此之外,其它参数可以自由设定(如Delay time = 10ns,Pulse width=20ns,Period=50ns),但要与最终总的瞬态仿真时间对应起来。

3.将脉冲电压源vpulse的参数设置好以后,在模拟环境(AnalogEnvironment)中选择运行瞬态仿真“tran”,只需给定总的仿真时间,然后选择plot输入与输出节点。

在开始运行之前,可以预先估计一下会得到什么样的波形,然后与仿真后得到的波形相对比,并将仿真得到的波形截屏粘贴在以下空白处:4.在波形窗口中,使用“Trace —> Delta cursor”观察,比较并记录输出电压中对应的上升时间t r和下降时间t f(10%~90%)。

思考:输出电压中的上升时间和下降时间分别是由哪个晶体管决定?在采取同样参数设计的情况下,为什么会存在着上升下降时间的不同?上升时间由P管的尺寸决定,下降时间由N管的尺寸决定由于导电因子迁移率不同,所以对称设计的上升下降时间不同5.参照讲义,观察并记录输出电压由高到低变化时对应的延迟时间t PHL和由低到高变化时对应的延迟时间t PLH,并计算总的延迟时间t pdtPHI=21.724pstPLH=68.860pstPD=45.292ps6. 通过修改PMOS管和NMOS管的宽长尺寸,将输出电压中的上升时间和下降时间调到大致相等,记录优化后的两管宽长尺寸及其宽长比的比值(W/L)PMOS/(W/L)NMOS。

将上述宽长比的比值与实验二中逻辑阈值等于0.9V 时的宽长比的比值做比较,看它们是否一样?最后,将放大后带有“Delta cursor”的输入输出曲线上升和下降部分分别截屏并粘贴到以下空白处。

第三章CMOS反相器介绍及设计

V0

Vdd

0≤Vi<Vtn时: n截止 p线性 (Vi<vtn<v0+Vtp) p管无损地将Vdd传送到输出端:

Vth

V0=Vdd, 如图a——b段。 Vtn≤Vi<V0+Vtp时: n饱和 p线性 由In=-Ip得:

a----b b----c c----d d----e e----f

Vi

一、结构特点

第二节 CMOS反相器

IN

nMOS和pMOS交替导通 高电Dep平artm-ent“of M1ic”roe为lectrVonDicsD, P,KU低,X电iaoy平an L-iu “0”为

二、CMOS反相器的直流电压传输特性

Department of Microelectronics, PKU,Xiaoyan Liu

dVOUT 1 dVIN

VOUT VIN dVOUT 1 dVIN

VIL VM VIH

VTC-直流下,将Vout描述为Vin的函数

Department of Microelectronics, PKU,Xiaoyan Liu

阈值电压 VM-VTC曲线中 VOUT VIN 的点

VOH:当输出电平为逻辑“1”时的最小输出电压,转折点

理想情况

再生能力抑制噪声

Department of Microelectronics, PKU,Xiaoyan Liu

再生的条件

为了具备再生能力,在VTC的不定区域具有大于1的增益

Department of Microelectronics, PKU,Xiaoyan Liu

最大噪声容限

理想反相器

IDp

1 Wp 2 Lp

CMOS反相器的分析与设计

CMOS反相器的分析与设计CMOS反相器由一对互补金属氧化物半导体场效应晶体管(n型MOSFET和p型MOSFET)组成。

n型MOSFET和p型MOSFET分别由n型沟道和p型沟道构成。

它们的沟道接在一起,形成一个共用的沟道。

根据输入电压的高低,CMOS反相器能够在输出端产生相反的电平。

CMOS反相器的工作原理是利用MOSFET的负阈值特性,即当输入电压高于一些阈值电压时,MOSFET处于关断状态;当输入电压低于阈值电压时,MOSFET处于导通状态。

CMOS反相器由这两个互补的MOSFET构成,保证了输入电压上升时一个MOSFET关闭,另一个MOSFET打开,输出电压下降;输入电压下降时,一个MOSFET打开,另一个MOSFET关闭,输出电压上升。

这样就实现了电平的反转。

1.确定输入输出电平:根据电路的需求,确定输入输出电平的高低电压范围,并根据具体电路的工作电压确定电源电压。

2.选择适当的MOSFET:根据设计要求,选择合适的n型MOSFET和p 型MOSFET,以满足工作电流和电压要求。

3.确定电阻参数:根据MOSFET的特性,选择合适的电阻参数来限制输入电流和确定电路的放大倍数。

4.确定电容参数:根据电路的带宽要求,确定输入和输出端的负载电容。

5.确定工作频率:根据电路的工作频率要求,确定MOSFET的开启和关闭时间。

6.进行电路仿真:通过电路仿真软件,验证设计的正确性和性能。

CMOS反相器的设计可以通过电路仿真软件如LTSpice来实现。

首先,根据设计要求选择适当的MOSFET,并确定电源电压和电阻电容参数。

然后,通过电路仿真软件搭建CMOS反相器电路,并进行仿真分析。

通过观察输入电压和输出电压的波形曲线,验证电路的正确性和性能。

如果需要进一步优化电路性能,可以通过调整各个元器件的参数来实现。

总结起来,CMOS反相器是一种常见的数字逻辑门电路,利用MOSFET的特性来实现输入输出电平的反转。

CMOS反相器的概述

CMOS反相器的概述CMOS反相器是一种非常常用的逻辑门,可以进行数字信号的反相操作。

CMOS反相器由CMOS技术制造而成,具有低功耗、高可靠性和低噪声的特点。

在数字电路中,CMOS反相器被广泛应用于时序电路、计数器、存储器等模块。

CMOS反相器的基本结构包括一个N型MOS管和一个P型MOS管,N型管和P型管的栅极通过逻辑信号控制,当输入信号为高电平时,N型管导通,P型管截断;当输入信号为低电平时,N型管截断,P型管导通。

这样,输出信号就与输入信号相反,实现了信号的反相操作。

CMOS反相器的输入和输出特性非常重要。

在CMOS反相器中,输入和输出电平可以区分为三个状态:高电平、低电平和开路状态。

当输入电平为高电平时,即逻辑1时,N型管导通,输出电平为低电平,即逻辑0;当输入电平为低电平时,即逻辑0时,P型管导通,输出电平为高电平,即逻辑1;当输入电平为开路状态时,即逻辑Z,输出电平保持上一个状态。

CMOS反相器的优点在于其低功耗和高可靠性。

由于CMOS技术将N型和P型管结合在一起,只有当输入信号改变时才会有电流流动。

在不改变输入信号时,CMOS反相器几乎不消耗功耗。

此外,由于N型和P型管分别负责导通和截断,CMOS反相器对噪声和电压干扰的抵抗能力较强,能够提供稳定的输出信号。

另外,CMOS反相器还具有较高的噪声容限和抗串扰能力。

在数字电路中,信号的传输会产生一定的噪声和串扰,这会导致信号的失真和误差。

CMOS反相器在设计上减小了管子之间的互感和电路之间的耦合,使其能够在抗噪声和抗串扰方面有较好的性能。

这使得CMOS反相器能够适应较严苛的工作环境,提供可靠的信号处理能力。

尽管CMOS反相器具有许多优点,但它也存在一些问题。

首先,由于CMOS反相器采用两个互补型MOS管连接而成,因此在制造过程中需要精心控制各项参数,如电流、阈值电压等,这使得制造过程复杂,成本较高。

此外,CMOS反相器在频率较高的应用中,存在一定的延迟和功耗问题,因此在高速和高频率应用中需要进行相应的优化和补偿。

CMOS反相器

CMOS反相器由本书模拟部分已知,MOSFET有P沟道和N沟道两种,每种中又有耗尽型和增强型两类。

由N沟道和P沟道两种MOSFET组成的电路称为互补MOS或CMOS电路。

下图表示CMOS反相器电路,由两只增强型MOSFET组成,其中一个为N沟道结构,另一个为P沟道结构。

为了电路能正常工作,要求电源电压V DD大于两个管子的开启电压的绝对值之和,即V DD>(V TN+|V TP|) 。

1.工作原理首先考虑两种极限情况:当v I处于逻辑0时,相应的电压近似为0V;而当v I处于逻辑1时,相应的电压近似为V DD。

假设在两种情况下N沟道管T N为工作管P沟道管T P为负载管。

但是,由于电路是互补对称的,这种假设可以是任意的,相反的情况亦将导致相同的结果。

下图分析了当v I=V DD时的工作情况。

在TN的输出特性i D—v DS(v GSN =V DD)(注意v DSN=v O)上,叠加一条负载线,它是负载管T P在v SGP=0V 时的输出特性i D-v SD。

由于v SGP<V T(V TN=|V TP|=V T),负载曲线几乎是一条与横轴重合的水平线。

两条曲线的交点即工作点。

显然,这时的输出电压v OL≈0V(典型值<10mV ,而通过两管的电流接近于零。

这就是说,电路的功耗很小(微瓦量级)下图分析了另一种极限情况,此时对应于v I=0V。

此时工作管T N在v GSN =0的情况下运用,其输出特性i D-v DS几乎与横轴重合,负载曲线是负载管T P在v sGP=V DD时的输出特性i D-v DS。

由图可知,工作点决定了V O=V OH≈V DD;通过两器件的电流接近零值。

可见上述两种极限情况下的功耗都很低。

由此可知,基本CMOS反相器近似于一理想的逻辑单元,其输出电压接近于零或+V DD,而功耗几乎为零。

2.传输特性下图为CMOS反相器的传输特性图。

图中V DD=10V,V TN=|V TP|=V T= 2V。

第三章CMOS反相器介绍及设计

再生能力抑制噪声

Department of Microelectronics, PKU,Xiaoyan Liu

再生的条件

为了具备再生能力,在VTC的不定区域具有大于1的增益

Department of Microelectronics, PKU,Xiaoyan Liu

最大噪声容限

理想反相器

0 V dd V tp V i V dd 截止 2 p I p 2 V i V tp V dd V 0 V tp V i V dd V tp 饱和 2 2 p V V V 线性 V V V V i tp dd i tp 0 i V 0 V tp 2

如果输入信号由于噪声而偏离额定值,则输出电压也会偏离原先的额定值

V

' OUT

dVOUT f VIN VIN 高阶项(忽略) dVIN

扰动后的电压=额定电压+增益x外部干扰

如果输出电压的增益的数量级小于1,则输入扰动不会被放大,因而造成的 输出扰动较小;否则,输入端的小小干扰将会使输出电压有一很大的扰动。 定义

第三章 CMOS反器

第一节 反相器的特性

第二节 CMOS反相器

第三节 CMOS反相器的设计

第四节 环振和反相器链

Department of Microelectronics, PKU,Xiaoyan Liu

第一节 反相器的特性

一、直流特性

1、定义

符号

反相器是实现只有一个输入变量的最基本的逻辑门电路

输入电压下降到V50%时和输出电压 上升到V50%时之间的延迟时间

详细讲解cmos反相器的原理及特点

详细讲解cmos反相器的原理及特点详细讲解cmos反相器的原理及特点CMOS(cornplementary MOS)由成对的互补p沟道与n沟道MOSFET所组成.CMoS逻辑成为目前集成电路设计最常用技术的缘由,在于其有低功率损耗以及较佳的噪声抑止才干.事实上,由于低功率损耗的需求,目前仅有CMOS技术被运用于ULSI 的制造.CMOS反相器如图6. 28所示,CMOS反相器为CMOS逻辑电路的基本单元.在CMOS反相器中,p 与n沟道晶体管的栅极衔接在一同,并作为此反相器的输入端,而此二晶体管的漏极也连接在一同,并作为反相器的输出端.n沟道MOSFET的源极与衬底接点均接地,而p沟道MOSFET的源极与衬底则衔接至电源供应端(VDD),需留意的是p沟道与n沟道MOSFET 均为增强型晶体管,当输入电压为低电压时(即vin=O,VGsn=o|VTp|(VGSp与VTp 为负值),所以p沟道MOSFET.为导通态,因此,输出端经过p沟道MOSFET充电至VDD,当输入电压逐渐升高,使栅极电压等于VDD时,由于VGSn=VDD>VTn,所以n 沟道MOSFET将被导通,而由于|VGSp |≈O欲更深化天文解CMOS反相器的工作,可先画出晶体管的输出特性,如图6.29所示,其中显现Ip以及In为输出电压(V out)函数.Ip为p沟道MOSFET由源极(衔接至VDD)流向漏极(输出端)的电流;In为n沟道MOSFET由漏极(输出端)流向源极(衔接至接地端)的电流.需留意的是在固定V out下,增加输入电压(vin)将会增加In而减少Ip,但是在稳态时,In应与Ip相同,关于给定一个Vin 可由In(Vin)与Ip(Vin)的截距,计算出相对应的V out如图6. 29所示.如图6.30所示的Vin-V out曲线称为CMOS反相器的传输曲线.CMOS反相器的一个重要的特性是,当输出处于逻辑稳态(即V out=或VDD)时,仅有一个晶体管导通,因此由电源供应处流到地端的电流非常小,且相当于器件关闭时的漏电流.事实上,只需在两个器件暂时导通时的极短暂态时间内才会有大电流流过,因此与。

第三章-MOS管反相器

图3.5.2 两级CMOS反相器级联

(a)充电模型

(b)放电模型

图3.5.3 延迟模型

(a)充电过程

(b)放电过程

图3.5.4 主要电阻和电容来源

3.6 功耗

CMOS反相器的耗功P由两部分组成, (1)静态功耗,即反向漏电造成的功耗PD; (2)动态功耗,即反相器电平发生跳变时产生的 功耗。

3.1 引言

反相器是这样的电路,当其输入信号为高电平时,其输出为低 电平,而当其输入信号为低电平,其输出则为高电平。反相器在 电路中的表示符号如图3.1.1所示。

图3.1.1 反相器符号

图3.1.2 反相器结构

3.2 NMOS管负载反相器 3.2.1 增强型NMOS管负载反相器

1、负载NMOS管工作于饱和区的反相器

1、静态功耗 图3.6.1 CMOS反相器的稳态时没有电流

图3.6.2 NMOS反相器稳态会产生电流

2、动态功耗

以CMOS反相器为例来分析动态功耗。在输入信号从 逻辑0到逻辑1的跳变或输入信号从逻辑1到逻辑0跳变的瞬间, CMOS反相器的NMOS晶体管和PMOS晶体管都处于导通状态, 这导致一个从电源VDD到地的窄电流脉冲。同时为了对负载电容 进行充电和放电,也需要有电流流动,这将引起功耗。通常,对 负载电容的充电和放电所需要的电流是造成动态功耗的主要因素。

(a)电路

3.3.2 CMOS反相器直流特性 (b)转移特性 (c)电流的变化

图3.3.1 CMOS反相器

3.4 动态反相器 3.4.1 动态有比反相器

图3.4.1 动态反相器

3.4.2 动态无比反相器 图3.4.2 动态无比反相器

3.5 延迟

(a)反相器

(b)输入从逻辑0跳变到逻辑1 (c)输入从逻辑1跳变到逻辑 图3.5.1 反相器产生延迟

cmos常用电路中异或门及反相器的功能

cmos常用电路中异或门及反相器的功能[CMOS常用电路中异或门及反相器的功能]CMOS(Complementary Metal-Oxide-Semiconductor)是一种常用的集成电路技术,在数字电路中起着重要的作用。

在CMOS常用电路中,异或门和反相器是常常会使用到的两种基本的逻辑门。

它们在数字电路设计中起着至关重要的作用,本文将探讨它们的功能以及在CMOS电路中的应用。

首先,让我们来了解一下反相器的功能及原理。

反相器是一种基本的逻辑门,它的输出与输入恰好相反。

也就是说,当输入为高电平时,输出为低电平;而当输入为低电平时,输出为高电平。

反相器常用来翻转输入信号的逻辑电平,它的符号通常表示为一个箭头,箭头指向一个小圆圈,表示逻辑反相。

在CMOS电路中,反相器通常是通过两个晶体管和一个负载电阻来实现的。

当输入为高电平时,其中一个晶体管导通,另一个截至,从而让输出变为低电平;而当输入为低电平时,另一个晶体管导通,一个截至,输出变为高电平。

这种反相器的实现方式在CMOS电路中非常常见,因为它能够提供高稳定性和高性能。

接下来我们来了解一下异或门的功能及原理。

异或门是一种逻辑门,它的输出为1的条件是两个输入信号不同。

换句话说,只有在一个输入为1,另一个输入为0的时候,输出才会为1;其他情况下输出为0。

异或门的符号通常表示为一个希腊字母“Σ”,表示逻辑异或。

在CMOS电路中,异或门通常是通过多个晶体管和负载电阻来实现的。

它的结构相对复杂一些,但原理其实和反相器类似。

通过合理地配置晶体管的导通状态,可以实现对两个输入信号进行异或运算,并得到相应的输出。

CMOS异或门通常具有高速、高稳定性和低功耗的特点,因此在数字电路设计中得到了广泛的应用。

总的来说,反相器和异或门是CMOS电路中常用的两种基本逻辑门,它们分别提供了对输入信号进行反相和异或运算的功能。

在数字电路设计中,我们可以借助这两种逻辑门来实现各种复杂的逻辑功能,比如加法、减法、乘法等等。

数字集成电路学习总结5CMOS反相器

数字集成电路学习总结5CMOS反相器今天开始总结数字集成电路。

这本书其实算是本科最难的⼀本了,细节过多⽆法卒读,涉及到的知识也⾮常全⾯。

实际上本科课程安排中并为将其作为重点,我们的课⾮常⽔,不知道讲了什么。

今天详细总结⼀下。

当时然由于内容过多,⽆法全部涵盖,只能⼤致总结,并着重记录定性的结论。

涉及到计算之类的问题,就只能略过了。

第五章 COMS反相器5.1 引⾔为什么从第五章开始,原因是这章⽐较基础,详细学习CMOS反相器后,才能继续看组合电路和时序电路等等。

研究的对象有如下⼏个指标:成本(复杂性和⾯积)、完整性和稳定性(静态特性)、性能(动态特性)、能量效率(功耗)。

5.2 静态CMOS反相器——直观综述课本上的描述:晶体管只不过是⼀个具有⽆限关断电阻和有限导通电阻的开关。

以开关来理解,可以推导出其他重要特性:1、输出⾼电平和低电平分别为VDD和GND,换⾔之,电压摆幅等于电源电压。

因此噪声容限很⼤。

2、逻辑电平与器件的相对尺⼨⽆关,所以晶体管可以采⽤最⼩尺⼨。

这⾥有⼀个概念叫⽆⽐逻辑3、稳态时,输出和VDD或GND之间总存在有限电阻的通路。

因此⼀个设计良好的CMOS反相器具有低输出阻抗,这使得它对噪声和⼲扰不敏感。

4、输⼊电阻极⾼。

理论上,单个反相器可以驱动⽆穷个门,或者说有⽆穷⼤的扇出。

但很快我们发现增加扇出也会增加传播延时。

因此扇出不会影响稳态特性,会影响瞬态特性。

5、忽略漏电流的话,意味着⽆静态功耗。

之前常⽤的是NMOS电路,静态功耗不为0,限制了集成度。

后来必须转向CMOS。

电压传输特性(VTC)的性质和形状可以通过图解法迭加两管的图像得到。

结果是观察到VTC具有⾮常窄的过渡区。

我们可以把开关特性简化为RC电路,⼀个快速门的设计是通过减⼩输出电容或者减⼩晶体管的导通电阻(增⼤宽长⽐)实现的。

5.3 CMOS反相器稳定性的评估——静态特性5.3.1 开关阈值开关阈值VM定义是Vin=Vout的点,利⽤图解法可以看出。

cmos集成电路设计第三章读书笔记

第三章:逻辑门和CMOS技术在CMOS集成电路设计中,逻辑门是一个非常重要的概念,它是数字电路的基本单元。

而在第三章中,我们对逻辑门和CMOS技术进行了深入的学习和讨论。

在本文中,我将根据第三章的内容,对逻辑门和CMOS技术进行全面评估,并撰写一篇有价值的文章,帮助你更深入地理解这一主题。

1. 逻辑门的基本概念在电子工程中,逻辑门是表示及执行布尔函数的电子电路。

它可以接受一个或多个输入信号,并产生一个输出信号。

常见的逻辑门包括与门、或门、非门等。

通过组合不同的逻辑门,我们可以实现各种复杂的逻辑功能。

2. 逻辑门的CMOS实现CMOS技术是一种在集成电路设计中广泛应用的技术。

它通过利用互补型金属氧化物半导体(CMOS)来实现逻辑门。

CMOS逻辑门由PMOS和NMOS晶体管组成,具有低功耗、高噪声抑制比和抗干扰能力强的优点。

在CMOS技术中,逻辑门的实现方式也受到了广泛的关注。

3. 对逻辑门和CMOS技术的个人观点在我看来,逻辑门和CMOS技术的学习对于集成电路设计至关重要。

逻辑门作为数字电路的基本单元,对于理解数字电路的原理和功能至关重要。

而CMOS技术作为一种先进的集成电路设计技术,不仅在数字电路设计中具有重要意义,同时在低功耗、高集成度的应用中也有着广泛的应用前景。

总结回顾通过对第三章内容的学习,我更加深入地理解了逻辑门和CMOS技术。

逻辑门作为数字电路的基本单元,具有重要的作用;而CMOS技术作为一种先进的集成电路设计技术,也具有广阔的应用前景。

希望通过这篇文章的共享,你也能对这一主题有更全面、深刻和灵活的理解。

在本文中,我根据第三章的内容,对逻辑门和CMOS技术进行了全面的评估,并共享了我的个人观点和理解。

希望这篇文章能够帮助你更深入地理解这一重要的主题。

以上就是我根据你的要求撰写的有关逻辑门和CMOS技术的文章,希望你能满意!逻辑门和CMOS技术在现代电子工程领域中扮演着至关重要的角色。

第3章-CMOS反相器的分析与设计

VDD Input

GND

反相器的逻辑符号

Vin

Vout

V DD

V in

V ou t

t

Output

特点: 作为和的共栅极; 作为共漏极; 作为的源极和体端; 作为的源极和体端

3.1 反相器的结构和基本特性

若输入为“1”( ): = , = 0V 导通,截止 输出“0” ( = 0V)

Vout Vin

的垂直线:导通/截 止

-的斜线:饱和区/ 线性区

-的斜线:线性区/ 饱和区

3.2.1 反相器的直流电压传输特性

(1) 0≤≤,截止, 线性

ID N ID P K P V in V T P V D D2V in V T P V o u t 2 0

在一定范围变化(0~),V 始o u t终 V 保D D 持。

VNLM Vit 0Vit VNHM VDD Vit

若2, =2。 实际情况, ,最大直流噪

声容限由 {} 决定。

例题

KN VinVTN 2 KP VinVTPVDD 2

Vit

KrVTN VDDVTP 1 Kr

一个反相器,1,设 = 5V, = 0.8V, = -1V, = 4.6×10-8 2,μn = 500 2、μp = 200 2。由逻辑阈值点确 定的最大噪声容限为多少?

第3章 反相器的分析与设计

第3章 反相器的分析与设计

3.1 反相器的结构和基本特性 3.2 反相器的直流特性 3.3 反相器的瞬态特性 3.4 反相器的设计

3.1 反相器的结构和基本特性

管的衬底接地,管的衬底 接。

输入端——栅极 输出端——?极 如何判断分析器中和器件

的源漏区? 是否有衬偏效应?

CMOS反相器原理结构及性能参数

CMOS反相器原理结构及性能参数CMOS反相器是一种基本的数字逻辑电路元件,由两个互补MOSFET (Metal-Oxide-Semiconductor Field-Effect Transistor)组成。

它可以实现电信号的反相,并起到信号放大的作用。

CMOS反相器不仅在数字电路中使用广泛,还在模拟电路中应用于放大器和振荡器等电路中。

CMOS反相器的基本原理是利用MOSFET的门电压控制特性,当输入信号为高电平时,NMOS(负材料氧化物半导体场效应晶体管)导通,PMOS (正材料氧化物半导体场效应晶体管)截止;当输入信号为低电平时,NMOS截止,PMOS导通。

这样,通过选取适当的参数,输出信号就可以实现输入信号的反相。

CMOS反相器的结构是由一个PMOS和一个NMOS组成,它们的结构和工作原理有所不同。

PMOS是由P型半导体材料构成的,当门电压低于阈值电压时,导电性较好;NMOS是由N型半导体材料构成的,当门电压高于阈值电压时,导电性较好。

输入电压范围指的是输入信号的电压范围,一般为输入高电平(High Level Input)和输入低电平(Low Level Input)两个阈值电压之间的范围。

输出电压范围指的是输出信号的电压范围,一般为输出高电平(High Level Output)和输出低电平(Low Level Output)两个阈值电压之间的范围。

增益是指输出电压随输入电压的变化率,一般为输出电压变化量与输入电压变化量的比值。

在CMOS反相器中,增益一般很高,可以达到几十倍甚至更高。

功耗是指CMOS反相器消耗的电功率,一般与输入电压和输出电流有关。

CMOS反相器的功耗一般比较低,因为在输入端只需要很小的电流就能控制输出的大电流。

速度是指CMOS反相器的响应时间,即输入信号变化到输出信号变化的时间。

CMOS反相器的速度一般较快,可以达到几纳秒的量级。

除了以上的性能参数,CMOS反相器还有一些其他的性能指标,如输入电容、输出电容、输出阻抗和输入阻抗等。

第三章_CMOS反相器介绍及设计概要

第三章CMOS反相器第一节反相器的特性第二节CMOS反相器第三节CMOS反相器的设计第四节环振和反相器链第一节反相器的特性一、直流特性1、定义反相器是实现只有一个输入变量的最基本的逻辑门电路符号真值表理想反相器实际反相器逻辑1OH MAXV V V≤≤逻辑0MIN OLV V V≤≤不定区OL OHV V V≤≤2、直流电压传输特性VTC Voltage Transfer CharacteristicsVTC -直流下,将Vout 描述为Vin 的函数V IL V IH1OUTINdV dV =-1OUTINdV dV =-V M OUT INV V =五个关键的电压,完全决定了VTC 、噪声容限及过渡区的位置和宽度。

阈值电压V M -VTC 曲线中的点OUT IN V V =V OH :当输出电平为逻辑“1”时的最小输出电压,转折点1OUTINdV dV =-V OL :当输出电平为逻辑“0”时的最大输出电压V IL :当输入电平为逻辑“0”时的最大输入电压V IH :当输入电平为逻辑“1”时的最小输入电压在数字电路中,逻辑值不是由单一量化电压值决定,而是相应的电压区3、噪声容限定义噪声容限:数字电路中对噪声的容忍量。

电路的抗噪声干扰能力随噪声容限(NM)的增加而增加。

低电平信号的噪声容限NML:NM L=V IL-V OL高电平信号的噪声容限NMH:NM H=V OH-V IHNM L NM HNoise Margin噪声影响下的数字信号传播在噪声容限内前级反相器输出的逻辑1能够被后级反相器识别前级反相器输出的逻辑0能够被后级反相器识别设在无噪声条件下,输入电压和输出电压间的关系为()OUT IN V f V =如果输入信号由于噪声而偏离额定值,则输出电压也会偏离原先的额定值()'OUTOUTIN IN INdV Vf V V dV =+∆+ 高阶项(忽略)扰动后的电压=额定电压+增益x 外部干扰如果输出电压的增益的数量级小于1,则输入扰动不会被放大,因而造成的输出扰动较小;否则,输入端的小小干扰将会使输出电压有一很大的扰动。

第三周学习总结-CMOS反相器

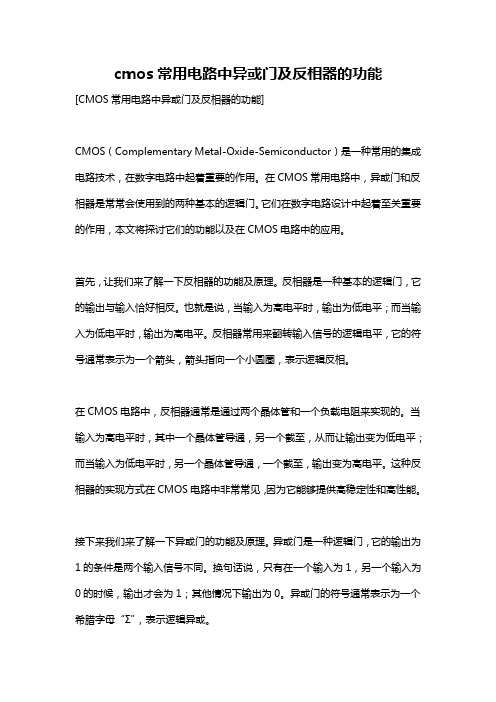

CMOS反相器静态CMOS(Complementary Metal Oxide Semiconductor)反相器是目前最普遍的反相器,其电路图如图1所示,当V in为高并等于V DD时,NMOS管导通而PMOS管截止,此时在Vout 的接地节点之间存在直接通路,形成一个稳态值0V。

相反,当输入电压为低(0V)时,NMOS 关断而PMOS管导通,V DD和V out之间存在一条通路,产生一个高电平输出电压。

由此实现反相器的功能。

图1.静态CMOS反相器电路静态CMOS反相器具有以下许多特性:(1)输出高电平和低电平分别为V DD和GND,摆幅为电源电压,噪声容限大;(2)逻辑电平与器件的相对尺寸无关;(3)具有低的输出阻抗,使它对噪声和干扰不敏感;(4)输入阻抗极高,缘于MOS管的栅实际上是一个绝缘体;(5)稳态工作下的电源线和地线之间没有直接的通路,在忽略漏电流的情况下意味着该门不消耗任何静态功率。

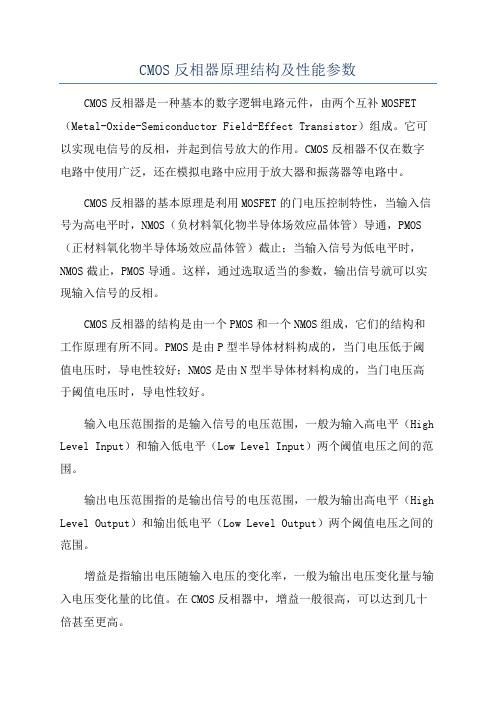

反相器的电压传输特性(VTC)可以通过图解法迭加NMOS管和PMOS管的电流特性来得到,最终如图2所示。

图2.CMOS反相器的VTC门的输出电容C L事实上包括NMOS和PMOS管的漏扩散电容、连线电容以及扇出门的输入电容。

门的响应时间由通过管子的导通电阻Rp(或者Rn)充放电容CL所需要的时间决定,传播延迟正比于RC。

这意味着可以通过减少输出电容或者减小晶体管的导通电阻实现快速响应。

应当注意,NMOS和PMOS晶体管的导通电阻不是常数,而是晶体管的两端电压的非线性函数,确切决定传播延时较为复杂。

反相器稳定性的评估,静态特性:1.开关阈值V MV M定义为V in=V out的点,在这一区域V DS=V GS,PMOS和NMOS总是饱和,使通过两晶体管的电流相等,得到V M表达式如下(器件处于速度饱和状态即V DSAT<V M-V T且忽略沟长调制效应):,得到当V DD较大时(大于阈值电压及饱和电压),上式简化为。

CMOS反相器实验报告

数字集成电路设计

实验报告

一、实验目的

通过实验了解CMOS反相器的工作原理,能自己用NMOS和PMOS搭建反相器,画出反相器的VTC曲线,可以找到Vm,调节Wp使得Vm=(1/2)Vdd,通过逼近法找到Vm点。

二、实验内容

1.用软件模拟出VTC曲线

2.找到Vm点和Vdd的关系

3.调节Wp找到Vm点

三、实验原理

四、实验步骤VTC曲线

调节Wp

最后找到Vm点

五、实验心得

通过这次实验我了解CMOS反相器的原理,对反相器有了更深的了解,同时也对tanner软件使用的更加熟练了,对上课的内容也有了深刻的了解,希望以后多做实验,通过实验才能对上课的内容记忆更加深刻,感觉总体上还好。

实验三 CMOS反相器瞬态特性

实验三CMOS反相器瞬态特性

姓名学号

CMOS反相器上升、下降及延迟时间

1.为实验二中新建的CMOS反相器“inv”建立逻辑符号“symbol”,“check

and save”没有error之后将其截屏粘贴复制到以下空白中:

3.将脉冲电压源vpulse的参数设置好以后,在模拟环境(Analog

Environment)中选择运行瞬态仿真“tran”,只需给定总的仿真时间,然后选择plot输入与输出节点。

在开始运行之前,可以预先估计一下会得到什么样的波形,然后与仿真后得到的波形相对比,并将仿真得到的波形截屏粘贴在以下空白处:

4.在波形窗口中,使用“Trace —> Delta cursor”观察,比较并记录输出电

压中对应的上升时间t r和下降时间t f(10%~90%)。

思考:输出电压中的上升时间和下降时间分别是由哪个晶体管决定?在采取同样参数设计的情况下,为什么会存在着上升下降时间的不同?

5.参照讲义,观察并记录输出电压由高到低变化时对应的延迟时间t PHL和

由低到高变化时对应的延迟时间t PLH,并计算总的延迟时间t pd

6. 通过修改PMOS管和NMOS管的宽长尺寸,将输出电压中的上升时间和下降时间调到大致相等,记录优化后的两管宽长尺寸及其宽长比的比值(W/L)PMOS/(W/L)NMOS。

将上述宽长比的比值与实验二中逻辑阈值等于0.9V 时的宽长比的比值做比较,看它们是否一样?最后,将放大后带有“Delta cursor”的输入输出曲线上升和下降部分分别截屏并粘贴到以下空白处。

最新CMOS反相器的分析与设计汇总

3.2.1 CMOS反相器的直流电压传输特性

Vin=VTN的垂直线: NMOS截止/导通

Vin=VDD+VTP的垂直 线:PMOS导通/截 止

Vin-VTN=Vout的斜线 :NMOS饱和区/线 性区

Vin-VTP=Vout的斜线 :PMOS线性区/饱 和区

16

Voltage Transfer Characteristic(VTC)

总上升时间:

tr

CL

KP

VTPV10% VDDVTP 2

2(VDD1VTP)lnVDDVDD V90% V90% 2VTP

34

K CLPV VTDPD0V.1TP VD2D2(VDD1VTP)ln1.9V0D .1DVDD 2VTP

3.3.2 CMOS反相器输出电压的上升/下降时间

(2) 阶跃输入的下降时间

21 Kr

VinVTPVDD22

Vout随Vin的增加而非线性地下降。

14

3.2.1 CMOS反相器的直流电压传输特性

(5) VDD≥Vin≥VDD+VTP,NMOS线性, PMOS截止

ID PID NK N V inV T N2V inV T NV out 2 0

V out 0

Vin在一定范围变化(VDD+VTP ~ VDD),Vout始终保持0。

VTC的转变区: Ion ≠ 0

Vin=Vit时, Ion达到最大值:

Ipeak KN Vit VTN 2 KP Vit VTP VDD 2

20

3.2.3 CMOS反相器的直流噪声容限

直流噪声容限:允许的输入电平 变化范围

由单位增益点确定噪声容限:

✓ 在VTC的(2)区和(4)区,分别可 以找到增益为1的位置;

CMOS反相器

反相器中MOSFET的工作区域

Vout

N-O P-L

Vout +VTP=Vin

N-S

N-S Vout+VTN

P-L

P-O =Vin

缩写对照:

N-O NMOS Off N-L NMOS Linear N-S NMOS Saturation P-O PMOS Off P-L PMOS Linear P-S PMOS Saturation

决定最大直流噪声容限

数字电路具有可恢复逻辑特性

可恢复逻辑特性

不可恢复逻辑特性

Transient Performance

CMOS反相器的直流特性

CMOS反相器的瞬态特性

CMOS反相器的输出上升时间 CMOS反相器的输出下降时间 CMOS反相器的传输延迟时间 电路的最高工作频率

CMOS反相器的设计 CMOS和NMOS电路性能比较

2

⎤ ⎦

=

KP

Vin − VTP − VDD

2

1

( ) ( ) ( ) Vout =

Vin − VTN

⎡ − ⎢ Vin − VTN

⎣

2− 1 Kr

Vin − VTP − VDD

2⎤ 2 ⎥ ⎦

VDD ≥ Vin ≥ VDD + VTP

特点: N-L & P-O

( ) ( ) KN

⎡ ⎣

Vin

− VTN

分析下降时间的等效电路

(1) 与上升电路类似的分析:

Vout

通过NMOS对Vout节点的

电容放电

Vin

CL

CL

dVout dt

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

CMOS反相器

静态CMOS(Complementary Metal Oxide Semiconductor)反相器是目前最普遍的反相器,其电路图如图1所示,当V in为高并等于V DD时,NMOS管导通而PMOS管截止,此时在Vout 的接地节点之间存在直接通路,形成一个稳态值0V。

相反,当输入电压为低(0V)时,NMOS 关断而PMOS管导通,V DD和V out之间存在一条通路,产生一个高电平输出电压。

由此实现反相器的功能。

图1.静态CMOS反相器电路

静态CMOS反相器具有以下许多特性:

(1)输出高电平和低电平分别为V DD和GND,摆幅为电源电压,噪声容限大;

(2)逻辑电平与器件的相对尺寸无关;

(3)具有低的输出阻抗,使它对噪声和干扰不敏感;

(4)输入阻抗极高,缘于MOS管的栅实际上是一个绝缘体;

(5)稳态工作下的电源线和地线之间没有直接的通路,在忽略漏电流的情况下意味着该门不消耗任何静态功率。

反相器的电压传输特性(VTC)可以通过图解法迭加NMOS管和PMOS管的电流特性来得到,最终如图2所示。

图2.CMOS反相器的VTC

门的输出电容C L事实上包括NMOS和PMOS管的漏扩散电容、连线电容以及扇出门的输入电容。

门的响应时间由通过管子的导通电阻Rp(或者Rn)充放电容CL所需要的时间决定,传播延迟正比于RC。

这意味着可以通过减少输出电容或者减小晶体管的导通电阻实现快速响应。

应当注意,NMOS和PMOS晶体管的导通电阻不是常数,而是晶体管的两端电压的非线性函数,确切决定传播延时较为复杂。

反相器稳定性的评估,静态特性:

1.开关阈值V M

V M定义为V in=V out的点,在这一区域V DS=V GS,PMOS和NMOS总是饱和,使通过两晶

体管的电流相等,得到V M表达式如下(器件处于速度饱和状态即V DSAT<V M-V T且忽略沟长调制效应):

,得到

当V DD较大时(大于阈值电压及饱和电压),上式简化为。

为使低电平噪声容限和高电平噪声容限具有接近的值(对称的特性),要求r接近1,即应满足。

由上述关于开关阈值的讨论可以得到下面结果:

(1)V M对器件比值的变化相对来说是不敏感的;

(2)改变Wp与Wn的比值的影响是使VTC的过渡区平移,有时不对称的传输特性在某些设计中是所希望的。

2.噪声容限与中点增益

V IH和V IL是dV out/dV in=-1时反相器的工作点,对VTC采用逐段线性近似,如图3,可以得到V IH,V IL以及噪声容限NM H和NM L如下:

图3.对VTC进行逐段近似中点增益求取的过程中,再次假设PMOS与NMOS都处在速度饱和,并考虑沟长调制效应,得到电流公式:

求解dV out/dV in,得

忽略某些二次项简化,令Vin=VM,得

I D(V M)是V in=V M流过反相器的电流。

这一增益几乎完全取决于工艺参数。

3.稳定性

主要讨论两个方面,包括器件参数、电源电压变化对器件稳定性的影响。

静态CMOS 管对器件参数变化并不敏感,如前所述器件尺寸的变化对反相器的开关阈值只产生很小影响。

增益公式说明在过渡区的增益实际上随着电源电压的降低而加大,且注意对于固定的晶体管尺寸比r,V M近似地正比于V DD,由此说明反相器的在电源电压接近晶体管的阈值电压时仍能很好地工作。

当然电源电压不是越低越好,主要受三个方面的限制:一是降低电源电压会使门延时加大;二是当电源电压和与阈值电压可以比拟时,dc特性对器件参数变化越来越敏感;三降低电源电压意味着减小信号摆幅,使反相器对外部噪声敏感。

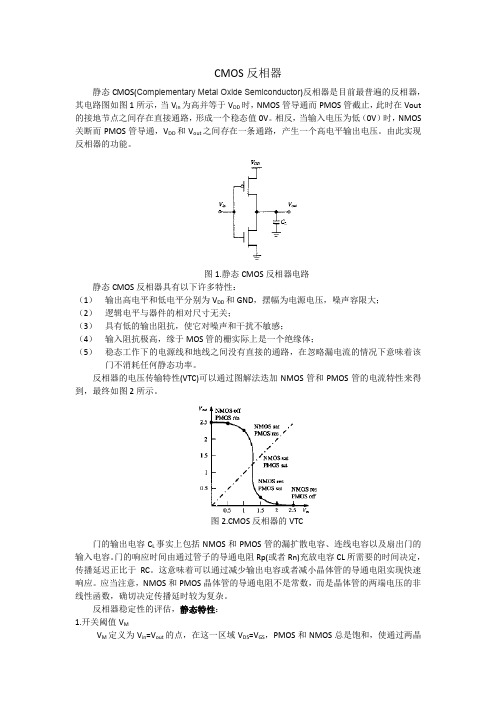

反相器的动态特性:

图4为一对串联反相器的电路图,其包括了影响节点V out瞬态响应的所有电容。

只考虑连至输出节点上的电容时,包括以下几个部分。

图4.影响一对串联反相器动态特性的寄生电容

栅漏电容C gd12:只考虑M1和M2的覆盖电容,不考虑MOS管的沟道电容,得到计算公式为Cgd=2C GD0W,其中C GD0是SPICE模型中采用的每单位宽度的覆盖电容。

此处的推导应用了密勒效应(一个在其两端经历大小相同但相位相反的电压摆幅的电容可以用一个两倍于该电容值的接地电容来代替)。

扩散电容C db1和C db2:在漏和体之间的电容来自反向偏置的pn结。

此电容很大程度取决于所加的电压,用线性电容来代替此非线性电容,引入乘数因子K eq,得到C eq=K eq C j0,C j0是零偏置条件下单位面积的结电容。

连线电容Cw:由连线引起的电容取决于连线的长度和宽度,且与扇出离开驱动门的距离和扇出门的数目有关。

扇出的栅电容Cg3和Cg4:假设扇出电容等于负载门M3和M4总的栅电容,即

计算传播延时的一种方法是对电容的充(放)电电流积分,即,确切求解方程较为困难,简化的方法通常是用常数线性元件替代取决于电压的导通电阻以及负载电容,常数线性元件的值取它在所关注时间间隔内的平均值。

电容前面已经叙述,而对于

MOS管的平均导通电阻表示为

由此得到由高到低的电压翻转时的传播延时为,由低到高翻转的传播延时为,总的传播延时定义为两个值的平均。

减少传播延时的方法无外乎减小R或者C,具体方法如减小漏扩散区的面积以减小C L、增加晶体管的W/L比,提高V DD等。

从前面推导出的延时表达式可以得出一些有意义的设计综合考虑原则,最终形成确定晶体管尺寸的一般方法。

功耗问题

反相器的功耗是由在充电和放电负载电容时消耗的动态功耗决定的,它为

功耗与电路的活动性成正比,在开关通断期间发生的直接通路电流所引起的功耗可以通过对信号斜率的仔细修正限制。

静态功耗通常可以忽略,但如果考虑亚阈值电流,它可能会成为一个主要因素。