半导体器件原理 第六章

半导体器件物理--薄膜晶体管(TFT) ppt课件

BTS(bias temperature stress):VG=VD=30 V, T=55 oC;

应力作用产生缺陷态,引起C-V曲线漂移. 16 ppt课件

6. p-Si TFF的改性技术 (1)非晶硅薄膜晶化技术-----更低的温度、更大的晶粒, 进一步提高载流子迁移率. (2)除氢技术----改善稳定性. (3)采用高k栅介质----降低阈值电压和工作电压. (4)基于玻璃或塑料基底的低温工艺技术(<350 oC).

对于恒定的VDS,VGS越大,则

沟道中的可动载流子就越多,

沟道电阻就越小,ID就越大.

即栅电压控制漏电流.

对于恒定的VGS,当VDS增大时,沟道厚度从源极到漏极逐渐变 薄, 引起沟道电阻增加,导致IDS增加变缓.当VDS>VDsat时,漏极 被夹断,而后VDS增大,IDS达到饱和.

8 ppt课件

TFT的工作原理

低载流子 迁移率

稳定性和 可靠性

TFT发展过程中遭遇 的关键技术问题?

低成本、大面 积沉膜

低温高性能半 导体薄膜技术

挑战:在玻璃或塑料基底上生长出单晶半导体薄膜!

5 ppt课件

TFT的种类

按采用半导体材料不同分为: 硅基:非晶Si-TFT,多晶硅-TFT

无机TFT 化合物:CdS-TFT,CdSe-TFT 氧化物:ZnO-TFT

V

th)V

d

1 2

V

2 d

]

(V d V g V th) …….(3)

当Vd<<Vg时,(3)式简化为I d

W L

Ci (V g V th)V d

在饱和区(Vd>Vg-Vth),将Vd=Vg-Vth代入(3)式可得:

半导体物理_第六章

对于N型半导体材料,在小注入条件下,少数载 流子空穴的浓度将以时间常数τp0进行衰减。

τp0称为过剩少数载流子的寿命。此时多数载流 子电子和少数载流子空穴的复合率也完全相等, 即:

一般而言,过剩载流子产生率通常与电子或空 穴的浓度无关。

讨论过剩载流子产生和复合过程常用的符号

3. 产生与复合过程 (1)带与带之间的产生与复合过程:

2. 过剩载流子的产生与复合 当有外界激发条件(例如光照)存在时, 将会把价带中的一个电子激发至导带,从而产 生了一个电子-空穴对,这些额外产生出的电 子和空穴就称为过剩电子和过剩空穴。

过剩电子和过剩空穴一般是由外界激发条件 而产生的,其产生率通常记为gn'和gp',对于 导带与价带之间的直接产生过程来说,过剩电 子和过剩空穴也是成对产生的,因此有:

当有过剩载流子产生时,电子的浓度和空穴 的浓度就会高出热平衡时的浓度,即:

其中n0和p0分别是热平衡状态下导带电子和价带 空穴的浓度,δn和δp分别是过剩电子和过剩空 穴的浓度。 右图所示 就是由光 激发所引 起的过剩 电子和过 剩空穴的 产生过程

当有过剩载流子产生时,外界的激发作用就 已经打破了热平衡状态,电子和空穴的浓度也 不再满足热平衡时的条件,即:

第六章 半导体中的非平衡过剩载流子

本章学习要点: 1. 了解有关过剩载流子产生与复合的概念; 2. 掌握描述过剩载流子特性的连续性方程; 3. 学习双极输运方程,并掌握双极输运方程的 几个典型的应用实例; 4. 建立并深刻理解准费米能级的概念; 5. 了解表面效应对过剩载流子复合的影响,并 掌握其定性分析的方法。

D’和μ’分别称为双极扩散系数和双极迁移率。 根据扩散系数和迁移率之间的爱因斯坦关系,

半导体物理_第六章_pn结

Jn dEF dx n n

qDp dEF J p p0 kT dx

电流密度与费米能级的关系 对于平衡的pn结,Jn, Jp均为零,因此,

Jp dEF dx p p

EF=常数

qDp dEF J p p0 kT dx

当电流密度一定时,载流子浓度大的地方, EF随 位置变化小,而载流子浓度小的地方, EF随位置 变化较大。

非平衡载流子的电注入:正向偏压使非平衡载流子进入半导 体的过程。

注入到p区的电子断与空穴复合,电子流不断转化 为空穴流,直到全部复合为止。

扩散电流〉漂移电流

根据电流连续性原理,通过pp’(或nn’)任何一个界 面的总电流是相等的。只是电子电流和空穴电流 的比例不同。 总电流=扩散电流+漂移电流

反向偏移下,非平衡状态 外加反向电场与内建势场方向一致。

1. pp’处注入的非平衡少数载流子浓度:

EFn Ei n p ni exp( ) k0T EFn EFP n p p p ni exp( ) k0T

2

p p ni exp(

Ei EFp k0T

)

在pp’边界处, x=-xp, qV=Efn-Efp,

qV n p ( x p ) p p ( x p ) ni exp( ) k0T

电子电势能-q V(x)由n到p不断升高 P区能带整体相对n区上移。n区能带整体相对p区下移。 直到具有统一费米能级 pn结费米能级处处相等标志pn结达到动态平衡,无扩散、 漂移电流流过。

动态平衡时

本征费米能级Ei的变化与-qV(x)一致

k0T n Dn q

k0T n Dn q

同理,空穴电流密度为:

qV x p ( ) 0 2. 加反向偏压下,如果qV>>k0T, e k0T

半导体物理学第六章解读

ND X D ND NA

1

Q=eND

Xn

2

0e

(

NDNA ND NA

)(VD

V

2 )

♦单边突变结:

XD

2

e

0

1

(VD V NB

)

2

♦势垒区主要在轻掺杂 一边

• 对p+-n结, NB代表ND • 对p-n+结, NB代表NA

xn X D

xp XD

P+-n结

3. 突变结的势垒电容

电势

图6-8

电子势能(能带)

6.1.5p-n载流子的分布 ♦ 当电势零点取x=-xp处,则有: EC (x) EC qV (x)

EV (x) EV qV ( x)

x x p , EC ( x) EC x xn , EC (x) EC qVD

♦势垒区的载流子浓度为:

EC qV ( x ) EF

• 反向偏压下的突变结势垒电容(单位面积):

1

CT A

dQ dV

2(

0eND NA

ND NA )(VD

V

)

2

CT 0

A XD

CT

(VD

1 V )1/ 2

• 几点说明:

① p-n结的势垒电容可以等效为一个平行

板电容器,势垒宽度即两平行极板的距离

② 这里求得的势垒电容, 主要适用于反向 偏置情况

xn

NAXD ND NA

, xp

ND X D ND NA

• 代入上式

VD

q

2 0

( NAND ND NA

)

X

2 D

♦则,平衡p-n结

1

XD

电力电子半导体器件(GTO)

掩埋门极GTO

逆导GTO

MOS—GTO

光控GTO§6.2 特性与参数一、静态特性

1.阳极伏安特性*

减小温度影响,可在门极与阴极间并一个电阻定义:正向额定电压为90%VDRM反向额定电压为90%VRRM

毛刺电流2.通态压降特性

通态压降越小,通态损耗越小

尽量缩短缓冲电路的引线,采用快恢复二极管和无感电容。

4.dv/dt和di/dt

①dv/dt :①dv/dt :

静态dv/dt 指GTO阻断时所能承受的最大电压上升率,过高

会使GTO结电容流过较大的位移电流,使α增大,印发误导通。

结温和阳极电压越高,GTO承受静态dv/dt 能力越低;门极反偏

10.关断时间:toff为存储时间

ts与下降时间tf之和。随阳极电流增大而增大2us随阳极电流增大而增大2us可关断晶闸管的主要参数和电气特性:§6.3 GTO的缓冲电路一、缓冲电路的作用

GT0的缓冲电路除用来抑制换相过电压,限制dv/dt,

,,

,动态

均压之外,还关系到GTO的可靠开通和关断,尤其是GTO的关

②下降阶段:tfIG变化到最大值-

IGM时,P1N1P2晶体管退出饱和,N1P2N2晶体管恢复控制能力,α1、α2不断减小,内部正反馈停止。

阳极电流开始下降,电压上升,关断损耗较大。尤其在感性

负载条件下,阳极电压、电流可能同时出现最大值,此时关负载条件下,阳极电压、电流可能同时出现最大值,此时关

特点:

①α1<

α212P1N1P2管不灵敏,

N1P2N2管灵敏。

②α1+

α2略大于1;器件

第6章半导体存储器

(a)

图6-8

(b)

3.快闪存储器(Flash Memory)

而且浮置栅一源区间的电容要比浮置栅一控制栅间的电容小得多 。 当控制栅和源极间加上电压时,大部分电压都将降在浮置栅与源极 之间的电容上。 快闪存储器的存储单元就是用这样一只单管组成的,如图6-8(b)所 示。

(a)

图6-8

(b)

半导体存储器的技术指标

存取容量:表示存储器存放二进制信息的多少。二值 信息以字的形式出现。一个字包含若干位。一个字的 位数称做字长。

例如,16位构成一个字,那么该字的字长为16位。一个存储 单元只能存放一个一位二值代码,即只能存一个0或者一个1。 这样,要存储字长为16的一个字,就需要16个存储单元。若 存储器能够存储1024个字,就得有1024×16个存储单元。 通常,用存储器的存储单元个数表示存储器的存储容量,即 存储容量表示存储器存放二进制信息的多少。存储容量应表 示为字数乘以位数。 例如,某存储器能存储1024个字 ,每个字4位,那它的存储容 量就为1024×4=4096,即该存储器有4096个存储单元。 存储器写入(存)或者读出(取)时,每次只能写入或读出 一个字。若字长为8位,每次必须选中8个存储单元。 选中哪些存储单元,由地址译码器的输出来决定。即由地址 码来决定。地址码的位数n与字数之间存在2n=字数的关系。 如果某存储器有十个地址输入端,那它就能存210=1024个字。

[例6-1]

[例6-1]

根据表6-2可以写出Y的表达式: Y7=∑(12,13,14,15) Y6=∑(8,9,10,11,14,15) Y5=∑(6,7,10,11,13,15) Y4=∑(4,5,7,9,11,12) Y3=∑(3,5,11,13) Y2=∑(2,6,10,14) Y1=0 Y0=∑(1,3,5,7,9,11,13,15 ) 根据上述表达式可画出ROM存储点阵如图6-9所示。

半导体物理与器件第六章2

对于非本征掺杂与小注入条件的情况,对于上述非线性的 双极输运方程,我们可以利用非本征半导体材料和小注入 条件来对其进行简化和线性化处理。

根据前面的推导,双极扩散系数D’可表示为:

D' DnDp[(n0 n) ( p0 p)] Dn (n0 n) Dp ( p0 n)

考虑P型半导体材料则: p0 n0

Lp

LP

所以对厚样品可得: A ( p)0 B 0

所以:

p(x)

p0

exp(

x Lp

)

p(x)

p0

exp(

x Lp

)

△p po

该式说明非平衡载流子向内部按指数衰减

当 x=Lp时 p p0

p0 e

e

非平衡载流子的平均扩散距离为

0

Lp x

x

xp(x)dx

0

p(x)dx

x exp(

x

)dx

5.391013 s

在4τd时间后,即4ps,

可基本达到电荷平衡,即净 (0)

电荷为0,与过剩载流子寿 命(约0.1µ s)相比,该过 程非常迅速。这证明了准电

中性条件是非常容易实现的。 (0)

e

0τ

t

双极输运方程的应用

下面用双极输运方程来讨论一些具体的实例, pn结等半导体器件 所遇到的工作状态与这些例子设定的条件是相似的,是我们随后学 习pn结以及相关器件的基础

对电流方程求散度,并利用泊松方程:

J E

代入连续性方程:

d t dt

d

dt

0

该方程容易解得:

t 0et /d

d

介电常数

电导率

介质驰豫时间常数

例6.6 n型Si掺杂浓度为1016,计算该半导体的介电驰豫常数。

半导体物理第六章3

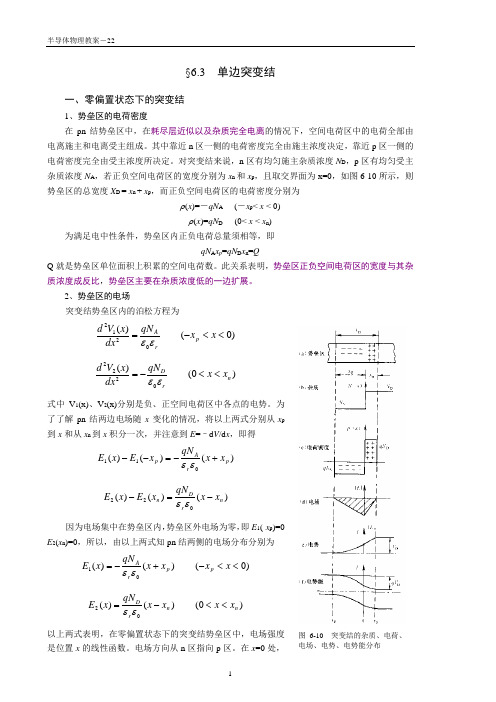

§6.3 单边突变结一、零偏置状态下的突变结1、势垒区的电荷密度在pn 结势垒区中,在耗尽层近似以及杂质完全电离的情况下,空间电荷区中的电荷全部由电离施主和电离受主组成。

其中靠近n 区一侧的电荷密度完全由施主浓度决定,靠近p 区一侧的电荷密度完全由受主浓度所决定。

对突变结来说,n 区有均匀施主杂质浓度N D ,p 区有均匀受主杂质浓度N A ,若正负空间电荷区的宽度分别为x n 和x p ,且取交界面为x=0,如图6-10所示,则势垒区的总宽度X D = x n + x p ,而正负空间电荷区的电荷密度分别为ρ(x )=-qN A (-x p < x < 0) ρ(x )=qN D (0< x < x n )为满足电中性条件,势垒区内正负电荷总量须相等,即qN A x p =qN D x n =QQ 就是势垒区单位面积上积累的空间电荷数。

此关系表明,势垒区正负空间电荷区的宽度与其杂质浓度成反比,势垒区主要在杂质浓度低的一边扩展。

2、势垒区的电场突变结势垒区内的泊松方程为)0()(0212<<-=x x qN dxx V d p r Aεε)0()(0222n r D x x qN dx x V d <<-=εε式中V 1(x)、V 2(x)分别是负、正空间电荷区中各点的电势。

为了了解pn 结两边电场随x 变化的情况,将以上两式分别从-x p 到x 和从x n 到x 积分一次,并注意到E =–d V /d x ,即得)()()(011p r Ap x x qN x E x E +-=--εε)()()(022n r Dn x x qN x E x E -=-εε因为电场集中在势垒区内,势垒区外电场为零,即E 1(-x p )=0 E 2(x n )=0,所以,由以上两式知pn 结两侧的电场分布分别为)0()()(01<<-+-=x x x x qN x E p p r Aεε)0()()(02n n r Dx x x x qN x E <<-=εε以上两式表明,在零偏置状态下的突变结势垒区中,电场强度是位置x 的线性函数。

第6章半导体器件的基本特性

(a. 电子电流、b.空穴电流)

二、PN结及其单向导电性

空间电荷区也称 PN 结

少子的漂移运动 内电场越强,漂移运 动越强,而漂移使空间 电荷区变薄。

P 型半导体

- - - - - -

- - - - - - - - - - - - - - - - - -

内电场 N 型半导体

+ + + + + + + + + + + +

1. 在杂质半导体中多子的数量与 a (a. 掺杂浓度、b.温度)有关。 2. 在杂质半导体中少子的数量与 b

(a. 掺杂浓度、b.温度)有关。 3. 当温度升高时,少子的数量 c (a. 减少、b. 不变、c. 增多)。 4. 在外加电压的作用下,P 型半导体中的电流 主要是 b ,N 型半导体中的电流主要是 a 。

+ + + + + +

+ + + + + +

扩散和漂移 这一对相反的 运动最终达到 动态平衡,空 间电荷区的厚 度固定不变。

浓度差 形成空间电荷区

多子的扩散运动 扩散的结果使 空间电荷区变宽。

PN结的单向导电性

1. PN 结加正向电压(正向偏置)

PN 结变窄

--- - - - --- - - - --- - - - + + + + + + + + + + + + + + + + + +

(c) 平面型 用于集成电路制作工艺中。PN结结面积可大可 小,用于高频整流和开关电路中。

第六章 纳米光电子材料和器件

纳米光电子材料与器件

概述

半导体器件基本类型

电子器件

光电子器件

漂移 -扩散模型 扩散 漂移模型

金半结 MIS 组 理论基础 结构基础 合 发 展 异质结 pn结

新原理,新结构器件 量子器件?光电器件? 光子器件?集成光路?

超晶格

定义:二种禁带宽度(或导电类型)不同的半导体薄层材料 交替生长组成的一维周期性结构。薄层周期小于电子的平均 自由程。 一、基本结构 1.禁带宽度不同(组份)超晶格

EC1

E0 EC1 Eg1

Eg2

EV1 EV2 LB LW LB

EV1

15

图 7.12 共振隧道二极管的能带图

b

L

EC

4.多量子阱激光器

# 量子阱中载流子能量量子化; 超晶格量子阱中量子化能级分裂成子带; 每个量子化能级的能级密度为常数:

gE m 2 2

c

略能带弯曲

EV

重空穴带

轻空穴带

17

施主能级电子—导带

受主能级空穴---价带 电离受主能级电子---导带 电离施主能级空穴---价带

Ec

Ev

3.自由载流子吸收

导带及价带内电子从低能级跃迁到高能级。 能量守恒: 动量守恒:吸收或释放声子。 特征:吸收系数随波长增大而增强。 (跃迁能量间隔小,参与声子少)

h

自由载流子等吸收

E k

直接跃迁

间接跃迁

k

4.激子吸收

激子: 处于禁带中的电子与价带中的空穴在 库仑场作用下束缚在一起形成的电中 性系统。激子可以在整个晶体中运动, 不形成电流。 激子吸收: 价带电子受激跃至禁带,形成激子。 激子吸收特征: h E g

半导体器件物理第六章--MOSFET

(6-2-24)

C ⎡ ⎛ 2C = ⎢1 + ⎜ Co ⎣ ⎝ qN a ∈S

⎞ ⎤ ⎟ VG ⎥ ⎠ ⎦

− 12

⎡ ⎤ 2 ∈0 V = ⎢1 + 2 G⎥ ⎣ qN a ∈S xo ⎦

2

− 12

(6-2-2 5)

归一化电容 C C 0 随着外加偏压 VG 的增加而减小. 反型区( VG >0)

2010-1-5

科学出版社 高等教育出版中心

9

6.1 理想MOS结构的表面空间电荷区

图6-4 几种偏压情况的能带和电荷分布

2010-1-5

科学出版社 高等教育出版中心

10

6.1 理想MOS结构的表面空间电荷区

载流子耗尽 单位面积下的总电荷为

QS = QB = − qN a x d

2 qN a xd ψS = 2 ∈s

13

6.1 理想MOS结构的表面空间电荷区

xdm 4ε sφ f 2ε sψ si = = qN a qN a

(6-1-21) (6-1-22)

QB = −qN a xdm

总表面空间电荷

QS = QI + QB = QI − qN a xdm

(6-1-23)

QI为反型层中单位面积下的可动电荷即沟道电荷:

2010-1-5

பைடு நூலகம்

(6-2-4)

科学出版社 高等教育出版中心

20

6.2 理想MOS电容器

则

1 1 1 = + C Co CS

(6-2-5)

Co =绝缘层单位面积上的电容,

C S =半导体表面空间电荷区单位面积电容。

C 1 = Co 1 + Co CS

半导体器件物理 第六章总结

6.2 少子分布

发射区空穴电流密度分布

0 qD pe pe qVeb dpe ( x) J pe ( x) qD pe (e dx L pe kT

1) e

( x x1 ) L pe

当

We L,则近似有 pe

J pe

qDpe Pe 0 qVbe L pe1 e kT 1 e We

37

6.2 少子分布

D. 基区渡越时间

Q' W B B B FB IC 2 DnB

2

38

6.2 少子分布

三 重掺杂发射区

禁带宽度变窄

1/ 2 2 N N Eg 9ln 17 ln 17 0.5 (meV ) 10 10

6.1.2 晶体管电流的简化表达式

基极电流:

一是iE2, 该电流正比于exp(VBE/Vt) ,记为iBa;另一是基区多子空穴 的复合流iBb,依赖于少子电子的数量,也正比于exp(VBE/Vt) 。故基极电 流正比于exp(VBE/Vt) 。

17

6.1 双极型晶体管的工作原理

6.1.3 工作模式

1948年,肖克莱发明了“结型晶体管 ”。1948年7月1日,美国《纽约 时报》只用了8个句子的篇幅,简短地公开了贝尔实验室发明晶体管的消 息。“一石激起千层浪”,它就像颗重磅炸弹,在全世界电子行业“引 爆”出强烈的冲击波。电子计算机终于就要大步跨进第二代的门槛! 1954年,贝尔实验室使用800支晶体管组装成功人类有史以来第一台晶 体管计算机 TRADIC

Wb csc h Lnb

X=Wb,得 到达集电结电子电流为

电工电子技术第六章

图 6-1 本征激发

2.掺杂半导体 在本征半导体中,若掺入微量的五价或三价元素,会使其 导电性能发生显著变化。掺入的五价或三价元素称为杂质 杂质。掺 杂质 有杂质的半导体称为掺杂半导体 掺杂半导体或杂质半导体,按掺入杂质元 掺杂半导体 素不同,掺杂半导体可分为N 型半导体和P 型半导体两种。

6.1.2 本征半导体和掺杂半导体

1.本征半导体 纯净而且结构完整的半导体称为本征半导体 本征半导体,它未经人 本征半导体 为的改造,具有这种元素的本来特征。 在绝对零度时,半导体所有的价电子都被束缚在共价键中, 不能参与导电,此时半导体相当于绝缘体。当温度逐渐升高或 受光照时,由于半导体共价键重的价电子并不像绝缘体种束缚 得那样紧,价电子从外界获得一定的能量,少数价电子会挣脱 共价键的束缚,成为自由电子 自由电子,同时在原共价键处出现一个空 自由电子 位,这个空位称为空穴 空穴。显然,自由电子和空穴是成对出现的, 空穴 所以称它们为电子空穴对 电子空穴对。 电子空穴对

4.非晶态半导体 非晶态半导体 原子排列短程有序、长程无序的半导体称为非晶态半 导体,主要有非晶Si、非晶Ge、非晶Te、非晶Se等元素 半导体及GeTe,As2Te3,Se2As3等非晶化合物半导体。 5.有机半导体 有机半导体 有机半导体分为有机分子晶体、有机分子络合物和 高分子聚合物,一般指具有半导体性质的碳-碳双键有 机化合物。

在我们的自然界中,各种物质按导电能力划分为导体、 绝缘体、半导体。半导体 半导体指的是导电能力导体和绝缘体之 半导体 间的物质 半导体材料的最外层轨道上的电子是4个,根据其特性, 可以将半导体材料分成以下五类: 1.元素半导体 元素半导体大约有十几种,它们处于ⅢA-ⅦA族的金 属与非金属的交界处,例如Ge(锗),Si(硅),Se (硒),Te(碲)等。

半导体物理_第六章

N型半导体材料: 假定 n0 >> p0, Dn、Dp处于同一个数量级。当其满足 小注入条件,则 δ n<< n0 。 此时双极扩散系数可简化为:

再将上述条件应用于双极迁移率的公式,同样可以 得到:

结论: 对于N型半导体材料和小注入条件: 双极扩散系数可简化为少子空穴的扩散系数; 双极迁移率可简化为少子空穴迁移率; 少子空穴的扩散系数和迁移率都为常数,因此: 双极输运方程也简化为一个线性微分方程。

电子和空穴的浓度也不再满足热平衡时的条件,即:

过剩载流子的复合 半导体中,即使有稳定的过剩载流子产生也不会导 致过剩电子浓度和过剩空穴浓度的持续增加。 过剩电子也会不断地和过剩空穴相复合。 假设过剩电子和过剩空穴的复合率分别为Rn′、Rp′ 由于过剩电子和过剩空穴是成对复合掉的,因此:

下图所示为半导体材料中过剩载流子的复合过程。 如果撤掉外界作用,由于过剩载流子的复合作用,非 热平衡状态会逐渐向热平衡状态恢复。

612过剩载流子的产生与复合讨论过剩载流子产生和复合过程常用的符号过剩载流子的产生当有外界激发条件如光照时会把半导体价带中的电子激发至导带从而在导带中产生导电电子同时也会在价带中产生导电空穴即受到外部激励时半导体材料相对于热平衡状态额外产生了电子空穴对

如果半导体材料受到外部的激励(如温度的突然 升高),那么在原来热平衡浓度的基础上,会增加额 外的导带电子和价带空穴----非平衡过剩载流子,过 剩载流子是半导体器件工作的基础。 本章重点学习描述非平衡过剩载流子随空间位置 和时间变化状态---双极输运方程,这是研究分析PN 结和双极型晶体管特性的基础。

利用上述两个方程消去其中电场的微分项,即可得 到:

上式称为双极输运方程。 它描述了过剩电子浓度和过剩空穴浓度随着时间和空 间的变化规律,其中的两个参数分别为:

半导体器件物理_chapter6_TFT及其制造技术[1]

![半导体器件物理_chapter6_TFT及其制造技术[1]](https://img.taocdn.com/s3/m/eaab7eea856a561252d36f95.png)

TFT的工作原理

工作于积累状态下原理示意图

工作原理:与MOSFET相似,TFT也是通过栅电压来调节沟道 电阻,从而实现对漏极电流的有效控制. 与MOSFET不同的是:MOSFET通常工作强反型状态,而TFT根 据半导体活性层种类不同,工作状态有两种模式: 对于a-Si TFT、OTFT、氧化物TFT通常工作于积累状态. 对于p-Si TFT工作于强反型状态.

∴ 可用于介 质、半导体的 沉积。

SiH4+H2,N2

等离子增强化学气相沉积(PECVD: Plasma Enhanced CVD) 加放电电源,使气体离化→等离子体

直流辉光放电 射频放电 脉冲放电 微波放电等 特点: 沉积温度较低

SiH4+H2,N2

(3)a-Si薄膜晶化方法比较

SPC:Solid-Phase Crystallization MILC:Metal-induced Lateral Crystallization ELA:Excimer Laser Crystallization

p-Si TFT制备中的关键工艺技术

1、LTPS TFT LCDs 技术水平 2002年 2005年 2009年

(640*480)(1024*768) (320*240) (60~120) (刷新频率) (50~60)

2002年

2005年

2009年

TEOS: 正硅酸乙酯

2、p-Si 薄膜制备技术 方法1:直接沉积p-Si thin film p-Si thin film 晶化 方法2: a-Si thin film (1)p-Si 薄膜制备方法----低压化学汽相沉积(LPCVD)

基于有机TFT的全打印7阶环形振荡器电路

全打印技术制备n、p沟TFT

半导体物理与器件-第六章 半导体中的非平衡过剩载流子

Generation rate

Recombination rate

3

6.1载流子的产生与复合 6.1.1平衡半导体

平衡态半导体的标志就是具有统一的费米能级

EF,此时的平衡载流子浓度n0和p0唯一由EF决定。

平衡态非简并半导体的n0和p0乘积为

n0p0

Nc N vexp(

Eg kT

)

ni2

质量定律

称n0p0=ni2为非简并半导体平衡态判据式。

第6章 半导体中的非平衡过剩载流子

1

第6章 半导体中的非平衡过剩载流子

6.1载流子的产生与复合 6.2过剩载流子的性质 6.3双极输运 6.4准费米能级 *6.5过剩载流子的寿命 *6.6表面效应

2

6.1载流子的产生与复合 6.1.1平衡半导体

平衡状态下产生率等于复合率

产生是电子和空穴的生成过程 复合是电子和空穴的消失过程

一般来说:n型半导体中:δn<<n0,δp<<n0。 p型半导体中:δn<<p0,δp<<p0。

小注入:过剩载流子浓度远小于平衡态时的多子浓度. 大注入:过剩载流子浓度接近或大于平衡时多子的浓度.

7

6.1载流子的产生与复合 6.1.2过剩载流子

注意:

1.非平衡载流子不满足费米-狄拉克统计分布.

(有发光现象)、把多余能量传递给晶格或者把多余能量交给其 它载流子(俄歇复合)。

15

6.1载流子的产生与复合 6.1.2过剩载流子

过剩载流子的产生与复合相关符号

16

6.2过剩载流子的性质 6.2.1连续性方程

单位时间内由x方向的粒子流产生的 空穴的净增加量

Fpx为空穴粒子的流量

半导体物理与器件第六章1

陈延湖

第六章 半导体中的非平衡过剩载流子

前面几章讨论的半导体的载流子均为热平衡载流子,在一定温度下 由本征激发和杂质激发产生的载流子浓度是一定的,用n0和p0表示热平 衡电子浓度和空穴浓度:

n0

Nc

exp(

EC EF kT

)

p0

Nv

exp(

EF EV kT

)

导带电子和价带空穴系统具有统一的费米能级EF

本章重点问题:

非平衡过剩载流子的产生与复合的机理 非平衡过剩载流子的寿命 在存在漂移和扩散运动时,非平衡过剩载流子的

时空分布特性分析——连续性方程 连续性方程的应用

本章主要内容

非平衡载过剩流子的产生、复合、寿命(6.1 6.5) 表面效应 表面复合(6.6) 准费米能级(6.4) 过剩载流子的性质-连续性方程(6.2) 连续性方程的深入-过剩载流子的双极输运方程

而非平衡少子远多于平衡少子,其影响不可忽略,在器件中 起到重要的作用,因此通常所说的非平衡载流子一般都是指的非 平衡少数载流子

对n型半导体: p p0

对p型半导体: n n0

§5.1 §5.2 非平衡载流子的注入、复合、寿命

例如

电阻率为 1 cm 的N型半导体,热平衡载流子浓度 n0 5.51015 cm-3, p0 3.1104 cm-3

G:载流子的产生率,单位时间,

单位体积内产生的导带电子或价 带空穴数。个/cm-3

R:电子一空穴对的复合率,单

位时间,单位体积内复合消失的 导带电子和价带空穴数。个/cm-3

产生率与导带中的空状态密度Nc以 及价带中相应的电子占据状态密度 成正比,对非简并半导体,因电子 和空穴浓度与导带和价带的状态密 度相比非常小,因而电子和空穴密 度几乎不影响产生率

半导体器件物理第六章习题

第六章 金属-氧化物-半导体场效应晶体管6-1.绘出在偏压条件下MOS 结构中对应载流子积累、耗尽以及强反型的能带和电荷分布的示意图,采用N 型衬底并忽略表面态和功函数的影响。

6-2.推导出体电荷、表面电势以及表面电场的表达式,说明在强反型时他们如何依赖于衬底的掺杂浓度a N 。

在1410至1810 3−cm 范围内画出体电荷、表面电势及电场与a N 的关系。

6-3.在受主浓度为31610−cm 的P 型硅衬底上的理想MOS 电容具有0.1um 厚度的氧化层,40=K ,在下列条件下电容值为若干?(a )V V G 2+=和Hz f 1=,(b ) V V G 20=和Hz f 1=,(c )V V G 20+=和MHz f 1=。

6-4.采用叠加法证明当氧化层中电荷分布为)(x ρ时,相应的平带电压变化可用下式表示:0000()x FB q x x V dx C x ρΔ=−∫ 6-5.一MOS 器件的01000x =Å,eV q m 0.4=φ,eV q s 5.4=φ,并且有21610−cm的均匀正氧化层电荷,计算出它的平带电压。

假设40=K ,运用习题6-4的表达式 6-6.利用习题6-4中的结果对下列情形进行比较。

(a) 在MOS 结构的氧化层中均匀分布着212105.1−×cm 的正电荷,若氧化层的厚度为150nm ,计算出这种电荷引起的平带电压。

(b) 若全部电荷都位于硅-氧化硅的界面上,重复(a)。

(c) 若电荷成三角分布,它的峰值在0=x ,在0x x =处为零,重复(a)。

6-7.在31510−=cm N a 的P 型Si<111>衬底上制成一铝栅MOS 晶体管。

栅氧化层厚度为120nm ,表面电荷密度为211103−×cm 。

计算阈值电压。

6-8. 一MOS 结构中由315105−×=cm N a 的N 型衬底,100nm 的氧化层以及铝接触构成,测得阈值电压为2.5V ,计算表面电荷密度。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

6.2.1 内建夹断电压、夹断电压和漏源饱 和电压

VGS

VGS

单边n沟JFET

单边p沟JFET

近似为单边突变结,设沟道宽度为a,热平衡时的耗尽层 宽度为h,内建电势为Vbi,外加栅源电压VGS,内建夹断电

压Vpo,夹断电压Vp

6.2.1 内建夹断电压、夹断电压和漏源饱和电压

空间电荷区宽度为: 1 2 s (Vbi VGS ) 2 h[ ] eN d 在阈值点, h a , p n结 的 总 电 势 称 为 内 建 断 夹电 压 , 用V po 表 示 2 sV po 1 a [ ]2 eN d 2 eN d a V po 2 s 把 形 成 沟 道 夹 断 所 加栅 的源 电 压 称 为 夹 断 电 压 ( 阈 电) 压VP Vbi V p VPo n沟 耗 尽 型 JFET , 夹 断 电 压 是 负 值 , 此 因VPO Vbi

漏电流同时决定于栅源电

压和漏源电压 饱和区: 漏电流与漏源电压无关, 只决定于栅源电压

6.1.2 MESFET的基本工作原理

MESFET ( Metal-Semiconductor FET ) 是 一 种 由

Schottky 势垒栅极构成的场效应晶体管,适用于高频 应 用 , 如 工 作 频 率 超 过 5GHz 的 放 大 器 和 振 荡 电 路 中。可以作为分立器件,也可以做成集成芯片, GaAs-MESFET是微波集成电路的核心。

ID存在,且仍由导电沟道区电特性决定

6.1.1pn-JFET

漏源I-V特性定性分析

击穿区:(VDS大到漏栅结的雪崩击穿电压 )

6.1.1pn-JFET

漏源I-V特性定性分析

2、 VGS<0的情况:(1)器件偏置特点(VDS=0)

零偏栅压

小反偏栅压

VGS<0

漏(源)栅结已经反偏 ; 耗尽层厚度大于VGS =0的情况; 有效沟道电阻增加。

6.1.1 pn-JFET

沟道随VGS变化情况 (VDS很小时)

为分析JFET的基本工作原理,首先假设

一个标准的偏置条件。VG≤0:pn结是零

偏或反偏。

VD≥0:确保n区电子从源端流向漏端。

通过系统改变电压来分析器件内发生的变

化。

1.

ID-VDS特性曲线随VGS的变化会有什么变化?

(1)VGS=0,顶部和底部的p+n结处于热平衡,沟道宽度

如果把半绝缘衬底用本征材料,其能带如图所示。因为

在沟道与衬底之间,沟道与金属栅之间存在势垒,电子 将被束缚在沟道中。

MESFET分为耗尽型(D- MESFET)和增强型(E- MESFET)

耗尽型: VG=0时,沟道 没有完全耗尽

VG=0时,沟道已完全耗尽,必须加一个正向偏压, 以减少耗尽层宽度,增加沟道电流

(2) ID—VDS关系

VDS较小: 线性区

VDS增大: VDS较大: 增加到正好使漏 端处沟道横截面 积 =0 夹断点:沟道横 截面积正好=0

过渡区

6.1.1pn-JFET

漏源I-V特性定性分析

不断增大漏电压,直到靠近漏端附近的顶部和底部的耗尽

区最终连接到一起,此时沟道完全耗尽,这一条件称为 “夹断”,所对应的漏电压称为“夹断电压”。 饱和区:( VDS 在沟道夹断基础上增加)

6.1.1pn-JFET

(2) I D — V DS关系

漏源I-V特性定性分析

特点:a. 电流随电压变化趋势,基本过程相同, b. 电流相对值减小。 c. 夹断电压变小,VDS(sat: VGS<0)<VDS(sat: VGS=0) d. 击穿电压变小,BVDS(sat: VGS<0)<BVDS (sat:VGS=0)

6.1.1pn-JFET

VGS足够小 3、

漏源I-V特性定性分析

VGS

VGS ↓= VP使上下耗尽层将沟道区填满, 沟道从源到漏 I D =0 ,器件截止。 彻底夹断,

结论:栅结反偏压可改变耗尽层大小,从而控制漏电流大小。

6.1.1pn-JFET

非饱和区:

漏源I-V特性定性分析

N沟耗尽型JFET的输出特性:

增强型:电压摆幅小,因为所加正压不能太高, 否则从电流从栅极走掉了

第六章:结型场效应晶体管

6.1 JFET概念 6.2 器件的特性 6.3 非理想因素 6.4 等效电路和频率限制 6.5 高电子迁移率晶体管

6.2 器件的特性

6.2.1 内建夹断电压、夹断电压和漏源饱和电压

最宽,漏端加一个小的VDS,就形成漏电流。

VGS=0

(2)栅极加负偏压VGS<0时,顶部和底部的p+n结都处于反

偏,增加了耗尽层宽度,而使沟道的宽度变窄,沟道电阻变 大,使ID-VD曲线中线性部分的斜率变小。 栅极加负偏 压VGS<0

(3)对于较大的负偏压VG,即使VD=0,也可能使整个沟道

都处于耗尽状态。当VD=0,使整个沟道完全耗尽的栅电压

调制(影响)下面半导体的电 导,从而实现AB两端的电流控 制。

场效应:半导体电导被垂直于半

导体表面的电场调制的现象。

特点:多子器件,单极型晶体管

6.1.1 pn-JFET基本工作原理

1952年,Shockley首次提出并分析了结型场效应晶体

管。

在JFET中所加的栅电压改变了 pn结耗尽层宽度,耗

管的工作电流仅由多数载流子输运,故又称之为“单 极型(场效应)晶体管”。

JFET可分为两类:

Pn结场效应晶体管(pn JFET),pn结制成;

金属-半导体结型场效应晶体管(MESFET),肖特基

势垒整流接触结制成。

所用知识:半导体材料、PN结、肖特基势垒二极管

第六章:结型场效应晶体管

6.1 JFET概念 6.2 器件的特性 6.3 非理想因素 6.4 等效电路和频率限制 6.5 高电子迁移率晶体管

内建夹断电压、夹断电压和漏源饱和电压

对 于p沟JFET 2 s (Vbi VGS ) 1 h[ ]2 eN a 在阈值点, h a , n p结 的 总 电 势 称 为 内 建 断 夹电 压 , 用V po 表 示 2 sV po 1 a [ ]2 eN a eN a a 2 V po 2 s 把 形 成 沟 道 夹 断 所 加栅 的源 电 压 称 为 夹 断 电 压 (阈电压) VP Vbi V p VPo或VP VPO Vbi P沟 耗 尽 型 JFET , 夹 断 电 压 是 正 值 。

6.1.2 MESFET的基本工作原理

肖特基势垒代替PN结

耗尽型:

当在栅源极之间加一个反偏 电压时,金属栅极下面产生 一个空间电荷区,用以调制 沟道电导。如果所加负压足 够大,空间电荷区就扩散到 衬底,这种情况称为夹断。

耗尽型:加负压耗尽层扩展到夹断(正压情况不行)

6.1.2 MESFET的基本工作原理

内建夹断电压、夹断电压和漏源饱和电压

2 s (Vbi VGS 源端的耗尽层宽的: h1 [ ] eN d 2 s (Vbi VDS VGS 1 漏端的耗尽层宽的: h2 [ ]2 eN d 当h2 a时 , 沟 道 夹 断 在 漏 端 生 发, 这 时 对 应 的 漏源 电 压V 用 (sat )表 示 DS 1 2 s (Vbi VDS ( sat ) VGS 2 a [ ] eN d ea 2 N d 也可表示为: Vbi VDS ( sat ) VGS VPO 2 s VDS ( sat ) VPO (Vbi VGS )当VGS〉VP时 , 此 式 将 失 去 意 义 对 于p沟JFET , 则 有 : VDS ( sat ) VPO (Vbi VGS )

(3)当VD增加到零点几伏以上时,由于从沟道电阻逐渐增大,ID-VD 曲线的斜率将

会减小。

(4)不断增大漏电压,直到靠近

漏 端附近的顶部和底部的耗尽区最 终连接到一起,此时沟道完全耗尽, 这一条件称为“夹断”,所对应的 漏电压称为“夹断电压VDsat” (5) 当VD>VDsat后,随VD的增加, ID基本保持不变,达到饱和

在N型半导体硅 片的两侧各制造 一个PN结,形 成两个PN结夹 着一个N型沟道 的结构。P区即 为栅极,N型硅 的一端是漏极, 另一端是源极。

G-栅极(基极) S-源极(发射极) D-漏极(集电极)

JFET的基本结构(n沟道结型场效应管)

6.1.1 pn-JFET基本工作原理

漏源I-V特性定性分析

6.2.1 内建夹断电压、夹断电压和漏源饱和电压

分析栅极和漏极同时加电压的情况:

由于漏端电压的作用,沟道中不同位置的电压

不同,所以耗尽层的宽度随沟道中的位置而不

同。

内建夹断电压、夹断电压和漏源饱和电压 栅极和漏极同时加上电压: 耗尽层的宽度随在沟道中的 位置不同而不同

N沟pn JFET器件的基本几何结构图

漏源电压在沟道 区产生电场,使 多子从源极流向 漏极。

对称n沟pn结JFET的横截面图

6.1.1 pn-JFET基本工作原理 与MOSFET比较

ID的形成:(n沟耗尽型)

如果源极接地,并在漏极加上一个小的正电压,则在漏源之

间就产生了一个漏电流ID。

两边夹 厚度几~十 几微米 对称n沟pn结JFET的横截面 结型:大于107Ω,绝缘栅:109~1015Ω。

6.1 JFET概念内容

6.1.1 pn JFET基本工作原理

6.1.2 MESFET基本工作原理

结型场效应管分类: pn JFET MESFET

JFET基本概念

场效应现象20世纪20年代和30年

代被发现,文献记载如图所示的 晶体管结构,是第一个被提出来 的固态晶体管。